#### Feature

- 4.75V to 16V Supply Voltage Operating Range.

- 380KHz ±15% Fixed Switching Frequency.

- Voltage-Mode PWM Step-Down Regulator.

- Built-in Power MOSFET,  $Rds(on) = 100m \Omega$ .

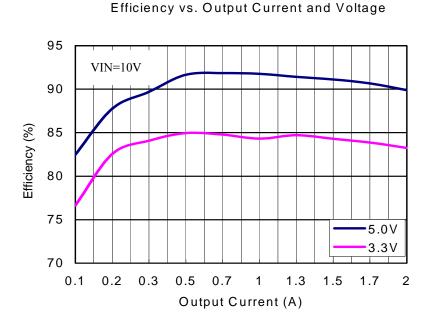

- 2A Output Current, Up to 91.9% Efficiency

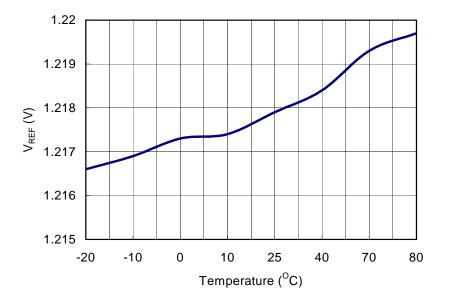

- 1.215V±1.5% Internal Reference

- Shutdown Current less than 20uA.

- Thermal-Shutdown and Built-in Soft-Start.

- Cycle-by-Cycle Current-Limit Protection.

- Short Circuitry Protection.

- Under-Voltage Lockout Protection.

- Output Voltage Adjustable From 1.215V to 16V.

- SOP-8 Package.

#### Application

- · Distributed Power Systems

- Battery Charger.

- Palmtop Computers, PDAs.

- DSL Modems

**Block Diagram**

#### Description

AT1799 is a voltage-mode PWM step-down DC-DC converter capable of driving up to 2A loads over a wide input supply range with excellent line and load regulation characteristics. High efficiency is obtained through the use of a low Rds(on) P-channel power switch.

It uses a fixed switching frequency up to 380KHz thus allowing smaller sized components. The output voltage level is user-programmable via an external resistive voltage divider. The built-in soft-start can reduce inrush current on the input source at turn on.

The device also has built-in cycle-by-cycle current-limit, thermal shutdown, under-voltage lockout and an ON/OFF logic-control that can power down the regulator to a shutdown mode. In shutdown mode the regulator draws less than 20uA of supply current. When a short circuit is detected on the output, the device immediately change switching frequency to 42 KHz and duty cycle is limited to 5% to protect IC from damage.

AT1799 is available in SOP-8 package.

#### EN Under-voltage IN lockout Current Sense Amplifier Curren Se P-MOS Contol osc Logic 42/380KHz SW SCI WM Con Error Softnplifie Start GND 1 215 FB COMP

Aimtron reserves the right without notice to change this circuitry and specifications.

2F, No.10, Prosperity RD. II, Science-Based Industrial Park, Hsinchu 300, Taiwan, R.O.C.Tel: 886-3-563-0878Fax: 886-3-563-08798/23/2006REV:1.1Email: service@aimtron.com.tw

# Downloaded from Elcodis.com electronic components distributor

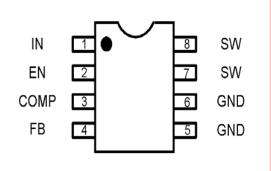

# **Pin Configuration**

#### **Ordering Information**

| Part number | Package     | Marking                             |

|-------------|-------------|-------------------------------------|

| AT1799S     | SOP-8       | Dello Date Code                     |

| AT17998_GRE | SOP-8,Green | DDD ,Date Code with one bottom line |

#### **DDD:** Date Code

\*For more marking information, contact out sales representative directly

#### **Pin Descriptions**

| Pin N0. | Symbol | I/0 | Description                                                                                                                               |

|---------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | IN     | Р   | Power Input. IN supplies power to the IC and Step-down converter switch. IN must be bypassed with a low-ESR capacitor.                    |

| 2       | EN     | Ι   | Enable input. EN is a digital input that turns the regulator on/off. Drive EN high to turn on the regulator, drive it low to turn it off. |

| 3       | COMP   | 0   | Error Amplifier Output. A series RC network connected to this pin compensates AT1799.                                                     |

| 4       | FB     | Ι   | Feedback Input. Connect a resistive divider from switching output to FB to ground.                                                        |

| 5,6     | GND    | Р   | Ground.                                                                                                                                   |

| 7,8     | SW     | 0   | Power Switching Output.                                                                                                                   |

#### **Absolute Maximum Ratings \*1**

| Parameter                           |                         | Rated Value | unit |

|-------------------------------------|-------------------------|-------------|------|

| IN , EN voltage                     |                         | -0.3 to 16  | V    |

| SW voltage                          |                         | -1 to IN+1  | V    |

| FB, COMP voltage                    |                         | -0.3 to 6   | V    |

| Quiescent current                   |                         | 5           | mA   |

| Thermal Resistance (Junction to amb | pient $\theta_{JA}$ )*2 | 105         | °C/W |

| Junction Temperature (Tj)           |                         | 150         | °C   |

| Lead Temperature (Soldering 10 sec) | )                       | 260         | °C   |

| Storage Temperature                 |                         | -65~150     | °C   |

|                                     | HBM                     | 2           | KV   |

| ESD Susceptibility*3                | MM                      | 200         | V    |

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2. Measured on approximately 1" square of 1 oz. copper FR4 board.

3. Device are ESD sensitive. Handling precaution recommended. The Human Body model is a 100pF capacitor discharged through a  $1.5 K\Omega$  resistor into each pin.

| Parameter             | Symbol | Values |      |      | T    |  |

|-----------------------|--------|--------|------|------|------|--|

|                       |        | Min.   | Тур. | Max. | Unit |  |

| Power supply voltage  | IN     | 4.75   | 12   | 16   | V    |  |

| Operating temperature | Тор    | -20    | +25  | +85  | °C   |  |

#### **Recommended Operation Conditions**

#### **Electrical Characteristics**

| Electrical Characteristics (IN=12V, EN=5V, Ta=+25°C, unless otherwise note |                            |                                            |      |       |       |       |  |

|----------------------------------------------------------------------------|----------------------------|--------------------------------------------|------|-------|-------|-------|--|

| Parameter                                                                  | Symbol                     | Test Condition                             | Min. | Тур.  | Max.  | Units |  |

| Input operating voltage                                                    | IN                         |                                            | 4.75 | 12    | 16    | V     |  |

| Input under-voltage lockout threshold                                      | V <sub>UVLO</sub>          | IN Rising                                  | 3.8  | 4.2   | 4.6   | V     |  |

| UVLO hysteresis                                                            |                            |                                            | -    | 500   | -     | mV    |  |

| Quiescent Current                                                          | Iin                        | V <sub>FB</sub> =1.5V                      | -    | 3.5   | -     | mA    |  |

| Shutdown Current                                                           | I <sub>SHDN</sub>          | EN =GND                                    | -    | 20    | 50    | uA    |  |

| Oscillator Frequency                                                       | $\mathbf{f}_{\mathrm{SW}}$ | Ta=+25                                     | -    | 380   | 440   | KHz   |  |

| Short-Circuit Frequency                                                    |                            | FB=0V                                      | -    | 42    | -     | KHz   |  |

| Feedback Regulation voltage                                                | $V_{FB}$                   | Ta=+25                                     | 1.20 | 1.215 | 1.233 | V     |  |

| FB Input Bias Current                                                      | I <sub>FB</sub>            | V <sub>FB</sub> =1.215V                    | -50  | -     | 50    | nA    |  |

| Current limit                                                              |                            |                                            | 2.5  | 2.75  | -     | А     |  |

| Maximum Duty Cycle                                                         | D <sub>MAIN</sub>          | FB=1.0V                                    | -    | -     | 100   | %     |  |

| Minimum Duty Cycle                                                         | D <sub>MIIN</sub>          | FB=1.5V                                    | 0    | -     | -     | %     |  |

| SW Switch On-Resistance                                                    | R <sub>SW-DS(ON)</sub>     | I <sub>SW</sub> =2A                        | -    | 100   | 130   | mΩ    |  |

| SW Leakage Current                                                         | I <sub>SW</sub>            | IN=13.5V,V <sub>SW</sub> =GND<br>, EN=0V   | -    | 0.1   | 20    | μΑ    |  |

| Load Regulation                                                            |                            | $0 \text{ A} \leq I_{SW} \leq 2 \text{ A}$ |      | 0.2   |       | %     |  |

| Line Regulation                                                            |                            | 4.75V < IN<16V                             | -    | 1.0   | -     | %/V   |  |

| Error Amplifier Voltage Gain                                               |                            |                                            | -    | 70    | -     | dB    |  |

| Error Amplifier Trans-conductance                                          |                            |                                            | 500  | 800   | 1000  | μA/V  |  |

| Soft-Start Time                                                            |                            |                                            | -    | 10    | -     | ms    |  |

| EN Threshold Voltage                                                       |                            | Hysteresis 150mV                           | -    | 1     | -     | V     |  |

| EN Pull Up Current                                                         |                            | EN=0V                                      | -    | 1     | -     | μΑ    |  |

| Thermal Shutdown                                                           |                            |                                            | -    | 160   | -     | °C    |  |

# **Typical characteristics**

Reference Voltage vs Temperature

# AT1799 2A Step-Down Voltage Regulator

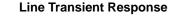

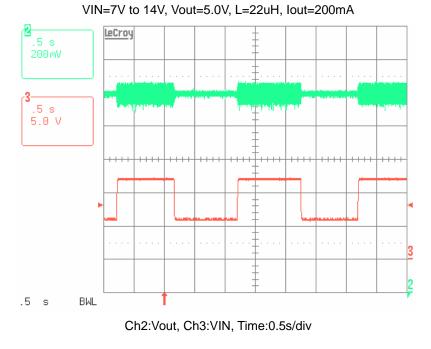

# VIN=12V, Vout=5.0V, L=22uH, Iout=500mA to 2.0A Eile Edit Vertical Horiz/Acq Irig Display Cursors Measure Masks Math MyScope Utilities Help Sample 776 Acqs 15 May 06 22:41:52 Tek Run (Buttons) Ch1 Position 1.0div Ch1 Scale 200.0mV 4+ 200mV % Bw Ch1 M 200µs 250MS/s A Ch1 \ -116mV 4.0ns/pt 1.0A Ω <sup>B</sup>W Ch4

#### Ch2:Vout, Ch4:Iout, Time:1ms/div

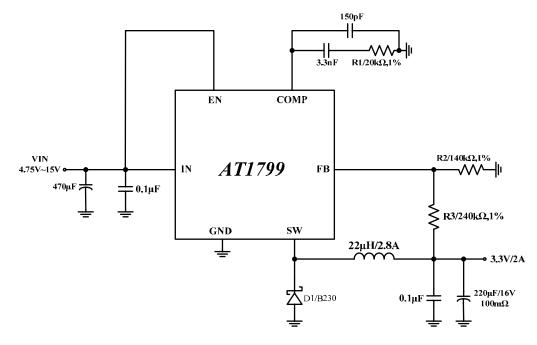

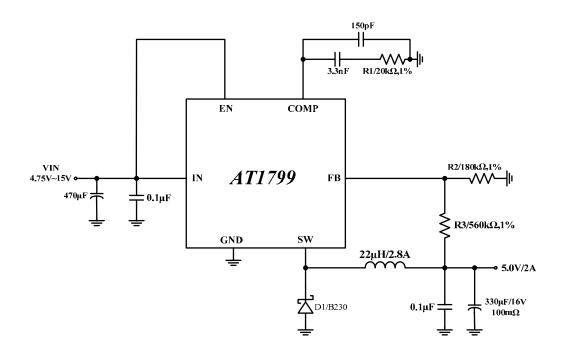

# **Typical Application Circuit**

## **General Description**

The AT1799 features a PWM step-down converter operating with a fixed switching frequency of 380 KHz and uses internal power MOSFET to provide maximum efficiency. The output voltage of the converter can be set as low as 1.215V with external resistive divider. When trans-conductance signal is higher than saw-tooth wave, then PWM comparator will produce ON-time signal to set internal flip-flop, which turns on the switching power MOSFET. The external inductor current ramps up linearly, storing energy in a magnetic field. Once peak current of flowing through switching power MOSFET over current-limited threshold or trans-conductance signal level is lower than saw-tooth wave, the switching power MOSFET will turns off, the flip-flop resets, and external schottky diode turns on. This forces the current through the inductor to ramp back down, transferring the energy stored in the magnetic field to the output capacitor and load. To add higher flexibility to the selection of external component values, the device uses external loop compensation.

#### **Enable Control**

Digital logic of EN provides an electrical ON/OFF control of the power supply. Connecting this pin to ground or to any voltage less than 1.0V will completely turn OFF the regulator. In this state, current drain from the input supply is only  $20\mu$ A, the internal reference, error amplifier, comparators, and biasing circuitry turn off. When EN control is not required that it should be left open circuited.

#### Soft-Start

AT1799 is built-in soft-start function. When power up, after input voltage is above the under-voltage lockout threshold, then soft-start allows a gradual increase of COMP voltage to get to a steady state operating point. Therefore, reducing input surge currents. During this time, the COMP voltage increases and the output duty cycle is allowed to increase from zero to the value required for regulation. The maximum load current is available after the soft-start cycle is completed. When EN pin is taken low, the soft-start capacitor is discharge to ground.

#### **Short-Circuit Protection**

If feedback voltage of the regulator falls below 0.7V, the oscillator clock switched operating frequency to 42KHz and duty cycle is limited to 5% to reduce input power delivered to output. If the short circuitry is not removed, the protection circuitry will activate sustainability. When short-circuit problem is to eliminate, oscillator clock will switch back to 380KHz automatically.

## **Cycle-by-Cycle Over-Current Protection**

The AT1799 provides cycle-by-cycle over-current protection. Current limit is accomplished using a separate dedicated comparator. If the current sense amplifier output voltage is larger than current-limited threshold level, it will be immediately turned off power MOS. The current-limit feature protects against a hard short or over current fault at the output.

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the AT1799. When the junction temperature exceeds Tj=160 , a thermal sensor activates the thermal protection, which shuts down the IC, allowing the IC to cool. Once the device cools down by 15 , IC will automatically recover normal operation. For continuous operation , do not exceed the absolute maximum junction-temperature rating of Tj=150 .

# **Applications Information**

External components of step-down converter can be designed by performing simple calculations. It must be to follow regulation by the output voltage and the maximum load current, as well as maximum and minimum input voltages. Begin by selecting an inductor value. Once L is know, choose the diode and capacitors.

#### Inductor

Inductor selection depends on input voltage, output voltage, maximum current, switching frequency and availability of inductor values. The following buck circuit equations are useful in choosing the inductor values based on the application. Choose an inductor that does not saturate under the maximum rating load conditions. The magnitude of inductance is selected to maintain a peak to peak ripple current of 30% of the maximum load current.

The peak inductor current is given by:

$$I_{Lpeak} = I_{LAVG} + \frac{\Delta I_{L}}{2}$$

$$I_{LAVG} = \frac{I_{in}}{D}$$

$$D = \frac{V_{O}}{V_{in}}$$

D is the MOSFET turn on ratio

where:

I<sub>L</sub> is the inductor peak-to-peak current ripple and is decided by:

$$\Delta I_{L} = \frac{V_{in} - V_{O}}{L} \times \frac{D}{f_{OSC}} \Longrightarrow L = \frac{(V_{in} - V_{O}) \times D}{\Delta I_{L} \times f_{OSC}}$$

f<sub>OSC</sub> is the switching frequency.

The inductor should be chosen to be able to handle this current and inductor saturation current rating should be greater than  $I_{PEAK}$ .

#### **Diode selection**

When the power switch turns off, the current through the inductor continues to flow. The path for this current is through the diode connected between the switch output and ground. This forward biased diode must has a minimum voltage drop and recovery times. Schottky diode is recommended and it should be able to handle those current. As usual, the reverse voltage rating of the diode should be at least 1.3 times greater than the maximum input voltage, and current rating is greater than the

maximum load current.

## Feedback Resistor Network

An external resistor divider is required to divide the output voltage down to the nominal reference voltage. Current drawn by the resistor network should be limited to maintain the overall converter efficiency. The maximum value of the resistor network is limited by the feedback input bias current and the potential for noise being coupled into the feedback pin. A resistor network in the order of  $100k\Omega$  is recommended. The buck converter output voltage is determined by the following relationship:

$$V_O = V_{REF} \times \left(1 + \frac{R_3}{R_2}\right)$$

where  $V_{REF} = 1.215 V$  as specified.

#### Input capacitor

An input capacitor helps to provide additional current to the power supply as well as smooth input voltage variations in high current switching regulators. When selecting an input capacitor, a low ESR capacitor is required to keep the noise at the IC to a minimum. Ceramic capacitors are preferred, but tantalum or low-ESR electrolytic capacitors may also suffice. Choose an input capacitor who's maximum voltage rating is 1.3 times greater than the maximum input voltage, and who's RMS current rating is equal to one-half of the maximum dc load current. It may be necessary in some designs to add a small valued ceramic type capacitor in parallel with the input capacitor to prevent any ring.

# **Output Capacitor**

The output capacitor acts to smooth the dc output voltage and also provides energy storage. Selection of an output capacitor, with an associated equivalent series resistance (ESR), impacts both the amount of output ripple voltage and stability of the control loop. Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple is estimated to be:

$$\Delta V_{ripple} = \frac{(1-D) \times V_O}{8 \times L \times C_{OUT} \times f_{OSC}^2}$$

For low ESR ceramic capacitors, the output ripple is dominated by the charging or

11

<sup>2</sup>F, No.10, Prosperity RD. II, Science-Based Industrial Park, Hsinchu 300, Taiwan, R.O.C.Tel: 886-3-563-0878Fax: 886-3-563-08798/23/2006REV:1.1Email: service@aimtron.com.tw

discharging of the output capacitor.

In the case of low-ESR electrolytic capacitors, Output ripple voltage drop caused by the switching current through the ESR of the output capacitor. The output ripple is estimated as:

$V_{\rm RIPPLE} \cong \Delta I_{\rm L} \times R_{\rm ESR}$

Impacting frequency stability of the overall control loop, the output capacitance, in conjunction with the inductor, creates a double pole inside the feedback loop. In addition the capacitance and the ESR value create a zero. These frequency response effects together with the internal frequency compensation circuitry of AT1799 modify the gain and phase shift of the closed loop system.

# Compensation

The step-down loop can be compensated by adjusting the external components connected to the COMP pin. The COMP pin is connected to the output of the internal trans-conductance error amplifier. The compensation capacitor adjusts the low frequency gain , and the series resistor value adjusts the high frequency gain. A series capacitor-resistor combination sets a pole-zero combination to control the characteristics of the control system. The system has 2 poles and one zero of importance, 2 poles consist of compensation capacitor and output capacitor. One zero is produced by the compensation capacitor and the compensation resistor.

If electrolytic capacitor with relatively high ESR is used, the zero due to the capacitance and ESR of the output capacitor can be compensated by a third pole set by the compensation resistor and another compensation capacitor connected form COMP pin to ground.

#### PCB layout guidelines

Careful printed circuit layout is extremely important to avoid causing parasitical capacitance and line inductance. The following layout guidelines are recommended to achieve optimum performance.

- Please the buck converter diode and inductor close to the SW pin and no via.

- Please ceramic bypass capacitors near the input pin.

- Locate all feedback resistive dividers as close to their respective feedback pins as possible.

- Use wide traces and trace length is short as possible.

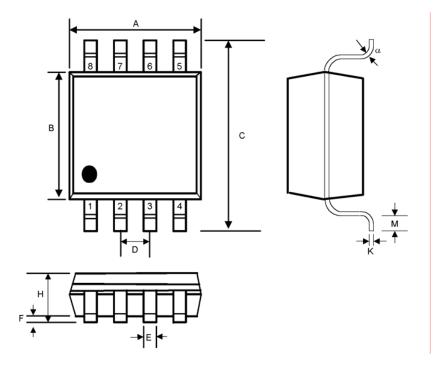

# Outline 8-pin SOP

| SYMBOL | INCHES          |       | MILLIMETERS     |                | NOTES |  |

|--------|-----------------|-------|-----------------|----------------|-------|--|

| SIMBOL | MIN             | MAX   | MIN             | MAX            | NOTES |  |

| А      | 0.188           | 0.197 | 4.80            | 5.00           | -     |  |

| В      | 0.149           | 0.158 | 3.80            | 4.00           | -     |  |

| С      | 0.228           | 0.244 | 5.80            | 6.20           | -     |  |

| D      | 0.050 BSC       |       | 1.27 BSC        |                | -     |  |

| Е      | 0.013           | 0.020 | 0.33            | 0.51           | -     |  |

| F      | 0.004           | 0.010 | 0.10            | 0.25           | -     |  |

| Н      | 0.053           | 0.069 | 1.35            | 1.75           | -     |  |

| J      | 0.011           | 0.019 | 0.28            | 0.48           |       |  |

| K      | 0.007           | 0.010 | 0.19            | 0.25           |       |  |

| М      | 0.016           | 0.050 | 0.40            | 1.27           |       |  |

| e1     | 45 <sup>0</sup> |       | 45 <sup>0</sup> |                |       |  |

| α      | 00              | $8^0$ | $0^{0}$         | 8 <sup>0</sup> | -     |  |