# Application Note: MLX90255 Demo Board

The demo board described in this document facilitates the evaluation of the MLX90255xx Linear Optical Arrays. The board provides the necessary timing and clock signals to support both the on-board imaging device or an externally connected sensor. The designer is then free to investigate the properties and performance of the device without having to design and construct an external support circuitry. A regulated DC power supply between 6 and 10V is the only input signal. An oscilloscope is required for observation and analysis of the output signals.

## Features and Benefits

- 128 x 1 Sensor-Element Organization (1 Not Connected, 1 dummy, 128 real, 1 dummy, 1 Dark Pixel)

- 385 DPI sensor pitch

- High Linearity and Uniformity for 256 Gray-Scale

- High Sensitivity: 1.7V @ 10µW/cm 2 @ 0.7ms integration time

- Special Gain Compensation for use with single LED light source

- Output Referenced to Ground

- Single 5V Supply

- Operation to 1MHz

## Applications

- position Sensing

- electrical Power Assist Steering (EPAS)

- spectrometer Applications

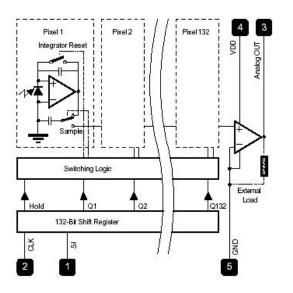

## **Functional Diagram**

## **General Description**

The MLX90255xx linear sensor array consists of a 128 x 1 array of photodiodes, associated charge amplifier circuitry and a pixel data-hold function that provides simultaneous integration start and stop times for all pixels. The pixels measure 200µm (H) by 66 µm (W) and there is 8 µm spacing between pixels. Operation is simplified by internal control logic that requires only a Serial Input (SI) pulse and a clock signal. The sensor consists of 128 photodiodes arranged in a linear array. Light energy falling on a photodiode generates photocurrent, which is integrated by the active integration circuitry associated with that pixel. During the integration period, a sampling capacitor connects to the output of the integrator through an analog switch. The amount of charge accumulated at each pixel is directly proportional to the light intensity and the integration time. The output and reset of the integrators is controlled by a 132-bit shift register and reset logic. An output cycle is initiated by clocking in a logic 1 on SI. This causes all 132 sampling capacitors to be disconnected from their respective integrators and starts an integrator-reset period.

### MLX90255 Pin Description

| Pin Number |      | Symbol | Description                                                                                     |  |

|------------|------|--------|-------------------------------------------------------------------------------------------------|--|

| SMD8       | GLP5 |        |                                                                                                 |  |

| 1          | 1    | SI     | Serial Input. SI defines the end of the integration time and the start of the data out sequence |  |

| 2          | 2    | CLK    | Clock. The clock controls the charge transfer, pixel output and reset (together with SI)        |  |

| 3          | 3    | A0     | Analog output                                                                                   |  |

| 4          | 4    | VDD    | Supply Voltage, for both analog and digital circuits                                            |  |

| 5, 6, 7, 8 | 5    | GND    | Ground. All GND pins are referenced to the substrate.                                           |  |

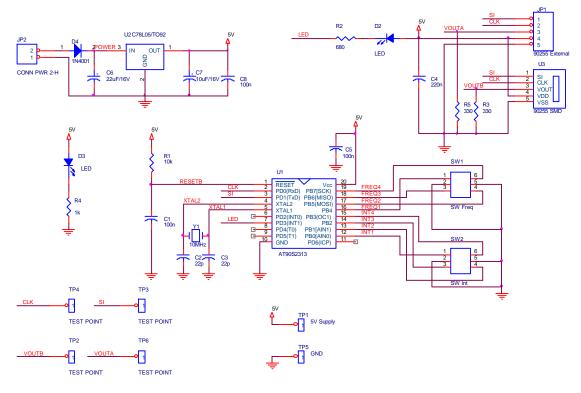

## **Schematics**

## **Functional Description**

The demo board mainly consists of the following blocks:

- 5V regulator with a power-on indication LED

- general purpose microcontroller with reset circuitry and crystal oscillator

- 2 rotary DIL switches for changing settings

- a LED which lights up if the chosen settings

are out of the device specification

- 1 on-board MLX90255 sensor (B) and a 5pins connector for an external device (A)

- test terminals for all important signals The different blocks can easily be found in the schematic diagram.

The main purpose of the demonstration board is to provide a specified clock frequency and an

appropriate SI pulse to the optical array. The required pull-down resistors are also foreseen on the board. All important signals (SI, CLK, VOUT, 5V and GND) are connected to test terminals, which makes it easy to visualize them on an oscilloscope. One sensor in a SMD package is soldered on the PCB (called B) while an external sensor can be connected to the 5pins connector row (upper right corner) (called A). Both output signals are connected to test terminals, called respectively VOUTB and VOUTA.

An external regulated DC power supply, with an output voltage between 6 and 10V, needs to be connected to the screw connector in the upper left corner of the PCB. A regular 9V battery is also possible. (Mind the sign!) As soon as the power supply is switched on, a LED lights up and the micro controller starts generating the CLK and SI signals with the selected frequency and integration time.

The frequency of the signal CLK can be chosen with the rotary DIL switch on the right. The frequencies corresponding to the 16 positions of this switch are shown in the following table.

| Position | CLK frequency |  |

|----------|---------------|--|

| 0        | 36kHz         |  |

| 1        | 64kHz         |  |

| 2        | 77kHz         |  |

| 3        | 93kHz         |  |

| 4        | 112kHz        |  |

| 5        | 141kHz        |  |

| 6        | 170kHz        |  |

| 7        | 214kHz        |  |

| 8        | 284kHz        |  |

| 9        | 345kHz        |  |

| A        | 435kHz        |  |

| В        | 588kHz        |  |

| С        | 909kHz        |  |

| D        | 1.0MHz        |  |

| E        | 1.25MHz       |  |

| F        | 1.67MHz       |  |

Positions 0, E and F correspond to frequencies that are outside the device specification. Lighting up a second LED indicates selecting one of them.

For each SI pulse, 133 CLK pulses are

generated with the selected frequency, and after them the CLK line is pulled low until the next SI pulse. See further in this document for the correct timings.

The light integration time can be selected with the other rotary DIL switch. Again 16 positions are possible, however now there is no one-toone relation with the corresponding integration times. Actually the switch specifies a time which starts only after the 133<sup>rd</sup> CLK pulse. As the integration time already starts after the 18<sup>th</sup> pulse (see device specification), the total integration time also depends on the selected frequency. The following table shows for each position (of the 'integration time switch') the minimal and the maximal integration time, corresponding to respectively the maximal and the minimal CLK frequency.

| Position | Total Integration Time |         |  |

|----------|------------------------|---------|--|

|          | Minimal                | Maximal |  |

| 0        | 79us                   | 3.17ms  |  |

| 1        | 230us                  | 3.33ms  |  |

| 2        | 380us                  | 3.48ms  |  |

| 3        | 682us                  | 3.77ms  |  |

| 4        | 985us                  | 4.09ms  |  |

| 5        | 1.30ms                 | 4.40ms  |  |

| 6        | 2.50ms                 | 5.60ms  |  |

| 7        | 3.10ms                 | 6.20ms  |  |

| 8        | 3.85ms                 | 6.95ms  |  |

| 9        | 4.60ms                 | 7.70ms  |  |

| А        | 6.10ms                 | 9.15ms  |  |

| В        | 7.7ms                  | 10.7s   |  |

| С        | 9.15ms                 | 12.5ms  |  |

| D        | 10.5ms                 | 10.5ms  |  |

| E        | 15ms                   | 15ms    |  |

| F        | 20ms                   | 20ms    |  |

The analog output voltage is directly proportional to the light intensity and the integration time up to the devices saturation level (3V typical). The response of a pixel can be described with the following formula:

$VOUT = PR^*P_{light} + offset + PR_{error}^*P_{light} + DC$

where DC means the dark current.

The proportionality constant PR is the responsivity of the device given in  $(V^*cm2/\mu W^*sec)$ . Responsivity is wavelength

dependent. For the MLX90255 the responsivity will peak at about 770nm.

#### Bill of Materials for the demo

- an MLX90255 demo board with on-board sensor device

- optionally an external device connected to the 5 pins header

- a regulated power supply (6...10VDC)

- an oscilloscope

#### Operation

To operate the demo board the following steps are necessary:

- apply 6...10VDC to the board

- connect an oscilloscope probe to the VOUTA or VOUTB pin (depending on the actual device of interest) and the scope ground to the GND terminal

- connect a second oscilloscope probe to the SI terminal, and use this channel as a triggering input

- select the appropriate integration time and CLK frequency. If the amount of impinging energy is relatively large, a short integration time is necessary to prevent complete saturation of the output.

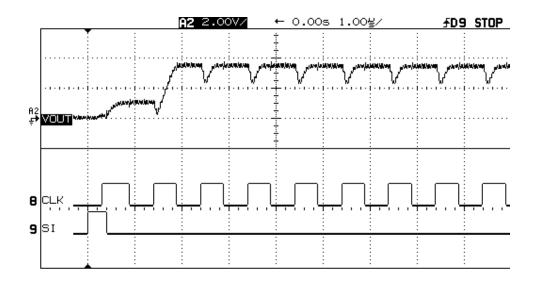

#### Timing diagram

The first scan after power up is incorrect: the chip needs 1 SI pulse and 133 CLK pulses to initialize the complete device. The second SI pulse is valid and starts the integration time after 18 clock pulses (see device specification). A next SI pulse ends the integration time, and the pixel values are scanned out to the output pin at the rate of CLK.

Note that it is perfectly possible to stop the CLK pulses after the 133<sup>rd</sup>. After each SI pulse, 133 CLK pulses are necessary however.

When an SI pulse is given the chip always does 2 things:

- It clocks out the former data of the pixels to the OUT pin, at the rate of the CLK signal.

- The device is in a reset state until the falling edge of the 18<sup>th</sup> CLK pulse. At that moment the integration time starts.

FD9 STOP

2<sup>nd</sup> SI pulse

P2

2.00V/

← 0.005

500½/

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Integration Time

Some oscilloscope screenshots to make it even more clear.

1st SI pulse

BICLK

9 SI

In the first figure, one can see clearly a first SI pulse, followed by 133 CLK pulses. After the selected integration time, a next SI pulse is generated, again accompanied with 133 CLK pulses. Note that the CLK pulses have stopped. During the CLK pulses, the pixel values of the former integration time are clocked out. This screenshot repeats itself continously for every new scan.

Note that this figure does not show the initialisation scan (very first scan), as this is only necessary after Power Up. These pictures were taken during continuous operation.

The second screenshot shows a zoom of the first one. Here the SI pulse together with the first CLK pulses is clearly visible. The first pixel has a low value, as this is an unconnected pixel. (The last one is connected, but covered with metal.)

#### Note

In a real-life application two different timing solutions are possible, depending on the overall system specification and performance.

- 1. Continuous read-out. SI pulses are generated in a regular and controlled time frame. For each SI pulse, the integration time is controlled and the data at the output of the sensor is valid. This requires a highspeed microcontroller, as it has to handle this high throughput of data. Continuous read-out can also be used if the algorithm requires only a very limited amount of calculation.

- 2. 'Burst-like' read-out. If the application needs a long time for data manipulation, the system cannot control the integration time for each SI pulse. SI pulses aren't generated in a regular time frame corresponding to the necessary integration time. The first SI pulse after a longer calculation intensive part, results in useless data as the integration time was not precisely timed, so the sensor will be completely saturated. After the desired integration time, a second SI pulse is generated, and the valid data is clocked out.