#### **Features**

- Single Supply Voltage, Range 2.7V to 3.6V

- . Single Supply for Read and Write

- Fast Read Access Time 55 ns

- Internal Program Control and Timer

- 8K bytes Boot Block With Lockout

- Fast Erase Cycle Time 10 seconds

- Byte By Byte Programming 30 μs/Byte typical

- Hardware Data Protection

- DATA Polling For End Of Program Detection

- Low Power Dissipation

- 25 mA Active Current

- 50 μA CMOS Standby Current

- Typical 10,000 Write Cycles

#### Description

The AT49(H)BV010 and the AT49(H)LV010 are 3-volt-only, 1-megabit Flash memories organized as 131,072 words of 8 bits each. Manufactured with Atmel's advanced nonvolatile CMOS technology, the devices offer access times to 55 ns with power dissipation of just 90 mW over the commercial temperature range. When the devices are deselected, the CMOS standby current is less than 50  $\mu$ A.

To allow for simple in-system reprogrammability, the AT49(H)BV/(H)LV010 does not require high input voltages for programming. Three-volt-only commands determine the read and programming operation of the device. Reading data out of the device is similar to reading from an EPROM. Reprogramming the AT49(H)BV/(H)LV010 is performed by erasing the entire 1 megabit of memory and then programming on a byte by byte basis. The typical byte programming time is a fast 30  $\mu s$ . The end of a program cycle can be optionally detected by the DATA polling feature. Once the end of a byte program cycle has been detected, a new access for a read or program can begin. The typical number of program and erase cycles is in excess of 10,000 cycles.

(continued)

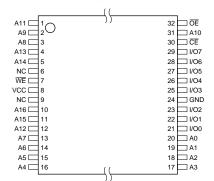

#### **Pin Configurations**

| Pin Name    | Function            |

|-------------|---------------------|

| A0 - A16    | Addresses           |

| CE          | Chip Enable         |

| ŌĒ          | Output Enable       |

| WE          | Write Enable        |

| I/O0 - I/O7 | Data Inputs/Outputs |

| NC          | No Connect          |

**PLCC Top View**

TSOP Top View **Type 1**

1-Megabit (128K x 8) Single 2.7-volt *Battery-Voltage*<sup>™</sup> Flash Memory

AT49BV010 AT49HBV010 AT49LV010 AT49HLV010

0677B-A-9/97

The optional 8K bytes boot block section includes a reprogramming write lock out feature to provide data integrity. The boot sector is designed to contain user secure code,

and when the feature is enabled, the boot sector is permanently protected from being reprogrammed.

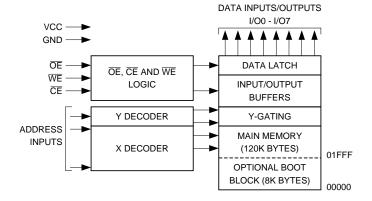

#### **Block Diagram**

#### **Device Operation**

**READ:** The AT49(H)BV/(H)LV010 is accessed like an EPROM. When  $\overline{CE}$  and  $\overline{OE}$  are low and  $\overline{WE}$  is high, the data stored at the memory location determined by the address pins is asserted on the outputs. The outputs are put in the high impedance state whenever  $\overline{CE}$  or  $\overline{OE}$  is high. This dual-line control gives designers flexibility in preventing bus contention.

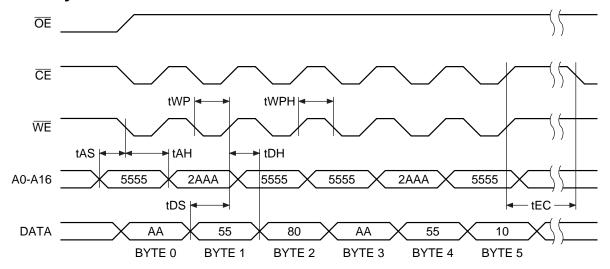

**ERASURE:** Before a byte can be reprogrammed, the 128K bytes memory array (or 120K bytes if the boot block featured is used) must be erased. The erased state of the memory bits is a logical "1". The entire device can be erased at one time by using a 6-byte software code. The software chip erase code consists of 6-byte load commands to specific address locations with a specific data pattern (please refer to the Chip Erase Cycle Waveforms).

After the software chip erase has been initiated, the device will internally time the erase operation so that no external clocks are required. The maximum time needed to erase the whole chip is  $t_{\rm EC}$ . If the boot block lockout feature has been enabled, the data in the boot sector will not be erased.

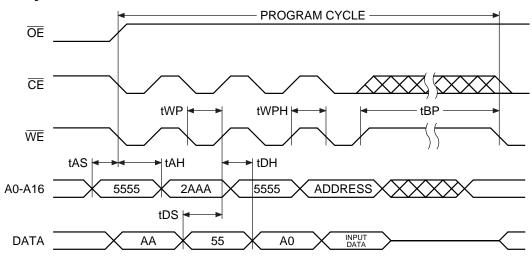

BYTE PROGRAMMING: Once the memory array is erased, the device is programmed (to a logical "0") on a byte-by-byte basis. Please note that a data "0" cannot be programmed back to a "1"; only erase operations can convert "0"s to "1"s. Programming is accomplished via the internal device command register and is a 4 bus cycle operation (please refer to the Command Definitions table). The device will automatically generate the required internal program pulses.

The program cycle has addresses latched on the falling edge of  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ , whichever occurs last, and the data latched on the rising edge of  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ , whichever occurs first. Programming is completed after the specified  $t_{\text{BP}}$  cycle time. The  $\overline{\text{DATA}}$  polling feature may also be used to indicate the end of a program cycle.

BOOT BLOCK PROGRAMMING LOCKOUT: The device has one designated block that has a programming lockout feature. This feature prevents programming of data in the designated block once the feature has been enabled. The size of the block is 8K bytes. This block, referred to as the boot block, can contain secure code that is used to bring up the system. Enabling the lockout feature will allow the boot code to stay in the device while data in the rest of the device is updated. This feature does not have to be activated; the boot block's usage as a write protected region is optional to the user. The address range of the boot block is 00000H to 01FFFH.

Once the feature is enabled, the data in the boot block can no longer be erased or programmed. Data in the main memory block can still be changed through the regular programming method. To activate the lockout feature, a series of six program commands to specific addresses with specific data must be performed. Please refer to the Command Definitions table.

BOOT BLOCK LOCKOUT DETECTION: A software method is available to determine if programming of the boot block section is locked out. When the device is in the software product identification mode (see Software Product Identification Entry and Exit sections) a read from address location 00002H will show if programming the boot block is locked out. If the data on I/O0 is low, the boot block can be programmed; if the data on I/O0 is high, the program lock-out feature has been activated and the block cannot be programmed. The software product identification code should be used to return to standard operation.

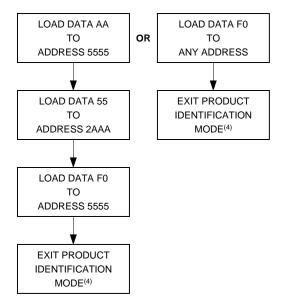

**PRODUCT IDENTIFICATION:** The product identification mode identifies the device and manufacturer as Atmel. It may be accessed by hardware or software operation. The hardware operation mode can be used by an external programmer to identify the correct programming algorithm for the Atmel product.

For details, see Operating Modes (for hardware operation) or Software Product Identification. The manufacturer and device code is the same for both modes.

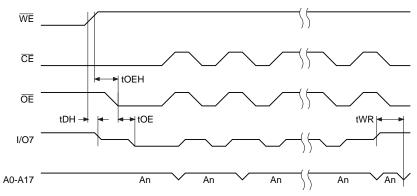

DATA POLLING: The AT49(H)BV/(H)LV010 features DATA polling to indicate the end of a program cycle. During a program cycle an attempted read of the last byte loaded will result in the complement of the loaded data on I/O7. Once the program cycle has been completed, true data is valid on all outputs and the next cycle may begin. DATA polling may begin at any time during the program cycle.

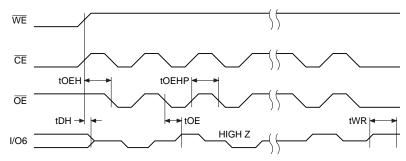

TOGGLE BIT: In addition to DATA polling the AT49(H)BV/(H)LV010 provides another method for determining the end of a program or erase cycle. During a program or erase operation, successive attempts to read data from the device will result in I/O6 toggling between one and

zero. Once the program cycle has completed, I/O6 will stop toggling and valid data will be read. Examining the toggle bit may begin at any time during a program cycle.

**HARDWARE DATA PROTECTION:** Hardware features protect against inadvertent programs to the AT49(H)BV/(H)LV010 in the following ways: (a)  $V_{CC}$  sense: if  $V_{CC}$  is below 1.8V (typical), the program function is inhibited. (b) Program inhibit: holding any one of  $\overline{OE}$  low,  $\overline{CE}$  high or  $\overline{WE}$  high inhibits program cycles. (c) Noise filter: Pulses of less than 15 ns (typical) on the  $\overline{WE}$  or  $\overline{CE}$  inputs will not initiate a program cycle.

**INPUT LEVELS:** While operating with a 2.7V to 3.6V power supply, the address inputs and control inputs ( $\overline{\text{OE}}$ ,  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$ ) may be driven from 0 to 5.5V without adversely affecting the operation of the device. The I/O lines can only be driven from 0 to  $V_{\text{CC}}$  + 0.6V.

#### **Command Definition (in Hex)**

| Command<br>Sequence                  |   |      | Bus<br>cle       |      | Bus<br>cle |      | Bus<br>cle |      | Bus<br>cle      |      | Bus<br>cle |      | Bus<br>cle |

|--------------------------------------|---|------|------------------|------|------------|------|------------|------|-----------------|------|------------|------|------------|

|                                      |   | Addr | Data             | Addr | Data       | Addr | Data       | Addr | Data            | Addr | Data       | Addr | Data       |

| Read                                 | 1 | Addr | D <sub>OUT</sub> |      |            |      |            |      |                 |      |            |      |            |

| Chip Erase                           | 6 | 5555 | AA               | 2AAA | 55         | 5555 | 80         | 5555 | AA              | 2AAA | 55         | 5555 | 10         |

| Byte<br>Program                      | 4 | 5555 | AA               | 2AAA | 55         | 5555 | A0         | Addr | D <sub>IN</sub> |      |            |      |            |

| Boot Block<br>Lockout <sup>(1)</sup> | 6 | 5555 | AA               | 2AAA | 55         | 5555 | 80         | 5555 | AA              | 2AAA | 55         | 5555 | 40         |

| Product ID<br>Entry                  | 3 | 5555 | AA               | 2AAA | 55         | 5555 | 90         |      |                 |      |            |      |            |

| Product ID<br>Exit <sup>(2)</sup>    | 3 | 5555 | AA               | 2AAA | 55         | 5555 | F0         |      |                 |      |            |      |            |

| Product ID<br>Exit <sup>(2)</sup>    | 1 | XXXX | F0               |      |            |      |            |      |                 |      |            |      |            |

Notes: 1. The 8K byte boot sector has the address range 00000H to 01FFFH.

2. Either one of the Product ID exit commands can be used.

#### **Absolute Maximum Ratings\***

| Temperature Under Bias55°C to +125°C                                        |

|-----------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                           |

| All Input Voltages (including NC Pins) with Respect to Ground0.6V to +6.25V |

| All Output Voltages with Respect to Ground0.6V to V <sub>CC</sub> + 0.6V    |

| Voltage on $\overline{\text{OE}}$ with Respect to Ground0.6V to +13.5V      |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC and AC Operating Range**

|                              |           | AT49HLV<br>010-55 | AT49HBV/<br>HLV010-70 | AT49HBV/<br>HLV010-90 | AT49BV/<br>LV010-12 | AT49BV010-15 |

|------------------------------|-----------|-------------------|-----------------------|-----------------------|---------------------|--------------|

| Operating                    | Com.      | 0°C - 70°C        | 0°C - 70°C            | 0°C - 70°C            | 0°C - 70°C          | 0°C - 70°C   |

| Temperature (Case)           | Ind.      | -40°C - 85°C      | -40°C - 85°C          | -40°C - 85°C          | -40°C - 85°C        | -40°C - 85°C |

| V <sub>CC</sub> Power Supply | AT49LV010 | 3.0V to 3.6V      | 3.0V to 3.6V          | 3.0V to 3.6V          | 3.0V to 3.6V        | N/A          |

|                              | AT49BV010 | N/A               | 2.7V to 3.6V          | 2.7V to 3.6V          | 2.7V to 3.6V        | 2.7V to 3.6V |

## **Operating Modes**

| Mode                    | CE              | ŌĒ               | WE              | Ai                                                                             | I/O                              |

|-------------------------|-----------------|------------------|-----------------|--------------------------------------------------------------------------------|----------------------------------|

| Read                    | V <sub>IL</sub> | V <sub>IL</sub>  | V <sub>IH</sub> | Ai                                                                             | D <sub>OUT</sub>                 |

| Program <sup>(2)</sup>  | V <sub>IL</sub> | V <sub>IH</sub>  | V <sub>IL</sub> | Ai                                                                             | D <sub>IN</sub>                  |

| Standby/Write Inhibit   | V <sub>IH</sub> | X <sup>(1)</sup> | Х               | Х                                                                              | High Z                           |

| Program Inhibit         | Х               | Х                | V <sub>IH</sub> |                                                                                |                                  |

| Program Inhibit         | Х               | V <sub>IL</sub>  | Х               |                                                                                |                                  |

| Output Disable          | Х               | V <sub>IH</sub>  | Х               |                                                                                | High Z                           |

| Product Identification  |                 |                  |                 |                                                                                |                                  |

| Hardware                | V <sub>IL</sub> | V <sub>IL</sub>  | V <sub>IH</sub> | A1 - A16 = V <sub>IL</sub> , A9 = V <sub>H</sub> , (3)<br>A0 = V <sub>IL</sub> | Manufacturer Code <sup>(4)</sup> |

|                         |                 |                  |                 | A1 - A16 = V <sub>IL</sub> , A9 = V <sub>H</sub> , (3)<br>A0 = V <sub>IH</sub> | Device Code <sup>(4)</sup>       |

| Software <sup>(5)</sup> |                 |                  |                 | A0 = V <sub>IL</sub> , A1 - A16 = V <sub>IL</sub>                              | Manufacturer Code <sup>(4)</sup> |

|                         |                 |                  |                 | A0 = V <sub>IH</sub> , A1 - A16 = V <sub>IL</sub>                              | Device Code <sup>(4)</sup>       |

Notes: 1. X can be  $V_{IL}$  or  $V_{IH}$ .

2. Refer to AC Programming Waveforms.

3.  $V_H = 12.0V \pm 0.5V$ .

4. Manufacturer Code: 1FH, Device Code: 17H.

5. See details under Software Product Identification Entry/Exit.

#### **DC Characteristics**

| Symbol                         | Parameter                            | Condition                                                                     | Min | Max  | Units |

|--------------------------------|--------------------------------------|-------------------------------------------------------------------------------|-----|------|-------|

| I <sub>LI</sub>                | Input Load Current                   | V <sub>IN</sub> = 0V to V <sub>CC</sub>                                       |     | 10   | μΑ    |

| I <sub>LO</sub>                | Output Leakage Current               | $V_{I/O} = 0V \text{ to } V_{CC}$                                             |     | 10   | μΑ    |

| I <sub>SB1</sub>               | V <sub>CC</sub> Standby Current CMOS | $\overline{\text{CE}} = \text{V}_{\text{CC}} - 0.3 \text{V to V}_{\text{CC}}$ |     | 50   | μΑ    |

| I <sub>SB2</sub>               | V <sub>CC</sub> Standby Current TTL  | $\overline{\text{CE}}$ = 2.0V to V <sub>CC</sub>                              |     | 1    | mA    |

| I <sub>CC</sub> <sup>(1)</sup> | V <sub>CC</sub> Active Current       | f = 5 MHz; I <sub>OUT</sub> = 0 mA                                            |     | 25   | mA    |

| V <sub>IL</sub>                | Input Low Voltage                    |                                                                               |     | 0.6  | V     |

| V <sub>IH</sub>                | Input High Voltage                   |                                                                               | 2.0 |      | V     |

| V <sub>OL</sub>                | Output Low Voltage                   | I <sub>OL</sub> = 2.1 mA                                                      |     | 0.45 | V     |

| V <sub>OH</sub>                | Output High Voltage                  | $I_{OH} = -100  \mu A;  V_{CC} = 3.0 V$                                       | 2.4 |      | V     |

Note: 1. In the erase mode,  $I_{CC}$  is 50 mA.

## 4 AT49(H)BV/(H)LV010

#### **AC Read Characteristics**

|                                |                                                                    | AT49 | 9HLV<br>9-55 |     | HBV/<br>10-70 | _   | HBV/<br>10-90 |     | 9BV/<br>0-12 | AT49E<br>1 | 3V010-<br>5 |       |

|--------------------------------|--------------------------------------------------------------------|------|--------------|-----|---------------|-----|---------------|-----|--------------|------------|-------------|-------|

| Symbol                         | Parameter                                                          | Min  | Max          | Min | Max           | Min | Max           | Min | Max          | Min        | Max         | Units |

| t <sub>ACC</sub>               | Address to Output Delay                                            |      | 55           |     | 70            |     | 90            |     | 120          |            | 150         | ns    |

| t <sub>CE</sub> <sup>(1)</sup> | CE to Output Delay                                                 |      | 55           |     | 70            |     | 90            |     | 120          |            | 150         | ns    |

| t <sub>OE</sub> (2)            | OE to Output Delay                                                 |      | 30           |     | 35            |     | 40            |     | 50           | 0          | 70          | ns    |

| t <sub>DF</sub> (3, 4)         | CE or OE to Output<br>Float                                        | 0    | 25           | 0   | 25            | 0   | 25            | 0   | 30           | 0          | 40          | ns    |

| t <sub>OH</sub>                | Output Hold from OE,<br>CE or Address,<br>whichever occurred first | 0    |              | 0   |               | 0   |               | 0   |              | 0          |             | ns    |

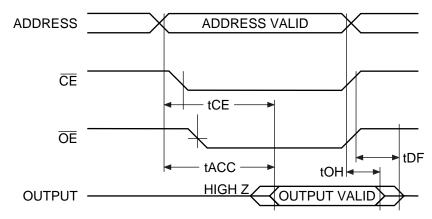

### AC Read Waveforms<sup>(1)(2)(3)(4)</sup>

- Notes: 1.  $\overline{\text{CE}}$  may be delayed up to  $t_{\text{ACC}}$   $t_{\text{CE}}$  after the address transition without impact on  $t_{\text{ACC}}$ .

- 2.  $\overline{\text{OE}}$  may be delayed up to  $t_{\text{CE}}$   $t_{\text{OE}}$  after the falling edge of  $\overline{\text{CE}}$  without impact on  $t_{\text{CE}}$  or by  $t_{\text{ACC}}$   $t_{\text{OE}}$  after an address change without impace on t<sub>ACC</sub>.

- 3.  $t_{DF}$  is specified from  $\overline{OE}$  or  $\overline{CE}$  whichever occurs frist (CL 5 pF).

- 4. This parameter is characterized and is not 100% tested.

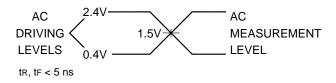

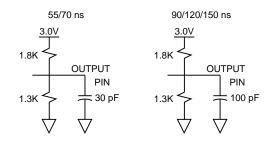

#### **Input Test Waveforms and Measurement Level**

#### **Output Test Load**

#### Pin Capacitance (f = 1 MHz, T = $25^{\circ}$ C)<sup>(1)</sup>

|                  | Тур | Max | Units | Conditions            |

|------------------|-----|-----|-------|-----------------------|

| C <sub>IN</sub>  | 4   | 6   | pF    | $V_{IN} = 0V$         |

| C <sub>OUT</sub> | 8   | 12  | pF    | V <sub>OUT</sub> = 0V |

1. This parameter is characterized and is not 100% tested. Note:

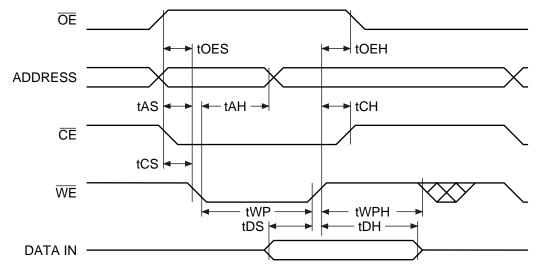

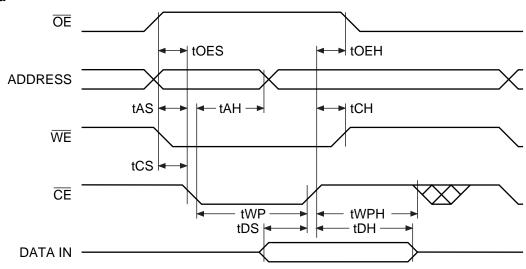

## **AC Byte Load Characteristics**

| Symbol                             | Parameter                     | Min | Max | Units |

|------------------------------------|-------------------------------|-----|-----|-------|

| t <sub>AS</sub> , t <sub>OES</sub> | Address, OE Set-up Time       | 0   |     | ns    |

| t <sub>AH</sub>                    | Address Hold Time             | 100 |     | ns    |

| t <sub>CS</sub>                    | Chip Select Set-up Time       | 0   |     | ns    |

| t <sub>CH</sub>                    | Chip Select Hold Time         | 0   |     | ns    |

| t <sub>WP</sub>                    | Write Pulse Width (WE or CE)  | 200 |     | ns    |

| t <sub>DS</sub>                    | Data Set-up Time              | 100 |     | ns    |

| t <sub>DH</sub> , t <sub>OEH</sub> | Data, <del>OE</del> Hold Time | 0   |     | ns    |

| t <sub>WPH</sub>                   | Write Pulse Width High        | 200 |     | ns    |

## **AC Byte Load Waveforms**

### **WE** Controlled

#### **CE** Controlled

# AT49(H)BV/(H)LV010

## **Program Cycle Characteristics**

| Symbol           | Parameter              | Min | Тур | Max | Units   |

|------------------|------------------------|-----|-----|-----|---------|

| t <sub>BP</sub>  | Byte Programming Time  |     | 30  |     | μs      |

| t <sub>AS</sub>  | Address Set-up Time    | 0   |     |     | ns      |

| t <sub>AH</sub>  | Address Hold Time      | 100 |     |     | ns      |

| t <sub>DS</sub>  | Data Set-up Time       | 100 |     |     | ns      |

| t <sub>DH</sub>  | Data Hold Time         | 0   |     |     | ns      |

| t <sub>WP</sub>  | Write Pulse Width      | 200 |     |     | ns      |

| t <sub>WPH</sub> | Write Pulse Width High | 200 |     |     | ns      |

| t <sub>EC</sub>  | Erase Cycle Time       |     |     | 10  | seconds |

## **Program Cycle Waveforms**

## **Chip Erase Cycle Waveforms**

Note:  $\overline{OE}$  must be high only when  $\overline{WE}$  and  $\overline{CE}$  are both low.

## **Data** Polling Characteristics<sup>(1)</sup>

| Symbol           | Parameter                         | Min | Тур | Max | Units |

|------------------|-----------------------------------|-----|-----|-----|-------|

| t <sub>DH</sub>  | Data Hold Time                    | 0   |     |     | ns    |

| t <sub>OEH</sub> | OE Hold Time                      | 10  |     |     | ns    |

| t <sub>OE</sub>  | OE to Output Delay <sup>(2)</sup> |     |     |     | ns    |

| t <sub>WR</sub>  | Write Recovery Time               | 0   |     |     | ns    |

Notes: 1. These parameters are characterized and not 100% tested.

2. See  $t_{OE}$  spec in AC Read Characteristics.

#### **Data Polling Waveforms**

## Toggle Bit Characteristics<sup>(1)</sup>

| Symbol            | Parameter                         | Min | Тур | Max | Units |

|-------------------|-----------------------------------|-----|-----|-----|-------|

| t <sub>DH</sub>   | Data Hold Time                    | 0   |     |     | ns    |

| t <sub>OEH</sub>  | OE Hold Time                      | 10  |     |     | ns    |

| t <sub>OE</sub>   | OE to Output Delay <sup>(2)</sup> |     |     |     | ns    |

| t <sub>OEHP</sub> | OE High Pulse                     | 150 |     |     | ns    |

| t <sub>WR</sub>   | Write Recovery Time               | 0   |     |     | ns    |

Notes: 1. These parameters are characterized and not 100% tested.

2. See  $t_{\text{OE}}$  spec in AC Read Characteristics.

## Toggle Bit Waveforms<sup>(1)(2)(3)</sup>

Notes: 1. Toggling either  $\overline{OE}$  or  $\overline{CE}$  or both  $\overline{OE}$  and  $\overline{CE}$  will operate toggle bit. The t<sub>OEHP</sub> specification must be met by the toggling input(s).

- 2. Beginning and ending state of I/O6 will vary.

- 3. Any address location may be used but the address should not vary.

## 8 AT49(H)BV/(H)LV010

### **Software Product** Identification Entry<sup>(1)</sup>

#### **Software Product** Identification Exit<sup>(1)</sup>

- Notes: 1. Data Format: I/O7 I/O0 (Hex); Address Format: A14 - A0 (Hex).

- 2. A1 A16 =  $V_{IL}$ . Manufacture Code is read for  $A0 = V_{IL}$ ; Device Code is read for  $A0 = V_{IH}$ .

- 3. The device does note remain in identification mode if powered down.

- The device returns to standard operation mode.

- Manufacturers Code: 1FH Device Code: 17H.

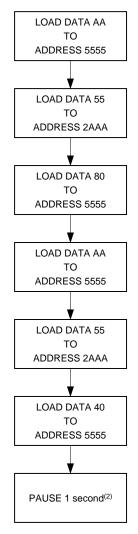

#### **Boot Block Lockout Feature Enable Algorithm**<sup>(1)</sup>

Notes: Data Format: I/O7 - I/O0 (Hex); Address Format: A14 - A0 (Hex).

Boot block lockout feature enabled.

## **Ordering Information**<sup>(1)</sup>

| t <sub>ACC</sub><br>(ns) | I <sub>CC</sub> (mA) |         |                                    |            |                              |

|--------------------------|----------------------|---------|------------------------------------|------------|------------------------------|

|                          | Active               | Standby | Ordering Code                      | Package    | Operation Range              |

| 70                       | 25                   | 0.05    | AT49HBV010-70JC<br>AT49HBV010-70TC | 32J<br>32T | Commercial<br>(0°C - 70°C)   |

|                          | 25                   | 0.05    | AT49HBV010-70JI<br>AT49HBV010-70TI | 32J<br>32T | Industrial<br>(-40°C - 85°C) |

| 90                       | 25                   | 0.05    | AT49HBV010-90JC<br>AT49HBV010-90TC | 32J<br>32T | Commercial<br>(0°C - 70°C)   |

|                          | 25                   | 0.05    | AT49HBV010-90JI<br>AT49HBV010-90TI | 32J<br>32T | Industrial<br>(-40°C - 85°C) |

| 120                      | 25                   | 0.05    | AT49BV010-12JC<br>AT49BV010-12TC   | 32J<br>32T | Commercial<br>(0°C - 70°C)   |

|                          | 25                   | 0.05    | AT49BV010-12JI<br>AT49BV010-12TI   | 32J<br>32T | Industrial<br>(-40°C - 85°C) |

| 150                      | 25                   | 0.05    | AT49BV010-15JC<br>AT49BV010-15TC   | 32J<br>32T | Commercial<br>(0°C - 70°C)   |

|                          | 25                   | 0.05    | AT49BV010-15JI<br>AT49BV010-15TI   | 32J<br>32T | Industrial<br>(-40°C - 85°C) |

Note: 1. The 49(H)BV/(H)LV010 has as optional boot block feature. The part number shown in the Ordering Information table is for devices with the boot block in the lower address range (i.e., 00000H to 01FFFH). Users requiring the boot block to be in the higher address range should contact Atmel.

| Package Type |                                                       |  |  |

|--------------|-------------------------------------------------------|--|--|

| 32J          | 32-Lead, Plastic J-Leaded Chip Carrier Package (PLCC) |  |  |

| 32T          | 32-Lead, Thin Small Outline Package (TSOP)            |  |  |

# Ordering Information (Continued)

| t <sub>ACC</sub><br>(ns) | I <sub>CC</sub> (mA) |         |                                    |            |                              |

|--------------------------|----------------------|---------|------------------------------------|------------|------------------------------|

|                          | Active               | Standby | Ordering Code                      | Package    | Operation Range              |

| 55                       | 25                   | 0.05    | AT49HLV010-55JC<br>AT49HLV010-55TC | 32J<br>32T | Commercial<br>(0°C - 70°C)   |

|                          | 25                   | 0.05    | AT49HLV010-55JI<br>AT49HLV010-55TI | 32J<br>32T | Industrial<br>(-40°C - 85°C) |

| 70                       | 25                   | 0.05    | AT49HLV010-70JC<br>AT49HLV010-70TC | 32J<br>32T | Commercial<br>(0°C - 70°C)   |

|                          | 25                   | 0.05    | AT49HLV010-70JI<br>AT49HLV010-70TI | 32J<br>32T | Industrial<br>(-40°C - 85°C) |

| 90                       | 25                   | 0.05    | AT49HLV010-90JC<br>AT49HLV010-90TC | 32J<br>32T | Commercial<br>(0°C - 70°C)   |

|                          | 25                   | 0.05    | AT49HLV010-90JI<br>AT49HLV010-90TI | 32J<br>32T | Industrial<br>(-40°C - 85°C) |

| 120                      | 25                   | 0.05    | AT49LV010-12JC<br>AT49LV010-12TC   | 32J<br>32T | Commercial<br>(0°C - 70°C)   |

|                          | 25                   | 0.05    | AT49LV010-12JI<br>AT49LV010-12TI   | 32J<br>32T | Industrial<br>(-40°C - 85°C) |

| Package Type |                                                       |  |  |

|--------------|-------------------------------------------------------|--|--|

| 32J          | 32-Lead, Plastic J-Leaded Chip Carrier Package (PLCC) |  |  |

| 32T          | 32-Lead, Thin Small Outline Package (TSOP)            |  |  |