### **General Description**

The MAX8821 integrates a charge pump for white LEDs, an audio loudspeaker amplifier, and two lownoise LDOs controlled by an I<sup>2</sup>C control interface. The high-efficiency, adaptive-mode inverting charge pump drives up to six LEDs with constant current for uniform brightness. The LED current is controlled by an I<sup>2</sup>C interface and adjusts from 0.1mA to 25.6mA per LED into 32 pseudo-logarithmic steps. Independent voltages for each LED maximize efficiency even with large LED forward voltage (VF) mismatch. An internal temperature derating function reduces the current above +40°C to protect the LEDs.

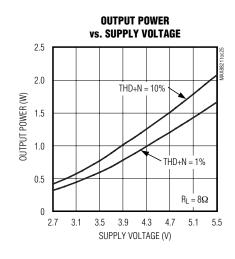

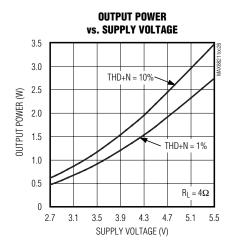

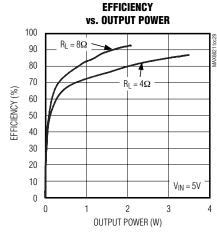

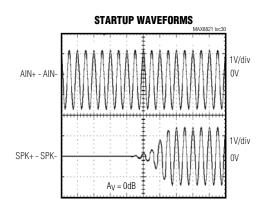

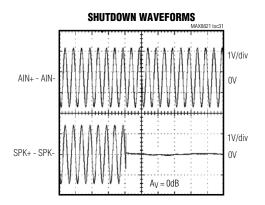

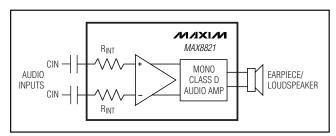

The high-efficiency mono Class D audio amplifier delivers up to 2W into a  $4\Omega$  speaker from a 5V input supply. The amplifier features proprietary filterless Active Emissions Limiting (AEL) technology. AEL prevents high-frequency emissions resulting from conventional Class D free-wheeling behavior in the presence of an inductive load. The amplifier offers two modulation schemes: a fixed-frequency mode (FFM) and a spreadspectrum mode (SSM) that reduce EMI-radiated emissions due to the modulation frequency. The amplifier also has robust output protection and high power-supply rejection ratio (PSRR). Click-and-pop suppression is active during power-up/down, enable/disable, and for all mode changes. The amplifier's gain is adjustable through an I2C interface, from -3dB to +24dB in 10 3dB steps. Differential inputs improve common-mode noise rejection.

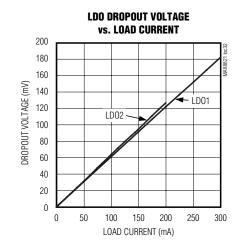

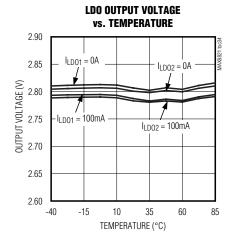

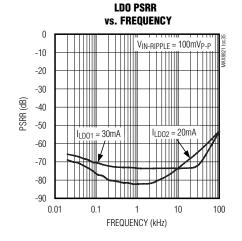

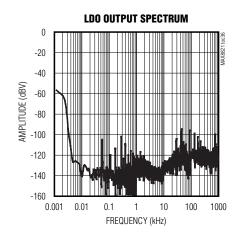

The LDOs in the MAX8821 are designed for low-noise operation. Each LDO output voltage can be individually programmed by the I<sup>2</sup>C interface. Both LDO1 and LDO2 have a high 70dB PSRR rating.

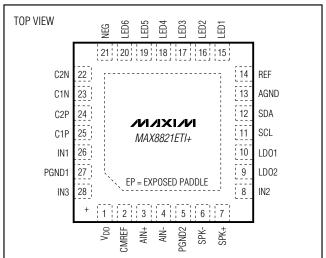

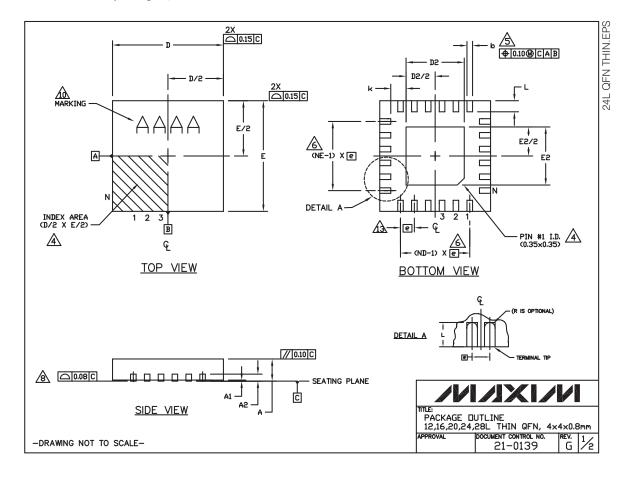

The MAX8821 includes soft-start, thermal shutdown, open-circuit, and short-circuit protections, and is available in a compact 28-pin, Thin QFN, 4mm x 4mm package (0.8mm max height).

### Applications

Cell Phones and Smartphones PDAs, Digital Cameras, Camcorders MP3 Players, GPS Devices

#### \_\_\_\_ Features

- White LED Inverting Charge Pump Independent Adaptive Current Regulators for Each LED

- 6 Low-Dropout Current Regulators

Flexible I<sup>2</sup>C Dimming Control for Each LED

Ramp-Up/Down, Current Control for Each LED

Low 70μA (typ) Quiescent Current

T<sub>A</sub> Derating Function Protects LEDs

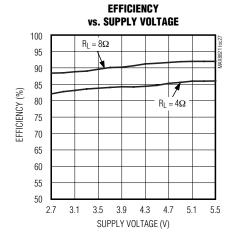

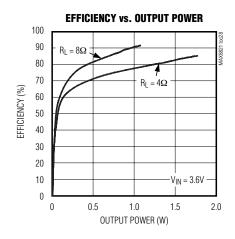

- ♦ Mono 2W Class D Loudspeaker Amplifier 85% Efficiency (R<sub>L</sub> = 8Ω, P<sub>OUT</sub> = 600mW) Low 0.05% THD+N at 1kHz High 65dB PSRR at 1kHz Fully Differential Inputs -3dB to +24dB Gain Settings in 3dB Steps Integrated Click-and-Pop Suppression Low Quiescent Current

- ◆ Dual Low-Noise LDO 45µVRMS Output Noise, 70dB PSRR Flexible I<sup>2</sup>C-Controlled Output Voltages 200mA and 300mA Output Current Drive

## Ordering Information

| PART        | TEMP RANGE     | PIN-<br>PACKAGE          | PKG<br>CODE |

|-------------|----------------|--------------------------|-------------|

| MAX8821ETI+ | -40°C to +85°C | 28 Thin QFN<br>4mm x 4mm | T2844-1     |

<sup>+</sup>Denotes a lead-free package.

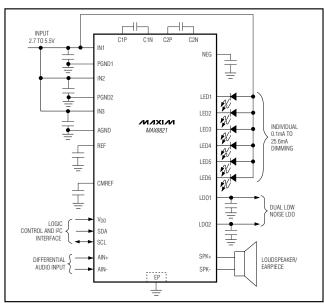

## **Typical Operating Circuit**

Maxim Integrated Products

1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN1, IN2, IN3, V <sub>DD</sub> to AGNDSCL, SDA to AGNDIN1, IN2, IN3 to NEG | 0.3V to (V <sub>DD</sub> + 0.3V)  | IN1, IN2 to IN3<br>PGND1, PGND2 to A0<br>SPK+, SPK- Short Circ |

|----------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------|

| AGND to C2N                                                                |                                   | Continuous Power Dis                                           |

| C1P, C2P to AGND                                                           |                                   | 28-Pin, Thin QFN 4n                                            |

| LED_, C1N, C2N to NEG                                                      | 0.3V to (V <sub>IN1</sub> + 0.3V) | (derate 28.6mW/°C                                              |

| LDO1, LDO2, REF to AGND                                                    | 0.3V to (V <sub>IN3</sub> + 0.3V) | Junction Temperature                                           |

| CMREF, AIN+, AIN-, SPK+, SPK-                                              |                                   | Storage Temperature                                            |

| to AGND                                                                    | 0.3V to $(V_{IN2} + 0.3V)$        | Lead Temperature (so                                           |

| IN1, IN2 to IN3                                       | 0.3V to +0.3V |

|-------------------------------------------------------|---------------|

| PGND1, PGND2 to AGND                                  |               |

| SPK+, SPK- Short Circuit to PGND2 or IN2              | Continuous    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

| 28-Pin, Thin QFN 4mm x 4mm                            |               |

| (derate 28.6mW/°C above +70°C)                        | 2286mW        |

| Junction Temperature                                  | +150°C        |

| Storage Temperature Range                             |               |

| Lead Temperature (soldering, 10s)                     | +300°C        |

|                                                       |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V$ , circuit of Figure 2,  $T_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25$ °C.) (Note 1)

| PARAMETER                                                                   | CONDITIONS                                                                                                       |                        |       | TYP         | MAX   | UNITS |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------|-------|-------------|-------|-------|

| V <sub>IN1</sub> , V <sub>IN2</sub> , V <sub>IN3</sub> Operating<br>Voltage |                                                                                                                  |                        | 2.7   |             | 5.5   | V     |

| V <sub>DD</sub> Operating Range                                             |                                                                                                                  |                        | 1.5   |             | 5.5   | V     |

| Undervoltage Lockout (UVLO)<br>Threshold                                    | V <sub>IN3</sub> rising                                                                                          |                        | 2.25  | 2.45        | 2.65  | V     |

| UVLO Hysteresis                                                             |                                                                                                                  |                        |       | 100         |       | mV    |

| V <sub>DD</sub> Shutdown Threshold                                          |                                                                                                                  |                        | 0.450 | 0.865       | 1.350 | V     |

|                                                                             | V <sub>DD</sub> = AGND                                                                                           | T <sub>A</sub> = +25°C |       | 0.1         | 1     |       |

| IN1, IN2, IN3 Shutdown Supply<br>Current                                    | VDD = AGND                                                                                                       | $T_A = +85^{\circ}C$   |       | 0.1         |       | μΑ    |

| (All Outputs Off)                                                           | $V_{DD} = 3.6V$                                                                                                  | $T_A = +25^{\circ}C$   |       | 2           | 10    | μΑ    |

| ,                                                                           | VDD = 0.0V                                                                                                       | T <sub>A</sub> = +85°C |       | 2           |       |       |

|                                                                             | Charge pump inactive, 2 LEDs at 0.1mA setting, audio amplifier disabled, LDO1 and LDO2 disabled                  |                        |       | 70          | 120   | ^     |

|                                                                             | LED driver disabled, audio amplifier disabled, and LDO1 and LDO2 enabled                                         |                        |       | 170         | 250   | μΑ    |

| No-Load Supply Current                                                      | Charge pump active, 1MHz switching, all LEDs at 25.6mA setting, audio amplifier disabled, LDO1 and LDO2 disabled |                        |       | 1.50        | 4.00  | mA    |

|                                                                             | LED driver disabled, audio amplifier enabled, LDO1 and LDO2 disabled                                             |                        |       | 6.6         | 20    |       |

| Thermal Shutdown                                                            |                                                                                                                  |                        |       | +160        |       | °C    |

| Thermal-Shutdown Hysteresis                                                 |                                                                                                                  |                        |       | 20          |       | °C    |

| CHARGE PUMP                                                                 |                                                                                                                  |                        |       |             |       |       |

|                                                                             | SYNC = 0                                                                                                         |                        |       | 1000        |       |       |

| Switching Fraguency                                                         | SYNC = 1, SW_MODE = 00                                                                                           |                        | 450   | 550         | 650   |       |

| Switching Frequency (fsw)                                                   | SYNC = 1, SW_MODE = 01                                                                                           |                        |       | 700         | 825   | kHz   |

| (.011)                                                                      | SYNC = 1, SW_MODE = 10                                                                                           |                        |       | 625<br>± 25 |       |       |

2 \_\_\_\_\_\_ NIXI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V, circuit of Figure 2, T_{A} = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_{A} = +25^{\circ}C.) (Note 1)$

| PARAMETER                                      | CC                                                              | ONDITIONS                                                             |       | MIN  | TYP   | MAX  | UNITS |  |

|------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|-------|------|-------|------|-------|--|

| Soft-Start Time                                |                                                                 |                                                                       |       |      | 0.1   |      | ms    |  |

| Regulation Voltage                             | (VIN1 - VNEG)                                                   |                                                                       |       |      | 5     |      | V     |  |

| Open-Loop NEG Output<br>Resistance             | (0.5 x V <sub>IN1</sub> - V <sub>NEG</sub> ) / I <sub>NEG</sub> | રે                                                                    |       |      | 1.75  | 3.5  | Ω     |  |

| Output Current                                 | V <sub>IN1</sub> = 3.2V, LED V <sub>FMAX</sub>                  | = 3.9V                                                                |       | 154  |       |      | mA    |  |

| NEG Discharge Resistance in Shutdown           | All LEDs disabled                                               |                                                                       |       |      | 10    |      | kΩ    |  |

| LED_ CURRENT REGULATORS                        |                                                                 |                                                                       |       | •    |       |      | •     |  |

| Current Setting Range                          | I <sub>LED</sub> _                                              |                                                                       |       | 0.1  |       | 25.6 | mA    |  |

|                                                |                                                                 | T <sub>A</sub> = +25°C                                                |       | -2   | ±1    | +2   |       |  |

| Current Accuracy                               | 25.6mA setting                                                  | $T_A = -40$ °C to dera<br>function start temp<br>(enabled by $I^2$ C) |       | -5   |       | +5   | %     |  |

|                                                | $0.1$ mA setting, $T_A = +25$                                   | °C                                                                    |       | -30  | ±5    | +30  | ]     |  |

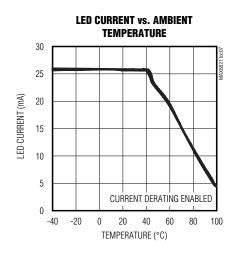

| Current-Derating-Function Start<br>Temperature |                                                                 |                                                                       |       |      | +40   |      | °C    |  |

| Current-Derating-Function Slope                | $T_A = +40^{\circ}C \text{ to } +85^{\circ}C$                   |                                                                       |       |      | -1.67 |      | %/°C  |  |

| Dec ou                                         | Charge pump inactive                                            |                                                                       |       |      | 2.3   | 4.6  | 0     |  |

| R <sub>DS</sub> ON                             | Charge pump active                                              |                                                                       |       |      | 5     | 14   | Ω     |  |

| Dropout Voltage                                | 25.6mA setting (Note 2)                                         |                                                                       | ctive |      | 72    | 120  | mV    |  |

| Dropout voltage                                | 25.011A Setting (Note 2)                                        | ive                                                                   |       | 120  | 360   | 1110 |       |  |

| Current Regulator<br>Switchover Threshold      | Charge pump inactive to V <sub>LED</sub> falling                | active,                                                               |       | 125  | 150   | 175  | mV    |  |

| Current Regulator<br>Switchover Hysteresis     |                                                                 |                                                                       |       |      | 100   |      | mV    |  |

| Landana Commandia Chadalana                    | All LEDs                                                        | All LEDs $T_A = +25^{\circ}C$                                         |       |      | 0.01  | 1    |       |  |

| Leakage Current in Shutdown                    | disabled                                                        | T <sub>A</sub> = +85°C                                                |       |      | 0.1   |      | μA    |  |

|                                                |                                                                 |                                                                       | 00    |      | 524   |      |       |  |

| Off Blink Time                                 | B7, B6 or B3, B2,<br>SYNC = 0,                                  |                                                                       | 01    |      | 1048  |      | ms    |  |

| On Blink Time                                  | Table 11                                                        |                                                                       | 10    |      | 2097  |      | 1113  |  |

|                                                |                                                                 |                                                                       | 11    |      | 4194  |      |       |  |

|                                                | DE D4 or D4 D0                                                  |                                                                       | 00    |      | 66    |      |       |  |

| On Blink Time                                  | B5, B4 or B1, B0,<br>SYNC = 0,                                  |                                                                       | 01    |      | 131   |      | ms    |  |

|                                                | Table 11                                                        | 10                                                                    |       | 262  |       | 1110 |       |  |

|                                                |                                                                 | 1                                                                     |       |      | 524   |      |       |  |

|                                                | LEDRU: B7, B6 or B3,                                            |                                                                       | 00    | ļ    | 262   |      | 1     |  |

| Ramp-Up/Down Time                              | LEDRD: B5, B4 or B1, B0                                         |                                                                       | 10    |      | 524   |      | - ms  |  |

|                                                | SYNC = 0,<br>Tables 8, 9, 10 (Note 3)                           | SYNC = 0,<br>Tables 8 9 10 (Note 3)                                   |       | -    | 1048  |      |       |  |

|                                                | 145.55 5, 5, 15 (146.6 5)                                       | 11                                                                    |       | 2097 |       |      |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V$ , circuit of Figure 2,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                            | CONDITIONS                                                            |                                |                 |                                  | TYP                  | MAX                              | UNITS |

|--------------------------------------|-----------------------------------------------------------------------|--------------------------------|-----------------|----------------------------------|----------------------|----------------------------------|-------|

| AUDIO AMPLIFIER                      |                                                                       |                                |                 |                                  |                      |                                  |       |

| Common-Mode Bias Voltage             |                                                                       |                                |                 | 0.95 x<br>(V <sub>IN3</sub> / 2) | V <sub>IN3</sub> / 2 | 1.05 x<br>(V <sub>IN3</sub> / 2) | V     |

| Output Offset Voltage                | V <sub>AIN+</sub> = V <sub>AIN-</sub> = V <sub>IN3</sub> /            | 2, audio gain = 0              | dB              |                                  | ±1                   |                                  | mV    |

| Common-Mode Input Voltage            |                                                                       |                                |                 | 0.5                              |                      | V <sub>IN3</sub> -<br>1.2V       | ٧     |

|                                      |                                                                       |                                |                 |                                  | -3                   |                                  |       |

|                                      |                                                                       |                                |                 |                                  | 0                    |                                  |       |

|                                      |                                                                       |                                |                 |                                  | 3                    |                                  |       |

|                                      |                                                                       |                                |                 |                                  | 6                    |                                  |       |

| Audio Gain                           | Table 15, B3:B0                                                       |                                |                 |                                  | 9                    |                                  | dB    |

| , tage dans                          | 14510 10, 20.20                                                       |                                |                 |                                  | 12                   |                                  | QD.   |

|                                      |                                                                       |                                |                 |                                  | 15                   |                                  |       |

|                                      |                                                                       |                                |                 |                                  | 18                   |                                  |       |

|                                      |                                                                       |                                |                 |                                  | 21                   |                                  |       |

|                                      |                                                                       |                                |                 |                                  | 24                   |                                  |       |

| Audio Gain Accuracy                  |                                                                       |                                |                 | -3<br>54.4                       | 99.0                 | +3                               | %     |

|                                      |                                                                       | Audio gain = -3dB              |                 |                                  |                      | 143.5                            |       |

|                                      | Audio gain = 0dB                                                      | 49.1                           | 89.2            | 129.3                            | kΩ                   |                                  |       |

|                                      | Audio gain = 3dB                                                      | 43.1                           | 78.4            | 113.7                            |                      |                                  |       |

|                                      | Audio gain = 6dB                                                      | 36.8                           | 66.9            | 97.0                             |                      |                                  |       |

| Input Resistance                     | Audio gain = 9dB                                                      | 30.5                           | 55.5            | 80.5                             |                      |                                  |       |

|                                      | Audio gain = 12dB                                                     | 24.6                           | 44.7            | 64.8                             |                      |                                  |       |

|                                      | Audio gain = 15dB                                                     | 19.3<br>14.8                   | 35.2<br>26.9    | 51.0                             |                      |                                  |       |

|                                      | Audio gain = 16dB                                                     | Audio gain = 18dB              |                 |                                  |                      | 39.0<br>29.3                     |       |

|                                      | Audio gain = 24dB                                                     | 11.1<br>8.2                    | 20.2            | 22.0                             |                      |                                  |       |

|                                      | V <sub>IN2</sub> = V <sub>IN3</sub> = 3.6V                            |                                |                 |                                  | 46                   | 22.0                             |       |

| Common-Mode Rejection Ratio          | f = 1kHz, V <sub>IN2</sub> = V <sub>IN3</sub> =                       |                                | 46              |                                  | dB                   |                                  |       |

|                                      | V <sub>AIN+</sub> = V <sub>AIN-</sub> = V <sub>IN3</sub> /            |                                | f = 217Hz       |                                  | 65                   |                                  |       |

| Power-Supply Rejection Ratio         | 100mV <sub>P-P</sub> at V <sub>IN3</sub>                              | ۷,                             | f = 20kHz       |                                  | 50                   |                                  | dB    |

|                                      |                                                                       |                                | $R_L = 8\Omega$ | 0.36                             | 0.5                  |                                  |       |

|                                      | THD+N = 1%,                                                           | $V_{IN3} = 3.6V$               | $R_L = 4\Omega$ |                                  | 0.85                 |                                  | W     |

| Output Power                         | f = 1kHz                                                              |                                | $R_L = 8\Omega$ | 0.8                              | 1.1                  |                                  |       |

|                                      | (14016 4)                                                             | (Note 4) V <sub>IN3</sub> = 5V | $R_L = 4\Omega$ |                                  | 2.0                  |                                  |       |

| Total Harmonic Distortion Plus Noise | $R_L = 8\Omega$ , $f = 1kHz$ , $P_{OU}$<br>$V_{IN2} = V_{IN3} = 3.6V$ |                                | 0.05            |                                  | %                    |                                  |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V, circuit of Figure 2, T_{A} = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_{A} = +25^{\circ}C.) (Note 1)$

| PARAMETER                                                          |                                                                          | CONDITIONS                 | MIN      | TYP         | MAX   | UNITS             |

|--------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|----------|-------------|-------|-------------------|

|                                                                    |                                                                          | Fixed-frequency mode (FFM) |          | 91          |       |                   |

| Cignal to Naiga Datio                                              | $R_L = 8\Omega$ , $f = 1$ kHz,<br>$P_{OUT} = 0.25$ W,                    | Spread-spectrum mode (SSM) |          | 89          |       | dB                |

| Signal-to-Noise Ratio                                              | $V_{IN2} = V_{IN3} = 3.6V$                                               | FFM A weighted             |          | 93          |       | ав                |

|                                                                    | 1111/2 1111/0 0101                                                       | SSM A weighted             |          | 91          |       |                   |

|                                                                    | SW_MODE = 00                                                             |                            | 900      | 1100        | 1300  |                   |

| Oscillator Frequency                                               | SW_MODE = 01                                                             |                            | 1150     | 1400        | 1650  | kHz               |

| (f <sub>osc</sub> )                                                | SW_MODE = 10                                                             |                            |          | 1250<br>±50 |       | NI IZ             |

| Differential Input<br>Resistance                                   | Shutdown mode only                                                       |                            |          | 100         |       | kΩ                |

| Output Current Limit                                               | SPK+, SPK- short circ                                                    | cuited to PGND2 or to IN2  |          | 2           |       | А                 |

| Wake-Up Delay After<br>Short Circuit                               |                                                                          |                            |          |             |       | μs                |

| LDO1                                                               |                                                                          |                            | <u>.</u> |             |       |                   |

| Output Voltage V <sub>LDO1</sub>                                   | $3.6V \le V_{IN3} \le 5.5V$ ,<br>$1mA \le I_{LDO1} \le 300m$             | A                          | 1.164    | 1.200       | 1.236 | V                 |

| Maximum Output<br>Current                                          |                                                                          |                            | 300      |             |       | mA                |

| Output Current Limit                                               | $V_{LDO1} = 0V$                                                          |                            | 400      | 650         | 1000  | mA                |

| Dropout Voltage                                                    | I <sub>LDO1</sub> = 200mA, T <sub>A</sub> =                              | +25°C (Note 5)             |          | 150         | 300   | mV                |

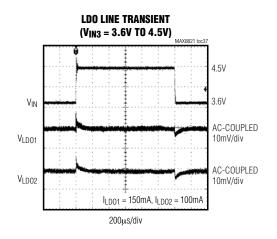

| Line Regulation                                                    | V <sub>IN3</sub> stepped from 3.4V to 5.5V,<br>I <sub>LDO1</sub> = 150mA |                            |          | 2.4         |       | mV                |

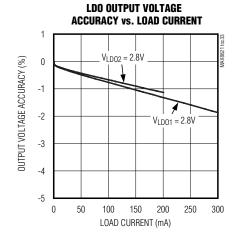

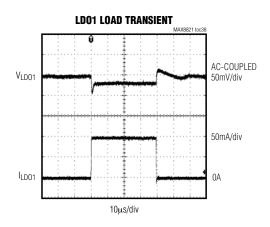

| Load Regulation                                                    | I <sub>LDO1</sub> stepped from 1mA to 300mA                              |                            |          | 25          |       | mV                |

| Power-Supply<br>Rejection<br>ΔV <sub>IN3</sub> /ΔV <sub>LDO1</sub> | 10Hz to 10kHz,<br>I <sub>LDO1</sub> = 30mA                               |                            |          | 70          |       | dB                |

| Output Voltage Noise (RMS)                                         | 100Hz to 100kHz,<br>I <sub>LDO1</sub> = 30mA                             |                            |          | 45          |       | μV <sub>RMS</sub> |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V$ , circuit of Figure 2,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                          | CONDITIONS                                                            | }    | MIN   | TYP   | MAX   | UNITS |

|--------------------------------------------------------------------|-----------------------------------------------------------------------|------|-------|-------|-------|-------|

|                                                                    |                                                                       | 0000 | 1.164 | 1.2   | 1.236 |       |

|                                                                    |                                                                       | 0001 | 1.261 | 1.3   | 1.339 |       |

|                                                                    |                                                                       | 0010 | 1.455 | 1.5   | 1.545 |       |

|                                                                    |                                                                       | 0011 | 1.552 | 1.6   | 1.648 |       |

|                                                                    |                                                                       | 0100 | 1.746 | 1.8   | 1.854 |       |

|                                                                    |                                                                       | 0101 | 1.843 | 1.9   | 1.957 |       |

|                                                                    |                                                                       | 0110 | 1.940 | 2.0   | 2.060 |       |

| Programmable Output                                                | I <sub>LDO1</sub> = 50mA<br>control bits B3:B0;                       | 0111 | 2.231 | 2.3   | 2.369 | V     |

| Voltage                                                            | see Table 13                                                          | 1000 | 2.425 | 2.5   | 2.575 | V     |

|                                                                    | los rabie re                                                          | 1001 | 2.522 | 2.6   | 2.678 |       |

|                                                                    |                                                                       | 1010 | 2.619 | 2.7   | 2.781 |       |

|                                                                    |                                                                       | 1011 | 2.716 | 2.8   | 2.884 |       |

|                                                                    |                                                                       | 1100 | 2.813 | 2.9   | 2.987 |       |

|                                                                    |                                                                       | 1101 | 2.910 | 3.0   | 3.090 |       |

|                                                                    |                                                                       | 1110 | 3.007 | 3.1   | 3.193 |       |

|                                                                    |                                                                       | 1111 | 3.104 | 3.2   | 3.296 |       |

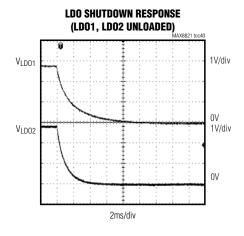

| Shutdown Output Impedance                                          | LDO1 disabled through I <sup>2</sup> C                                |      |       | 1     |       | kΩ    |

| LDO2                                                               |                                                                       |      | •     |       |       | •     |

| Output Voltage V <sub>LDO2</sub>                                   | $3.6V \le V_{IN3} \le 5.5V$ ,<br>$1mA \le I_{LDO2} \le 200mA$         |      | 1.455 | 1.500 | 1.545 | V     |

| Maximum Output<br>Current                                          |                                                                       |      | 200   |       |       | mA    |

| Output Current Limit                                               | V <sub>LDO2</sub> = 0V                                                |      | 250   | 550   | 750   | mA    |

| Dropout Voltage                                                    | I <sub>LDO2</sub> = 133mA, T <sub>A</sub> = +25°C (Note 5)            |      |       | 100   | 200   | mV    |

| Line Regulation                                                    | V <sub>IN3</sub> stepped from 3.4V to 5.5V, I <sub>LDO2</sub> = 100mA |      |       | 2.4   |       | mV    |

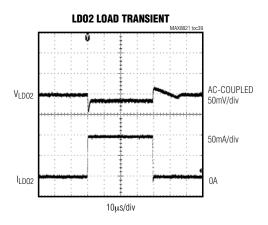

| Load Regulation                                                    | I <sub>LDO2</sub> stepped from 1mA to 200mA                           |      |       | 25    |       | mV    |

| Power-Supply<br>Rejection<br>ΔV <sub>IN3</sub> /ΔV <sub>LDO2</sub> | 10Hz to10kHz,<br>I <sub>LDO2</sub> = 20mA                             |      | 70    |       | dB    |       |

| Output Voltage Noise (RMS)                                         | 100Hz to100kHz,<br>I <sub>LDO2</sub> = 20mA                           |      |       | 45    |       | μVRMS |

6 \_\_\_\_\_\_\_NIXI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V, circuit of Figure 2, T_{A} = -40^{\circ}C to +85^{\circ}C, unless otherwise noted. Typical values are at T_{A} = +25^{\circ}C.) (Note 1)$

| PARAMETER                                  | СО                                        | NDITIONS            |      | MIN                      | TYP  | MAX                      | UNITS    |

|--------------------------------------------|-------------------------------------------|---------------------|------|--------------------------|------|--------------------------|----------|

|                                            |                                           |                     | 0000 | 1.455                    | 1.5  | 1.545                    |          |

|                                            |                                           |                     | 0001 | 1.552                    | 1.6  | 1.648                    |          |

|                                            |                                           |                     | 0010 | 1.746                    | 1.8  | 1.854                    |          |

|                                            |                                           |                     | 0011 | 1.940                    | 2.0  | 2.060                    |          |

|                                            |                                           |                     | 0100 | 2.134                    | 2.2  | 2.266                    |          |

|                                            |                                           |                     | 0101 | 2.231                    | 2.3  | 2.369                    |          |

|                                            | ILDO2 = 50mA                              | <u></u>             | 0110 | 2.328                    | 2.4  | 2.472                    | <u> </u> |

| Programmable Output                        | control bits                              |                     | 0111 | 2.425                    | 2.5  | 2.575                    | V        |

| Voltage                                    | B3:B0;                                    |                     | 1000 | 2.522                    | 2.6  | 2.678                    | V        |

|                                            | see Table 14                              |                     | 1001 | 2.619                    | 2.7  | 2.781                    |          |

|                                            |                                           | <u></u>             | 1010 | 2.716                    | 2.8  | 2.884                    | <u> </u> |

|                                            |                                           |                     | 1011 | 2.813                    | 2.9  | 2.987                    |          |

|                                            |                                           |                     | 1100 | 2.910                    | 3.0  | 3.090                    |          |

|                                            |                                           |                     | 1101 | 3.007                    | 3.1  | 3.193                    |          |

|                                            |                                           |                     | 1110 | 3.104                    | 3.2  | 3.296                    |          |

|                                            |                                           |                     | 1111 | 3.201                    | 3.3  | 3.399                    |          |

| Shutdown Output<br>Impedance               | LDO2 disabled through I <sup>2</sup> C    |                     |      |                          | 1    |                          | kΩ       |

| I <sup>2</sup> C INTERFACE (Figur          | re 8)                                     |                     |      |                          |      |                          |          |

| Logic Input High<br>Voltage                |                                           |                     |      | 0.7 x<br>V <sub>DD</sub> |      |                          | V        |

| Logic Input Low<br>Voltage                 |                                           |                     |      |                          |      | 0.3 x<br>V <sub>DD</sub> | V        |

| La sia la sant Orresant                    | V 0V - 11 V                               | $T_A = +25^{\circ}$ | C    | -1                       | 0.01 | +1                       | ^        |

| Logic Input Current                        | $V_{IL} = 0V \text{ or } V_{IH} = V_{DD}$ | $T_A = +85^\circ$   | °C   |                          | 0.1  |                          | μΑ       |

| SDA Output Low<br>Voltage                  | I <sub>SDA</sub> = 3mA                    |                     |      |                          | 0.03 | 0.4                      | V        |

| I <sup>2</sup> C Clock Frequency           |                                           |                     |      |                          |      | 400                      | kHz      |

| Bus-Free Time<br>Between START and<br>STOP | <sup>†</sup> BUF                          |                     |      | 1.3                      |      |                          | μs       |

| Hold Time Repeated<br>START Condition      | <sup>†</sup> HD_STA                       |                     |      | 0.6                      | 0.1  |                          | μs       |

| SCL Low Period                             | t <sub>LOW</sub>                          |                     |      | 1.3                      | 0.2  |                          | μs       |

| SCL High Period                            | tніgh                                     |                     |      | 0.6                      | 0.2  |                          | μs       |

| Setup Time Repeated<br>START Condition     | tsu_sta                                   |                     |      |                          |      |                          | μs       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V$ , circuit of Figure 2,  $T_A = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                        | CONDITIONS | MIN | TYP   | MAX | UNITS |

|----------------------------------|------------|-----|-------|-----|-------|

| SDA Hold Time                    | thd_dat    | 0   | -0.01 |     | μs    |

| SDA Setup Time                   | tsu_dat    | 100 | 50    |     | ns    |

| Setup Time for STOP<br>Condition | tsu_sto    | 0.6 | 0.1   |     | μs    |

- Note 1: Limits are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design.

- Note 2: Dropout voltage is defined as the LED\_ to GND voltage when the current into LED\_ drops 10% from the value at V<sub>LED</sub> = 0.5V.

- Note 3: Ramp-up time is from 0mA to full scale; ramp-down time is from full scale to 0mA.

- Note 4: Output power is specified by a combination of a functional output current test and characterization analysis.

- Note 5: The dropout voltage is defined as V<sub>IN</sub>\_ V<sub>OUT</sub> when V<sub>OUT</sub> is 100mV below the nominal value of V<sub>OUT</sub>. The specification only applies when V<sub>OUT</sub> ≥ 3.0V.

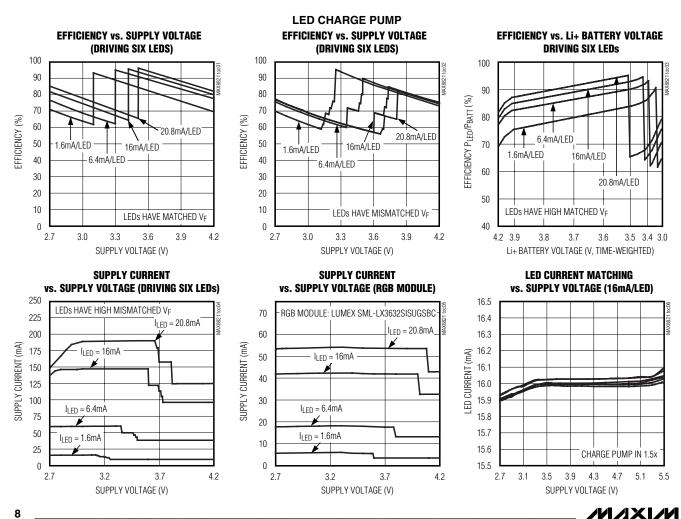

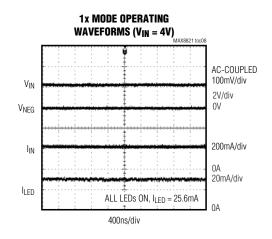

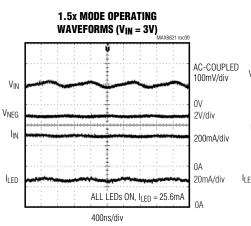

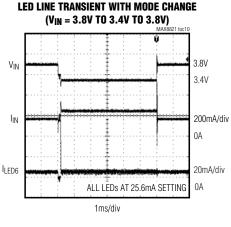

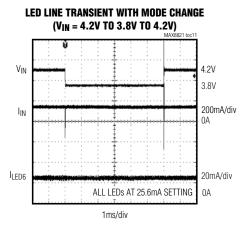

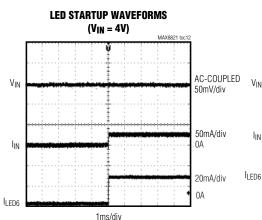

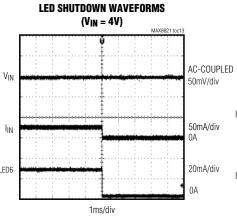

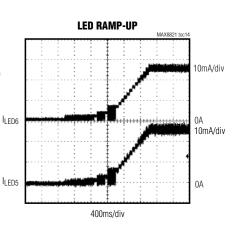

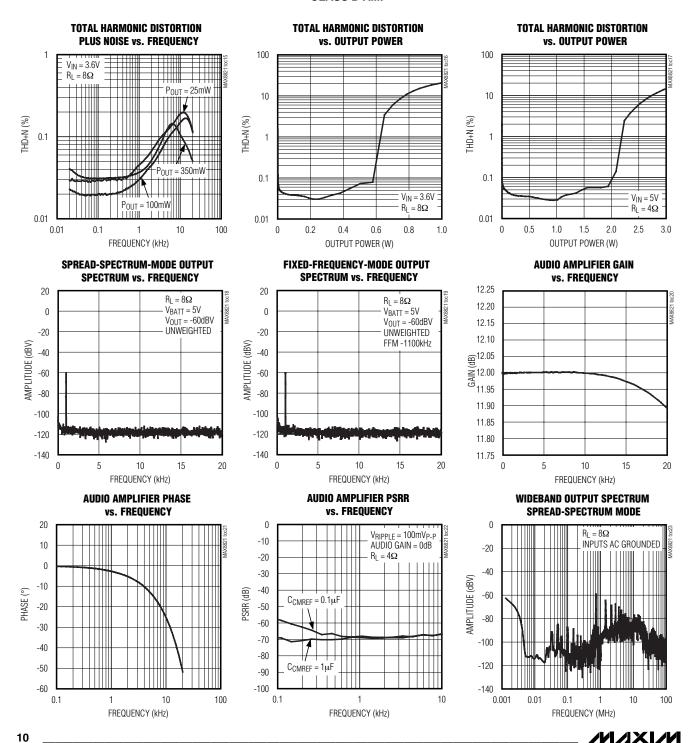

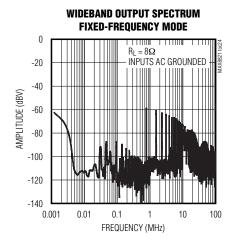

### **Typical Operating Characteristics**

(V<sub>IN1</sub> = V<sub>IN2</sub> = V<sub>IN3</sub> = V<sub>DD</sub> = 3.6V, V<sub>AGND</sub> = V<sub>PGND1</sub> = V<sub>PGND2</sub> = 0V, circuit of Figure 2, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V$ , circuit of Figure 2,  $T_A = +25$ °C, unless otherwise noted.)

MIXIM

## Typical Operating Characteristics (continued)

(V<sub>IN1</sub> = V<sub>IN2</sub> = V<sub>IN3</sub> = V<sub>DD</sub> = 3.6V, V<sub>AGND</sub> = V<sub>PGND1</sub> = V<sub>PGND2</sub> = 0V, circuit of Figure 2, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### **CLASS D AMP**

## Typical Operating Characteristics (continued)

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V$ , circuit of Figure 2,  $T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V, circuit of Figure 2, T_{A} = +25^{\circ}C, unless otherwise noted.)$

#### **DUAL LDOs**

## **Typical Operating Characteristics**

$(V_{IN1} = V_{IN2} = V_{IN3} = V_{DD} = 3.6V, V_{AGND} = V_{PGND1} = V_{PGND2} = 0V$ , circuit of Figure 2,  $T_A = +25$ °C, unless otherwise noted.)

## **Pin Description**

| PIN   | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                     |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>DD</sub> | I <sup>2</sup> C Input Supply Voltage. The V <sub>DD</sub> supply range is 1.5V to 5.5V. Drive V <sub>DD</sub> high to enable the I <sup>2</sup> C control. Drive V <sub>DD</sub> low to place the IC into shutdown mode.                                                                                    |

| 2     | CMREF           | Audio Common-Mode Reference Voltage. Bypass CMREF with a 0.1µF ceramic capacitor to AGND as close as possible to the IC.                                                                                                                                                                                     |

| 3     | AIN+            | Noninverting Audio Input                                                                                                                                                                                                                                                                                     |

| 4     | AIN-            | Inverting Audio Input                                                                                                                                                                                                                                                                                        |

| 5     | PGND2           | Audio Amplifier Power Ground. Connect PGND2 to the system ground plane.                                                                                                                                                                                                                                      |

| 6     | SPK-            | Audio Amplifier Negative Output                                                                                                                                                                                                                                                                              |

| 7     | SPK+            | Audio Amplifier Positive Output                                                                                                                                                                                                                                                                              |

| 8     | IN2             | Audio Amplifier Output Buffer Supply Voltage Input. The input voltage range is 2.7V to 5.5V. Connect IN2 directly to IN1 and IN3. Bypass IN2 to PGND2 with a 1µF ceramic capacitor as close as possible to the IC. IN2 is high impedance during shutdown.                                                    |

| 9     | LDO2            | 200mA LDO Output. Bypass LDO2 to AGND with a 1µF ceramic capacitor. LDO2 is disabled through the I <sup>2</sup> C interface.                                                                                                                                                                                 |

| 10    | LDO1            | 300mA LDO Output. Bypass LDO1 to AGND with a 2.2µF ceramic capacitor. LDO1 is disabled through the I <sup>2</sup> C interface.                                                                                                                                                                               |

| 11    | SCL             | I <sup>2</sup> C Clock Input. Data is read on the rising edge of V <sub>SCL</sub> .                                                                                                                                                                                                                          |

| 12    | SDA             | I <sup>2</sup> C Data Input. Data is read on the rising edge of V <sub>SCL</sub> .                                                                                                                                                                                                                           |

| 13    | AGND            | Analog Ground. Connect AGND to the system ground plane. AGND is also internally connected to the exposed paddle.                                                                                                                                                                                             |

| 14    | REF             | Reference Bypass. Bypass REF with a 0.1µF ceramic capacitor to AGND as close as possible to the IC.                                                                                                                                                                                                          |

| 15–20 | LED1-<br>LED6   | LED Current Regulators. Current flowing into LED_ is based upon the internal I <sup>2</sup> C registers. Connect LED_ to the cathodes of the external LEDs. LED_ is high impedance during shutdown. If unused, short LED_ to IN1 to disable the regulator.                                                   |

| 21    | NEG             | Charge-Pump Negative Output. Connect a $1\mu F$ ceramic capacitor from NEG to AGND. In shutdown, an internal $10k\Omega$ resistor connects NEG to AGND.                                                                                                                                                      |

| 22    | C2N             | Transfer Capacitor 2 Negative Connection. Connect a 1µF ceramic capacitor from C2P to C2N.                                                                                                                                                                                                                   |

| 23    | C1N             | Transfer Capacitor 1 Negative Connection. Connect a 1µF ceramic capacitor from C1P to C1N.                                                                                                                                                                                                                   |

| 24    | C2P             | Transfer Capacitor 2 Positive Connection. Connect a 1µF ceramic capacitor from C2P to C2N.                                                                                                                                                                                                                   |

| 25    | C1P             | Transfer Capacitor 1 Positive Connection. Connect a 1µF ceramic capacitor from C1P to C1N.                                                                                                                                                                                                                   |

| 26    | IN1             | Charge-Pump Supply Voltage Input. The input voltage range is 2.7V to 5.5V. Connect IN1 directly to IN2 and IN3. Bypass IN1 to PGND1 with a 2.2µF ceramic capacitor as close as possible to the IC. IN1 is high impedance during shutdown.                                                                    |

| 27    | PGND1           | Charge-Pump Power Ground. Connect PGND1 to the system ground plane.                                                                                                                                                                                                                                          |

| 28    | IN3             | Input Voltage Supply for LDO1, LDO2, REF, Class D Preamplifier, and Class D Amplifier Modulator Core. The input voltage range is 2.7V to 5.5V. Connect IN3 directly to IN1 and IN2. Bypass IN3 to AGND with a 2.2µF ceramic capacitor as close as possible to the IC. IN3 is high impedance during shutdown. |

| _     | EP              | Exposed Paddle. Connect the exposed paddle to AGND directly under the IC. Exposed paddle is internally connected to AGND.                                                                                                                                                                                    |

\_\_\_\_\_\_NIXI/N

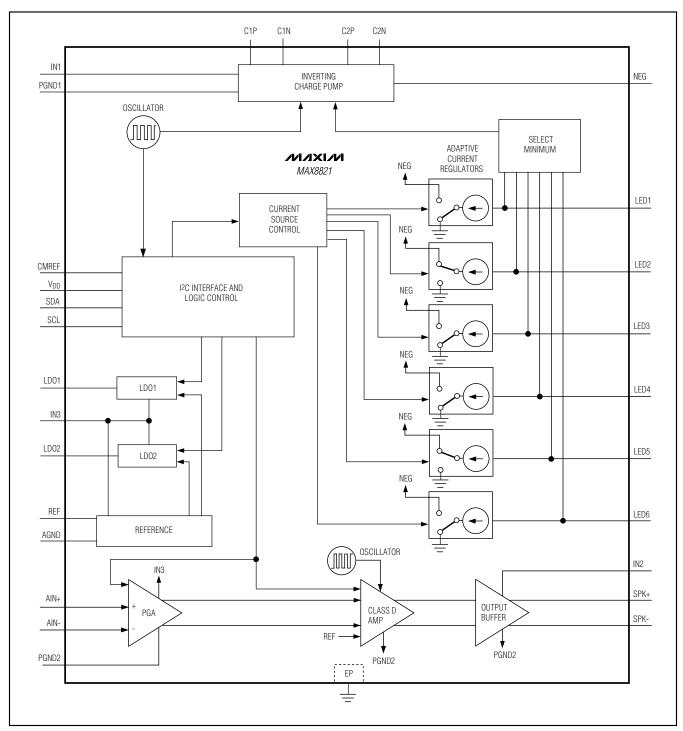

Figure 1. Block Diagram

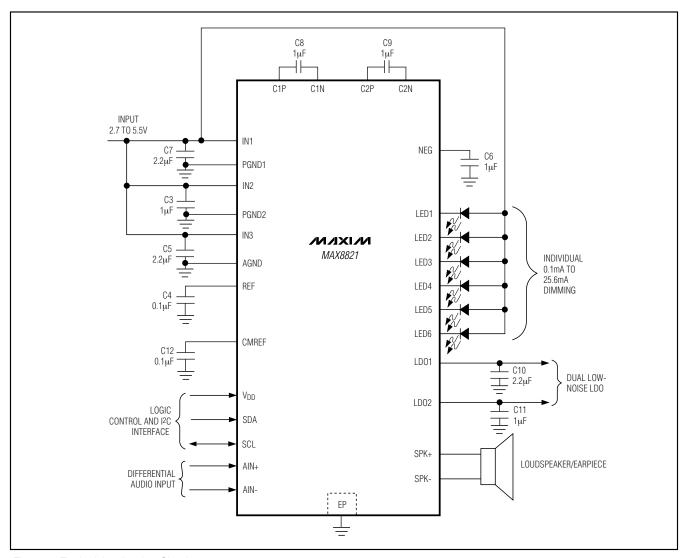

Figure 2. Typical Application Circuit

## **Detailed Description**

The MAX8821 integrates a charge pump for white LED display backlighting, an audio loudspeaker amplifier, and dual LDO for camera functions. It includes softstart, thermal shutdown, open-circuit and short-circuit protections for the white LEDs, audio amplifier, and LDOs. Figure 1 is the block diagram, and Figure 2 shows the typical application circuit.

#### LED Charge Pump

The MAX8821 features an inverting charge pump and six current regulators capable of 25.6mA each to drive

six LEDs. The current regulators are matched to within  $\pm 1\%$  (typ), providing uniform white LED brightness for LCD backlight applications. To maximize efficiency, the current regulators operate with as little as 0.15V voltage drop. Individual white LED current regulators conduct current to GND or NEG to extend usable battery life. In the case of mismatched forward voltage of white LEDs, only the white LEDs requiring higher voltage are switched to direct current to NEG instead of GND, further raising efficiency and reducing battery current drain. The regulation scheme is optimized to ensure low EMI and low input ripple. The on-chip ambient temperature derating function safely allows bright 25.6mA

full-scale output current while automatically reducing current gradually above +40°C in accordance with popular LED ratings. The on-chip derating feature can be enabled, or disabled, using the I<sup>2</sup>C interface.

#### **Current Regulator Switchover**

When  $V_{\text{IN}}$  is higher than the forward voltage of the white LED plus the 0.15V headroom of the current regulator, the LED current returns through ground. If this condition is satisfied for all six white LEDs the charge pump remains inactive. When the input voltage drops so that the current regulator head room cannot be maintained for any of the individual white LEDs, the inverting charge pump activates and generates a voltage on NEG that is no greater than 5V below  $V_{\text{IN}}$ . Each current regulator contains circuitry that detects when it is in dropout and switches that current regulator return path from GND to NEG. Since this is done on an LED-by-LED basis, the LED current is switched for only the individual LED requiring higher voltage, thus minimizing power consumption.

#### Ramp-Up and Ramp-Down Function

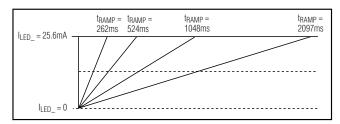

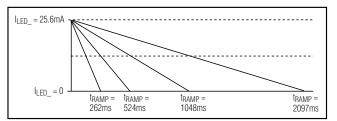

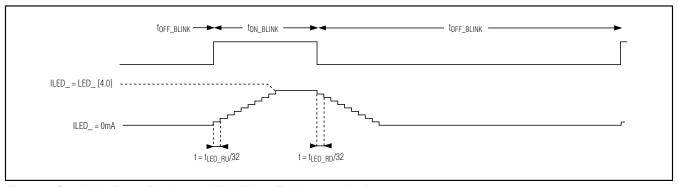

The LED drivers in the MAX8821 provide ramp-up and ramp-down of LED current for smooth transitions between different brightness settings. A controlled ramp is used when the LED current level is changed, when the LEDs are enabled, and when the LEDs are disabled. The LED currents ramp up and down smoothly on a pseudo-log scaling of the LED current sources (Figures 3 and 4). Each LED source has an individual ramp control making it possible to ramp different LEDs at different rates. The ramp-up and ramp-down (tramp) LED current times are controlled by the LED\_RU and LED\_RD control bits (Tables 8, 9, and 10). The LED\_RP\_EN bit enables and disables the ramps. The MAX8821 increases/decreases the current one step every tramp/32 until the desired current is reached.

#### Blink Timer

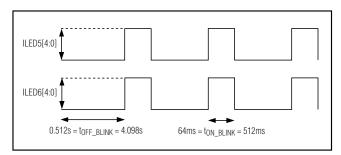

The current regulators for LED5 and LED6 feature a blink function. The OFF and ON time for LED5 and LED6 can be set using the I<sup>2</sup>C interface (Table 11). See Figure 5.

#### Combining Blink Timer and Ramp Function

To combine the ramp function together with the blink timer for LED5 and/or LED6, special timing considerations need to be fulfilled. It is recommended to keep the ramp-up timer shorter than the ON blink timer and the ramp-down timer shorter than the OFF blink timer. Failing to comply with these timing constraints results in the LED\_ not reaching the programmed current (LED\_[4:0], Tables 6 and 7) during the ON time and the

LED\_ current not returning to 0mA during the off time. See the following equations to ensure proper operation:

$$\begin{split} t_{\text{ON\_BLINK}} &\geq \frac{t_{\text{LED\_RU}}}{32} (\text{LED\_[4:0]+1}) \\ t_{\text{OFF\_BLINK}} &\geq \frac{t_{\text{LED\_RD}}}{32} (\text{LED\_[4:0]+1}) \end{split}$$

where LED\_[4:0] is the programmed current set by I<sup>2</sup>C (see Tables 6 and 7).

Figure 6 shows combining ramp function and blink timer.

#### LED Short- and Open-Circuit Protection

If any LED fails as an open circuit, the corresponding LED\_ is internally connected to ground and the charge pump is enabled. To disable the corresponding current regulator, short any unused LED\_ to IN1. The MAX8821 contains special circuitry to detect this condition and disables the corresponding current regulator to avoid wasting battery power.

#### Temperature Derating

The MAX8821 contains a derating function that automatically limits the LED current at high temperatures in accordance with the recommended derating curve of popular white LEDs. The derating function enables the safe usage of higher LED current at room temperature, thus reducing the number of LEDs required to backlight the display. The derating circuit limits the LED current by reducing the LED current above +40°C at approximately 1.67%/°C. The temperature derating function is enabled/disabled using the I²C interface and by default is disabled.

Figure 3. Ramp-Up Behavior

Figure 4. Ramp-Down Behavior

#### **Audio Amplifier**

The audio amplifier in the MAX8821 is a 2W Class D loudspeaker amplifier. The amplifier features a low-power shutdown mode and industry-leading click-and-pop suppression. The amplifier also features a programmable gain control through an I²C interface. The amplifier operates from a single 2.7V to 5.5V supply (VIN3 = VIN2) and features an internally generated common-mode bias voltage of VIN3 / 2 referenced to ground.

#### Click-and-Pop Suppression

The MAX8821 features Maxim's industry-leading click-and-pop suppression circuitry. During startup, the amplifier's common-mode bias voltage ramps to the DC bias point. When entering shutdown, the amplifier outputs are high impedance with  $100 \mathrm{k}\Omega$  between both inputs. This scheme minimizes the energy present in the audio band.

#### Class D Amplifier

The MAX8821 ultra-low-EMI, filterless, Class D audio power amplifier features several improvements to switch mode amplifier technology. The MAX8821 audio amplifier features output driver AEL circuitry to reduce EMI. Zero dead-time technology maintains state-of-theart efficiency and THD+N performance by allowing the output MOSFETs to switch simultaneously without cross-conduction.

A unique filterless modulation scheme and spread-spectrum mode create a compact, flexible, low-noise, efficient audio power amplifier while occupying minimal board space. The differential input architecture reduces common-mode noise pickup with or without the use of input-coupling capacitors. The MAX8821 audio amplifier can also be configured as a single-ended input amplifier without performance degradation. The input capacitors  $C_{IN}$  (Figure 7) are required for single-ended input applications and are typically 1µF.

The output of the MAX8821 shuts down if the output current reaches approximately 2A. Each output MOSFET has its own short-circuit protection. This protection scheme allows the amplifier to survive shorts to either supply rail. After a thermal overload or short circuit, the device remains disabled for a minimum of 110µs before attempting to return to normal operation. The amplifier shuts down immediately and waits another 110µs before turning on if the fault condition remains. This operation causes the output to pulse during a persistent fault.

Comparators monitor the MAX8821 inputs and compare the complementary input voltages to the sawtooth waveform. The comparators trip when the input magnitude of the sawtooth exceeds their corresponding input voltage.

Figure 5. Blink Timer Behavior

Both comparators reset at a fixed time after the rising edge of the second comparator trip point, generating a minimum width pulse ton(MIN) at the output of the second comparator. As the input voltage increases or decreases, the duration of the pulse at one output increases (the first comparator to trip), while the other output pulse duration remains at ton(MIN). This causes the net voltage across the speaker (SPK+ - SPK-) to change.

#### Adjustable Differential Gain

The audio amplifier has an internal gain control. The gain of the input amplifiers is controlled through the I<sup>2</sup>C interface. The gain setting of the input amplifier can be set from -3dB to +24dB (Table 15). This allows the amplifier to be used for both hands-free and for receiver mode without any external components.

#### Input Filter

The fully differential amplifier inputs can be biased at voltages other than midsupply. The common-mode feedback circuit adjusts for input bias, ensuring the outputs are still biased at midsupply. Input capacitors are not required as long as the common-mode input voltage is within the specified range listed in the *Electrical Characteristics* table. If input capacitors are used, input capacitor C<sub>IN</sub>, in conjunction with on-chip R<sub>INT</sub>, forms a highpass filter that removes the DC bias from an incoming signal. The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2 \times \pi \times R_{INT} \times C_{IN}}$$

Setting the -3dB corner too high affects the low-frequency response of the amplifier. Use capacitors with dielectrics that have low-voltage coefficients, such as aluminum electrolytic. Capacitors with high voltage coefficients, such as ceramics, can increase distortion at low frequencies.

18 \_\_\_\_\_\_\_ /V/X//V

Figure 6. Combining Ramp Function and Blink Timer (Tables 10 and 11)

#### LDO1 and LDO2

The linear regulators are designed for low dropout and low quiescent current to maximize battery life. Both LDOs are controlled through the I<sup>2</sup>C interface, minimizing the number of control lines to the MAX8821. Each LDO has an individual control register (LDO1\_CNTL and LDO2\_CNTL, Tables 13 and 14). The I<sup>2</sup>C interface controls the output voltages, and the enable/disable state for both LDO1 and LDO2.

#### Thermal Shutdown

The MAX8821 includes a thermal-limit circuit that shuts down the IC at a junction temperature of approximately +160°C. The IC turns on after it cools by approximately 20°C.

#### **Shutdown Mode**

The MAX8821 can be put into two different shutdown modes. The first shutdown mode is achieved by driving V<sub>DD</sub> low. In this mode, the I<sup>2</sup>C interface becomes disabled. The second shutdown is a lower power mode. To enter the low-power mode, disable LED\_, audio amplifier, and LDOs through I<sup>2</sup>C. In lower power mode, the I<sup>2</sup>C interface is still active.

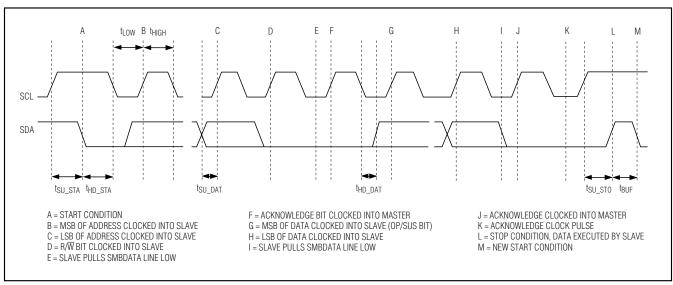

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C serial interface consists of a serial-data line (SDA) and a serial-clock line (SCL). Standard I<sup>2</sup>C write-byte commands are used. Figure 8 shows a timing diagram for the I<sup>2</sup>C protocol. The MAX8821 is a slave-only device, relying upon a master to generate a clock signal. The master (typically a microprocessor) initiates data transfer on the bus and generates SCL to permit data transfer. A master device communicates to the MAX8821 by transmitting the proper 8-bit address followed by the 8-bit control byte. Each transmit sequence is framed by a START (A) condition and a STOP (L) condition. Each word transmitted over the bus

Figure 7. Optional Input Capacitors

is 8 bits long and is always followed by an acknowledge clock pulse (K).

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (A) condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, the master issues a STOP (L) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission. One data bit is transferred during each clock pulse. The data on SDA must remain stable while SCL is high.

#### Register Reset

The I<sup>2</sup>C register is reset back to the default value when either  $V_{IN}$  drops below the UVLO threshold or  $V_{DD}$  is driven low.

# I<sup>2</sup>C Registers and Control I<sup>2</sup>C Address

The MAX8821 acts as a slave transmitter/receiver. The slave address of the MAX8821 is preset to 1001110X, where "X" is the R/W bit. The address 0x9C is designated for write operations and 0x9D for read operations.

Use Table 1 as a register map to reference the control bits found in Tables 2–16.

Figure 8. I2C Timing Diagram

## Table 1. Register Map

| NAME       | GROUP ADDRESS (hexadecimal) | TABLE | TYPE | DESCRIPTION                                                         |

|------------|-----------------------------|-------|------|---------------------------------------------------------------------|

| LED1_CNTL  | 00                          | 2     | R/W  | LED1 current regulator control                                      |

| LED2_CNTL  | 01                          | 3     | R/W  | LED2 current regulator control                                      |

| LED3_CNTL  | 02                          | 4     | R/W  | LED3 current regulator control                                      |

| LED4_CNTL  | 03                          | 5     | R/W  | LED4 current regulator control                                      |

| LED5_CNTL  | 04                          | 6     | R/W  | LED5 current regulator control                                      |

| LED6_CNTL  | 05                          | 7     | R/W  | LED6 current regulator control                                      |

| RAMP1_CNTL | 06                          | 8     | R/W  | LED1 and LED2 ramp control                                          |

| RAMP2_CNTL | 07                          | 9     | R/W  | LED3 and LED4 ramp control                                          |

| RAMP3_CNTL | 08                          | 10    | R/W  | LED5 and LED6 ramp control                                          |

| BLINK_CNTL | 09                          | 11    | R/W  | LED5 and LED6 blink control                                         |

| LED_EN     | 0A                          | 12    | R/W  | LED1-LED6 enable control                                            |

| LDO1_CNTL  | 0B                          | 13    | R/W  | LDO1 control                                                        |

| LDO2_CNTL  | 0C                          | 14    | R/W  | LDO2 control                                                        |

| AUDIO_CNTL | 0D                          | 15    | R/W  | Audio amplifier, control clock, and frequency                       |

| PUMP_CNTL  | 0E                          | 16    | R/W  | Charge-pump control setting and temperature derating enable/disable |

Table 2. LED1\_CNTL (Address 0x00)

CODE **DESCRIPTION** NAME B7, B6 N/A, do not use LED1 ramp-up/down 0 disabled. LED1\_RP\_EN В5 LED1 ramp-up/down enabled. 00000 0.1mA 00001 0.2mA 0.3mA 00010 00011 0.4mA 00100 0.5mA 00101 0.6mA 00110 0.7mA 00111 0.8mA 01000 1.0mA 01001 1.2mA 01010 1.4mA 01011 1.6mA 2.0mA 01100 2.4mA 01101 01110 2.8mA 01111 3.2mA B4-B0 LED1[4:0] 10000 4.0mA 10001 4.8mA 10010 5.6mA 10011 6.4mA 10100 8.0mA 10101 9.6mA 10110 11.2mA 12.8mA 10111 11000 14.4mA 11001 16.0mA 11010 17.6mA 11011 19.2mA 11100 20.8mA 11101 22.4mA 11110 24.0mA 11111 25.6mA

Note: Defaults in bold italics.

Table 3. LED2\_CNTL (Address 0x01)

| BIT    | NAME            | CODE DESCRIPTION |                                                                 |  |  |

|--------|-----------------|------------------|-----------------------------------------------------------------|--|--|

| B7, B6 | N/A, do not use |                  |                                                                 |  |  |

| B5     | LED2_RP_EN      | <b>0</b><br>1    | LED2 ramp-up/down<br>disabled.<br>LED2 ramp-up/down<br>enabled. |  |  |

|        |                 | 00000            | 0.1mA                                                           |  |  |

|        |                 | 00001            | 0.2mA                                                           |  |  |

|        |                 | 00010            | 0.3mA                                                           |  |  |

|        |                 | 00011            | 0.4mA                                                           |  |  |

|        |                 | 00100            | 0.5mA                                                           |  |  |

|        |                 | 00101            | 0.6mA                                                           |  |  |

|        |                 | 00110            | 0.7mA                                                           |  |  |

|        |                 | 00111            | 0.8mA                                                           |  |  |

|        |                 | 01000            | 1.0mA                                                           |  |  |

|        |                 | 01001            | 1.2mA                                                           |  |  |

|        |                 | 01010            | 1.4mA                                                           |  |  |

|        |                 | 01011            |                                                                 |  |  |

|        |                 | 01100            | 2.0mA                                                           |  |  |

|        |                 | 01101            | 2.4mA                                                           |  |  |

|        |                 | 01110            | 2.8mA                                                           |  |  |

| B4-B0  | LED2[4:0]       | 01111            | 3.2mA                                                           |  |  |

| D4-DU  | LED2[4.0]       | 10000            | 4.0mA                                                           |  |  |

|        |                 | 10001            | 4.8mA                                                           |  |  |

|        |                 | 10010            | 5.6mA                                                           |  |  |

|        |                 | 10011            | 6.4mA                                                           |  |  |

|        |                 | 10100            | 8.0mA                                                           |  |  |

|        |                 | 10101            | 9.6mA                                                           |  |  |

|        |                 | 10110            | 11.2mA                                                          |  |  |

|        |                 | 10111            | 12.8mA                                                          |  |  |

|        |                 | 11000            | 14.4mA                                                          |  |  |

|        |                 | 11001            | 16.0mA                                                          |  |  |

|        |                 | 11010            | 17.6mA                                                          |  |  |

|        |                 | 11011            | 19.2mA                                                          |  |  |

|        |                 | 11100            | 20.8mA                                                          |  |  |

|        |                 | 11101            | 22.4mA                                                          |  |  |

|        |                 | 11110            | 24.0mA                                                          |  |  |

|        |                 | 11111            | 25.6mA                                                          |  |  |

Note: Defaults in bold italics.

Table 4. LED3\_CNTL (Address 0x02)