###

### Wide-Input, High-Frequency, Triple-Output Supplies with Voltage Monitor and Power-On Reset

### **General Description**

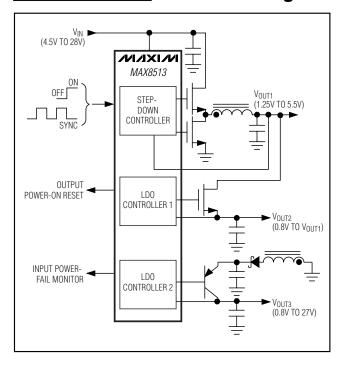

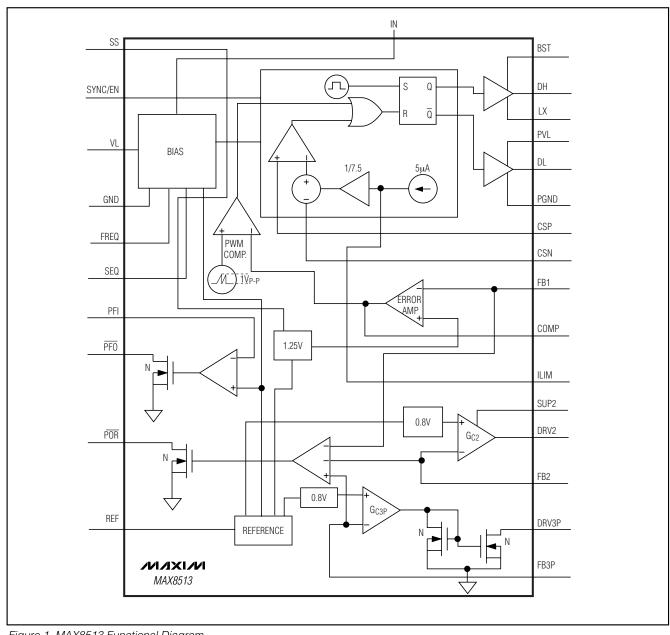

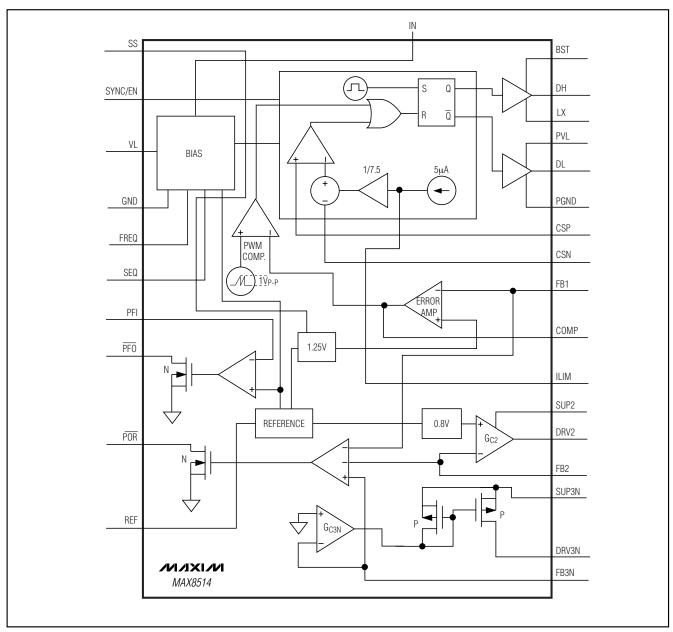

The MAX8513/MAX8514 integrate a voltage-mode PWM step-down DC-DC controller and two LDO controllers, a voltage monitor, and a power-on reset for the lowest-cost power-supply and monitoring solution for xDSL modems, routers, gateways, and set-top boxes.

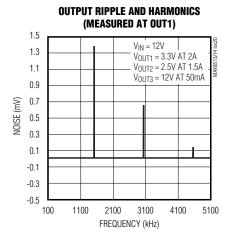

The DC-DC controller switching frequency can be set with an external resistor from 300kHz to 1.4MHz, to allow for the optimization of cost, size, and efficiency. For noisesensitive applications, the DC-DC controller can also be synchronized to an external clock, minimizing noise interference. Operation above 1.1MHz reduces noise for high data-rate xDSL applications. An adjustable soft-start and adjustable foldback current limit provide reliable startup and fault protection. The DC-DC controller output voltage can be set externally to a voltage from 1.25V to 5.5V. Current limiting is accomplished by inductor current sensing for improved efficiency, or by an external sense resistor for better accuracy.

The MAX8513/MAX8514s' first LDO controller is designed to provide a low-cost, high-current regulated output from 0.8V to 5.5V using an N-channel MOSFET or a low-current output using a low-cost NPN transistor. The MAX8513's second regulator can be used to generate 0.8V to 27V output with a low-cost PNP transistor. Both LDO regulators can operate either from the DC-DC controller output or from a higher voltage derived with a flyback overwinding on the DC-DC converter inductor. The MAX8514's second LDO regulator is designed to provide a negative output with an NPN transistor.

A sequence input allows the outputs to either power up together, or for the DC-DC regulator to power up first and each LDO controller to power up in sequence. An input power-fail output (PFO) is provided for input power-fail warning, such as in dying-gasp applications. A power-on reset circuit with a 140ms delay is also included to indicate when all outputs have achieved regulation and stabilized.

#### **Applications**

xDSL, Cable, ISDN Modems, and Routers Wireless Routers Set-Top Boxes

Automotive Dashboard Electronics

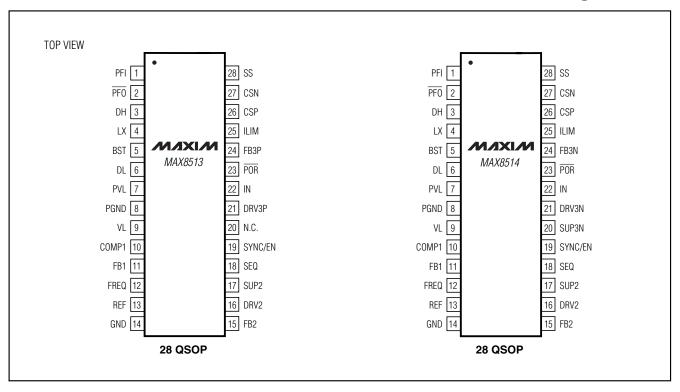

Pin Configurations appear at end of data sheet.

#### **Features**

- ◆ Low-Cost DC-DC Controller with Two LDOs

- Wide Input Range: 4.5V to 28V

- ♦ 300kHz to 1.4MHz Adjustable Switching Frequency

- ♦ Low Noise for High Data-Rate xDSL Applications

- ♦ Synchronizable to External Clock

- ◆ Adjustable Soft-Start

- ♦ Lossless Adjustable Foldback Current Limit

- ◆ Power-On Reset with 140ms Delay

- ◆ Adjustable Input Power-Fail Warning for Dying Gasp

- ♦ Selectable Output-Voltage Sequencing or **Output-Voltage Tracking**

### **Ordering Information**

| PART       | TEMP RANGE      | PIN-PACKAGE |

|------------|-----------------|-------------|

| MAX8513EEI | -40°C to +85°C  | 28 QSOP     |

| MAX8514EEI | -40°C to +85°C  | 28 QSOP     |

| MAX8514AEI | -40°C to +125°C | 28 QSOP     |

#### **Functional Diagram**

MIXIM

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN, DRV3P, SUP2 to GND        | 0.3V to +30V                                 |

|-------------------------------|----------------------------------------------|

| DRV2 to GND                   | 0.3V to (V <sub>SUP2</sub> + 0.3V)           |

| DRV3N to GND(Vs               | UP3N - 28V) to (VSUP3N + 0.3V)               |

| FREQ, PFI, PFO, POR, SUP3N, S |                                              |

| CSP, CSN to GND               | 0.3V to +6V                                  |

| VL to GND0.3V to the          | ne lesser of (V <sub>IN</sub> + 0.3V) or +6V |

| COMP1, FB1, FB2, FB3P, FB3N,  | , ,                                          |

| SS, SEQ to GND                | 0.3V to $(V_{VL} + 0.3V)$                    |

| PVL to PGND                   |                                              |

| DL to PGND                    | 0.3V to $(V_{PVL} + 0.3V)$                   |

| BST to LX                     | 0.3V to +6V                                  |

| DH to LX                      | 0.3V to $(V_{BST} + 0.3V)$                   |

|                               |                                              |

| PGND to GNDVL Short Circuit to GND | Continuous     |

|------------------------------------|----------------|

| 28-Pin QSOP (derate 10.8mW/°C ab   |                |

| Operating Temperature Range        |                |

| MAX8513EEİ, MAX8514EEI             | 40°C to +85°C  |

| MAX8514AEI                         | 40°C to +125°C |

| Junction Temperature               | +150°C         |

| Storage Temperature Range          |                |

| Lead Temperature (soldering, 10s)  |                |

|                                    |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{LX} = V_{SUP2} = 12V, V_{PVL} = V_{BST} - V_{LX} = V_{DRV3P} = 5V, V_{SUP3N} = 3.3V, V_{DRV3N} = -5V, C_{VL} = 4.7 \mu F, C_{REF} = 0.22 \mu F, R_{FREQ} = 15.0 k\Omega$ ,  $T_A = 0^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                 | SYMBOL                | CONDITIONS                                                                                                                           | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| GENERAL                                   |                       |                                                                                                                                      |       |      |       |       |

| IN Operating Dange                        |                       |                                                                                                                                      | 5.5   |      | 28.0  | V     |

| IN Operating Range                        |                       | IN = VL                                                                                                                              | 4.5   |      | 5.5   | V     |

| IN Supply Current                         |                       | V <sub>FB1</sub> = 1.3V, V <sub>FB2</sub> = V <sub>FB3</sub> = 1.0V, does not include switching current to PVL and BST, SYNC/EN = VL |       | 2.6  | 3.2   | mA    |

| IN Shutdown Current                       |                       | $V_{SYNC/EN} = 0$ , $R_{FREQ} = 50k\Omega$                                                                                           |       | 200  | 300   | μΑ    |

| VL REGULATOR                              |                       |                                                                                                                                      |       |      |       |       |

| VL Output Voltage                         |                       | $V_{IN} = 6V$ to 28V, $I_{VL} = 0.1$ mA to 40mA                                                                                      | 4.75  | 5    | 5.25  | V     |

| VL Dropout Voltage                        |                       | From IN to VL, $V_{IN} = 5V$ , $I_{VL} = 40mA$                                                                                       |       |      | 560   | mV    |

| VL Line Regulation                        |                       | $V_{IN} = 6V$ to 28V, $I_{VL} = 5mA$                                                                                                 |       | 0.05 |       | %     |

| VL Undervoltage Threshold                 |                       | VL rising, V <sub>HYST</sub> = 675mV (typ)                                                                                           | 3.6   |      | 4.2   | V     |

| OUT1 (BUCK CONVERTER)                     |                       |                                                                                                                                      |       |      |       |       |

| Output Voltage Range                      | V <sub>OUT1</sub>     | (Note 1)                                                                                                                             | 1.25  |      | 5.50  | V     |

| FB1 Regulation Threshold                  | V <sub>FB1</sub>      |                                                                                                                                      | 1.234 | 1.25 | 1.259 | V     |

| Error-Amplifier Open-Loop<br>Voltage Gain | Avol                  |                                                                                                                                      | 65    | 90   |       | dB    |

| FB1 Input Bias Current                    | IFB1_BIAS             | V <sub>FB1</sub> = 1.3V                                                                                                              | -200  | +10  | +200  | nA    |

| Error-Amplifier Gain Bandwidth            |                       |                                                                                                                                      |       | 25   |       | MHz   |

| DH Output-Resistance High                 | R <sub>DH_HIGH</sub>  |                                                                                                                                      |       | 1.5  | 2.55  | Ω     |

| DH Output-Resistance Low                  | R <sub>DH_LOW</sub>   |                                                                                                                                      |       | 1.2  | 2.1   | Ω     |

| DL Output-Resistance High                 | R <sub>DL_</sub> HIGH |                                                                                                                                      |       | 2.5  | 5     | Ω     |

| DL Output-Resistance Low                  | R <sub>DL_LOW</sub>   |                                                                                                                                      |       | 0.7  | 1.3   | Ω     |

| Driver Dead Time                          | t <sub>dt</sub>       | Starts from $V_{DL} = 1V$ or $(V_{DH} - V_{LX}) = 1V$                                                                                |       | 50   |       | ns    |

2 \_\_\_\_\_\_ *NIXIN*

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{LX} = V_{SUP2} = 12V, V_{PVL} = V_{BST} - V_{LX} = V_{DRV3P} = 5V, V_{SUP3N} = 3.3V, V_{DRV3N} = -5V, C_{VL} = 4.7 \mu F, C_{REF} = 0.22 \mu F, R_{FREQ} = 15.0 k\Omega, \textbf{T_A} = \textbf{0}^{\circ}\textbf{C}$  to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .)

| PARAMETER                                      | SYMBOL                | CON                                                                                    | DITIONS                           | MIN   | TYP   | MAX   | UNITS           |

|------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------|-----------------------------------|-------|-------|-------|-----------------|

|                                                |                       | VILIM = 2.00V, VCSN                                                                    | y = 0 to 5.5V                     | 246   | 275   | 300   |                 |

| Current-Limit Threshold (Positive)             | Vcs                   | VILIM = 0.50V, VCSN                                                                    | ı = 0 to 5.5V                     | 50    | 67    | 81    | mV              |

|                                                |                       | V <sub>ILIM</sub> = V <sub>VL</sub> , V <sub>CSN</sub> =                               | = 0 to 5.5V                       | 151   | 170   | 188   |                 |

|                                                |                       | VILIM = 2.00V, VCSN                                                                    | ı = 0 to 5.5V                     | -333  | -272  | -199  |                 |

| Current-Limit Threshold (Negative)             | Vcs                   | VILIM = 0.50V, VCSN                                                                    | ı = 0 to 5.5V                     | -90   | -67   | -42   | mV              |

| (Negative)                                     |                       | V <sub>ILIM</sub> = V <sub>VL</sub> , V <sub>CSN</sub> =                               | = 0 to 5.5V                       | -210  | -166  | -122  |                 |

| CSP and CSN Bias Current                       |                       | V <sub>CSP</sub> = V <sub>CSN</sub> = 0 to                                             | 5.5V                              | -120  |       | +135  | μΑ              |

| ILIM Bias Current                              |                       | V <sub>ILIM</sub> = 1.25V                                                              |                                   | -5.3  | -5    | -4.7  | μΑ              |

| SS Soft-Start Charge Current                   |                       | $V_{SS} = 0.6V$                                                                        |                                   | 15    | 25    | 35    | μΑ              |

| Soft-Start Discharge Resistance                |                       |                                                                                        |                                   |       | 100   | 200   | Ω               |

| LX, BST, PVL Leakage Current                   |                       | V <sub>L</sub> X = V <sub>I</sub> N = 28V, V <sub>E</sub><br>V <sub>S</sub> YNC/EN = 0 | 3ST = 33V, V <sub>PVL</sub> = 5V, |       | 0.03  | 20    | μΑ              |

| FB1 Power-On Reset Threshold                   |                       |                                                                                        |                                   | 1.08  | 1.125 | 1.20  | V               |

| OUT2 (POSITIVE LDO)                            |                       |                                                                                        |                                   | •     |       |       |                 |

| SUP2 Operating Range                           | V <sub>SUP2</sub>     | (Note 1)                                                                               |                                   | 4.5   |       | 28.0  | V               |

| DRV2 Clamp Voltage                             | V <sub>DRV2</sub>     | $V_{FB2} = 0.75V$                                                                      |                                   | 7.75  |       | 9.00  | V               |

| SUP2 Supply Current                            |                       |                                                                                        |                                   |       | 160   | 300   | μΑ              |

| SUP2 Shutdown Supply Current                   |                       | Vsync/en = 0                                                                           |                                   |       | 3     | 10    | μΑ              |

| FB2 Regulation Voltage                         | V <sub>FB2</sub>      |                                                                                        |                                   | 0.784 | 0.80  | 0.808 | V               |

| FB2 Input Bias Current                         | I <sub>FB2_BIAS</sub> | $V_{FB2} = 0.75V$                                                                      |                                   |       | 0.01  | 100   | nA              |

| DRV2 Output Current Limit                      |                       | $V_{IN} = 5V$ , $V_{DRV2} = 5$                                                         | $5V$ , $V_{FB2} = 0.77V$          | 15    | 30    |       | mA              |

| DRV2 Output Current Limit<br>During Soft-Start |                       | V <sub>IN</sub> = 6V, V <sub>DRV2</sub> = 5                                            | 5V, V <sub>FB2</sub> = 0.70V      | 8     | 10    | 12    | mA              |

| FB2 Power-On Reset Threshold                   |                       |                                                                                        |                                   | 0.690 | 0.720 | 0.742 | V               |

| FB2 to DRV2 Transconductance                   | G <sub>C2</sub>       | $I_{DRV2} = +250\mu A, -250\mu A$                                                      | 50μΑ                              | 0.12  | 0.2   | 0.36  | S               |

| OUT3P (POSITIVE PNP LDO) (MA                   | X8513 ONL             | Y)                                                                                     |                                   | •     |       |       |                 |

| DRV3P Operating Range                          | V <sub>DRV3P</sub>    |                                                                                        |                                   | 1     |       | 28    | V               |

| FB3P Regulation Voltage                        |                       | V <sub>DRV3P</sub> = 5V, I <sub>DRV3</sub>                                             | P = 1mA                           | 0.790 | 0.803 | 0.816 | V               |

| FB3P to DRV3P Large-Signal Transconductance    | G <sub>C3P</sub>      | $V_{DRV3P} = 5V$ , $I_{DRV3P} = 0.5$ mA to 5mA                                         |                                   | 0.38  | 0.6   | 1.1   | S               |

| Feedback Input Bias Current                    |                       | V <sub>FB3P</sub> = 0.75V                                                              |                                   |       | 0.01  | 100   | nA              |

| Deires Oigh Ouward                             |                       | 0.751/                                                                                 | DRV3P = 2.5V                      | 15    | 35    |       | 1               |

| Driver Sink Current                            |                       | $V_{FB3P} = 0.75V$                                                                     | DRV3P = 4.0V                      |       | 40    |       | mA              |

| FB3P POR Threshold                             |                       |                                                                                        | •                                 | 0.690 | 0.720 | 0.742 | V               |

| FB3P Soft-Start Period                         |                       |                                                                                        |                                   |       | 1312  |       | Clock<br>Cycles |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{LX} = V_{SUP2} = 12V, V_{PVL} = V_{BST} - V_{LX} = V_{DRV3P} = 5V, V_{SUP3N} = 3.3V, V_{DRV3N} = -5V, C_{VL} = 4.7 \mu F, C_{REF} = 0.22 \mu F, R_{FREQ} = 15.0 k \Omega, \textbf{T_A} = \textbf{0}^{\circ} \textbf{C} \textbf{ to +85}^{\circ} \textbf{C}, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ} \textbf{C}.)$

| PARAMETER                                   | SYMBOL           | CONDITIONS                                                                                  | MIN             | TYP  | MAX              | UNITS                |  |

|---------------------------------------------|------------------|---------------------------------------------------------------------------------------------|-----------------|------|------------------|----------------------|--|

| OUT3N (NEGATIVE NPN LDO C                   | ONTROLLER)       | ) (MAX8514 ONLY)                                                                            |                 |      |                  |                      |  |

| SUP3N Operating Range                       |                  | (Note 1)                                                                                    | 1.5             |      | 5.5              | V                    |  |

| DRV3N Operating Range                       |                  | (Note 1)                                                                                    | VSUP3N<br>- 21V |      | VSUP3N<br>- 1.5V | V                    |  |

| SUP3N Supply Current                        |                  | V <sub>DRV3N</sub> = 1.5V, V <sub>SUP3N</sub> = 3.5V,<br>I <sub>DRV3N</sub> = -1mA (source) |                 | 1.1  | 2                | mA                   |  |

| FB3N Regulation Voltage                     |                  | V <sub>DRV3N</sub> = 1.5V, V <sub>SUP3N</sub> = 3.5V,<br>I <sub>DRV3N</sub> = -1mA (source) | -20             | -5   | +10              | mV                   |  |

| FB3N to DRV3N Large-Signal Transconductance | G <sub>C3N</sub> | V <sub>DRV3N</sub> = 0, I <sub>DRV3N</sub> = -0.5mA to -5mA (source)                        | 0.225           | 0.36 | 0.550            | S                    |  |

| Feedback Input Bias Current                 |                  | V <sub>FB3N</sub> = -100mV                                                                  |                 | 60   | 1000             | nA                   |  |

| Driver Source Current                       |                  | V <sub>FB3N</sub> = 200mV, V <sub>DRV3N</sub> = 0,<br>V <sub>SUP3N</sub> = 3.5V             | 13              | 25   |                  | mA                   |  |

| FB3N POR Threshold                          |                  |                                                                                             | 450             | 500  | 550              | mV                   |  |

| FB3N Soft-Start Period                      |                  |                                                                                             |                 | 2048 |                  | Clock<br>Cycles      |  |

| REFERENCE                                   | •                |                                                                                             |                 |      |                  |                      |  |

| REF Output Voltage                          | V <sub>REF</sub> | -2μA < I <sub>REF</sub> < +50μA                                                             | 1.231           | 1.25 | 1.269            | V                    |  |

| OSCILLATOR                                  |                  |                                                                                             |                 |      |                  |                      |  |

|                                             |                  | $R_{FREQ} = 10.7 k\Omega \pm 1\%$ from FREQ to GND                                          | 1300            | 1390 | 1460             |                      |  |

| Frequency                                   | fS               | $R_{FREQ} = 15.0 \text{k}\Omega \pm 1\%$ from FREQ to GND                                   | 933             | 985  | 1040             | kHz                  |  |

|                                             |                  | R <sub>FREQ</sub> = $50.0$ k $Ω$ ±1% from FREQ to GND                                       | 260             | 290  | 324              |                      |  |

| FREQ Resistance-Frequency Product           |                  |                                                                                             |                 | 15.0 |                  | $MHz \times k\Omega$ |  |

| Mayiray va Duty Cyala                       |                  | $R_{FREQ} = 10.7 k\Omega \pm 1\%$ from FREQ to GND                                          | 77              | 83   | 91               |                      |  |

| Maximum Duty Cycle (Measured at DH Pin)     |                  | $R_{FREQ} = 15.0 k\Omega \pm 1\%$ from FREQ to GND                                          | 80              | 87   | 95               | %                    |  |

| (Modeland at 2111 m)                        |                  | $R_{FREQ} = 50.0 k\Omega \pm 1\%$ from FREQ to GND                                          | 93              | 96   | 99               |                      |  |

| Minimum On-Time<br>(Measured at DH Pin)     |                  | $R_{FREQ} = 10.7 k\Omega \pm 1\%$ from FREQ to GND                                          |                 | 20   | 62               | ns                   |  |

| SYNC/EN Pulse Width                         |                  | Low or high (Note 1)                                                                        | 200             |      |                  | ns                   |  |

| SYNC/EN Frequency Range                     |                  | SYNC/EN input frequency needs to be within ±30% of the value set at the FREQ pin (Note 1)   | 200             |      | 1850             | kHz                  |  |

| SYNC/EN Input Voltage, High                 |                  |                                                                                             | 2.4             |      |                  | V                    |  |

| SYNC/EN Input Voltage, Low                  |                  |                                                                                             |                 |      | 0.8              | V                    |  |

| SYNC/EN Input Current                       |                  | VSYNC/EN = 0 to 5.5V                                                                        | -1              |      | +1               | μΑ                   |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{LX} = V_{SUP2} = 12V, V_{PVL} = V_{BST} - V_{LX} = V_{DRV3P} = 5V, V_{SUP3N} = 3.3V, V_{DRV3N} = -5V, C_{VL} = 4.7 \mu F, C_{REF} = 0.22 \mu F, R_{FREQ} = 15.0 k\Omega, T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                   | SYMBOL | CONDITIO                                                                                                                                       | NS                                                          | MIN  | TYP   | MAX  | UNITS |

|-----------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|-------|------|-------|

| SEQ, PFI, PFO, POR          | •      |                                                                                                                                                |                                                             |      |       |      |       |

| SEQ Input-Voltage High      |        |                                                                                                                                                |                                                             | 2.4  |       |      | V     |

| SEQ Input-Voltage Low       |        |                                                                                                                                                |                                                             |      |       | 0.8  | V     |

| SEQ Input Current           |        | V <sub>SEQ</sub> = 0 to V <sub>V</sub> L                                                                                                       |                                                             |      | 1     | 10   | μΑ    |

|                             |        | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                                                          | $\overline{IPOR} = 1.6 \text{mA}$                           |      | 10    | 200  |       |

| POR Output-Voltage Low      |        | I VERSINI OUL-OI-LEGUIALIOLI I                                                                                                                 | $I\overline{POR} = 0.1\text{mA},$<br>$V_{IN} = 1.0\text{V}$ |      | 20    | 200  | mV    |

| POR Output Leakage Current  |        | V <sub>FB1</sub> , V <sub>FB2</sub> , and V <sub>FB3P</sub> or V <sub>FB3N</sub> , in-<br>regulation                                           |                                                             |      | 0.001 | 1    | μΑ    |

| POR Power-Ready Delay Time  |        | From V <sub>FB1</sub> , V <sub>FB2</sub> , and V <sub>FB3P</sub> or V <sub>FB3N</sub> , in-<br>regulation to $\overline{POR}$ = high impedance |                                                             | 140  | 315   | 560  | ms    |

| PFI Input Threshold         |        | Falling, V <sub>HYST</sub> = 20mV                                                                                                              |                                                             | 1.20 | 1.22  | 1.25 | V     |

| PFI Input Bias Current      |        | V <sub>PFI</sub> = 1.0V                                                                                                                        |                                                             |      | 0.1   | 100  | nA    |

|                             |        |                                                                                                                                                | $\overline{IPFO} = 1.6 \text{mA}$                           |      | 20    | 200  |       |

| PFO Output-Voltage Low      |        | PFI = 1.1V                                                                                                                                     | I <del>PFO</del> = 0.1mA,<br>V <sub>IN</sub> = 1.0V         |      | 10    | 200  | mV    |

| PFO Output Leakage Current  |        | PFI = 1.4V, <del>PFO</del> = 5V                                                                                                                |                                                             |      | 0.001 | 1    | μΑ    |

| THERMAL PROTECTION          | •      | •                                                                                                                                              |                                                             |      |       |      |       |

| Thermal Shutdown            |        | Junction temperature risir                                                                                                                     | Junction temperature rising +17                             |      | +170  |      | °C    |

| Thermal-Shutdown Hysteresis |        |                                                                                                                                                |                                                             |      | 25    |      | °C    |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{LX} = V_{SUP2} = 12V, V_{PVL} = V_{BST} - V_{LX} = V_{DRV3P} = 5V, V_{SUP3N} = 3.3V, V_{DRV3N} = -5V, C_{VL} = 4.7 \mu F, C_{REF} = 0.22 \mu F, R_{FREQ} = 15.0 k\Omega, T_A = -40 °C to +125 °C (Note 2), unless otherwise noted.)$

| PARAMETER                 | SYMBOL | SYMBOL CONDITIONS                                                                                |      | MAX  | UNITS |

|---------------------------|--------|--------------------------------------------------------------------------------------------------|------|------|-------|

| GENERAL                   |        |                                                                                                  |      |      |       |

| IN Operation Depart       |        |                                                                                                  | 5.5  | 28.0 | \/    |

| IN Operating Range        |        | IN = VL                                                                                          | 4.5  | 5.5  | V     |

| IN Supply Current         |        | VFB1 = 1.3V, VFB2 = VFB3 = 1.0V, does not include switching current to PVL and BST, SYNC/EN = VL |      | 3.2  | mA    |

| IN Shutdown Current       |        | $V_{SYNC/EN} = 0$ , $R_{FREQ} = 50k\Omega$                                                       |      | 300  | μΑ    |

| VL REGULATOR              |        |                                                                                                  |      |      |       |

| VL Output Voltage         |        | $V_{IN}$ = 6V to 28V, $I_{VL}$ = 0.1mA to 40mA                                                   | 4.75 | 5.25 | V     |

| VL Dropout Voltage        |        | From IN to VL, V <sub>IN</sub> = 5V, I <sub>VL</sub> = 40mA                                      |      | 610  | mV    |

| VL Undervoltage Threshold |        | VL rising, V <sub>HYST</sub> = 675mV (typ)                                                       | 3.6  | 4.2  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{LX} = V_{SUP2} = 12V, V_{PVL} = V_{BST} - V_{LX} = V_{DRV3P} = 5V, V_{SUP3N} = 3.3V, V_{DRV3N} = -5V, C_{VL} = 4.7 \mu F, C_{REF} = 0.22 \mu F, R_{FREQ} = 15.0 k\Omega$ ,  $T_A = -40 ^{\circ}C$  to  $+125 ^{\circ}C$  (Note 2), unless otherwise noted.)

| PARAMETER                                      | SYMBOL                | CONDITIONS                                                                                                        | MIN   | MAX   | UNITS |

|------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------|-------|-------|-------|

| OUT1 (BUCK CONVERTER)                          | •                     |                                                                                                                   | •     |       |       |

| Output Voltage Range                           | V <sub>OUT1</sub>     | (Note 1)                                                                                                          | 1.25  | 5.50  | V     |

| FB1 Regulation Threshold                       | V <sub>FB1</sub>      |                                                                                                                   | 1.225 | 1.265 | V     |

| Error-Amplifier Open-Loop<br>Voltage Gain      | Avol                  |                                                                                                                   | 65    |       | dB    |

| FB1 Input Bias Current                         | I <sub>FB1_BIAS</sub> | V <sub>FB1</sub> = 1.3V                                                                                           | -200  | +200  | nA    |

| DH Output-Resistance High                      | R <sub>DH_HIGH</sub>  |                                                                                                                   |       | 2.55  | Ω     |

| DH Output-Resistance Low                       | R <sub>DH_LOW</sub>   |                                                                                                                   |       | 2.1   | Ω     |

| DL Output-Resistance High                      | R <sub>DL_HIGH</sub>  |                                                                                                                   |       | 5     | Ω     |

| DL Output-Resistance Low                       | R <sub>DL_LOW</sub>   |                                                                                                                   |       | 1.3   | Ω     |

|                                                |                       | V <sub>ILIM</sub> = 2.00V, V <sub>CSN</sub> = 0 to 5.5V                                                           | 243   | 303   |       |

| Current-Limit Threshold (Positive)             | V <sub>CS</sub>       | V <sub>ILIM</sub> = 0.50V, V <sub>CSN</sub> = 0 to 5.5V                                                           | 49    | 83    | mV    |

| (FOSITIVE)                                     |                       | V <sub>ILIM</sub> = V <sub>VL</sub> , V <sub>CSN</sub> = 0 to 5.5V                                                | 147   | 190   |       |

|                                                |                       | V <sub>ILIM</sub> = 2.00V, V <sub>CSN</sub> = 0 to 5.5V                                                           | -333  | -199  |       |

| Current-Limit Threshold                        | Vcs                   | V <sub>ILIM</sub> = 0.50V, V <sub>CSN</sub> = 0 to 5.5V                                                           | -90   | -42   | mV    |

| (Negative)                                     |                       | V <sub>ILIM</sub> = V <sub>VL</sub> , V <sub>CSN</sub> = 0 to 5.5V                                                | -210  | -122  |       |

| CSP and CSN Bias Current                       |                       | $V_{CSP} = V_{CSN} = 0$ to 5.5V                                                                                   | -120  | +135  | μΑ    |

| ILIM Bias Current                              |                       | V <sub>ILIM</sub> = 1.25V                                                                                         | -5.7  | -4.3  | μΑ    |

| SS Soft-Start Charge Current                   |                       | V <sub>SS</sub> = 0.6V                                                                                            | 15    | 35    | μΑ    |

| Soft-Start Discharge Resistance                |                       |                                                                                                                   |       | 200   | Ω     |

| LX, BST, PVL Leakage Current                   |                       | V <sub>L</sub> X = V <sub>IN</sub> = 28V, V <sub>BST</sub> = 33V, V <sub>PVL</sub> = 5V, V <sub>SYNC/EN</sub> = 0 |       | 20    | μΑ    |

| FB1 Power-On Reset Threshold                   |                       |                                                                                                                   | 1.08  | 1.20  | V     |

| OUT2 (POSITIVE LDO)                            |                       |                                                                                                                   |       |       |       |

| SUP2 Operating Range                           | V <sub>SUP2</sub>     | (Note 1)                                                                                                          | 4.5   | 28.0  | V     |

| DRV2 Clamp Voltage                             | V <sub>DRV2</sub>     | $V_{FB2} = 0.75V$                                                                                                 | 7.75  | 9.00  | V     |

| SUP2 Supply Current                            |                       |                                                                                                                   |       | 300   | μΑ    |

| SUP2 Shutdown Supply Current                   |                       | VSYNC/EN = 0                                                                                                      |       | 10    | μΑ    |

| FB2 Regulation Voltage                         | V <sub>FB2</sub>      |                                                                                                                   | 0.775 | 0.816 | V     |

| FB2 Input Bias Current                         | I <sub>FB2_BIAS</sub> | $V_{FB2} = 0.75V$                                                                                                 |       | 150   | nA    |

| DRV2 Output Current Limit                      |                       | V <sub>IN</sub> = 5V, V <sub>DRV2</sub> = 5V, V <sub>FB2</sub> = 0.77V                                            | 12    |       | mA    |

| DRV2 Output Current Limit<br>During Soft-Start |                       | V <sub>IN</sub> = 6V, V <sub>DRV2</sub> = 5V, V <sub>FB2</sub> = 0.70V                                            | 8     | 12    | mA    |

| FB2 Power-On Reset Threshold                   |                       |                                                                                                                   | 0.690 | 0.742 | V     |

| FB2 to DRV2 Transconductance                   | G <sub>C2</sub>       | I <sub>DRV2</sub> = +250μA, -250μA                                                                                | 0.11  | 0.41  | S     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{LX} = V_{SUP2} = 12V, V_{PVL} = V_{BST} - V_{LX} = V_{DRV3P} = 5V, V_{SUP3N} = 3.3V, V_{DRV3N} = -5V, C_{VL} = 4.7 \mu F, C_{REF} = 0.22 \mu F, R_{FREQ} = 15.0 k\Omega, \textbf{T_A} = -40 ^{\circ}\textbf{C} \text{ to } +125 ^{\circ}\textbf{C} \text{ (Note 2), unless otherwise noted.)}$

| PARAMETER                                   | SYMBOL             | CONDITIONS                                                                                  | MIN             | MAX                          | UNITS |

|---------------------------------------------|--------------------|---------------------------------------------------------------------------------------------|-----------------|------------------------------|-------|

| OUT3P (POSITIVE PNP LDO) (N                 |                    |                                                                                             |                 |                              |       |

| DRV3P Operating Range                       | V <sub>DRV3P</sub> |                                                                                             | 1               | 28                           | V     |

| FB3P Regulation Voltage                     |                    | V <sub>DRV3P</sub> = 5V, I <sub>DRV3P</sub> = 1mA                                           | 0.780           | 0.820                        | V     |

| FB3P to DRV3P Large-Signal Transconductance | G <sub>C3P</sub>   | V <sub>DRV3P</sub> = 5V, I <sub>DRV3P</sub> = 0.5mA to 5mA                                  | 0.3             | 1.4                          | S     |

| Feedback Input Bias Current                 |                    | V <sub>FB3P</sub> = 0.75V                                                                   |                 | 100                          | nA    |

| Driver Sink Current                         |                    | V <sub>FB3P</sub> = 0.75V DRV3P = 2.5V                                                      | 15              |                              | mA    |

| FB3P POR Threshold                          |                    | '                                                                                           | 0.690           | 0.742                        | V     |

| OUT3N (NEGATIVE NPN LDO                     | ONTROLLER          | ) (MAX8514 ONLY)                                                                            | •               |                              |       |

| SUP3N Operating Range                       |                    | (Note 1)                                                                                    | 1.5             | 5.5                          | V     |

| DRV3N Operating Range                       |                    | (Note 1)                                                                                    | VSUP3N<br>- 21V | V <sub>SUP3N</sub><br>- 1.5V | V     |

| SUP3N Supply Current                        |                    | V <sub>DRV3N</sub> = 1.5V, V <sub>SUP3N</sub> = 3.5V,<br>I <sub>DRV3N</sub> = -1mA (source) |                 | 2                            | mA    |

| FB3N Regulation Voltage                     |                    | V <sub>DRV3N</sub> = 1.5V, V <sub>SUP3N</sub> = 3.5V,<br>I <sub>DRV3N</sub> = -1mA (source) | -20             | +10                          | mV    |

| FB3N to DRV3N Large-Signal Transconductance | G <sub>C3N</sub>   | V <sub>DRV3N</sub> = 0, I <sub>DRV3N</sub> = -0.5mA to -5mA (source)                        | 0.225           | 0.550                        | S     |

| Feedback Input Bias Current                 |                    | V <sub>FB3N</sub> = -100mV                                                                  |                 | 1500                         | nA    |

| Driver Source Current                       |                    | $V_{FB3N} = 200 \text{mV}, V_{DRV3N} = 0, V_{SUP3N} = 3.5 \text{V}$                         | 13              |                              | mA    |

| FB3N POR Threshold                          |                    |                                                                                             | 450             | 550                          | mV    |

| REFERENCE                                   |                    |                                                                                             |                 |                              |       |

| REF Output Voltage                          | V <sub>REF</sub>   | -2μA < I <sub>REF</sub> < +50μA                                                             | 1.22            | 1.27                         | V     |

| OSCILLATOR                                  |                    |                                                                                             |                 |                              |       |

|                                             |                    | $R_{FREQ} = 10.7 k\Omega \pm 1\%$ from FREQ to GND                                          | 1300            | 1500                         |       |

| Frequency                                   | fs                 | $R_{FREQ} = 15.0 k\Omega \pm 1\%$ from FREQ to GND                                          | 917             | 1070                         | kHz   |

|                                             |                    | $R_{FREQ} = 50.0 k\Omega \pm 1\%$ from FREQ to GND                                          | 250             | 335                          |       |

|                                             |                    | $R_{FREQ} = 10.7 k\Omega \pm 1\%$ from FREQ to GND                                          | 77              | 91                           |       |

| Maximum Duty Cycle<br>(Measured at DH Pin)  |                    | $R_{FREQ} = 15.0 \text{k}\Omega \pm 1\%$ from FREQ to GND                                   | 80              | 95                           | %     |

| (Measured at DITT III)                      |                    | $R_{FREQ} = 50.0 k\Omega \pm 1\%$ from FREQ to GND                                          | 93              | 99                           |       |

| Minimum On-Time<br>(Measured at DH Pin)     |                    | $R_{FREQ} = 10.7 k\Omega \pm 1\%$ from FREQ to GND                                          |                 | 62                           | ns    |

| SYNC/EN Pulse Width                         |                    | Low or high (Note 1)                                                                        | 200             |                              | ns    |

| SYNC/EN Frequency Range                     |                    | SYNC/EN input frequency needs to be within ±30% of the value set at the FREQ pin (Note 1)   | 200             | 1850                         | kHz   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{LX} = V_{SUP2} = 12V, V_{PVL} = V_{BST} - V_{LX} = V_{DRV3P} = 5V, V_{SUP3N} = 3.3V, V_{DRV3N} = -5V, C_{VL} = 4.7 \mu F, C_{REF} = 0.22 \mu F, R_{FREQ} = 15.0 k\Omega, \textbf{T_A} = -40 ^{\circ}\textbf{C} \textbf{ to +125 ^{\circ}\textbf{C}} \text{ (Note 2), unless otherwise noted.)}$

| PARAMETER                                     | SYMBOL | CONDITIO                                                                                | NS                                                               | MIN  | MAX  | UNITS |

|-----------------------------------------------|--------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------|------|------|-------|

| SYNC/EN Input-Voltage High                    |        |                                                                                         |                                                                  | 2.4  |      | V     |

| SYNC/EN Input-Voltage Low                     |        |                                                                                         |                                                                  |      | 0.8  | V     |

| SYNC/EN Input Current                         |        | $V_{SYNC/EN} = 0 \text{ to } 5.5V$                                                      |                                                                  | -1   | +1   | μΑ    |

| SEQ, PFI, $\overline{PFO}$ , $\overline{POR}$ |        |                                                                                         |                                                                  |      |      |       |

| SEQ Input-Voltage High                        |        |                                                                                         |                                                                  | 2.4  |      | V     |

| SEQ Input-Voltage Low                         |        |                                                                                         |                                                                  |      | 8.0  | V     |

| SEQ Input Current                             |        | $V_{SEQ} = 0$ to $V_{VL}$                                                               |                                                                  |      | 10   | μΑ    |

|                                               |        |                                                                                         | $\overline{IPOR} = 1.6mA$                                        |      | 200  |       |

| POR Output-Voltage Low                        |        | I VERSNI OUI-OI-TEGUIATION I                                                            | $I_{\overline{POR}} = 0.1 \text{mA},$<br>$V_{IN} = 1.0 \text{V}$ |      | 200  | mV    |

| POR Output Leakage Current                    |        | VFB1, VFB2, and VFB3P or VFB3N, in-<br>regulation                                       |                                                                  |      | 1    | μА    |

| POR Power-Ready Delay Time                    |        | From V <sub>FB1</sub> , V <sub>FB2</sub> , and V <sub>FI</sub> regulation to POR = high |                                                                  | 140  | 560  | ms    |

| PFI Input Threshold                           |        | Falling, V <sub>HYST</sub> = 20mV                                                       |                                                                  | 1.20 | 1.25 | V     |

| PFI Input Bias Current                        |        | V <sub>PFI</sub> = 1.0V                                                                 |                                                                  |      | 300  | nA    |

| PFO Output-Voltage Low                        |        |                                                                                         | IPFO = 1.6mA                                                     |      | 200  |       |

|                                               |        | PFI = 1.1V                                                                              | $I_{\overline{PFO}} = 0.1 \text{mA},$<br>$V_{IN} = 1.0 \text{V}$ |      | 200  | mV    |

| PFO Output Leakage Current                    |        | PFI = 1.4V, PFO = 5V                                                                    |                                                                  |      | 1    | μΑ    |

Note 1: Guaranteed by design, not production tested.

Note 2: Specifications to -40°C are guaranteed by design, not production tested.

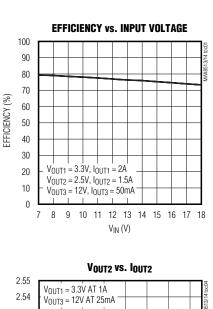

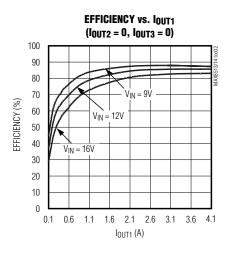

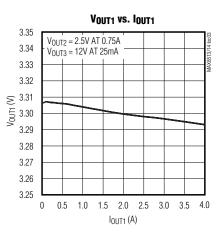

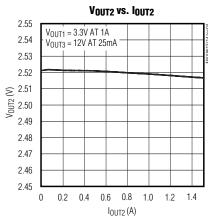

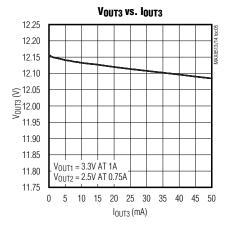

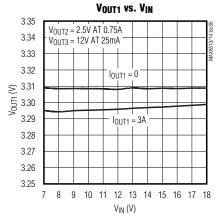

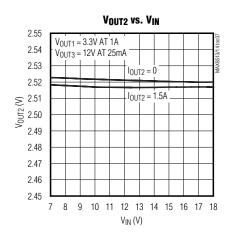

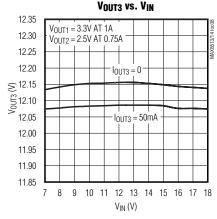

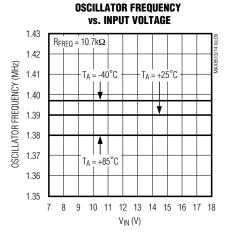

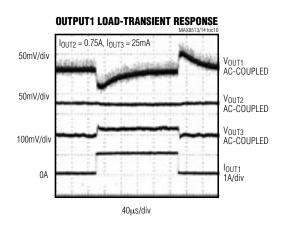

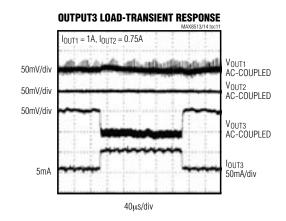

### **Typical Operating Characteristics**

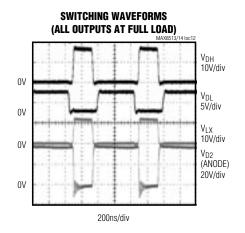

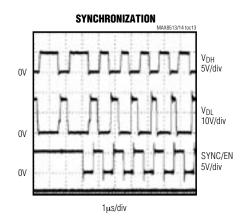

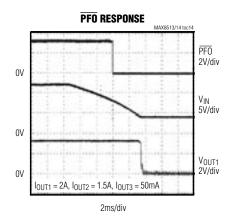

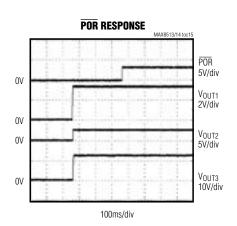

(Circuit of MAX8513 evaluation kit,  $V_{IN} = 12V$ ,  $T_A = +25$ °C,  $f_S = 1.4$ MHz, unless otherwise noted.)

MIXIM

### Typical Operating Characteristics (continued)

(Circuit of MAX8513 evaluation kit, VIN = 12V, TA = +25°C, fs = 1.4MHz, unless otherwise noted.)

10 \_\_\_\_\_\_\_/N/1XI/M

### Typical Operating Characteristics (continued)

(Circuit of MAX8513 evaluation kit,  $V_{IN} = 12V$ ,  $T_A = +25^{\circ}C$ ,  $f_S = 1.4$ MHz, unless otherwise noted.)

### **Pin Description**

| PIN<br>NAME | MAX8513 | MAX8514 | FUNCTION                                                                                                                                                                                                                                                                                                      |

|-------------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFI         | 1       | 1       | Power-Fail Input. Connect PFI to an external resistive-divider between IN, PFI, and GND. PFI senses V <sub>IN</sub> to detect voltage failure. Trip falling threshold at this input is 1.22V, with 20mV of hysteresis.                                                                                        |

| PFO         | 2       | 2       | Power-Fail Output. Open-drain output that goes low if V <sub>PFI</sub> < 1.22V.                                                                                                                                                                                                                               |

| DH          | 3       | 3       | OUT1 High-Side Gate-Drive Output. DH drives the high-side N-channel MOSFET (Q1 in the <i>Typical Applications Circuits</i> ). DH is a floating driver output that swings from LX to BST.                                                                                                                      |

| LX          | 4       | 4       | OUT1 High-Side Driver Return Path. The high-side FET driver uses BST and LX for its respective high and low-side supplies.                                                                                                                                                                                    |

| BST         | 5       | 5       | OUT1 Boost Capacitor Connection for High-Side Gate Drive. Connect a 0.1µF ceramic capacitor from BST to LX with a less than 5mm trace length.                                                                                                                                                                 |

| DL          | 6       | 6       | OUT1 Low-Side Gate-Drive Output. DL drives the low-side N-channel MOSFET (Q2 in the <i>Typical Applications Circuits</i> ). DL swings from 0 to V <sub>PVL</sub> .                                                                                                                                            |

| PVL         | 7       | 7       | OUT1 Gate-Drive Supply Bypass Connection. Connect PVL to VL through a $10\Omega$ resistor (R15), and bypass PVL to PGND with a minimum $1\mu$ F capacitor (C1).                                                                                                                                               |

| PGND        | 8       | 8       | Power-Ground Connection and Low-Side Supply for DI Driver                                                                                                                                                                                                                                                     |

| VL          | 9       | 9       | Internal +5V Linear-Regulator Bypass Pin. Bypass VL to GND with a minimum 2.2µF ceramic capacitor (C10) and 5mm or less of trace length. VL should be connected to IN when V <sub>IN</sub> < 5.5V.                                                                                                            |

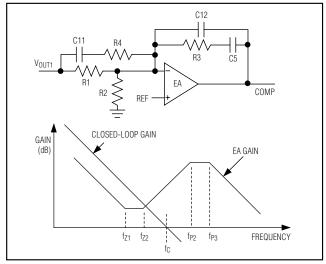

| COMP1       | 10      | 10      | OUT1 Compensation Node. See the OUT1 Compensation section.                                                                                                                                                                                                                                                    |

| FB1         | 11      | 11      | OUT1 Feedback Input. Connect a resistive-divider (R1, R2) from OUT1 to FB1 to GND to regulate FB1 at 1.25V.                                                                                                                                                                                                   |

| FREQ        | 12      | 12      | Oscillator Frequency-Set Input. A resistor from FREQ to GND sets the oscillator frequency from 300kHz to 1.4MHz (f = 15MHz x k $\Omega$ / RFREQ). RFREQ is still required if an external clock is used at SYNC/EN, and the SYNC/EN input frequency should be within $\pm 30\%$ of the frequency set by RFREQ. |

| REF         | 13      | 13      | 1.25V Reference Output. Connect a 0.1µF or larger ceramic capacitor (C9) from REF to GND.                                                                                                                                                                                                                     |

| GND         | 14      | 14      | Analog/Signal Ground                                                                                                                                                                                                                                                                                          |

| FB2         | 15      | 15      | OUT2 Feedback Input. Connect a resistive-divider (R5, R6) from OUT2 to FB2 to GND to regulate FB2 to 0.8V.                                                                                                                                                                                                    |

| DRV2        | 16      | 16      | OUT2 Gate Drive. DRV2 connects to the gate of an external N-channel MOSFET to form a positive linear voltage regulator.                                                                                                                                                                                       |

| SUP2        | 17      | 17      | Supply Input for DRV2. Connect to a voltage source of at least 1V above the maximum desired DRV2 gate voltage.                                                                                                                                                                                                |

### Pin Description (continued)

| PIN MAYOS40 MAYOS44 FUNOTION |         |         |                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                         | MAX8513 | MAX8514 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                          |

| SEQ                          | 18      | 18      | Connect to VL for output tracking. Connect to GND for output staggered sequence. Staggered sequence ramps up V <sub>OUT2</sub> and V <sub>OUT3</sub> softly to avoid glitches on the previous voltage due to charging of the LDO's output capacitors.                                                                                                                             |

| SYNC/EN                      | 19      | 19      | Shutdown Control and Synchronization Input. There are three operating modes:  When SYNC/EN is low, the controller is off but the VL regulator is still running.  When SYNC/EN is high, the controller is enabled with the switching frequency set by RFREQ.  When SYNC/EN is driven by an external clock, the controller is enabled and switches at the external clock frequency. |

| N.C.                         | 20      | _       | No Connection. Not internally connected. Connect to GND or leave floating.                                                                                                                                                                                                                                                                                                        |

| SUP3N                        | _       | 20      | OUT3N Base-Drive Supply. Connect SUP3N to any positive voltage between 1.5V and 5.5V to provide power for the negative linear-regulator transistor driver.                                                                                                                                                                                                                        |

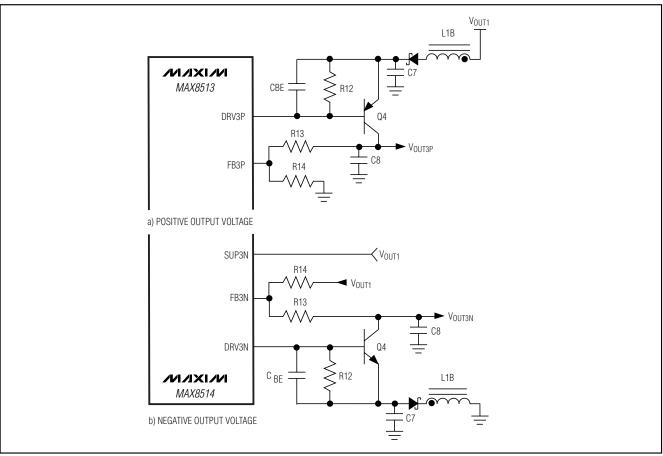

| DRV3P                        | 21      | _       | OUT3P Base Drive. Connect DRV3P to the base of an external PNP pass transistor to form a positive linear voltage regulator.                                                                                                                                                                                                                                                       |

| DRV3N                        | _       | 21      | OUT3N Base Drive. Connect DRV3N to the base of an external NPN pass transistor to form a negative linear voltage regulator.                                                                                                                                                                                                                                                       |

| IN                           | 22      | 22      | Main Voltage Input (4.5V to 28V). Bypass IN to GND, close to the IC, with a minimum 1µF ceramic capacitor (C2). IN powers the linear regulator whose output is VL.                                                                                                                                                                                                                |

| POR                          | 23      | 23      | Power-On Reset. Open-drain output that goes high after all outputs reach the regulation limit and a 315ms delay time has elapsed.                                                                                                                                                                                                                                                 |

| FB3P                         | 24      | _       | OUT3P Feedback Input. FB3P is referenced to 0.8V and connects to a resistive-divider (R13, R14) to control a positive linear voltage regulator.                                                                                                                                                                                                                                   |

| FB3N                         | _       | 24      | OUT3N Feedback Input. Connect a resistive-divider (R13, R14) from OUT1 to FB3N to OUT3N to regulate FB3N to 0V.                                                                                                                                                                                                                                                                   |

| ILIM                         | 25      | 25      | ILIM Set Input. Connect a resistive-divider (R17, R18) from OUT1 to ILIM to GND. See the <i>Current Limit</i> section.                                                                                                                                                                                                                                                            |

| CSP                          | 26      | 26      | Positive Current-Sense Input. Used to detect OUT1 current limit.                                                                                                                                                                                                                                                                                                                  |

| CSN                          | 27      | 27      | Negative Current-Sense Input. Used to detect OUT1 current limit.                                                                                                                                                                                                                                                                                                                  |

| SS                           | 28      | 28      | Analog Soft-Start Control Input. This pin goes into the positive input of the VOUT1's error amplifier. When the MAX8513/MAX8514 are turned on, SS is at GND and charges up to 1.25V with a constant 25µA. Connect a capacitor (C13) from SS to GND for the desired soft-start time.                                                                                               |

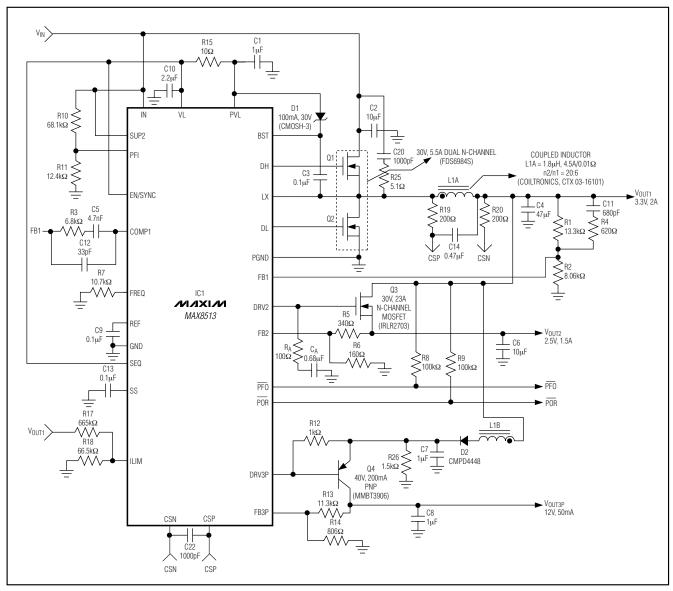

Figure 1. MAX8513 Functional Diagram

MIXIM 14

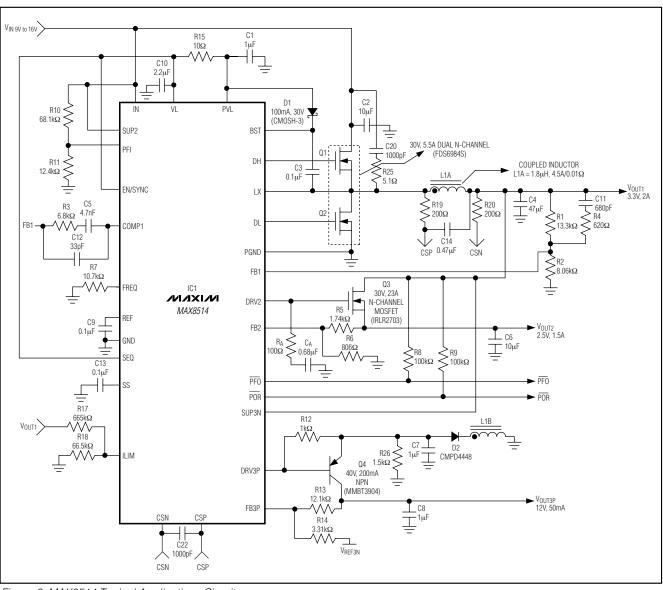

Figure 2. MAX8514 Functional Diagram

### **Detailed Description**

The MAX8513/MAX8514 combine a step-down DC-DC converter and two LDOs, providing three output voltages for xDSL modem and set-top box applications. The switching frequency is set with an external resistor connected from the FREQ pin to GND, and is adjustable from 300kHz to 1.4MHz. The main stepdown DC-DC controller operates in a voltage-mode, pulse-width-modulation (PWM) control scheme. The MAX8513/MAX8514 include two low-cost LDO controllers capable of delivering current from the DC-DC main output, an extra winding, the input, or from an alternate supply voltage. The first LDO controller drives an external NMOS or NPN with a maximum drive of 7.75V. The second LDO controller provides either a positive 0.8V to 27V output using an external PNP pass device, or a negative -1V to -18V output with an external NPN pass device.

#### **DC-DC Controller**

The MAX8513/MAX8514 step-down DC-DC converters use a PWM voltage-mode control scheme. An internal high-bandwidth (25MHz) operational amplifier is used as an error amplifier to regulate the output voltage. The output voltage is sensed and compared with an internal 1.25V reference to generate an error signal. The error signal is then compared with a fixed-frequency ramp by a PWM comparator to give the appropriate duty cycle to maintain output-voltage regulation. At the rising edge of the internal clock and when DL (the lowside MOSFET gate drive) is at 0V, the high-side MOSFET turns on. When the ramp voltage reaches the error-amplifier output voltage, the high-side MOSFET latches off until the next clock pulse. During the highside MOSFET on-time, current flows from the input through the inductor to the output capacitor and load. At the moment the high-side MOSFET turns off, the energy stored in the inductor during the on-time is released to support the load. The inductor current ramps down through the low-side MOSFET body diode. After a fixed delay, the low-side MOSFET turns on to shunt the current from its body diode for a lower voltage drop to increase the efficiency. The low-side MOSFET turns off at the rising edge of the next clock pulse, and when its gate voltage discharges to zero, the high-side MOSFET turns on after an additional fixed delay and another cycle starts.

The MAX8513/MAX8514 operate in forced-PWM mode, so even under light load the controller maintains a constant switching frequency to minimize noise and possible interference with system circuitry.

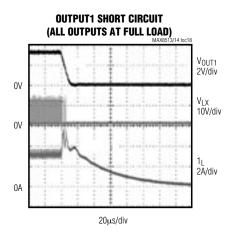

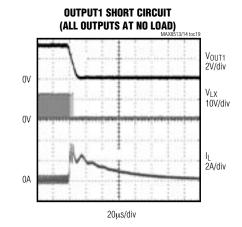

#### **Current Limit**

The MAX8513/MAX8514s' switching regulator senses the inductor current either through the DC resistance of the inductor itself for lossless sensing, or through a series resistor for more accurate sensing. When using the DC resistance of the inductor, an RC filter circuit is needed (see R19, R20, and C14 of the Typical Applications Circuits and the Current-Limit Setting section). When peak voltage across the sensing circuit (which occurs at the peak of the inductor current) exceeds the current-limit threshold set by ILIM, the controller turns off the high-side MOSFET and turns on the low-side MOSFET. The inductor current ramps down and DH turns on again if the inductor current is below the current-limit threshold at the next clock pulse. The MAX8513/MAX8514 current-limit threshold can be set by two external resistors to be proportional to the output voltage with an adjustable offset level, providing foldback current-limit and short-circuit protection. This feature greatly reduces power dissipation and prevents overheating of external components during an indefinite short-circuit at the output. See the Foldback Current Limit section for how to set ILIM with external resistors. The current-limit threshold defaults to 170mV when ILIM is connected to VL, and in this case, the current limit functions as a constant current limit only. The LDO controllers do not have current limit and rely on input current limit for protection.

#### **Synchronous-Rectifier Driver (DL)**

Synchronous rectification reduces the conduction loss in the rectifier by replacing the normal Schottky catch diode with a low-on-resistance MOSFET switch. The MAX8513/MAX8514 also use the synchronous rectifier to ensure proper startup of the boost gate-drive circuit.

#### **High-Side Gate-Drive Supply (BST)**

A flying-capacitor boost circuit (see D1 and C3 in the *Typical Applications Circuits*) generates the gate-drive voltage for the high-side N-channel MOSFET. On startup, the synchronous rectifier (low-side MOSFET, Q2) forces LX to ground and charges the boost capacitor (C3) to V<sub>VL</sub> - V<sub>DIODE</sub>. On the second half-cycle, the controller turns on the high-side MOSFET by closing an internal switch between BST and DH. This boosts the voltage at BST to V<sub>VL</sub> - V<sub>DIODE</sub> + V<sub>IN</sub>, providing the necessary gate-to-source voltage to turn on the high-side N-channel MOSFET.

#### **Internal 5V Linear Regulator**

All MAX8513/MAX8514 functions (except for the positive output LDO with an NFET or NPN, and the negative LDO on the MAX8514) are powered from the on-chip low-dropout 5V regulator with its input connected to IN. Bypass the regulator's output (VL) with a  $2.2\mu F$  or greater ceramic capacitor. The V<sub>IN</sub> to V<sub>VL</sub> dropout voltage is typically 350mV, so when V<sub>IN</sub> is greater than 5.5V, V<sub>VL</sub> is typically 5V. If V<sub>IN</sub> is between 4.5V and 5.5V, short VL to IN.

#### **Undervoltage Lockout**

If V<sub>VL</sub> drops below 3.8V, the MAX8513/MAX8514 assume that the supply voltage is too low to make valid decisions. When this happens, the undervoltage lockout (UVLO) circuitry inhibits switching, forces POR and PFO low, and forces DL and DH gate drivers low. After V<sub>VL</sub> rises above 3.9V, the controller powers up the outputs (see the *Startup* section).

#### Startup

The MAX8513/MAX8514 start switching when V<sub>V</sub>L rises above the 3.9V UVLO threshold. However, the controller is not enabled unless all three of the following conditions are met:

- 1) V<sub>VL</sub> exceeds the 3.9V UVLO threshold.

- The internal reference exceeds 90% of its nominal value.

- 3) The thermal limit is not exceeded.

Once the MAX8513/MAX8514 assert the internal enable signal, the step-down controller starts switching and enables soft-start. The soft-start circuitry gradually ramps up to the reference voltage to control the rate-of-rise of the step-down controller and reduce input surge currents. The soft-start period is determined by the value of the capacitor from SS to GND (C13 in the *Typical Applications Circuits*). SS sources a constant 25µA to charge the soft-start capacitor to 1.25V.

#### **Output-Voltage Sequencing**

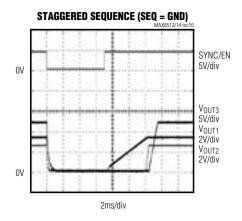

The MAX8513/MAX8514 can power up in either staggered-output sequencing or output tracking. For staggered-output sequencing, connect SEQ to GND. In this configuration, V<sub>OUT1</sub> comes up first. When it reaches 90% of the nominal regulated value, V<sub>OUT2</sub> is softly turned on. Once V<sub>OUT2</sub> reaches 90% of its nominal regulated value, V<sub>OUT3</sub> is softly turned on. Individual soft-start

on OUT2 and OUT3 eliminates glitches on the previous stages due to the charging of output capacitors. See the *Typical Operating Characteristics* section for the startup and staggered-output-sequence waveforms.

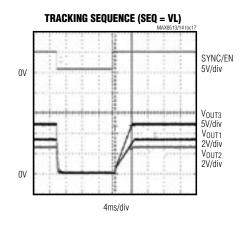

#### **Output-Voltage Tracking**

When SEQ is connected to VL, all outputs rise up at the same time and the external series pass transistors are driven fully on until reaching the respective regulation limits. Since the LDOs are powered from the main DC-DC step-down converter, either directly or through a coupled winding on the inductor, their outputs track the DC-DC step-down output (OUT1). See the *Typical Operating Characteristics* section for the startup output-tracking waveforms.

#### **Power-On Reset**

The MAX8513/MAX8514 provide a power-on-reset (POR) signal, which goes high 315ms after all outputs reach 90% of their nominal regulated value. Therefore, by the time POR goes high, all outputs are already stabilized at nominal regulated voltages. See the *Typical Operating Characteristics* section for the POR waveforms.

#### Input Power-Fail (PFI and PFO)

The MAX8513/MAX8514 have a built-in comparator to detect the input voltage with an external resistive-divider at PFI, with a threshold of 1.22V. When the input voltage drops and trips this comparator, the power-fail output (PFO) goes low, while all outputs are still within regulation limits. This is typically used for input power-fail warning for orderly system shutdown. The amount of warning time depends on the input storage capacitor, the input PFI trip voltage level, the main step-down output voltage, the total output power, and the efficiency. See the *Design Procedure* section for how to calculate the input capacitor to meet the required warning time.

#### **Enable and Synchronization**

The MAX8513/MAX8514 can be turned on with logic high, and off with logic low at SYNC/EN. When SYNC/EN is driven with an external clock, the internal oscillator synchronizes the rising edge of the clock at SYNC/EN to DH going high. When being driven by a synchronization clock signal at SYNC/EN, the controller synchronizes to the external clock within two cycles. The frequency at SYNC/EN needs to be within ±30% of the value set by RFREQ. See the *Switching-Frequency Setting* section.

#### **Thermal-Overload Protection**

Thermal-overload protection limits the total power dissipation in the MAX8513/MAX8514. When the junction temperature exceeds  $T_J = +170^{\circ}\text{C}$ , a thermal sensor shuts down the device, forcing DL and DH low and allowing the IC to cool. The thermal sensor turns the part on again after the junction temperature cools by 25°C, resulting in a pulsed output during continuous thermal-overload conditions. During a thermal event, the main step-down converter and the linear regulators are turned off,  $\overline{POR}$  and  $\overline{PFO}$  go low, and soft-start is reset.

### **Design Procedure**

#### **OUT1 Voltage Setting**

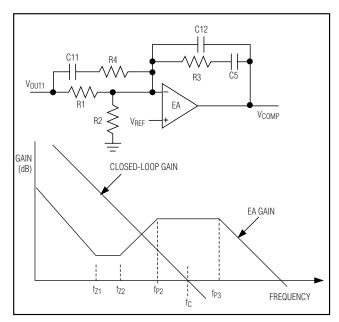

The output voltage is set by a resistive-divider network from OUT1 to FB1 to GND (see R1 and R2 in the *Typical Applications Circuits*). Select R2 between  $5k\Omega$  and  $15k\Omega$ . Then R1 can be calculated by: