#### **Features**

- Full function video fader

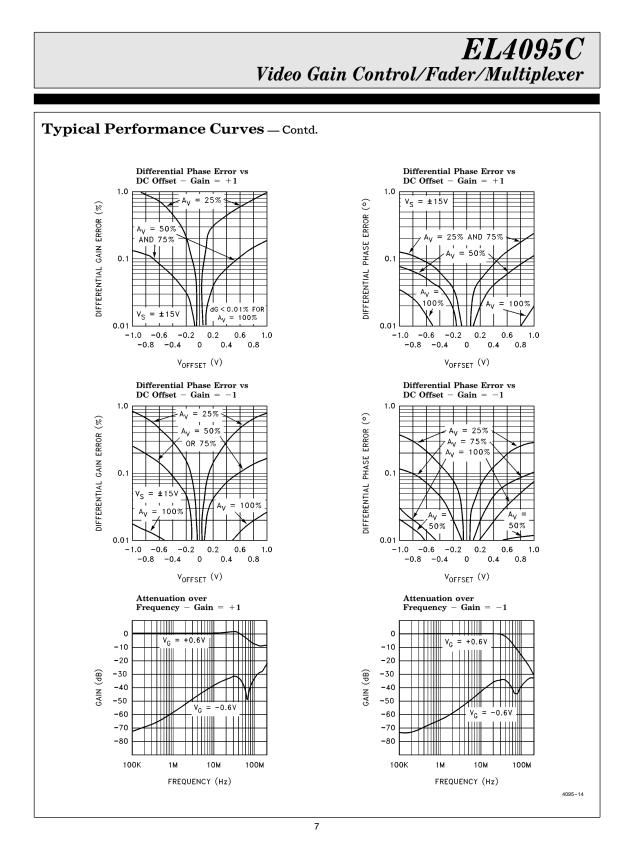

- 0.02%/0.02° differential gain/ phase @ 100% gain

- 25 ns multiplexer included

- Output amplifier included

- Calibrated linear gain control

- $\pm$  5V to  $\pm$  15V operation

- 60 MHz bandwidth

- Low thermal errors

#### Applications

- Video faders/wipers

- Gain control

- · Graphics overlay

- Video text insertion

- Level adjust

- Modulation

#### **Ordering Information**

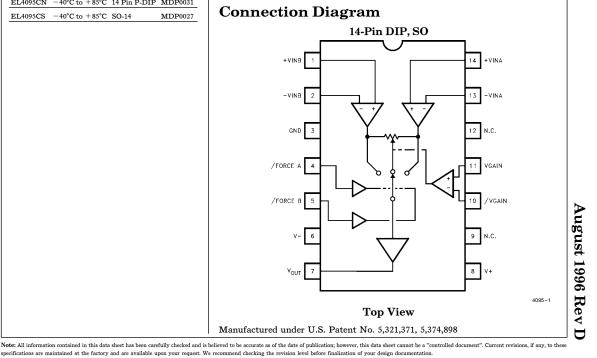

Package Part No. Temp. Range Outline# EL4095CN  $-40^\circ C$  to  $+85^\circ C$  14 Pin P-DIP MDP0031 EL4095CS  $-40^\circ C$  to  $+85^\circ C$  SO-14

#### **General Description**

The EL4095C is a versatile variable-gain building block. At its core is a fader which can variably blend two inputs together and an output amplifier that can drive heavy loads. Each input appears as the input of a current-feedback amplifier and with external resistors can separately provide any gain desired. The output is defined as:

$V_{OUT} = A^* V_{INA} (0.5V + V_{GAIN}) + B^* V_{INB} (0.5V - V_{GAIN}),$

where A and B are the fed-back gains of each channel.

Additionally, two logic inputs are provided which each override the analog  $V_{GAIN}$  control and force 100% gain for one input and 0% for the other. The logic inputs switch in only 25 ns and provide high attenuation to the off channel, while generating very small glitches.

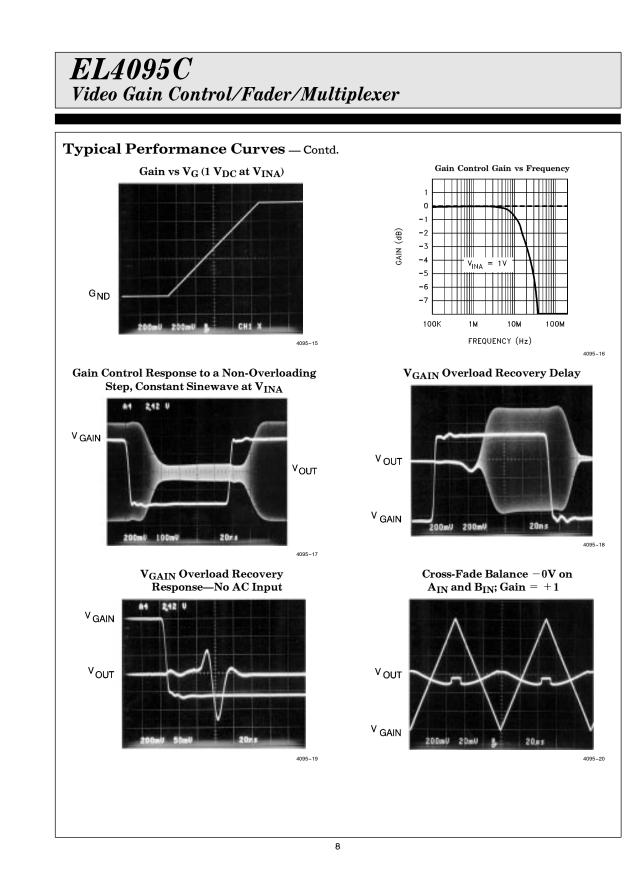

Signal bandwidth is 60 MHz, and gain-control bandwidth 20 MHz. The gain control recovers from overdrive in only 70 ns.

The EL4095C operates from  $\pm 5V$  to  $\pm 15V$  power supplies, and is available in both 14-pin DIP and narrow surface mount packages.

©1992 Elantec, Inc.

### Absolute Maximum Ratings $(T_A = 25^{\circ}C)$

#### Important Note:

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefore  $T_J=T_C=T_A$ .

#### Test Level Test Procedure

| n Level | Test Tibledule                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------|

| I       | 100% production tested and QA sample tested per QA test plan QCX0002.                               |

| II      | 100% production tested at $T_{\rm A}=25^{\circ}C$ and QA sample tested at $T_{\rm A}=25^{\circ}C$ , |

|         | $T_{MAX}$ and $T_{MIN}$ per QA test plan QCX0002.                                                   |

| III     | QA sample tested per QA test plan QCX0002.                                                          |

| IV      | Parameter is guaranteed (but not tested) by Design and Characterization Data.                       |

| v       | Parameter is typical value at $T_A = 25^{\circ}C$ for information purposes only.                    |

|         |                                                                                                     |

#### **Open Loop DC Electrical Characteristics**

$V_S = \pm 15V$ ,  $T_A = 25^{\circ}$ C,  $V_{\overline{GAIN}}$  ground unless otherwise specified

| Parameter                 | Description                                                    | Limits     |      |           | Test  | Units |

|---------------------------|----------------------------------------------------------------|------------|------|-----------|-------|-------|

|                           | Description                                                    | Min        | Тур  | Max       | Level |       |

| V <sub>OS</sub>           | Input Offset Voltage                                           |            | 1.5  | 5         | I     | mV    |

| ${\tt I_{B^+}}$           | $+V_{IN}$ Input Bias Current                                   |            | 5    | 10        | I     | μΑ    |

| $I_{B-}$                  | -V <sub>IN</sub> Input Bias Current                            |            | 10   | 50        | I     | μΑ    |

| CMRR                      | Common Mode Rejection                                          | 65         | 80   |           | I     | dB    |

| -CMRR                     | – V <sub>IN</sub> Input Bias Current<br>Common Mode Rejection  |            | 0.5  | 1.5       | I     | μA/V  |

| PSRR                      | Power Supply Rejection Ratio                                   | 65         | 95   |           | I     | dB    |

| -IPSR                     | -V <sub>IN</sub> Input Current<br>Power Supply Rejection Ratio |            | 0.2  | 2         | I     | μΑ/ν  |

| R <sub>OL</sub>           | Transimpedance                                                 | 0.2        | 0.4  |           | I     | MΩ    |

| R <sub>IN</sub> -         | -V <sub>IN</sub> Input Resistance                              |            | 80   |           | v     | Ω     |

| V <sub>IN</sub>           | + V <sub>IN</sub> Range                                        | (V-) + 3.5 |      | (V+) -3.5 | I     | v     |

| vo                        | Output Voltage Swing                                           | (V-) +2    |      | (V+) −2   | I     | v     |

| I <sub>SC</sub>           | Output Short-Circuit Current                                   | 80         | 125  | 160       | I     | mA    |

| V <sub>IH</sub>           | Input High Threshold at<br>Force A or Force B Inputs           |            |      | 2.0       | I     | v     |

| V <sub>IL</sub>           | Input Low Threshold at<br>Force A or Force B Inputs            | 0.8        |      |           | I     | v     |

| I <sub>FORCE</sub> , High | Input Current of Force A<br>or Force B, $V_{FORCE} = 5V$       |            |      | -50 I     |       | μΑ    |

| I <sub>FORCE</sub> , Low  | Input Current of Force A<br>or Force B, $V_{FORCE} = 0V$       |            | -440 | -650      | I     | μΑ    |

### Open Loop DC Electrical Characteristics - Contd.

$V_{\rm S} = \pm 15$ V,  $T_{\rm A} = 25$ °C, unless otherwise specified

| Parameter                                    | Description                                                                                                                                                                                                          |       | Limits                | Test  | Units       |        |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|-------|-------------|--------|--|

| Tarameter                                    | Distription                                                                                                                                                                                                          | Min   | Тур                   | Max   | Level       |        |  |

| Feedthrough,<br>Forced                       | Feedthrough of Deselected Input to Output,<br>Deselected Input at 100% Gain Control                                                                                                                                  | 60    | 75                    |       | I           | dB     |  |

| V <sub>GAIN</sub> , 100%                     | Minimum Voltage at<br>VGAIN for 100% Gain0.450.50.55                                                                                                                                                                 |       |                       |       | I           | v      |  |

| V <sub>GAIN</sub> , 0%                       | Maximum Voltage at<br>V <sub>GAIN</sub> for 0% Gain                                                                                                                                                                  | -0.55 | -0.5                  | -0.45 | I           | v      |  |

| NL, Gain                                     | Gain Control Non-linearity, $V_{IN} = \pm 0.5 V$                                                                                                                                                                     |       | 2                     | 4     | I           | %      |  |

| R <sub>IN</sub> , VG                         | Impedance between $V_{GAIN}$ and $V_{\overline{GAIN}}$                                                                                                                                                               | 4.5   | 5.5                   | 6.5   | I           | kΩ     |  |

| NL, $A_V = 1$<br>$A_V = 0.5$<br>$A_V = 0.25$ | $\begin{array}{l} \mbox{Signal Non-linearity, } V_{IN}=\pm 1V, V_{GAIN}=0.55V\\ \mbox{Signal Non-linearity, } V_{IN}=\pm 1V, V_{GAIN}=0V\\ \mbox{Signal Non-linearity, } V_{IN}=\pm 1V, V_{GAIN}=-0.25V \end{array}$ |       | <0.01<br>0.03<br>0.07 | 0.4   | V<br>V<br>I | %<br>% |  |

| I <sub>S</sub>                               | Supply Current                                                                                                                                                                                                       |       | 17                    | 21    | I           | mA     |  |

#### **Closed Loop AC Electrical Characteristics**

$V_S=\pm15V, A_V=+1, R_F=R_{IN}=1~k\Omega, R_L=500\Omega, C_L=15~pF, C_{IN}-=2~pF, T_A=25^\circ C, A_V=100\%~unless~otherwise~noted$

| Parameter               | Description                                                                                                                                                                                                                            | Limits |                      |     | Test  | Units             |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------|-----|-------|-------------------|

|                         | Description                                                                                                                                                                                                                            | Min    | Тур                  | Max | Level | Cints             |

| SR                      | Slew Rate; $V_{OUT}$ from $-3V$ to $+3V$<br>Measured at $-2V$ and $+2V$                                                                                                                                                                |        | 330                  |     | v     | V/µs              |

| BW                      | Bandwidth $-3 dB$<br>-1 dB<br>-0.1 dB                                                                                                                                                                                                  |        | 60<br>30<br>6        |     | v     | MHz<br>MHz<br>MHz |

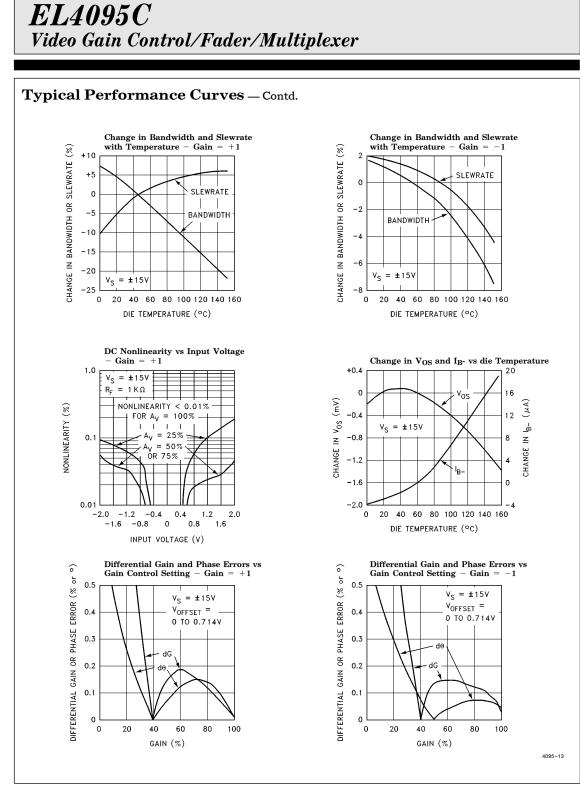

| dG                      | $ \begin{array}{l} Differential \mbox{ Gain; AC Amplitude of 286 mV}_{p\mbox{-}p} \\ \mbox{at 3.58 MHz on DC Offset of } -0.7V, 0V \mbox{ and } +0.7V \\ \mbox{ A}_V = 100\% \\ \mbox{ A}_V = 50\% \\ \mbox{ A}_V = 25\% \end{array} $ |        | 0.02<br>0.07<br>0.07 |     | v     | %<br>%            |

| dθ                      | $ \begin{array}{l} \mbox{Differential Phase; AC Amplitude of 286 mV_{p-p} \\ \mbox{at 3.58 MHz on DC Offset of } -0.7V, 0V \mbox{ and } +0.7V \\ \mbox{A}_V = 100\% \\ \mbox{A}_V = 50\% \\ \mbox{A}_V = 25\% \end{array} $            |        | 0.02<br>0.05<br>0.15 |     | v     | 0<br>0<br>0       |

| T <sub>S</sub>          | Settling Time to 0.2%; V <sub>OUT</sub> from $-2V$ to $+2V$<br>A <sub>V</sub> = 100%<br>A <sub>V</sub> = 25%                                                                                                                           |        | 100<br>100           |     | v     | ns<br>ns          |

| T <sub>FORCE</sub>      | Propagation Delay from V <sub>FORCE</sub> = 1.4V to 50%<br>Output Signal Enabled or Disabled Amplitude                                                                                                                                 |        | 25                   |     | v     | ns                |

| BW, Gain                | –3 dB Gain Control Bandwidth,<br>V <sub>GAIN</sub> Amplitude 0.5 V <sub>P-P</sub>                                                                                                                                                      |        | 20                   |     | v     | MHz               |

| T <sub>REC</sub> , Gain | Gain Control Recovery from Overload;<br>V <sub>GAIN</sub> from -0.7V to 0V                                                                                                                                                             |        | 70                   |     | v     | ns                |

Downloaded from Elcodis.com electronic components distributor

Downloaded from Elcodis.com electronic components distributor

#### **Applications Information**

The EL4095 is a general-purpose two-channel fader whose input channels each act as a current-feedback amplifier (CFA) input. Each input can have its own gain factor as established by external resistors. For instance, the Test Circuit shows two channels each arranged as +1 gain, with the traditional single feedback resistor  $R_F$  connected from  $V_{OUT}$  to the  $-V_{IN}$  of each channel.

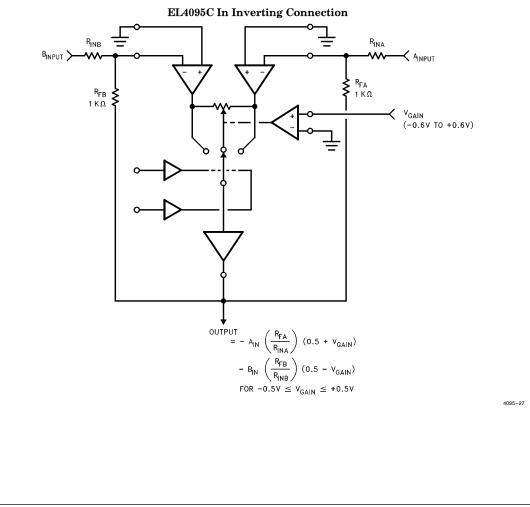

The EL4095 can be connected as an inverting amplifier in the same manner as any CFA:

#### **Frequency Response**

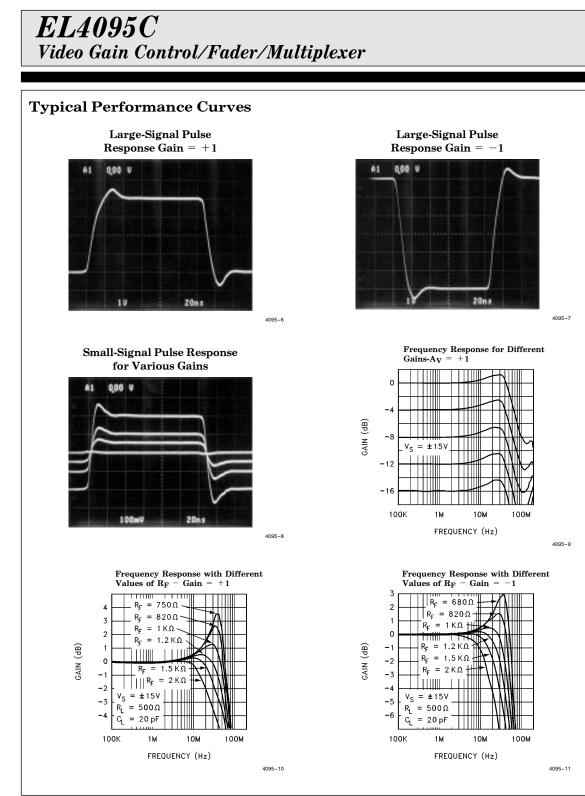

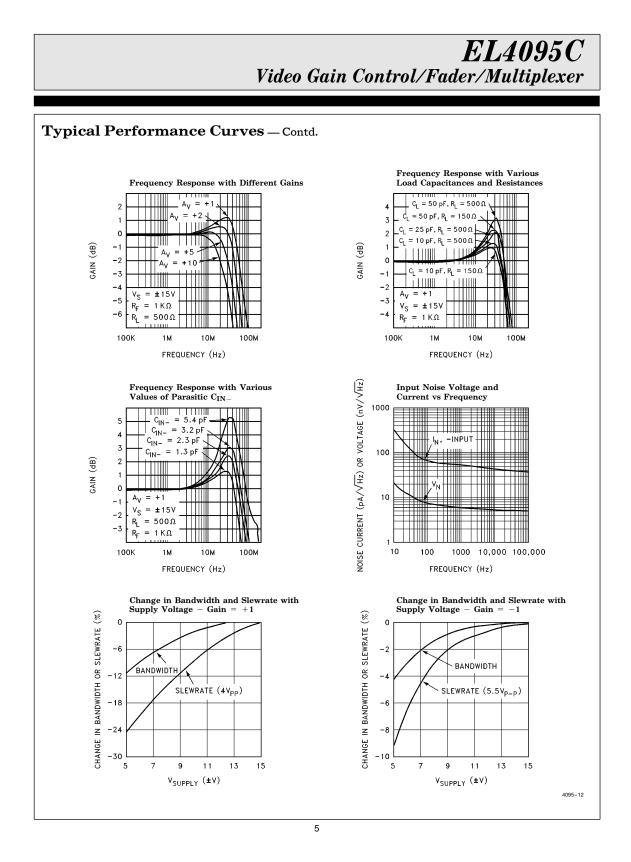

Like other CFA's, there is a recommended feedback resistor, which for this circuit is 1 K $\Omega$ . The value of RF sets the closed-loop -3 dB bandwidth, and has only a small range of practical variation. The user should consult the typical performance curves to find the optional value of  $R_F$  for a given circuit gain. In general, the bandwidth will decrease slightly as closed-loop gain is increased;  $R_F$  can be reduced to make up for bandwidth loss. Too small a value of  $R_F$  will cause frequency response peaking and ringing during transients. On the other hand, increasing  $R_F$  will reduce bandwidth but improve stability.

#### Applications Information - Contd.

Stray capacitance at each  $-V_{IN}$  terminal should absolutely be minimized, especially in a positivegain mode, or peaking will occur. Similarly, the load capacitance should be minimized. If more than 25 pF of load capacitance must be driven, a load resistor from 100 $\Omega$  to 400 $\Omega$  can be added in parallel with the output to reduce peaking, but some bandwidth degradation may occur. A "snubber" load can alternatively be used. This is a resistor in series with a capacitor to ground, 150 $\Omega$  and 100 pF being typical values. The advantage of a snubber is that it does not draw DC load current. A small series resistor, low tens of ohms, can also be used to isolate reactive loads.

#### Distortion

The signal voltage range of the  $+V_{IN}$  terminals is within 3.5V of either supply rail.

One must also consider the range of error currents that will be handled by the  $-V_{IN}$  terminals. Since the  $-V_{IN}$  of a CFA is the output of a buffer which replicates the voltage at  $+V_{IN}$ , error currents will flow into the  $-V_{IN}$  terminal. When an input channel has 100% gain assigned to it, only a small error current flows into its negative input; when low gain is assigned to the channel the output does not respond to the channel's signal and large error currents flow.

Here are a few idealized examples, based on a gain of  $\pm 1$  for channels A and B and  $R_F = 1 \ k\Omega$  for different gain settings:

| Gain | VINA | VINB | $I(-V_{INA})$  | I (-V <sub>INB</sub> ) | VOUT  |

|------|------|------|----------------|------------------------|-------|

| 100% | 1V   | 0    | 0              | 1 mA                   | 1V    |

| 75%  | 1V   | 0    | $-250 \ \mu A$ | 750 μA                 | 0.75V |

| 50%  | 1V   | 0    | $-500 \mu A$   | 500 µA                 | 0.5V  |

| 25%  | 1V   | 0    | $-750 \ \mu A$ | 250 μ <b>A</b>         | 0.25V |

| 0%   | 1V   | 0    | -1 mA          | 0                      | 0V    |

Thus, either  $-V_{IN}$  can receive up to 1 mA error current for 1V of input signal and 1 k $\Omega$  feedback resistors. The maximum error current is 3 mA for the EL4095, but 2 mA is more realistic. The major contributor of distortion is the magnitude of error currents, even more important than loading effects. The performance curves show distortion versus input amplitude for different gains. If maximum bandwidth is not required, distortion can be reduced greatly (and signal voltage range enlarged) by increasing the value of  $R_{\rm F}$  and any associated gain-setting resistor.

#### 100% Accuracies

When a channel gain is set to 100%, static and gain errors are similar to those of a simple CFA. The DC output error is expressed by

$$V_{OUT}$$

, Offset =  $V_{OS}^* A_V + (I_B^-)^* R_F$ .

The input offset voltage scales with fed-back gain, but the bias current into the negative input,  $I_B^-$ , adds an error not dependent on gain. Generally,  $I_B^-$  dominates up to gains of about seven.

The fractional gain error is given by

$$E_{GAIN} = (R_F + A_V^* R_{IN} -) R_F + A_V R_{IN} / R_{OL}$$

The gain error is about 0.3% for a gain of one, and increases only slowly for increasing gain.  $R_{IN}$  – is the input impedance of the input stage buffer, and  $R_{OL}$  is the transimpedance of the amplifier, 80 k $\Omega$  and 350 k $\Omega$  respectively.

#### **Gain Control Inputs**

The gain control inputs are differential and may be biased at any voltage as long as  $\overline{V_{GAIN}}$  is less than 2.5V below V+ and 3V above V-. The differential input impedance is 5.5 k $\Omega$ , and a common-mode impedance is more than 500 k $\Omega$ . With zero differential voltage on the gain inputs, both signal inputs have a 50% gain factor. Nominal calibration sets the 100% gain of  $V_{\rm INA}$  input at +0.5V of gain control voltage, and 0% at -0.5Vof gain control.  $V_{INB}$ 's gain is complementary to that of  $V_{INA}$ ; +0.5V of gain control sets 0% gain at  $V_{INB}$  and -0.5V gain control sets 100%  $V_{INB}$ gain. The gain control does not have a completely abrupt transition at the 0% and 100% points. There is about 10 mV of "soft" transfer at the gain endpoints. To obtain the most accurate 100% gain factor or best attenuation of 0% gain, it is necessary to overdrive the gain control input by about 30 mV. This would set the gain control voltage range as -0.565 mV to +0.565V, or 30 mV beyond the maximum guaranteed 0% to 100% range.

#### Applications Information - Contd.

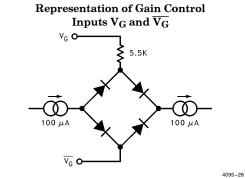

In fact, the gain control internal circuitry is very complex. Here is a representation of the terminals:

For gain control inputs between  $\pm 0.5V$  ( $\pm 90~\mu A$ ), the diode bridge is a low impedance and all of the current into  $V_G$  flows back out through  $\overline{V_G}$ . When gain control inputs exceed this amount, the bridge becomes a high impedance as some of the diodes shut off, and the  $V_G$  impedance rises sharply from the nominal 5.5 K $\Omega$  to over 500 K $\Omega$ . This is the condition of gain control overdrive. The actual circuit produces a much sharper overdrive characteristics than does the simple diode bridge of this representation.

The gain input has a 20 MHz -3 dB bandwidth and 17 ns risetime for inputs to  $\pm 0.45$ V. When the gain control voltage exceeds the 0% or 100% values, a 70 ns overdrive recovery transient will occur when it is brought back to linear range. If quicker gain overdrive response is required, the Force control inputs of the EL4095 can be used.

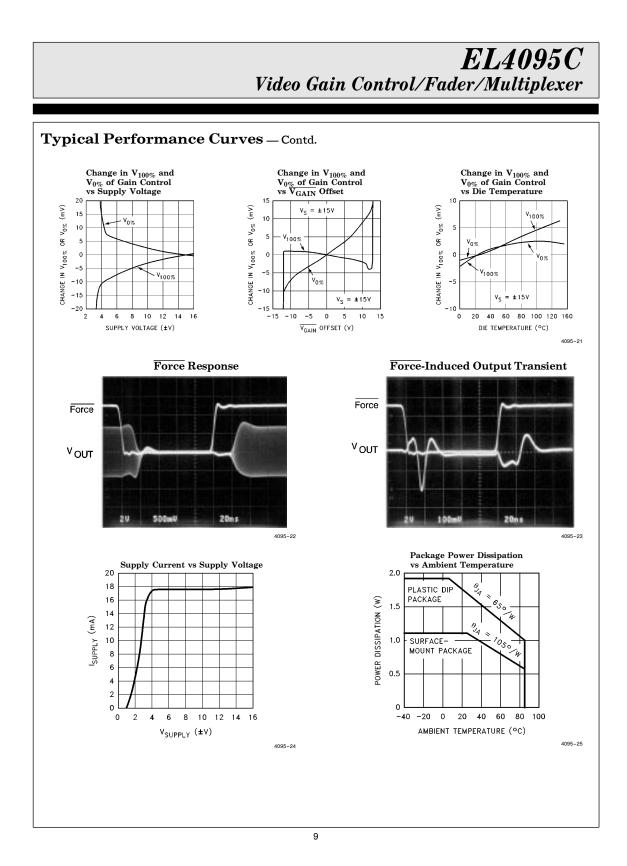

#### **Force Inputs**

The Force inputs completely override the  $V_{GAIN}$  setting and establish maximum attainable 0% and 100% gains for the two input channels. They are activated by a TTL logic low on either of the FORCE pins, and perform the analog switching very quickly and cleanly. FORCEA causes 100% gain on the A channel and 0% on the B channel. FORCEB does the reverse, but there is no defined output state when FORCEA and FORCEB are simultaneously asserted.

The Force inputs do not incur recovery time penalties, and make ideal multiplexing controls. A typical use would be text overlay, where the A channel is a video input and the B channel is digitally created text data. The FORCEA input is set low normally to pass the video signal, but released to display overlay data. The gain control can be used to set the intensity of the digital overlay.

#### **Other Applications Circuits**

The EL4095 can also be used as a variable-gain single input amplifier. If a 0% lower gain extreme is required, one channel's input should simply be grounded. Feedback resistors must be connected to both  $-V_{\rm IN}$  terminals; the EL4095 will not give the expected gain range when a channel is left unconnected.

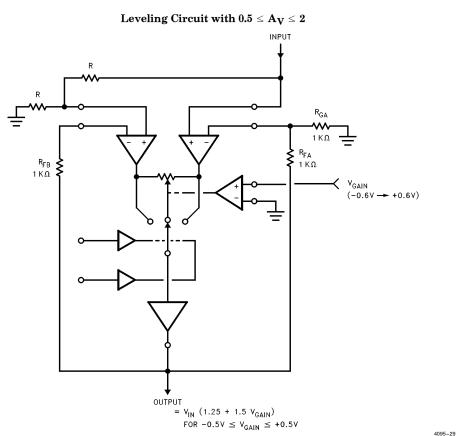

This circuit gives +0.5 to +2.0 gain range, and is useful as a signal leveller, where a constant output level is regulated from a range of input amplitudes:

#### Application Information - Contd.

Here the A input channel is configured for a gain of +2 and the B channel for a gain of +1 with its input attenuated by  $\frac{1}{2}$ . The connection is virtuous because the distortions do not increase monotonically with reducing gain as would the simple single-input connecton. For video levels, however, these constants can give fairly high differential gain error. The problem occurs for large inputs. Assume that a "twice-size" video input occurs. The A-side stage sees the full amplitude, but the gain would be set to 100% B-input gain to yield an overall gain of

duces the input signal, and drives  $R_{GA}$  and  $R_{FA}$ .

Into the two resistors 2.1 mA of error current

flows for a typical 1.4V of input DC offset, creating distortion in a A-side input stage.  $R_{GA}$  and

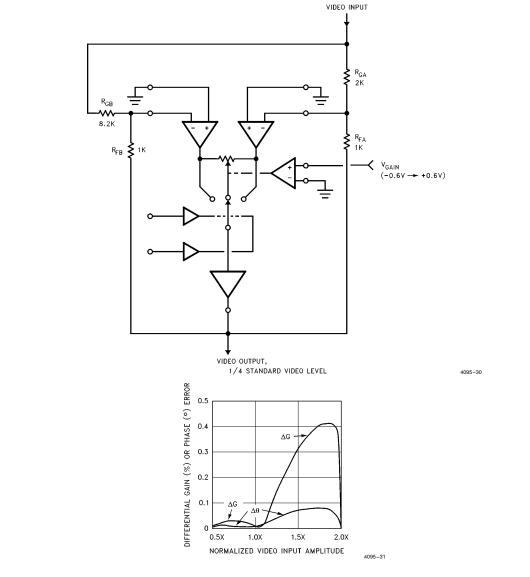

$R_{\rm FA}$  could be increased together in value to reduce the error current and distortions, but increasing  $R_{\rm FA}$  would lower bandwidth. A solution would be to simply attenuate the input signal magnitude and restore the EL4095 output level to standard level with another amplifier so:

Reduced-Gain Leveler for Video Inputs and Differential Gain and Phase Performance (see text)

#### Application Information - Contd.

Although another amplifier is needed to gain the output back to standard level, the reduced error currents bring the differential phase error to less than 0.1' over the entire input range.

A useful technique to reduce video distortion is to DC-restore the video level going into the EL4095, and offsetting black level to -0.35V so that the entire video span encompasses  $\pm 0.35V$  rather

than the unrestored possible span of  $\pm 0.7V$  (for standard-sized signals). For the preceding leveler circuit, the black level should be set more toward -0.7V to accommodate the largest input, or made to vary with the gain control itself (large gain, small offset; small gain, larger offset).

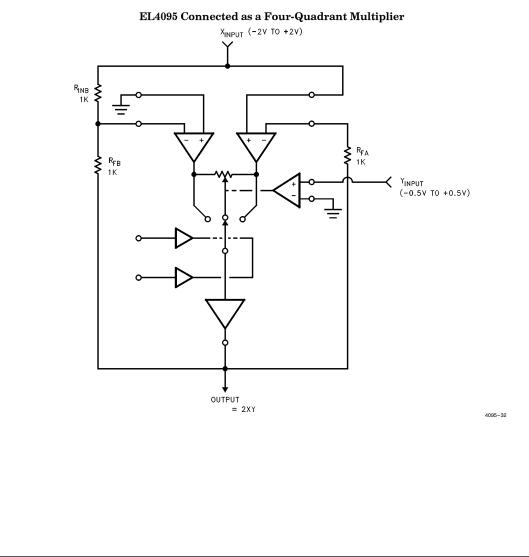

The EL4095 can be wired as a four quadrant multiplier:

#### Application Information - Contd.

The A channel gains the input by +1 and the B channel by -1. Feedthrough suppression of the Y input can be optimized by introducing an offset between channel A and B. This is easily done by injecting an adjustable current into the summing junction ( $-V_{IN}$  terminal) of the B input channel.

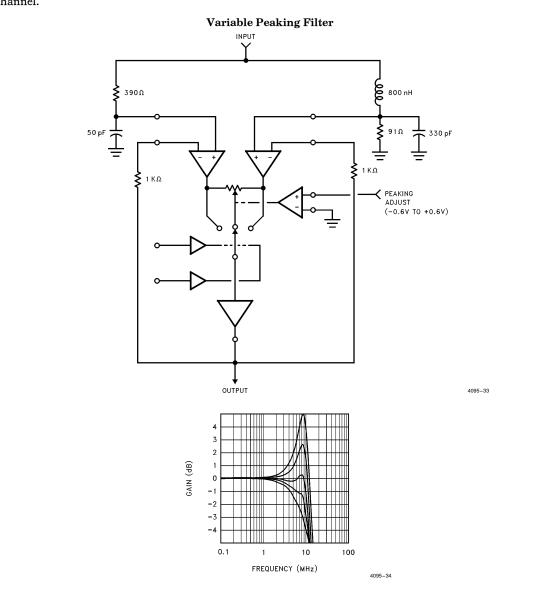

The two input channels can be connected to a common input through two dissimilar filters to create a DC-controlled variable filter. This circuit provides a controlled range of peaking through rolloff characteristics:

#### Applications Information - Contd.

The EL4095 is connected as a unity-gain fader, with an LRC peaking network connected to the A-input and an RC rolloff network connected to the B-input. The plot shows the range of peaking controlled by the  $V_{GAIN}$  input. This circuit would be useful for flattening the frequency response of a system, or for providing equalization ahead of a lossy transmission line.

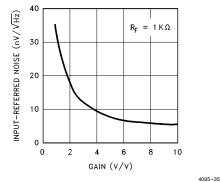

#### Noise

The electrical noise of the EL4095 has two components: the voltage noise in series with  $+ V_{IN}$  is 5 nV  $\sqrt{Hz}$  wideband, and there is a current noise injected into  $-V_{IN}$  of 35 pA $\sqrt{Hz}$ . The output noise will be

$\overline{V_{n, \text{ out}}} = \sqrt{(A_V \bullet \overline{V_{n, \text{ input}}})^2 + (\overline{I_{n, \text{ input}}} \bullet R_F)^2},$

and the input-referred noise is

$\overline{V_{n, \text{ input-referred}}} = \sqrt{(\overline{V_{n, \text{ input}}})^2 + (\overline{I_{n, \text{ input}}} \bullet R_F / A_V)^2}$

where  $A_V$  is the fed-back gain of the EL4095. Here is a plot of input-referred noise vs  $A_V$ :

#### Input-Referred Noise vs Closed-Loop Gain

Thus, for a gain of three or more the fader has a noise as good as an op-amp. The only trade-off is that the dynamic range of the input is reduced by the gain due to the nonlinearity caused by gained-up output signals.

#### **Power Dissipation**

Peak die temperature must not exceed  $150^{\circ}$ C. This allows  $75^{\circ}$ C internal temperature rise for a  $75^{\circ}$ C ambient. The EL4095 in the 14-pin PDIP

package has a thermal resistance of  $65^{\circ}$ C/W, and can thus dissipate 1.15W at a 75°C ambient temperature. The device draws 20 mA maximum supply current, only 600 mW at  $\pm$ 15V supplies, and the circuit has no dissipation problems in this package.

The SO-14 surface-mount package has a  $105^{\circ}$ C/W thermal resistance with the EL4095, and only 714 mW can be dissipated at 75°C ambient temperature. The EL4095 thus can be operated with  $\pm 15$ V supplies at 75°C, but additional dissipation caused by heavy loads must be considered. If this is a problem, the supplies should be reduced to  $\pm 5$ V to  $\pm 12$ V levels.

The output will survive momentary short-circuits to ground, but the large available current will overheat the die and also potentially destroy the circuit's metal traces. The EL4095 is reliable within its maximum average output currents and operating temperatures.

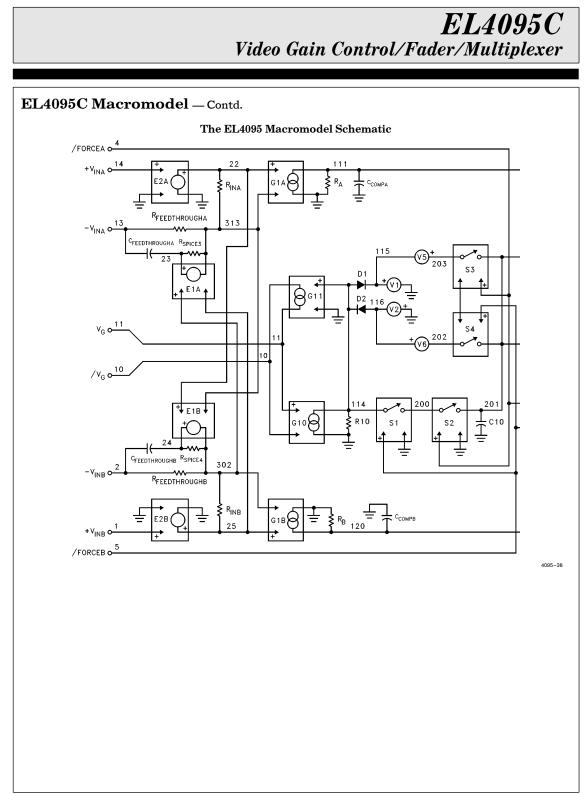

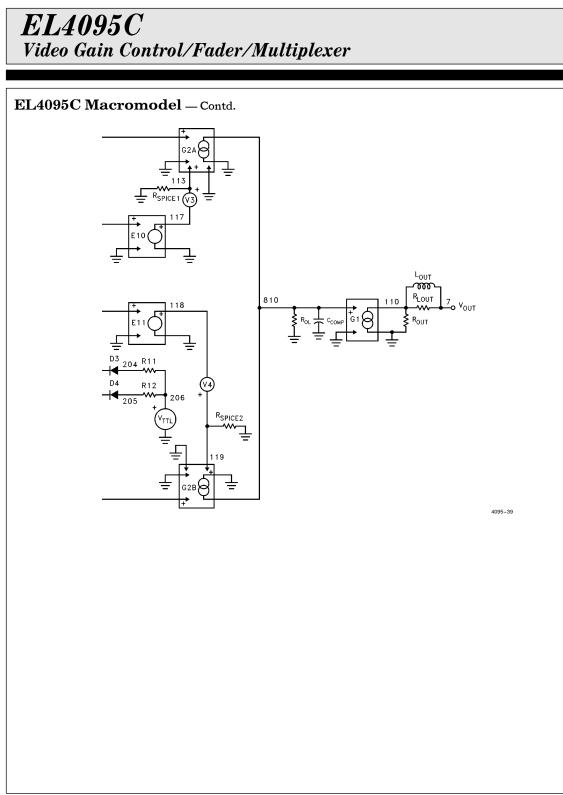

#### EL4095C Macromodel

This macromodel is offered to allow simulation of general EL4095 behavior. We have included these characteristics:

Small-signal frequency response Output loading effects Input impedance Off-channel feedthrough Output impedance over frequency - V<sub>IN</sub> characteristics and sensitivity to parasitic capacitance Signal path DC distoritons V<sub>GAIN</sub> I-V characteristics V<sub>GAIN</sub> overdrive recovery delay 100% gain error FORCE operation

These will give a good range of results of various operating conditions, but the macromodel does not behave identically as the circuit in these areas:

EL4095C Macromodel - Contd. \*\*\* EL4095 macromodel \*\*\* \*\*\*\*\* \* +VinB \* -VinB \* /ForceA \* /ForceB Vout . /Vqain 1 \* Vgain \* -VinA ł \* +VinA 1 Т \* .SUBCKT 4095macromodel ( 1 7 io 13 i4) 2 4 5 11 Rol 810 0 290k Ccomp 810 0 4.3p G1 110 0 810 0 -10 Rout 110 0 0.1 Lout 110 7 350n RLout 110 7 80 \*\*\* Rina+ 14 0 5E6 Rinb+ 1 0 5E6 Rvg 11 0 2E6 Rvgg 10 0 2E6 Rforcea 4 0 1E9 Rforceb 5 0 1E9 \*\*\* Input channel A \*\*\* Rina 22 313 79 Ra 111 0 1k Rfeedthrougha 13 313 1.0 Cfeedthrougha 23 13 2500p Ccompa 111 0 2p Ela 23 313 302 25 -1 E2a 22 0 14 0 0.9999 Rspice3 23 313 1E12 Gla 111 0 POLY(1) (22,313) 0.0 0.0125 -150E-6 G2a 810 0 POLY(2) (111,0) (113,0) 0.0 0.0 0.0 0.0 0.001 \*\*\* \*\*\*Input channel B +++ Rinb 25 302 79 Rb 120 0 1k Rfeedthroughb 2 302 1.0 Rfeedthroughb 2 302 1.0 Cfeedthroughb 2 302 1.0 Ccompb 120 0 2p Elb 24 302 22 313 -1 E2b 25 0 1 0 0.9999 Rspice4 24 302 IE12 Glb 120 0 POLY(1) (25,302) 0.0 0.0125 -150E-6 G2b 810 0 POLY(2) (120,0) (119,0) 0.0 0.0 0.0 0.0 0.001 \*\*\* \*\*\*Gain control \*\*\* Rspice1 113 0 1E12 Rspice2 119 0 1E12 R10 114 0 1E7 R11 204 206 2.5E6 R12 205 206 2.5E6 C10 201 0 9.5E-16 D1 114 115 Dclamp D2 116 114 Dclamp D3 204 4 Dclamp

4095-36

#### EL4095C Macromodel - Contd.

LL409DC INACTOMOGEI — Contd.

D4 205 5 Dclamp

.model Dclamp D(TT=200n)

Vttl 206 0 2.4

V1 105 0 4999.3

V2 0 116 4999.3

V2 0 116 4999.3

V3 113 117 0.5

V4 119 118 0.5

V5 203 115 0.7

V6 116 202 0.7

G10 114 0 11 10 -0.001

G11 11 10 114 0 -2E-8

E10 117 0 201 0 1E-4

E11 118 0 201 0 -1E-4

E11 118 0 201 0 -1E-4

E11 118 0 201 0 -1E-4

S1 114 200 5 0 Nopen

S2 200 201 4 0 Nclosed

S2 200 201 4 0 Nclosed

.model Nopen VSWITCH(Ron=100 Roff=1E12 Von=1.6 Voff=1.2)

.model Nclosed VSWITCH(Ron=100 Roff=1E12 Von=1.2 voff=1.6)

\*\*\*

.ENDS .ENDS \*\*\*\*\*\*

20

4095-37

BLANK

#### **General Disclaimer**

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

# August 1996 Rev D Elantec, Inc.

1996 Tarob Court Milpitas, CA 95035 Telephone: (408) 945-1323 (800) 333-6314 Fax: (408) 945-9305 European Office: 44-71-482-4596

#### WARNING - Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. products in Life Support Systems are requested to contact Elantec, Inc. factory headquarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.

Printed in U.S.A.