8ns High-Speed Comparator

## Features

- 8ns Typ. Propagation Delay

- 5V to 12V Input Supply

- +2.7V to +5V Output Supply

- True-to-ground Input

- Rail-to-rail Outputs

- Active Low Latch

- Dual Available (EL5281C)

- Window Comparator (EL5283C)

- Quad Available (EL5481C & EL5482C)

- Pin-compatible 4ns Family Available (EL5x85C, EL5287C & EL5486C)

## Applications

- Threshold Detection

- High Speed Sampling Circuits

- High Speed Triggers

- Line Receivers

- PWM Circuits

- High Speed V/F Converters

## **Ordering Information**

| Part No.     | Package  | Tape & Reel | Outline # |

|--------------|----------|-------------|-----------|

| EL5181CS     | 8-Pin SO | -           | MDP0027   |

| EL5181CS-T7  | 8-Pin SO | 7"          | MDP0027   |

| EL5181CS-T13 | 8-Pin SO | 13"         | MDP0027   |

# **General Description**

The EL5181C comparator is designed for operation in single supply and dual supply applications with 5V to 12V between  $V_{S+}$  and  $V_{S-}$ . For single supplies, the inputs can operate from 0.1V below ground for use in ground sensing applications.

The output side of the comparator can be supplied from a single supply of 2.7V to 5V. The rail-to-rail output swing enables direct connection of the comparator to both CMOS and TTL logic circuits.

The latch input of the EL5181C can be used to hold the comparator output value by applying a low logic level to the pin.

The EL5181C is available in the 8-pin SO package and is specified for operation over the full -40°C to +85°C temperature range. Also available are a dual (EL5281C), a window comparator (EL5283C), and quad versions (EL5481C and EL5482C).

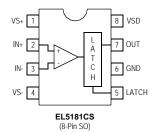

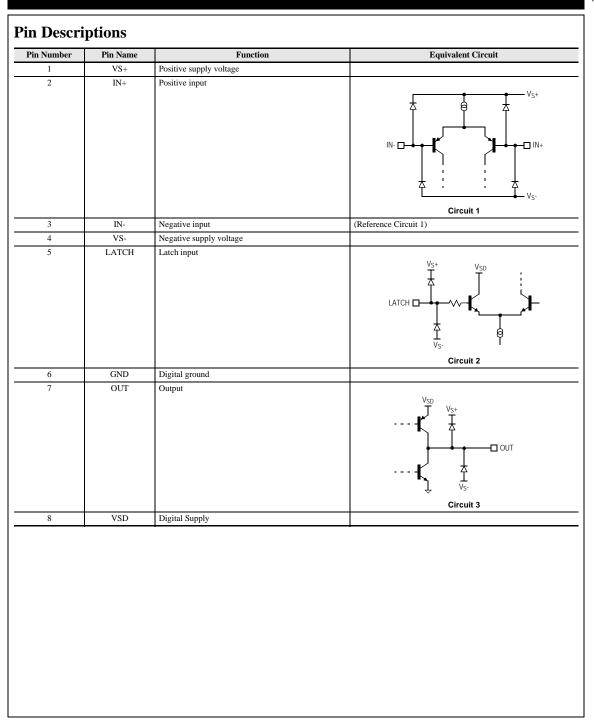

## **Pin Configuration**

**June 14, 200**

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a "controlled document". Current revisions, if any, to these specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

© 2001 Elantec Semiconductor, Inc

## Absolute Maximum Ratings $(T_A = 25^{\circ}C)$

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied. Analog Supply Voltage  $(V_S + to V_{S^-})$  +12.6V Digital Supply Voltage  $(V_{SD} to GND)$  +7V Differential Input Voltage  $[(V_{S^-}) - 0.2V]$  to  $[(V_{S^+}) + 0.2V]$  Common-mode Input Voltage Latch Input Voltage Storage Temperature Range Ambient Operating Temperature Operating Junction Temperature Power Dissipation [(Vs-) -0.2V] to [(Vs+) +0.2V] -0.2V to [(VsD) +0.2V] -65°C to +150°C -40°C to +85°C 125°C See Curves

#### Important Note:

All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$ .

## **Electrical Characteristics**

$V_S$  = ±5V,  $V_{SD}$  = 5V,  $R_L$  = 2.3k $\Omega,\,C_L$  = 15pF,  $T_A$  = 25°C, unless otherwise specified.

| Parameter           | Description                       | Condition                            | Min                      | Тур                   | Max                       | Unit |

|---------------------|-----------------------------------|--------------------------------------|--------------------------|-----------------------|---------------------------|------|

| Input               | •<br>•                            | <u>.</u>                             |                          |                       |                           |      |

| V <sub>OS</sub>     | Input Offset Voltage              | $V_{CM} = 0V, V_0 = 2.5V$            |                          | 1                     | 4                         | mV   |

| IB                  | Input Bias Current                |                                      | -6                       | -3.5                  |                           | μA   |

| CIN                 | Input Capacitance                 |                                      |                          | 5                     |                           | pF   |

| I <sub>OS</sub>     | Input Offset Current              | $V_{CM} = 0V, V_0 = 2.5V$            | -2.5                     | 0.5                   | 2.5                       | μA   |

| V <sub>CM</sub>     | Input Voltage Range               |                                      | (V <sub>S</sub> -) - 0.1 |                       | (V <sub>S</sub> +) - 2.25 | V    |

| CMRR                | Common-mode Rejection Ratio       | $-5.1V < V_{CM} < +2.75V$            | 65                       | 90                    |                           | dB   |

| Output              | •<br>•                            | <u>.</u>                             |                          |                       |                           |      |

| V <sub>OH</sub>     | Output High Voltage               | $V_{IN} > 250 mV$                    | V <sub>SD</sub> - 0.6    | V <sub>SD</sub> - 0.4 |                           | V    |

| V <sub>OL</sub>     | Output Low Voltage                | $V_{IN} > 250 mV$                    |                          | GND + 0.25            | GND + 0.5                 | V    |

| Dynamic Perf        | formance                          | -                                    | •                        | •                     |                           |      |

| t <sub>pd</sub> +   | Positive Going Delay Time         | $V_{IN}=1V_{P\text{-}P},V_{OD}=50mV$ |                          | 8                     | 12                        | ns   |

| t <sub>pd</sub> -   | Negative Going Delay Time         | $V_{IN}=1V_{P\text{-}P},V_{OD}=50mV$ |                          | 8                     | 12                        | ns   |

| Supply              | •<br>•                            | <u>.</u>                             |                          |                       |                           |      |

| $I_S+$              | Positive Analog Supply Current    |                                      |                          | 7                     | 8.2                       | mA   |

| Is-                 | Negative Analog Supply Current    |                                      |                          | 5                     | 6.5                       | mA   |

| I <sub>SD</sub>     | Digital Supply Current            | Output high                          |                          | 4                     | 5                         | mA   |

|                     |                                   | Output low                           |                          | 0.75                  | 1                         | mA   |

| PSRR                | Power Supply Rejection Ratio      |                                      | 60                       | 80                    |                           | dB   |

| Latch               | •<br>•                            | <u>.</u>                             |                          |                       |                           |      |

| V <sub>LH</sub>     | Latch Input Voltage High          |                                      |                          |                       | 2.0                       | V    |

| V <sub>LL</sub>     | Latch Input Voltage Low           |                                      | 0.8                      |                       |                           | V    |

| I <sub>LH</sub>     | Latch Input Current High          | V <sub>LH</sub> = 3.0V               | -30                      | -18                   |                           | μA   |

| I <sub>LL</sub>     | Latch Input Current Low           | $V_{LL} = 0.3V$                      | -30                      | -24                   |                           | μA   |

| t <sub>d</sub> +    | Latch Disable to High Delay       |                                      |                          | 6                     |                           | ns   |

| t <sub>d</sub> -    | Latch Disable to Low Delay        |                                      |                          | 6                     |                           | ns   |

| ts                  | Minimum Setup Time                |                                      |                          | 2                     | İ                         | ns   |

| t <sub>h</sub>      | Minimum Hold Time                 |                                      |                          | 1                     | İ                         | ns   |

| t <sub>pw</sub> (D) | Minimum Latch Disable Pulse Width |                                      |                          | 10                    |                           | ns   |

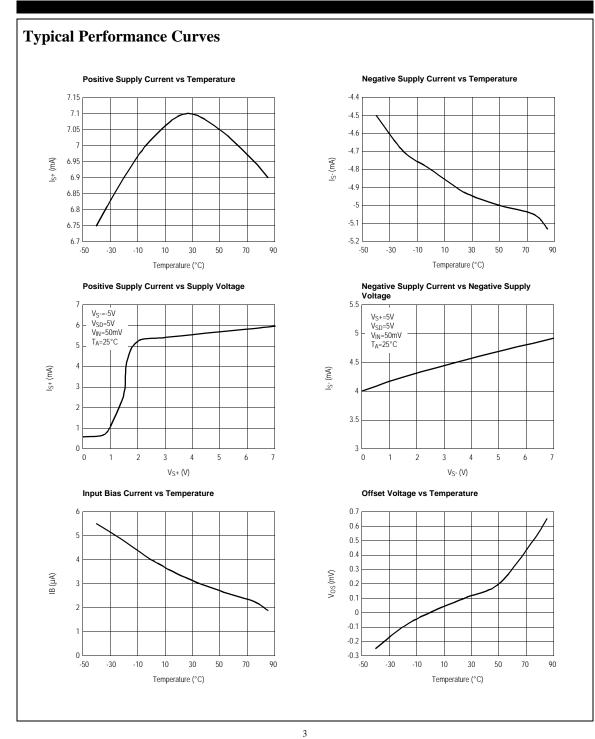

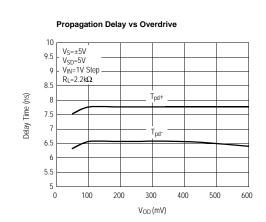

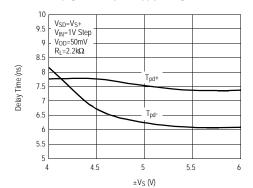

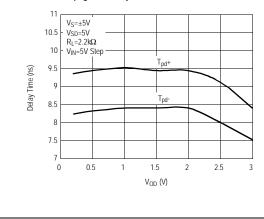

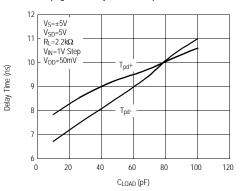

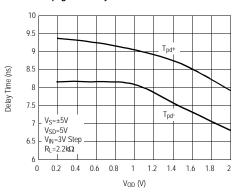

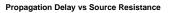

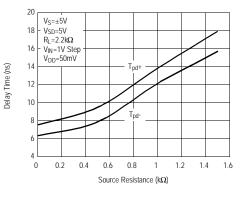

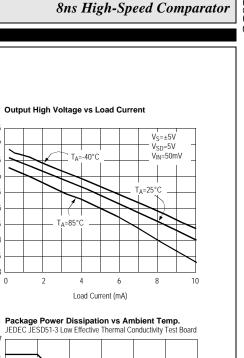

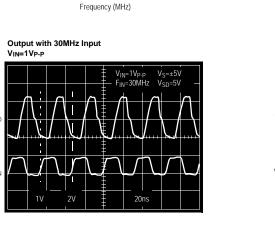

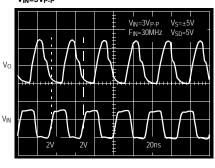

## **Typical Performance Curves**

Propagation Delay vs Overdrive

Propagation Delay vs Load Capacitance

Propagation Delay vs Overdrive

4.75

4.7

4.65

4.6

4.55

4.5 4.45

4.4

4.35

4.3

Output High Voltage (V)

V<sub>SD</sub>=3V

**Typical Performance Curves**

T\_=25°C

2

0.31

0.27

0.23

0.19

0.15

30 VS=±5V

25

20

15

10

5

0

Vc

VIN

0 5 10 15 20 25 30 35 40 45 50

I<sub>SD</sub> (mA)

0

Output Low Voltage (V)

Output Low Voltage vs Load Current

∧=85°C

-40°C

Load Current (mA)

6

4

Digital Supply Current vs Input Switching Frequency

V<sub>SD</sub>=5V

$V_{S}=\pm 5V$   $V_{SD}=5V$  $V_{IN}=-50mV$

8

10

EL5181C

Downloaded from Elcodis.com electronic components distributor

# **EL5181C** 8ns High-Speed Comparator

## **Definition of Terms**

| Term              | Definition                                                                                                                                                                                                                       |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>OS</sub>   | Input Offset Voltage - Voltage applied between the two input terminals to obtain CMOS logic threshold at the output                                                                                                              |  |  |  |

| V <sub>IN</sub>   | Input Voltage Pulse Amplitude - Usually set to 1V for comparator specifications                                                                                                                                                  |  |  |  |

| V <sub>OD</sub>   | Input Voltage Overdrive - Usually set to 50mV and in opposite polarity to VIN for comparator specifications                                                                                                                      |  |  |  |

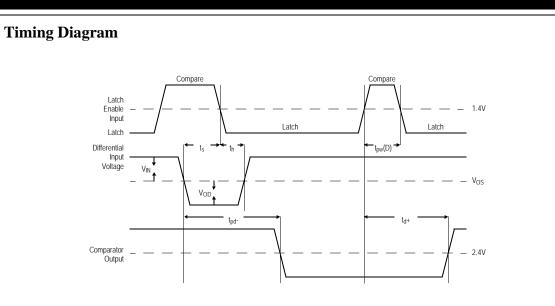

| t <sub>pd</sub> + | Input to Output High Delay - The propagation delay measured from the time the input signal crosses the input offset voltage to the CN logic threshold of an output low to high transition                                        |  |  |  |

| t <sub>pd</sub> - | Input to Output Low Delay - The propagation delay measured from the time the input signal crosses the input offset voltage to the CN logic threshold of an output high to low transition                                         |  |  |  |

| t <sub>d</sub> +  | Latch Disable to Output High Delay - The propagation delay measured from the latch signal crossing the CMOS threshold in a low to high transition to the point of the output crossing CMOS threshold in a low to high transition |  |  |  |

| t <sub>d</sub> -  | Latch Disable to Output Low Delay - The propagation delay measured from the latch signal crossing the CMOS threshold in a low t transition to the point of the output crossing CMOS threshold in a high to low transition        |  |  |  |

| ts                | Minimum Setup Time - The minimum time before the negative transition of the latch signal that an input signal change must be pre<br>order to be acquired and held at the outputs                                                 |  |  |  |

| t <sub>h</sub>    | Minimum Hold Time - The minimum time after the negative transition of the latch signal that an input signal must remain unchanged in order to be acquired and held at the output                                                 |  |  |  |

| $t_{pw}$ (D)      | Minimum Latch Disable Pulse Width - The minimum time that the latch signal must remain high in order to acquire and hold an input sign change                                                                                    |  |  |  |

**EL5181C** 8ns High-Speed Comparator

## **Applications Information**

#### **Power Supplies and Circuit Layout**

The EL5181C comparator operates with single and dual supply with 5V to 12V between  $V_{S+}$  and  $V_{S-}$ . The output side of the comparator is supplied by a single supply from 2.7V to 5V. The rail to rail output swing enables direct connection of the comparator to both CMOS and TTL logic circuits. As with many high speed devices, the supplies must be well bypassed. Elantec recommends a 4.7µF tantalum in parallel with a 0.1µF ceramic. These should be placed as close as possible to the supply pins. Keep all leads short to reduce stray capacitance and lead inductance. This will also minimize unwanted parasitic feedback around the comparator. The device should be soldered directly to the PC board instead of using a socket. Use a PC board with a good, unbroken low inductance ground plane. Good ground plane construction techniques enhance stability of the comparators.

#### Input Voltage Considerations

The EL5181C input range is specified from 0.1V below  $V_{S}$ - to 2.25V below  $V_{S}$ +. The criterion for the input limit is that the output still responds correctly to a small differential input signal. The differential input stage is a pair of PNP transistors, therefore, the input bias current flows out of the device. When either input signal falls below the negative input voltage limit, the parasitic PN junction formed by the substrate and the base of the PNP will turn on, resulting in a significant increase of input bias current. If one of the inputs goes above the positive input voltage limit, the output will still maintain the correct logic level as long as the other input stays within the input range. However, the propagation delay will increase. When both inputs are outside the input voltage range, the output becomes unpredictable. Large differential voltages greater than the supply voltage should be avoided to prevent damages to the input stage.

#### Input Slew Rate

Most high speed comparators oscillate when the voltage of one of the inputs is close to or equal to the voltage on the other input due to noise or undesirable feedback. For clean output waveform, the input must meet certain minimum slew rate requirements. In some applications, it may be helpful to apply some positive feedback (hysteresis) between the output and the positive input. The hysteresis effectively causes one comparator's input voltage to move quickly past the other, thus taking the input out of the region where oscillation occurs. For the EL5181C, the propagation delay increases when the input slew rate increases for low overdrive voltages. With high overdrive voltages, the propagation delay does not change much with the input slew rate.

#### **Latch Pin Dynamics**

The EL5181C contains a "transparent" latch for each channel. The latch pin is designed to be driven with either a TTL or CMOS output. When the latch is connected to a logic high level or left floating, the comparator is transparent and immediately responds to the changes at the input terminals. When the latch is switched to a logic low level, the comparator output remains latched to its value just before the latch's high-to-low transition. To guarantee data retention, the input signal must remain the same state at least 1ns (hold time) after the latch goes low and at least 2ns (setup time) before the latch goes low. When the latch goes high, the new data will appear at the output in approximately 6ns (latch propagation delay).

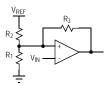

#### Hysteresis

Hysteresis can be added externally. The following two methods can be used to add hysteresis.

Inverting comparator with hysteresis:

$R_3$  adds a portion of the output to the threshold set by  $R_1$  and  $R_2$ . The calculation of the resistor values are as follows:

Select the threshold voltage  $V_{TH}$  and calculate  $R_1$  and  $R_2$ . The current through  $R_1/R_2$  bias string must be many

8ns High-Speed Comparator

times greater than the input bias current of the comparator:

$$\mathbf{V}_{\mathrm{TH}} = \mathbf{V}_{\mathrm{REF}} \times \frac{\mathbf{R}_1}{\mathbf{R}_1 + \mathbf{R}_2}$$

Let the hysteresis be  $V_H$ , and calculate  $R_3$ :

$$\mathbf{R}_3 = \frac{\mathbf{V}_0}{\mathbf{V}_H} \times (\mathbf{R}_1 \parallel \mathbf{R}_2)$$

where:

$V_{O}=V_{SD}-0.8V$  (swing of the output)

Recalculate  $R_2$  to maintain the same value of  $V_{TH}$ :

$$R_{2}1 = (V_{REF} - V_{TH}) \div \left(\frac{V_{TH}}{R_{1}} + \frac{V_{TH} - 0.5V_{SD}}{R_{3}}\right)$$

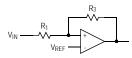

Non inverting comparator with hysteresis:

$R_3$  adds a portion of the output to the positive input. Note that the current through  $R_3$  should be much greater than the input bias current in order to minimize errors. The calculation of the resistor values as follows:

Pick the value of  $R_1$ .  $R_1$  should be small (less than  $1k\Omega$ ) in order to minimize the propagation delay time.

Choose the hysteresis  $V_H$  and calculate  $R_3$ :

$$R_3 = (V_{SD} - 0.8) \times \frac{R_1}{V_H}$$

Check the current through  $R_3$  and make sure that it is much greater than the input bias current as follows:

$$I = \frac{0.5V_{SD} - V_{REF}}{R_3}$$

The above two methods will generate hysteresis of up to a few hundred millivolts. Beyond that, the impedance of  $R_3$  is low enough to affect the bias string and adjustment of  $R_1$  may be required.

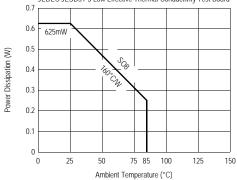

#### **Power Dissipation**

When switching at high speeds, the comparator's drive capability is limited by the rise in junction temperature caused by the internal power dissipation. For reliable operation, the junction temperature must be kept below  $T_{JMAX}$  (125°C).

An approximate equation for the device power dissipation is as follows. Assume the power dissipation in the load is very small:

$$P_{DISS} = (V_S \times I_S + V_{SD} \times I_{SD})$$

where:

$V_S$  is the analog supply voltage from  $V_S$ + to  $V_S$ -

Is is the analog quiescent supply current per comparator

V<sub>SD</sub> is the digital supply voltage from V<sub>SD</sub> to ground

I<sub>SD</sub> is the digital supply current per comparator

I<sub>SD</sub> strongly depends on the input switching frequency. Please refer to the performance curve to choose the input driving frequency. Having obtained the power dissipation, the maximum junction temperature can be determined as follows:

$$T_{JMAX} = T_{MAX} + \Theta_{JA} \times P_{DISS}$$

where:

T<sub>MAX</sub> is the maximum ambient temperature

$\theta_{\text{JA}}$  is the thermal resistance of the package

#### **Threshold Detector**

The inverting input is connected to a reference voltage and the non-inverting input is connected to the input. As the input passes the  $V_{REF}$  threshold, the comparator's

output changes state. The non-inverting and inverting inputs may be reversed.

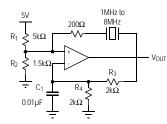

#### **Crystal Oscillator**

A simple crystal oscillator using one comparator of an EL5181C is shown below. The resistors  $R_1$  and  $R_2$  set the bias point at the comparator's non-inverting input. Resistors R<sub>3</sub>, R<sub>4</sub>, and C<sub>1</sub> set the inverting input node at an appropriate DC average voltage based on the output. The crystal's path provides resonant positive feedback and stable oscillation occurs. Although the EL5181C will give the correct logic output when an input is outside the common mode range, additional delays may occur when it is so operated. Therefore, the DC bias voltages at the inputs are set about 500mV below the center of the common mode range and the  $200\Omega$  resistor attenuates the feedback to the non-inverting input. The circuit will operate with most AT-cut crystal from 1MHz to 8MHz over a 2V to 7V supply range. The output duty cycle for this circuit is roughly 50% at 5V  $V_{CC}$ , but it is affected by the tolerances of the resistors. The duty cycle can be adjusted by changing V<sub>CC</sub> value.

# **EL5181C** 8ns High-Speed Comparator

#### **General Disclaimer**

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

Elantec Semiconductor, Inc.

675 Trade Zone Blvd. Milpitas, CA 95035 Telephone: (408) 945-1323 (888) ELANTEC Fax: (408) 945-9305 European Office: +44-118-977-6020 Japan Technical Center: +81-45-682-5820

### WARNING - Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. Products in Life Support Systems are requested to contact Elantec, Inc. factory headquarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.

June 14, 2001