EL5825C - Preliminary

8-Channel TFT-LCD Reference Voltage Generator

### Features

- 8-channel reference outputs

- Accuracy of ±0.1%

- Supply voltage of 5V to 16V

- Digital supply 3.3V to 5V

- Low supply current of 10mA

- Rail-to-rail capability

## Applications

- TFT-LCD drive circuits

- Reference voltage generators

### **Ordering Information**

| Part No  | Package      | Tape & Reel | Outline # |

|----------|--------------|-------------|-----------|

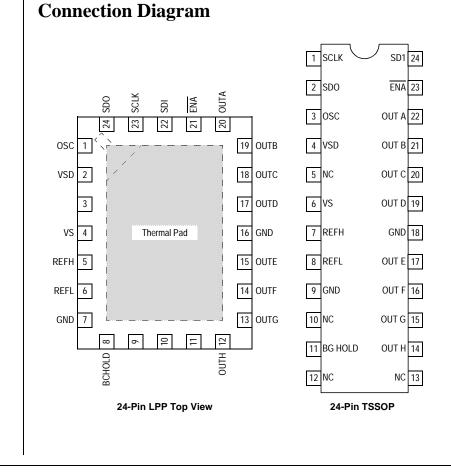

| EL5825CU | 24-Pin LPP   | -           | MDP0046   |

| EL5825CR | 24-Pin TSSOP | -           | MDP0044   |

## **General Description**

The EL5825C is designed to produce the reference voltages required in TFT-LCD applications. Each output is programmed to the required voltage with 10 bits of resolution. Reference pins determine the high and low voltages of the output range, which are capable of swinging to either supply rail. Programming of each output is performed using the serial interface. A serial out pin enables daisy chaining of multiple devices.

A number of the EL5825C can be stacked for applications requiring more than 8 outputs. The reference inputs can be tied to the rails, enabling each part to output the full voltage range, or alternatively, they can be connected to external resistors to split the output range and enable finer resolutions of the outputs.

The EL5825C has 8 outputs and is available in both the 24-pin TSSOP and the 24-pin LPP packages. It is specified for operation over the full  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a "controlled document". Current revisions, if any, to these specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

© 2001 Elantec Semiconductor, Inc.

# EL5825C - Preliminary

8-Channel TFT-LCD Reference Voltage Generator

## Absolute Maximum Ratings $(T_A = 25^{\circ}C)$

| Values beyond absolute maximum ratings can cause the device to be pre-<br>maturely damaged. Absolute maximum ratings are stress ratings only and |                              | Maximum Die Temperature | +125°C          |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------|-----------------|

|                                                                                                                                                  |                              | Storage Temperature     | -65°C to +150°C |

| functional device operation is not implied.                                                                                                      |                              | Operating Temperature   | -40°C to +85°C  |

| Supply Voltage between V <sub>S</sub> and GND                                                                                                    | +18V                         | Lead Temperature        | 260°C           |

| Supply Voltage between VSD and GND                                                                                                               | V <sub>S</sub> and +7V (min) | Power Dissipation       | See Curves      |

| Maximum Continuous Output Current                                                                                                                | 30mA                         | 1                       | 2kV             |

|                                                                                                                                                  |                              | ESD Voltage             | ZKV             |

#### Important Note:

All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$ .

### **Electrical Characteristics**

$V_S = 15V, V_{SD} = 5V, V_{REFH} = 13V, V_{REFL} = 2V, R_L = 1.5 k\Omega \text{ and } C_L = 200 pF \text{ to } 0V, T_A = 25^{\circ} C \text{ unless otherwise specified.}$

| Parameter         | Description                       | Condition                                 | Min                  | Тур  | Max                 | Unit  |

|-------------------|-----------------------------------|-------------------------------------------|----------------------|------|---------------------|-------|

| Supply            |                                   |                                           |                      |      |                     |       |

| Is                | Supply Current                    | No load                                   |                      | 10   | TBD                 | mA    |

| I <sub>SD</sub>   | Digital Supply Current            |                                           |                      |      | 1                   | mA    |

| Analog            |                                   |                                           |                      |      |                     |       |

| V <sub>OL</sub>   | Output Swing Low                  | $R_L = 1.5 k\Omega$ to 7.5V, after 1mS    |                      | 100  | 200                 | mV    |

| V <sub>OH</sub>   | Output Swing High                 | $R_L = 1.5 k\Omega$ to 7.5V, after 1mS    | 14.75                | 14.9 |                     | V     |

| I <sub>SC</sub>   | Short Circuit Current             | $R_L = 10\Omega$                          | 100                  |      |                     | mA    |

| PSRR              | Power Supply Rejection Ratio      | V <sub>S</sub> + is moved from 14V to 16V | TBD                  | TBD  |                     | dB    |

| V <sub>OS</sub>   | Offset Voltage                    | $V_{OUT} = V_S / 2$                       |                      | 2    | 5                   | mV    |

| tD                | Program to Out Delay              |                                           |                      | TBD  |                     | mS    |

| V <sub>AC</sub>   | Accuracy                          |                                           |                      | TBD  | 12                  | mV    |

| VDROOP            | Droop Voltage                     |                                           |                      | TBD  | 15                  | mV/mS |

| R <sub>INH</sub>  | Input Resistance @ VREFH          | $V_{REFH} = 15V$                          |                      | 32   |                     | kΩ    |

| R <sub>INL</sub>  | Input Resistance @ VREFL          | $V_{REFL} = 0V$                           |                      | 32   |                     | kW    |

| REG               | Load Regulation                   | $I_{OUT} = 5mA$ step                      |                      |      | 2                   | mV    |

| Digital           |                                   |                                           |                      |      |                     |       |

| V <sub>IH</sub>   | Logic 1 Input Voltage             |                                           | V <sub>SD</sub> -20% |      |                     | V     |

| V <sub>IL</sub>   | Logic 0 Input Voltage             |                                           |                      |      | 20%*V <sub>SD</sub> | V     |

| F <sub>CLK</sub>  | Clock Frequency                   |                                           |                      |      | 5                   | MHz   |

| t <sub>S</sub>    | Setup Time                        |                                           |                      | 10   |                     | ns    |

| t <sub>H</sub>    | Hold Time                         |                                           |                      | 10   |                     | ns    |

| t <sub>LC</sub>   | Load to Clock Time                |                                           |                      | 10   |                     | ns    |

| t <sub>CE</sub>   | Clock to Load Line                |                                           |                      | 10   |                     | ns    |

| tDCO              | Clock to Out Delay Time           |                                           |                      |      |                     | ns    |

| R <sub>SDIN</sub> | S <sub>DIN</sub> Input Resistance |                                           |                      | 1    |                     | GΩ    |

# EL5825C - Preliminary

8-Channel TFT-LCD Reference Voltage Generator

General Disclaimer

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

### **Elantec Semiconductor, Inc.**

675 Trade Zone Blvd. Milpitas, CA 95035 Telephone: (408) 945-1323 (800) ELANTEC Fax: (408) 945-9305 European Office: 44-118-977-6020 Japan Technical Center: 81-45-682-5820

### WARNING - Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. Products in Life Support Systems are requested to contact Elantec, Inc. factory headquarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.