REJ09B0273-0500

ardware

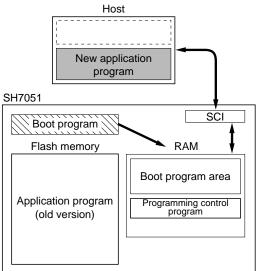

Manu

# SH7050 Group, SH7050F-ZTAT™, SH7051F-ZTAT™ Hardware Manual

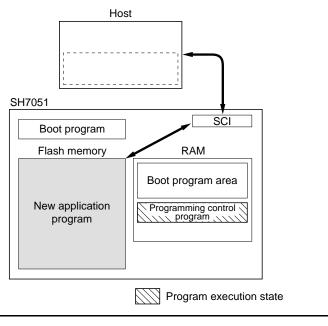

**Renesas 32-Bit RISC Microcomputer** SuperH<sup>™</sup> RISC engine Family/SH7050 Series

> HD6437050 HD64F7050 HD64F7051

RenesasTechnology www.renesas.com  Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

Rev. 5.00 Jan 06, 2006 page ii of xx

## Preface

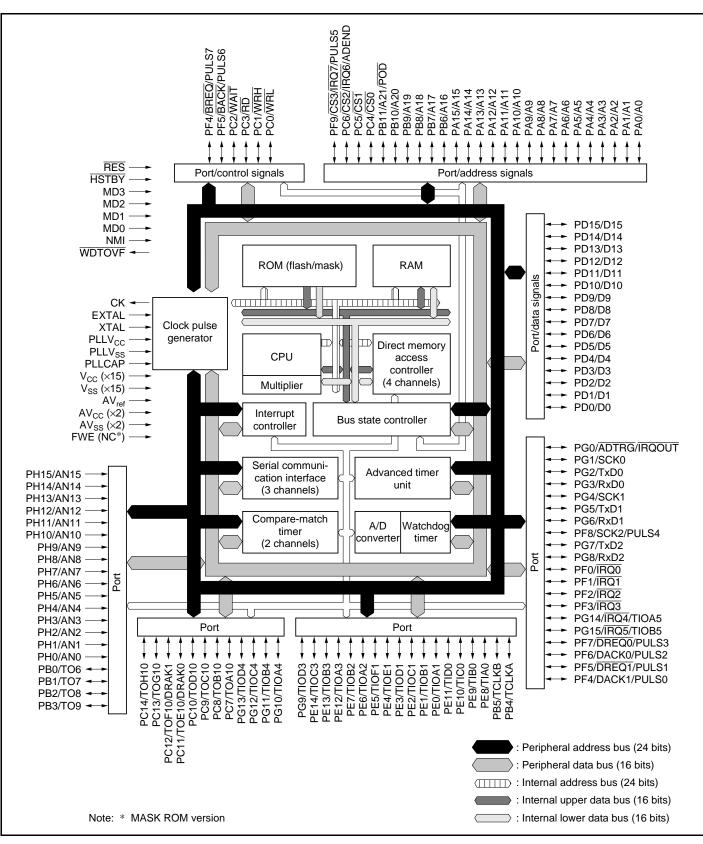

The SH7050 series (SH7050, SH7051) is a single-chip RISC microcontroller that integrates a RISC CPU core using an original Renesas architecture with peripheral functions required for system configuration.

The CPU has a RISC-type instruction set. Most instructions can be executed in one state (one system clock cycle), which greatly improves instruction execution speed. In addition, the 32-bit internal architecture enhances data processing power. With this CPU, it has become possible to assemble low-cost, high-performance/high-functionality systems even for applications such as real-time control, which could not previously be handled by microcontrollers because of their high-speed processing requirements.

In addition, the SH7050 series includes on-chip peripheral functions necessary for synchronous configuration, such as large-capacity ROM and RAM, a direct memory access controller (DMAC), timers, a serial communication interface (SCI), A/D converter, interrupt controller (INTC), and I/O ports.

ROM and SRAM can be directly connected by means of an external memory access support function, greatly reducing system cost.

There are versions of on-chip ROM: mask ROM and flash memory. The flash memory can be programmed with a programmer that supports SH7050 series programming, and can also be programmed and erased by software.

This hardware manual describes the SH7050 series hardware. Refer to the programming manual for a detailed description of the instruction set.

#### **Related Manual**

SH7050 series instructions

SH-1/SH-2/SH-DSP Software Manual (Document No. REJ09B0171-05000)

Please consult your Renesas sales representative for details of development environment system.

Rev. 5.00 Jan 06, 2006 page iv of xx

## Main Revisions for This Edition

| ltem                             | Page | Revision                                | (See Manual                             | for Deta            | ils)            |                     |     |     |      |

|----------------------------------|------|-----------------------------------------|-----------------------------------------|---------------------|-----------------|---------------------|-----|-----|------|

| All                              |      |                                         | nces to Hitach<br>chi brand nar         |                     | •               |                     |     |     | •    |

|                                  |      | -                                       | due to change $68B \rightarrow PRQF$    | -                   | -               | les.                |     |     |      |

| 2.3.3 Instruction<br>Format      | 35   | Table amo                               | ended                                   | _                   |                 | _                   | _   |     |      |

|                                  |      | Instruction F                           | ormats                                  | Source<br>Operand   | I               | Destinat<br>Operanc |     |     |      |

| Table 2.9<br>Instruction Formats |      | d format<br>15<br>xxxx xxx              | 0                                       |                     |                 | ddddddd<br>relative |     |     |      |

|                                  |      | d12 format<br>15<br>xxxx ddc            | 0<br>Id dddd dddd                       | =                   |                 | dddddd<br>PC relati |     |     |      |

| 13.2.8 Bit Rate                  | 385  | Descriptic                              | n amended                               |                     |                 |                     |     |     |      |

| Register (BRR)                   |      | Synchron                                | ous mode:                               |                     |                 |                     |     |     |      |

|                                  |      | N =                                     | $\frac{\phi}{2^{2n-1} \times B} \times$ | 10 <sup>6</sup> – 1 |                 |                     |     |     |      |

| 22.2 DC                          | 655  | Table am                                | ended                                   |                     |                 |                     |     |     |      |

| Characteristics                  |      | Item                                    | Pin                                     | Symbol              | Min             | Тур                 | Ма  | x   | Unit |

| Table 22.2 DC<br>Characteristics |      | Reference<br>power<br>supply<br>current | During A/D<br>conversion                | AI <sub>ref</sub>   | _               | 1.0                 | 5   |     | mA   |

| Table 22.3                       | 656  | Table am                                | ended                                   |                     |                 |                     |     |     |      |

| Permitted Output                 |      | Item                                    |                                         |                     | Symbol          | Min                 | Тур | Мах | Unit |

| Current Values                   |      | Output low-lev                          | el permissible curre                    | nt (per pin)        | I <sub>ol</sub> |                     |     | 8.0 | mA   |

Rev. 5.00 Jan 06, 2006 page vi of xx

## Contents

| Secti | on 1                                | Overview                        | 1  |  |

|-------|-------------------------------------|---------------------------------|----|--|

| 1.1   |                                     | es                              | 1  |  |

| 1.2   | Block                               | Diagram                         | 7  |  |

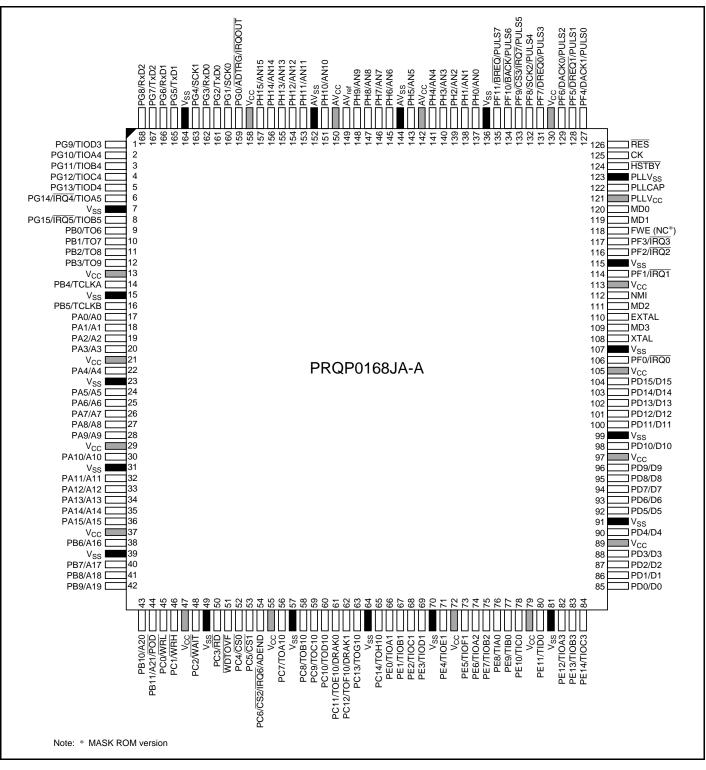

| 1.3   | 3 Pin Arrangement and Pin Functions |                                 |    |  |

|       | 1.3.1                               | Pin Arrangement                 | 8  |  |

|       | 1.3.2                               | Pin Functions                   | 9  |  |

|       | 1.3.3                               | Pin Assignments                 | 15 |  |

| Secti | on 2                                | CPU                             | 21 |  |

| 2.1   |                                     | er Configuration                | 21 |  |

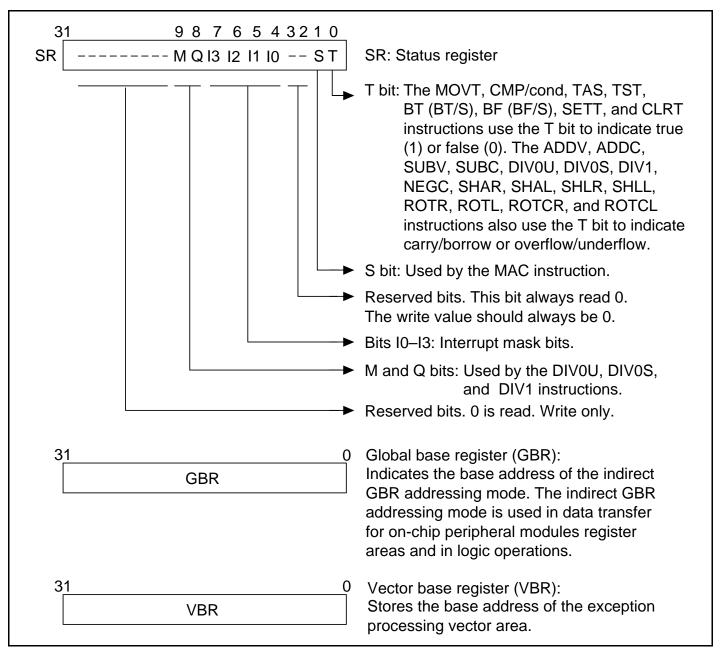

|       | 2.1.1                               | General Registers (Rn)          | 21 |  |

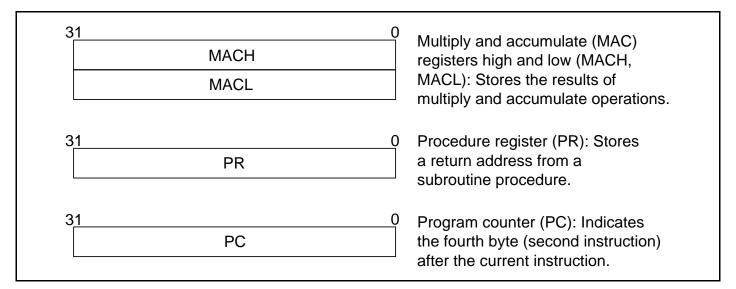

|       | 2.1.2                               | Control Registers               | 22 |  |

|       | 2.1.3                               | System Registers                | 23 |  |

|       | 2.1.4                               | Initial Values of Registers     | 23 |  |

| 2.2   | Data F                              | ormats                          | 24 |  |

|       | 2.2.1                               | Data Format in Registers        | 24 |  |

|       | 2.2.2                               | Data Format in Memory           | 24 |  |

|       | 2.2.3                               | Immediate Data Format           | 25 |  |

| 2.3   | Instruc                             | tion Features                   | 25 |  |

|       | 2.3.1                               | RISC-Type Instruction Set       | 25 |  |

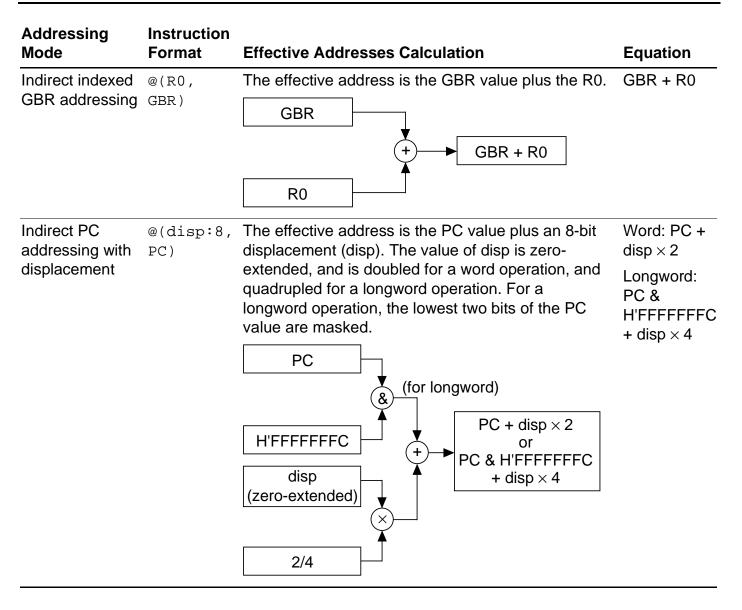

|       | 2.3.2                               | Addressing Modes                | 29 |  |

|       | 2.3.3                               | Instruction Format              | 33 |  |

| 2.4   | Instruc                             | tion Set by Classification      | 36 |  |

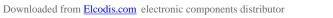

| 2.5   | Proces                              | sing States                     | 48 |  |

|       | 2.5.1                               | State Transitions               | 48 |  |

| Secti | on 3                                | Operating Modes                 | 51 |  |

| 3.1   |                                     | ing Mode Selection              | 51 |  |

|       | Ĩ                                   |                                 |    |  |

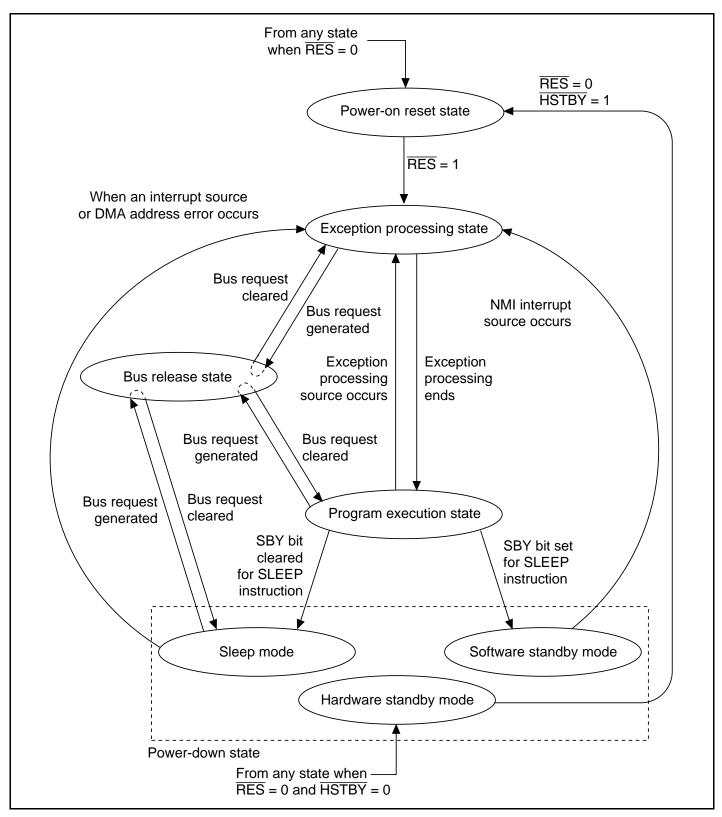

| Secti | on 4                                | Clock Pulse Generator (CPG)     | 53 |  |

| 4.1   |                                     | iew                             | 53 |  |

|       | 4.1.1                               | Block Diagram                   | 54 |  |

|       | 4.1.2                               | Pin Configuration               | 55 |  |

| 4.2   | Clock                               | Operating Modes                 | 55 |  |

| 4.3   |                                     | Source                          | 56 |  |

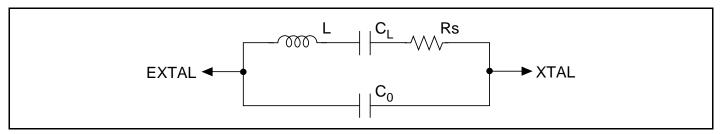

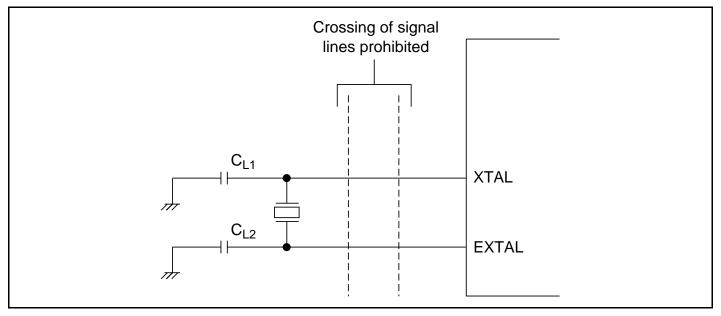

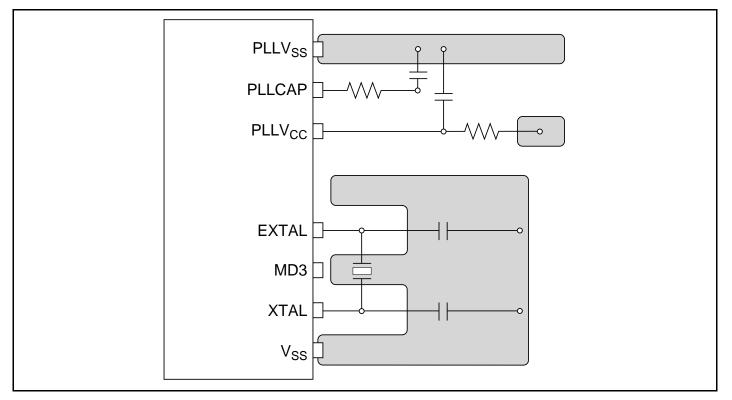

|       | 4.3.1                               | Connecting a Crystal Oscillator | 56 |  |

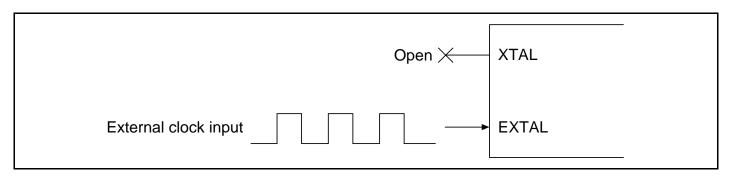

|       | 4.3.2                               | External Clock Input Method     | 57 |  |

Rev. 5.00 Jan 06, 2006 page vii of xx

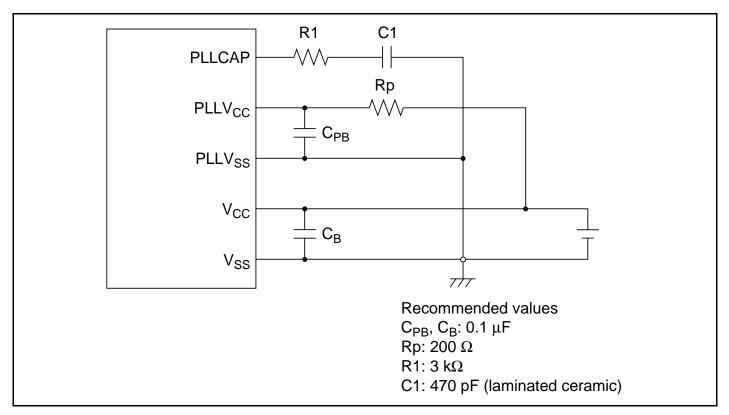

| 4.4   | Notes of | on Using                                                                | 58 |

|-------|----------|-------------------------------------------------------------------------|----|

| Secti | on 5 l   | Exception Processing                                                    | 61 |

| 5.1   | Overvie  | ew                                                                      | 61 |

|       | 5.1.1    | Types of Exception Processing and Priority                              | 61 |

|       | 5.1.2    | Exception Processing Operations                                         | 62 |

|       | 5.1.3    | Exception Processing Vector Table                                       | 63 |

| 5.2   | Resets.  |                                                                         | 65 |

|       | 5.2.1    | Power-On Reset                                                          | 65 |

| 5.3   | Addres   | s Errors                                                                | 66 |

|       | 5.3.1    | Address Error Sources                                                   | 66 |

|       | 5.3.2    | Address Error Exception Processing                                      | 67 |

| 5.4   | Interrup | pts                                                                     | 67 |

|       | 5.4.1    | Interrupt Sources                                                       | 67 |

|       | 5.4.2    | Interrupt Priority Level                                                | 68 |

|       | 5.4.3    | Interrupt Exception Processing                                          | 68 |

| 5.5   | Excepti  | ions Triggered by Instructions                                          | 69 |

|       | 5.5.1    | Types of Exceptions Triggered by Instructions                           | 69 |

|       | 5.5.2    | Trap Instructions                                                       | 69 |

|       | 5.5.3    | Illegal Slot Instructions                                               | 70 |

|       | 5.5.4    | General Illegal Instructions                                            | 70 |

| 5.6   | When H   | Exception Sources Are Not Accepted                                      | 71 |

|       | 5.6.1    | Immediately after a Delayed Branch Instruction                          | 71 |

|       | 5.6.2    | Immediately after an Interrupt-Disabled Instruction                     | 71 |

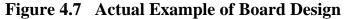

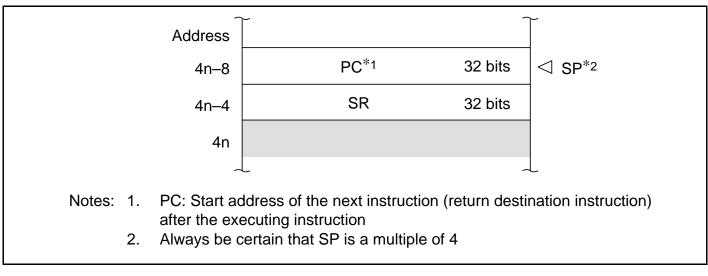

| 5.7   | Stack S  | tatus after Exception Processing Ends                                   | 72 |

| 5.8   | Notes of | on Use                                                                  | 73 |

|       | 5.8.1    | Value of Stack Pointer (SP)                                             | 73 |

|       | 5.8.2    | Value of Vector Base Register (VBR)                                     | 73 |

|       | 5.8.3    | Address Errors Caused by Stacking of Address Error Exception Processing | 73 |

| Secti | on 6     | Interrupt Controller (INTC)                                             | 75 |

| 6.1   | Overvie  | ew                                                                      | 75 |

|       | 6.1.1    | Features                                                                | 75 |

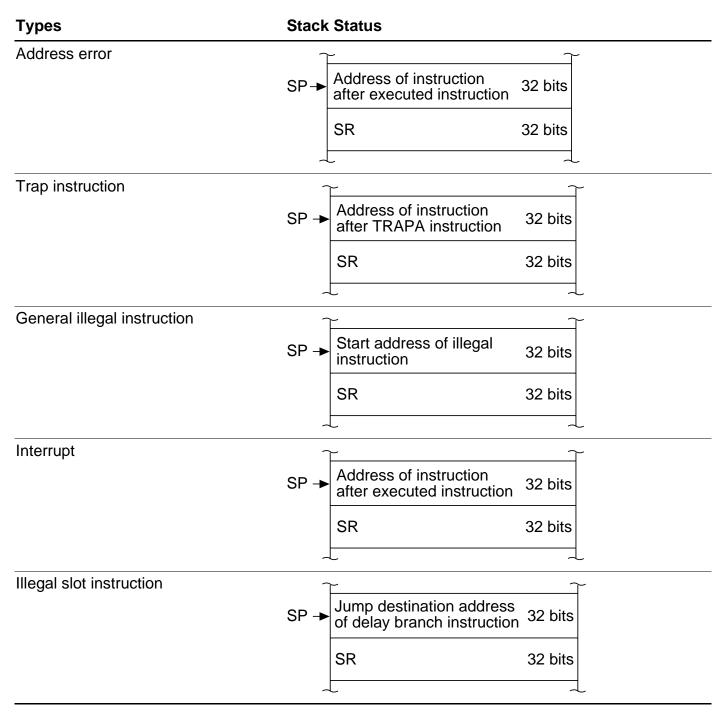

|       | 6.1.2    | Block Diagram                                                           | 76 |

|       | 6.1.3    | Pin Configuration                                                       | 77 |

|       | 6.1.4    | Register Configuration                                                  | 77 |

| 6.2   | Interruj | pt Sources                                                              | 78 |

|       | 6.2.1    | NMI Interrupts                                                          | 78 |

|       | 6.2.2    | User Break Interrupt                                                    | 78 |

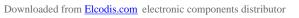

|       | 6.2.3    | IRQ Interrupts                                                          | 78 |

|       | 6.2.4    | On-Chip Peripheral Module Interrupts                                    | 79 |

|       |          |                                                                         |    |

Rev. 5.00 Jan 06, 2006 page viii of xx

|       | 6.2.5   | Interrupt Exception Vectors and Priority Rankings               | 79  |

|-------|---------|-----------------------------------------------------------------|-----|

| 6.3   | Descri  | ption of Registers                                              | 84  |

|       | 6.3.1   | Interrupt Priority Registers A-H (IPRA-IPRH)                    | 84  |

|       | 6.3.2   | Interrupt Control Register (ICR)                                | 86  |

|       | 6.3.3   | IRQ Status Register (ISR)                                       | 87  |

| 6.4   | Interru | pt Operation                                                    | 89  |

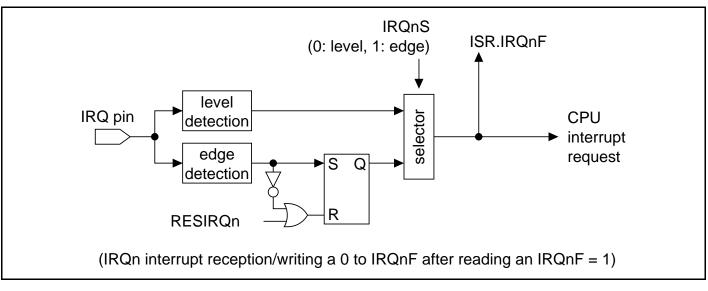

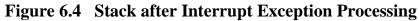

|       | 6.4.1   | Interrupt Sequence                                              | 89  |

|       | 6.4.2   | Stack after Interrupt Exception Processing                      | 91  |

| 6.5   | Interru | pt Response Time                                                | 92  |

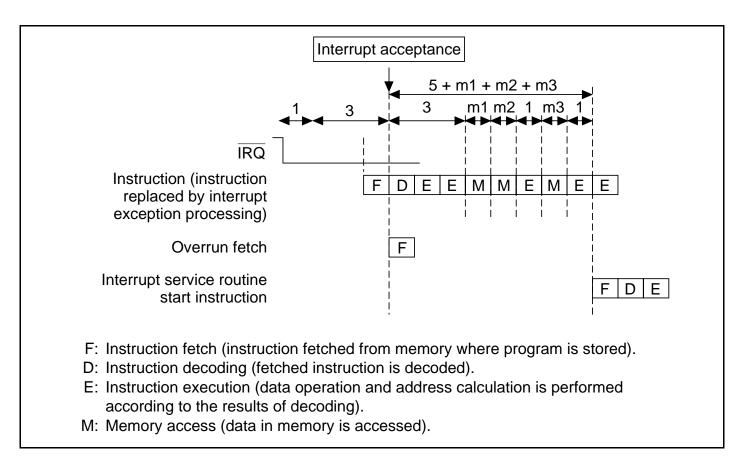

| 6.6   | Data 7  | Transfer with Interrupt Request Signals                         | 93  |

|       | 6.6.1   | Handling CPU Interrupt Sources, but Not DMAC Activating Sources | 94  |

|       | 6.6.2   | Handling DMAC Activating Sources but Not CPU Interrupt Sources  | 94  |

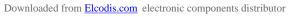

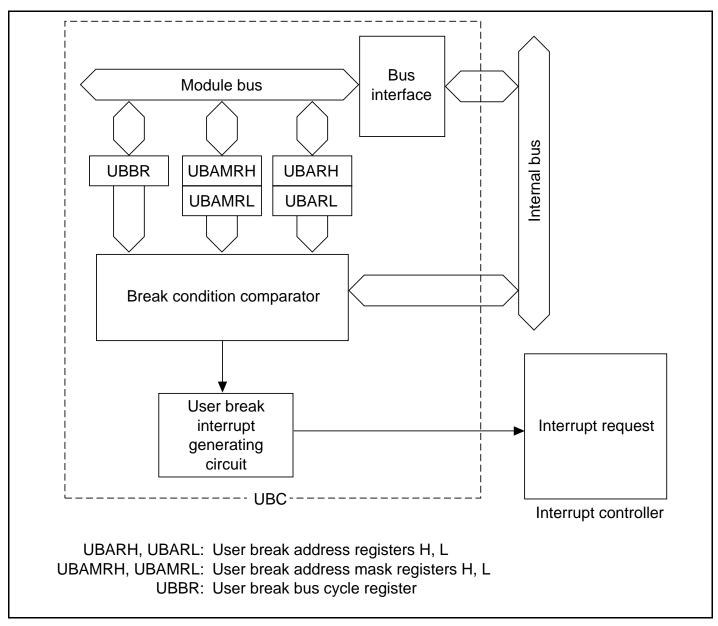

| Secti | on 7    | User Break Controller (UBC)                                     | 95  |

| 7.1   | Overv   | iew                                                             | 95  |

|       | 7.1.1   | Features                                                        | 95  |

|       | 7.1.2   | Block Diagram                                                   | 96  |

|       | 7.1.3   | Register Configuration                                          |     |

| 7.2   | Regist  | er Descriptions                                                 | 97  |

|       | 7.2.1   | User Break Address Register (UBAR)                              | 97  |

|       | 7.2.2   | User Break Address Mask Register (UBAMR)                        | 98  |

|       | 7.2.3   | User Break Bus Cycle Register (UBBR)                            | 100 |

| 7.3   | Opera   | tion                                                            | 102 |

|       | 7.3.1   | Flow of the User Break Operation                                | 102 |

|       | 7.3.2   | Break on On-Chip Memory Instruction Fetch Cycle                 | 104 |

|       | 7.3.3   | Program Counter (PC) Values Saved                               | 104 |

| 7.4   | Use E   | xamples                                                         | 105 |

|       | 7.4.1   | Break on CPU Instruction Fetch Cycle                            | 105 |

|       | 7.4.2   | Break on CPU Data Access Cycle                                  | 106 |

|       | 7.4.3   | Break on DMA/DTC Cycle                                          | 106 |

| 7.5   | Cautio  | ons on Use                                                      | 107 |

|       | 7.5.1   | On-Chip Memory Instruction Fetch                                | 107 |

|       | 7.5.2   | Instruction Fetch at Branches                                   | 107 |

|       | 7.5.3   | Contention between User Break and Exception Handling            | 108 |

|       | 7.5.4   | Break at Non-Delay Branch Instruction Jump Destination          |     |

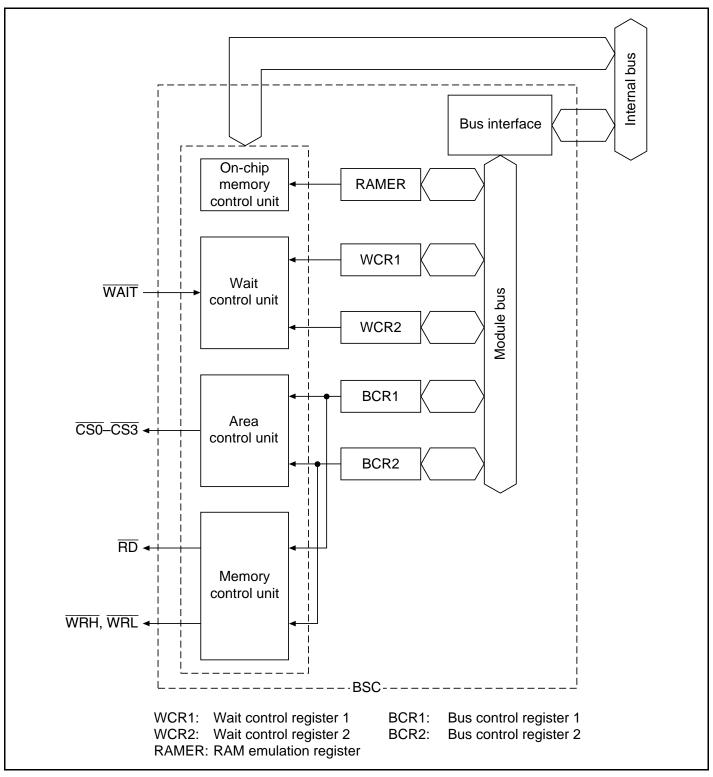

| Secti | on 8    | Bus State Controller (BSC)                                      | 109 |

| 8.1   | Overv   | iew                                                             | 109 |

|       | 8.1.1   | Features                                                        | 109 |

|       | 8.1.2   | Block Diagram                                                   |     |

|       | 8.1.3   | Pin Configuration                                               |     |

Rev. 5.00 Jan 06, 2006 page ix of xx

|       | 8.1.4  | Register Configuration                                           | 111 |

|-------|--------|------------------------------------------------------------------|-----|

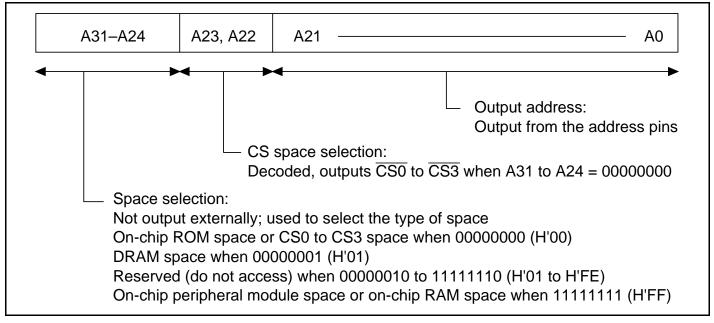

|       | 8.1.5  | Address Map                                                      | 112 |

| 8.2   | Descri | ption of Registers                                               | 115 |

|       | 8.2.1  | Bus Control Register 1 (BCR1)                                    | 115 |

|       | 8.2.2  | Bus Control Register 2 (BCR2)                                    | 116 |

|       | 8.2.3  | Wait Control Register 1 (WCR1)                                   | 119 |

|       | 8.2.4  | Wait Control Register 2 (WCR2)                                   | 121 |

|       | 8.2.5  | RAM Emulation Register (RAMER)                                   | 122 |

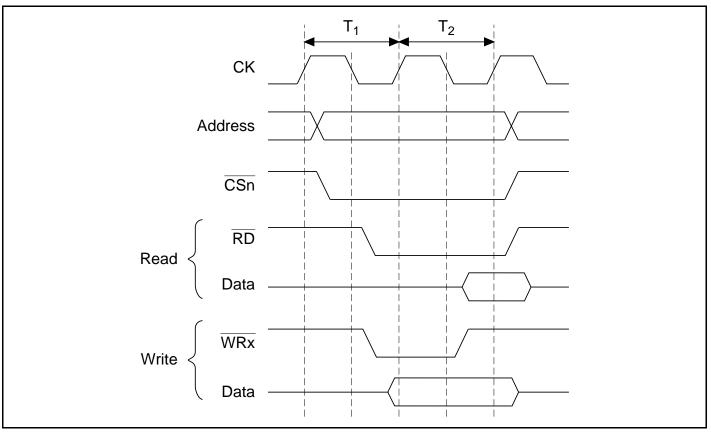

| 8.3   | Access | sing Ordinary Space                                              | 124 |

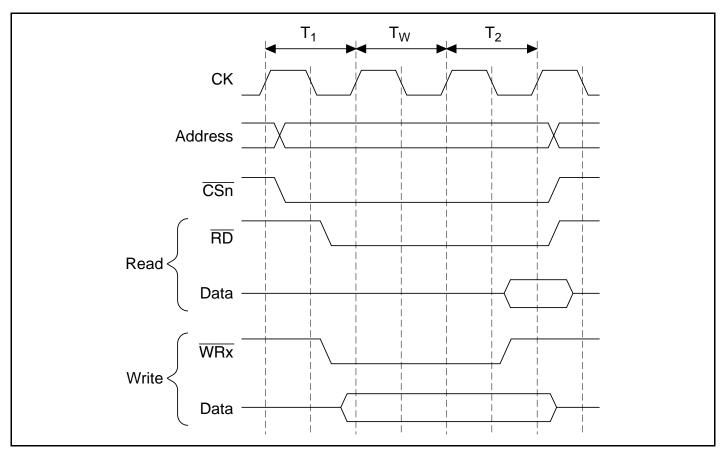

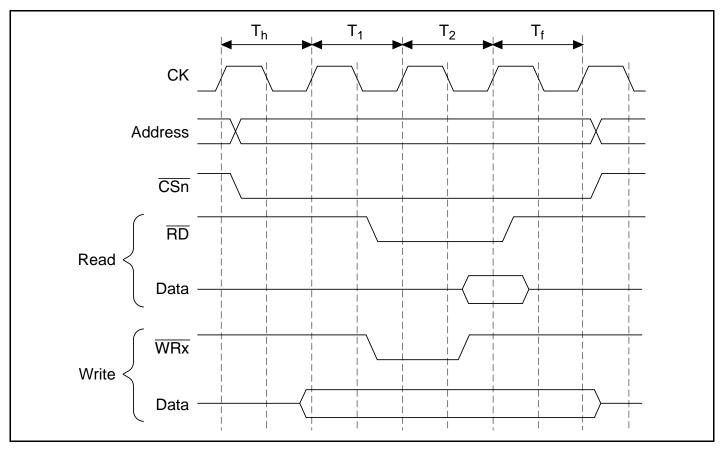

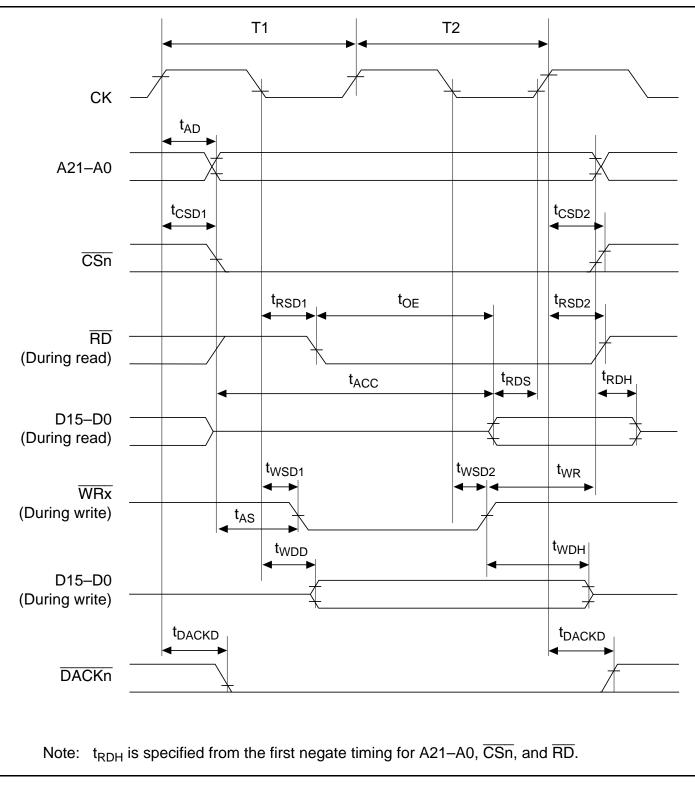

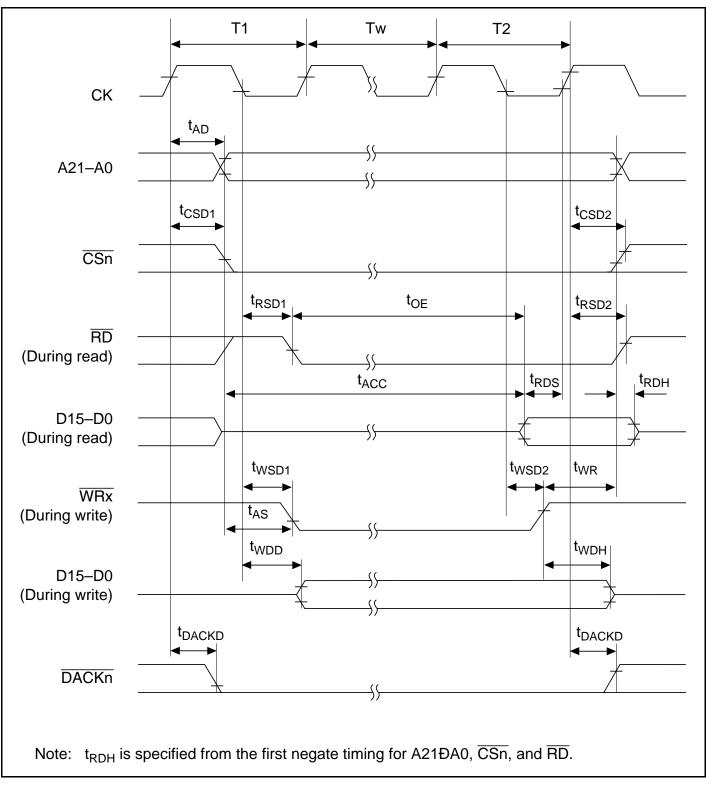

|       | 8.3.1  | Basic Timing                                                     | 124 |

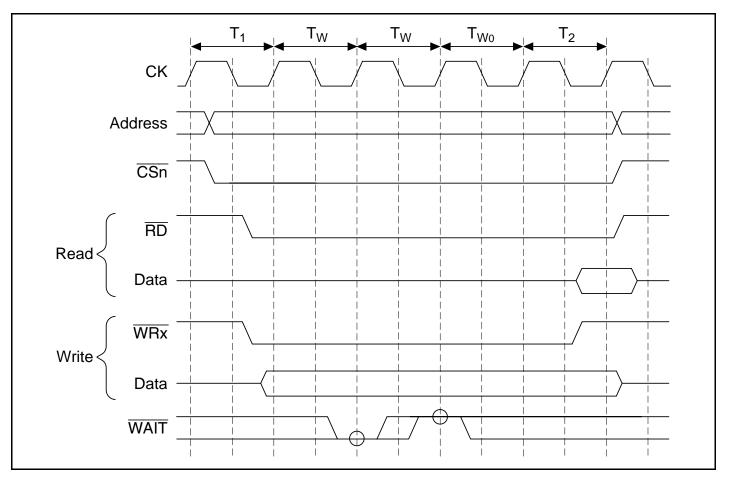

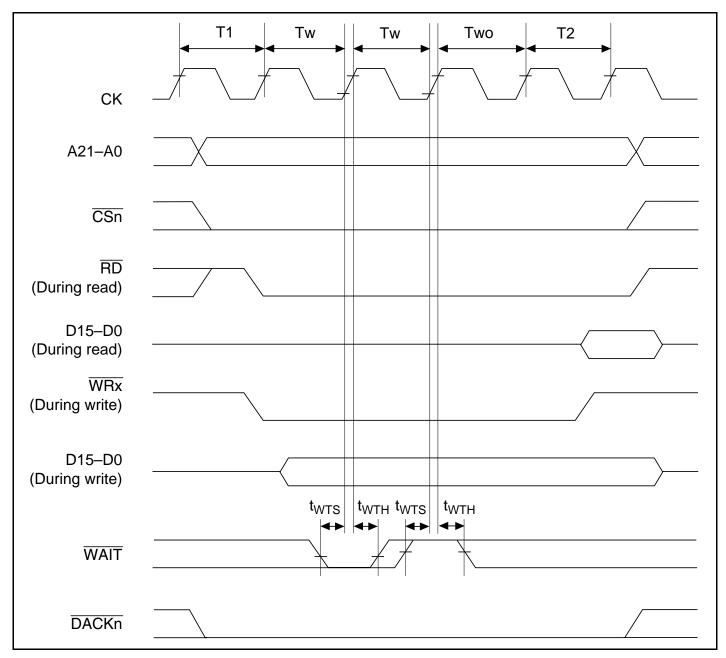

|       | 8.3.2  | Wait State Control                                               | 125 |

|       | 8.3.3  | CS Assert Period Extension                                       | 127 |

| 8.4   | Waits  | between Access Cycles                                            | 128 |

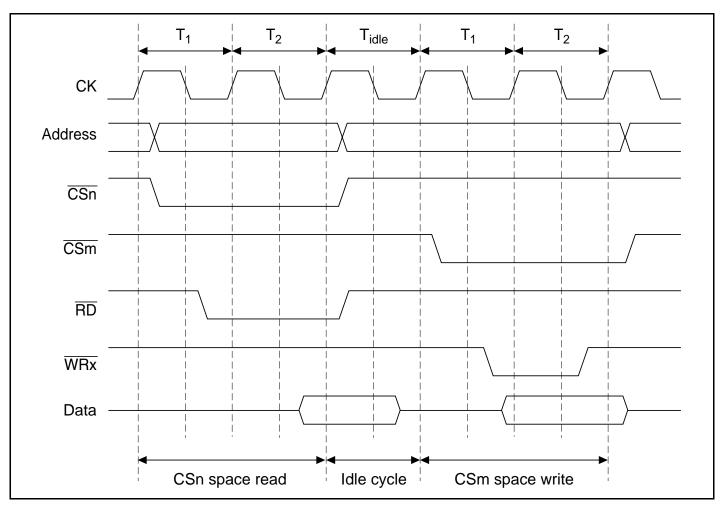

|       | 8.4.1  | Prevention of Data Bus Conflicts                                 | 128 |

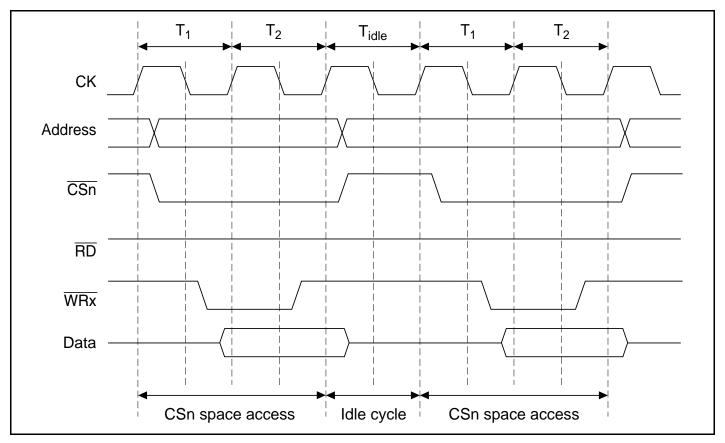

|       | 8.4.2  | Simplification of Bus Cycle Start Detection                      | 130 |

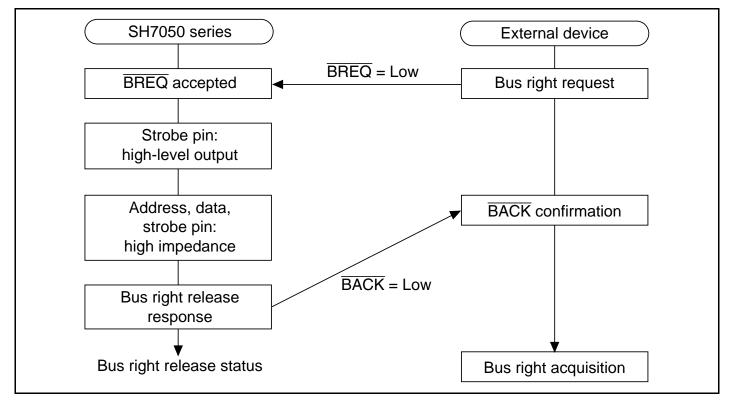

| 8.5   | Bus A  | rbitration                                                       | 131 |

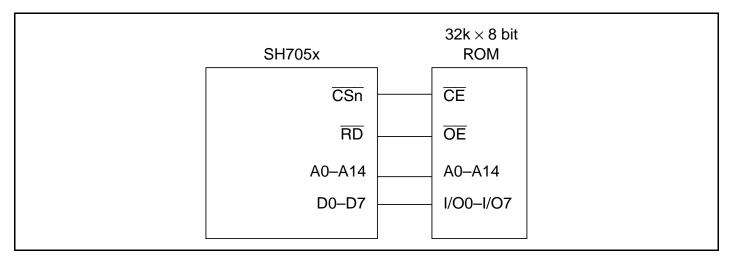

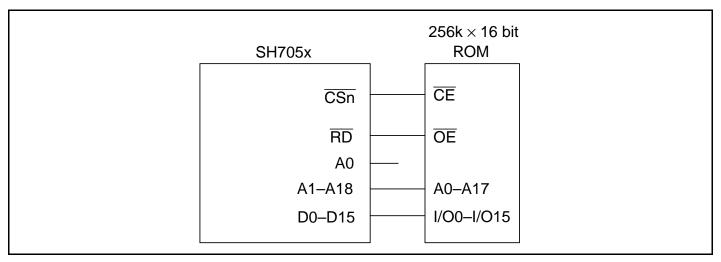

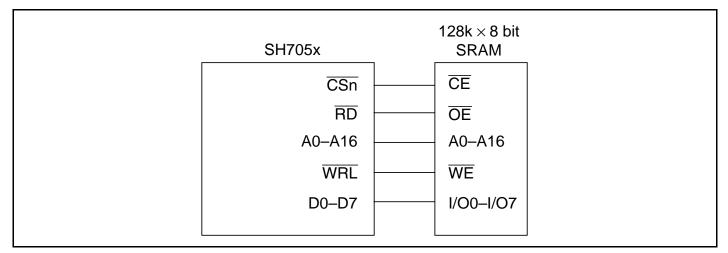

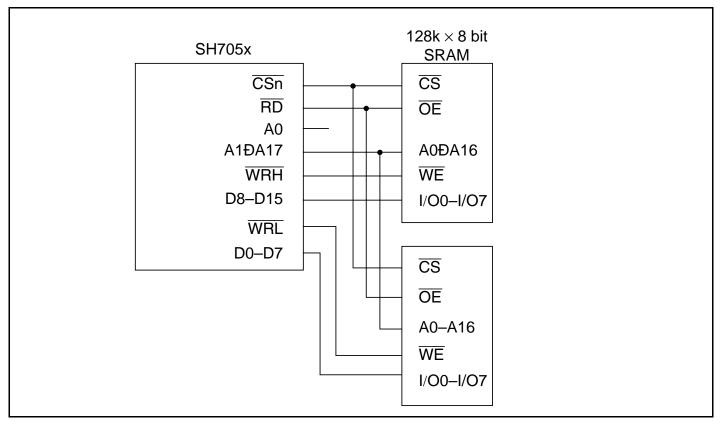

| 8.6   | Memo   | ry Connection Examples                                           | 132 |

|       |        |                                                                  |     |

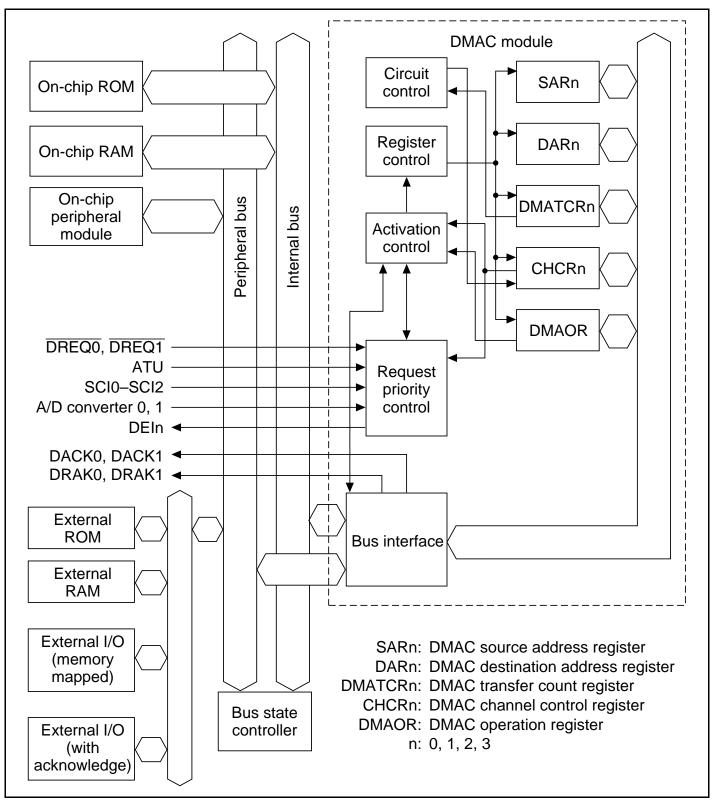

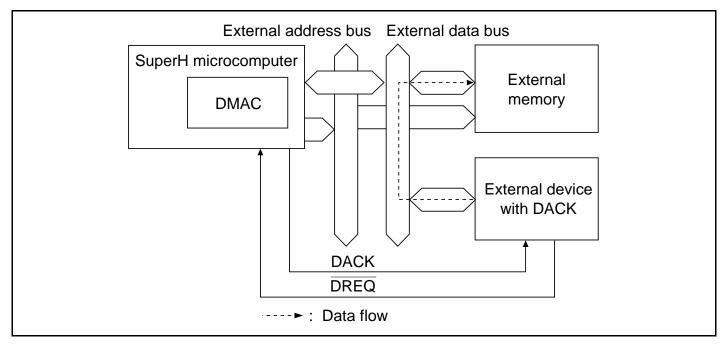

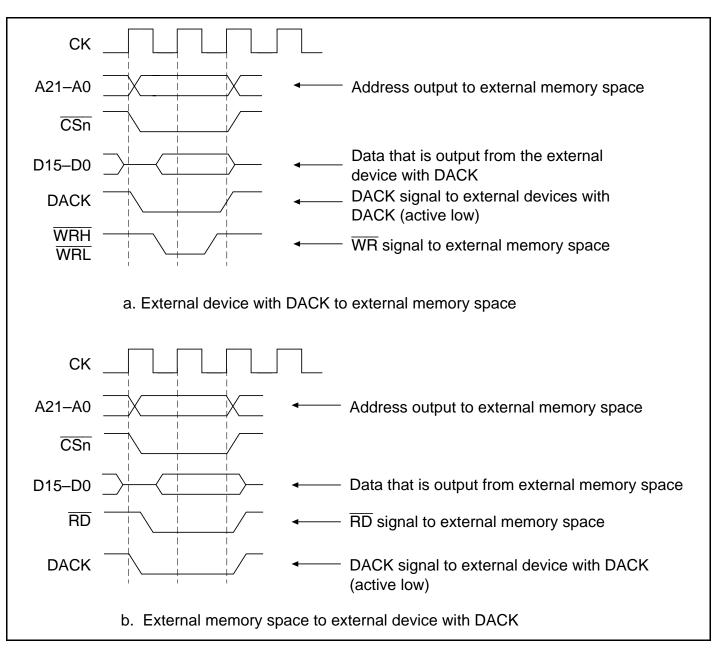

| Secti | on 9   | Direct Memory Access Controller (DMAC)                           | 135 |

| 9.1   | Overvi | ew                                                               | 135 |

|       | 9.1.1  | Features                                                         | 135 |

|       | 9.1.2  | Block Diagram                                                    | 137 |

|       | 9.1.3  | Pin Configuration                                                | 138 |

|       | 9.1.4  | Register Configuration                                           | 138 |

| 9.2   | Regist | er Descriptions                                                  | 140 |

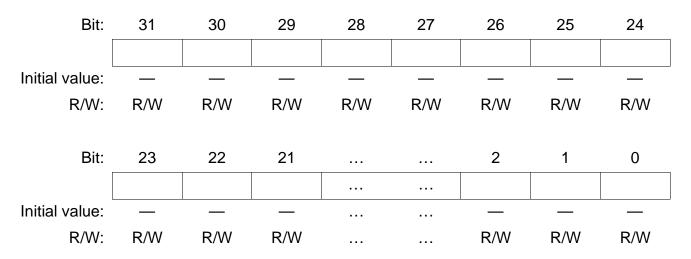

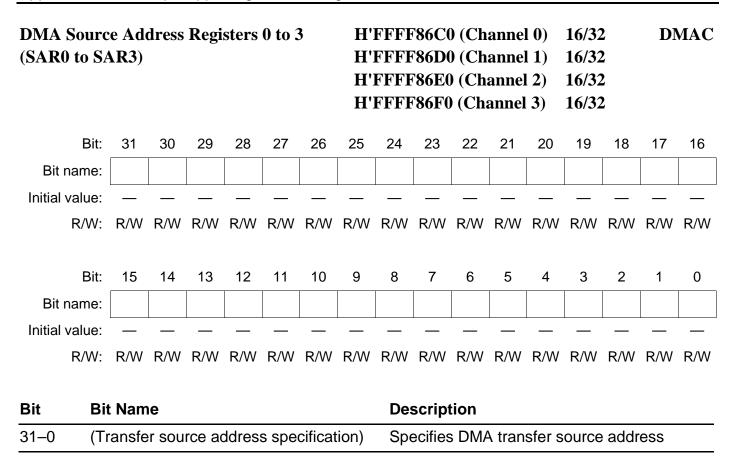

|       | 9.2.1  | DMA Source Address Registers 0-3 (SAR0-SAR3)                     |     |

|       | 9.2.2  | DMA Destination Address Registers 0–3 (DAR0–DAR3)                | 141 |

|       | 9.2.3  | DMA Transfer Count Registers 0–3 (DMATCR0–DMATCR3)               | 142 |

|       | 9.2.4  | DMA Channel Control Registers 0–3 (CHCR0–CHCR3)                  | 143 |

|       | 9.2.5  | DMAC Operation Register (DMAOR)                                  | 148 |

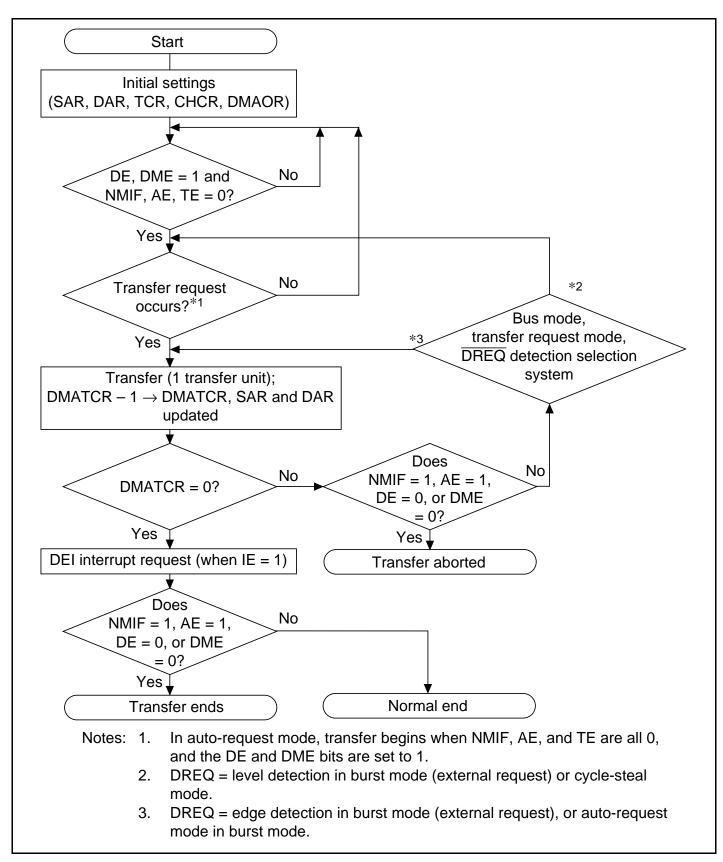

| 9.3   | •      | ion                                                              |     |

|       | 9.3.1  | DMA Transfer Flow                                                |     |

|       | 9.3.2  | DMA Transfer Requests                                            | 152 |

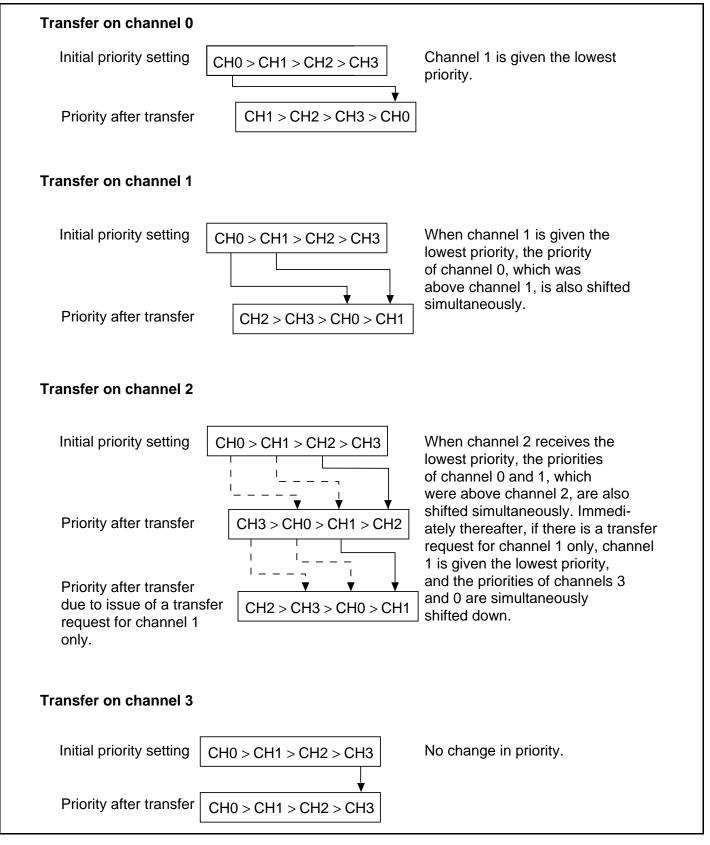

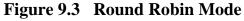

|       | 9.3.3  | Channel Priority                                                 |     |

|       | 9.3.4  | DMA Transfer Types                                               |     |

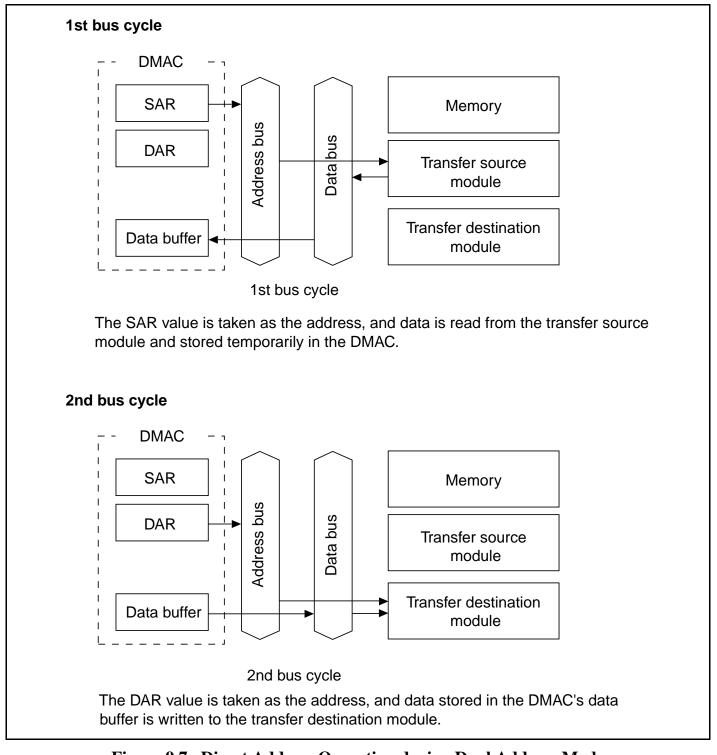

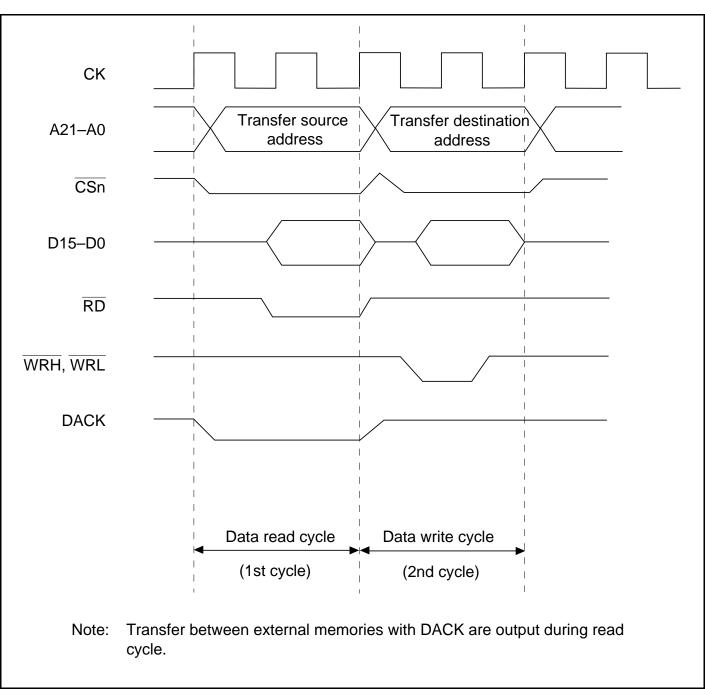

|       | 9.3.5  | Address Modes                                                    | 159 |

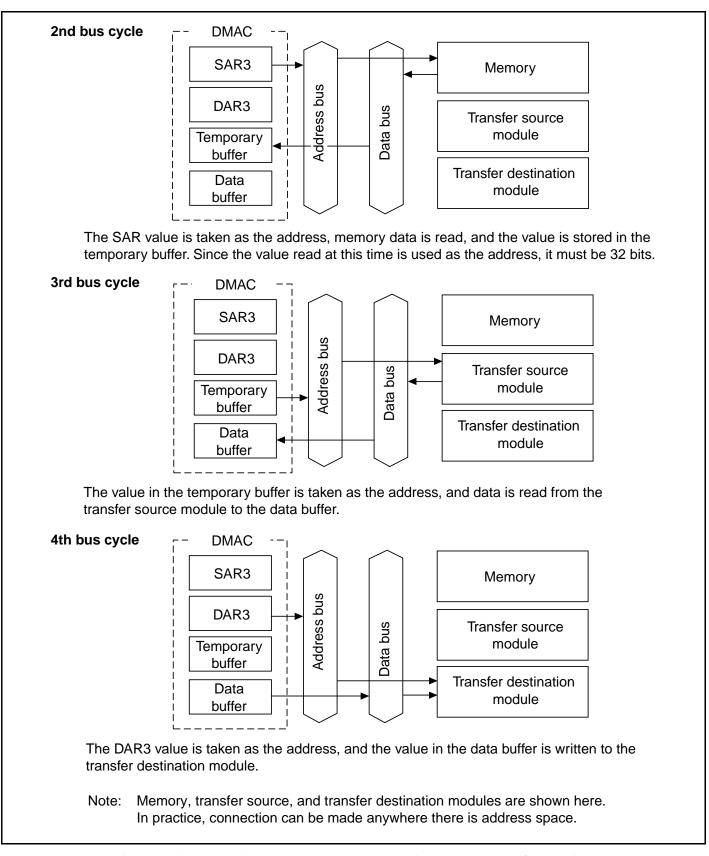

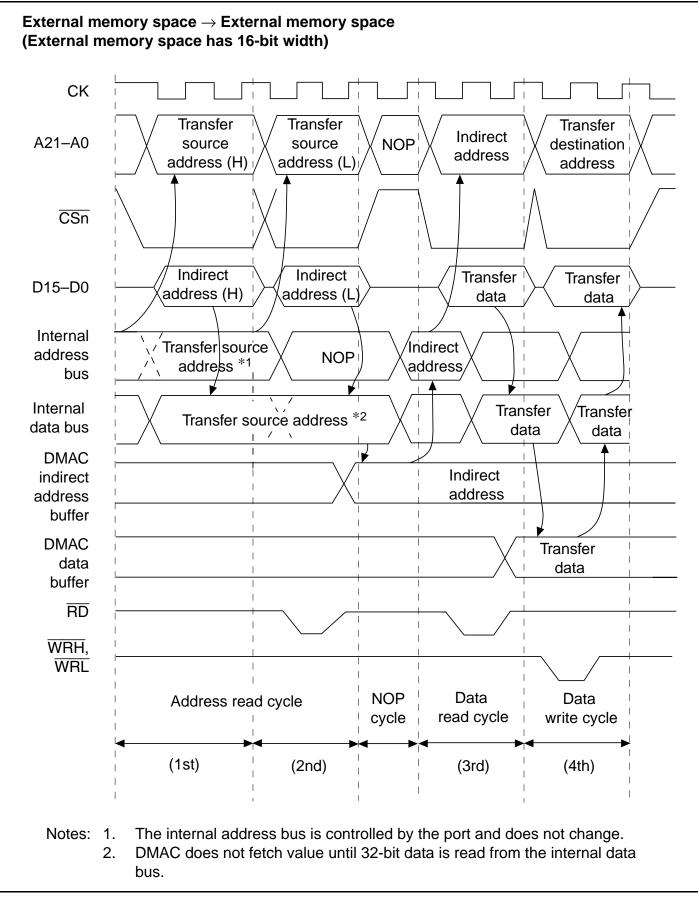

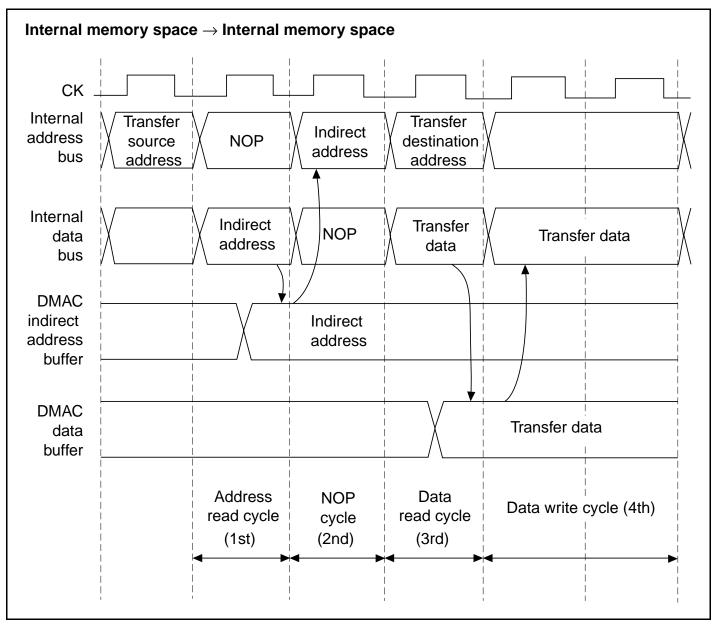

|       | 9.3.6  | Dual Address Mode                                                | 160 |

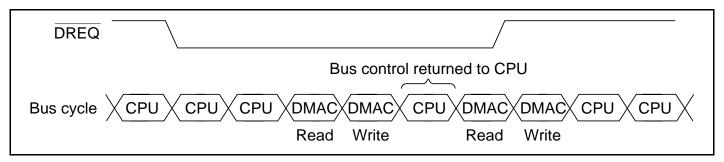

|       | 9.3.7  | Bus Modes                                                        | 167 |

|       | 9.3.8  | Relationship between Request Modes and Bus Modes by DMA Transfer |     |

|       |        | Category                                                         |     |

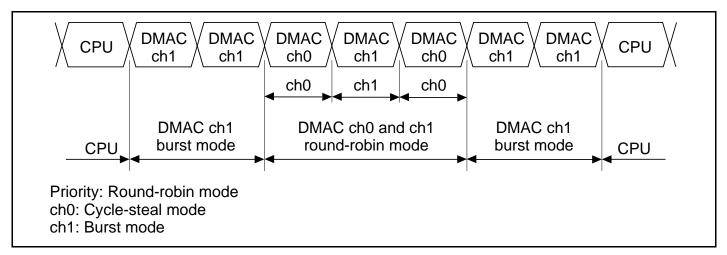

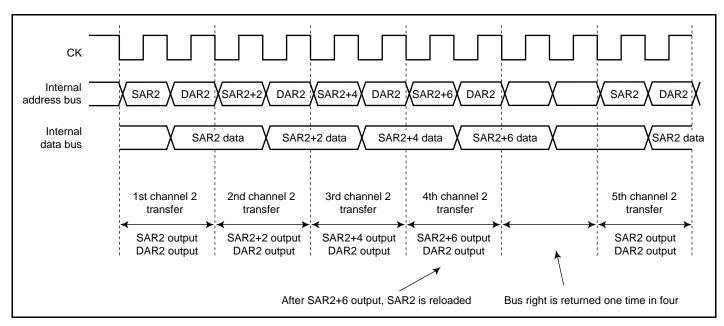

|       | 9.3.9  | Bus Mode and Channel Priority Order                              | 169 |

Rev. 5.00 Jan 06, 2006 page x of xx

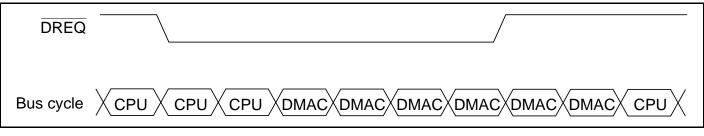

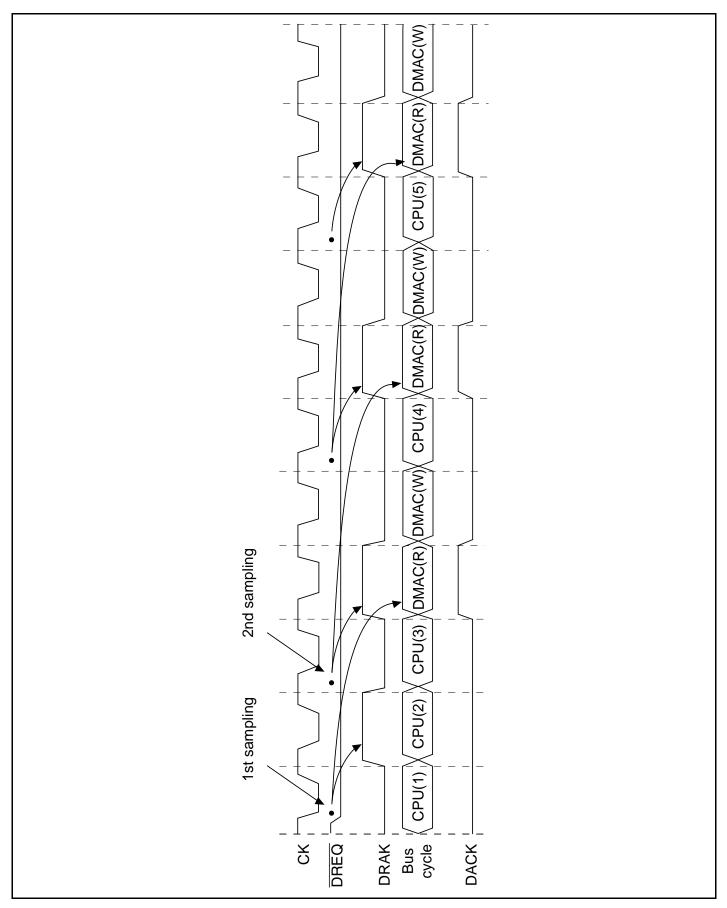

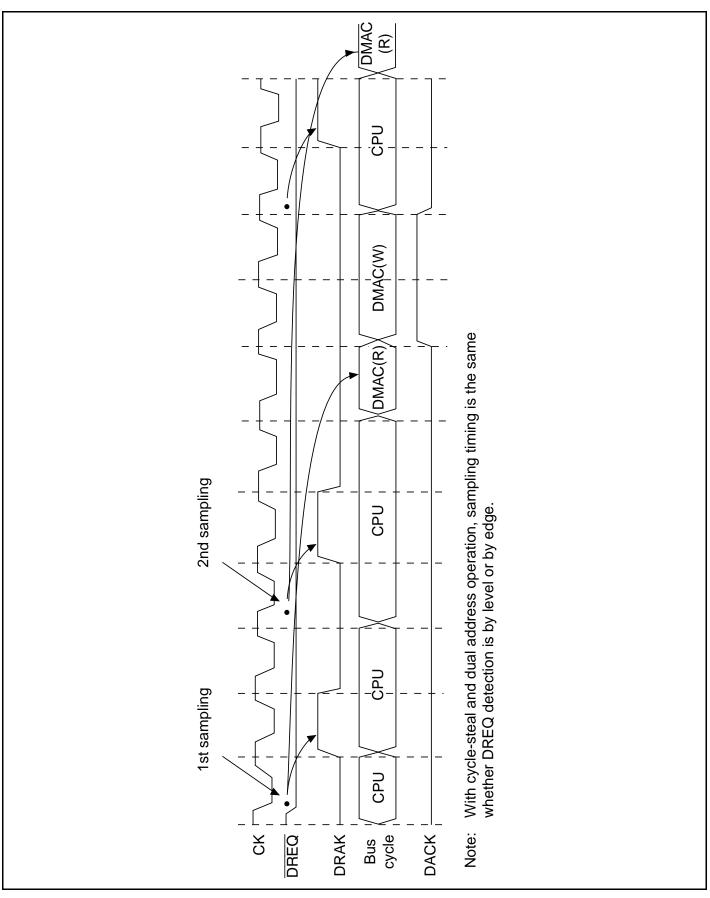

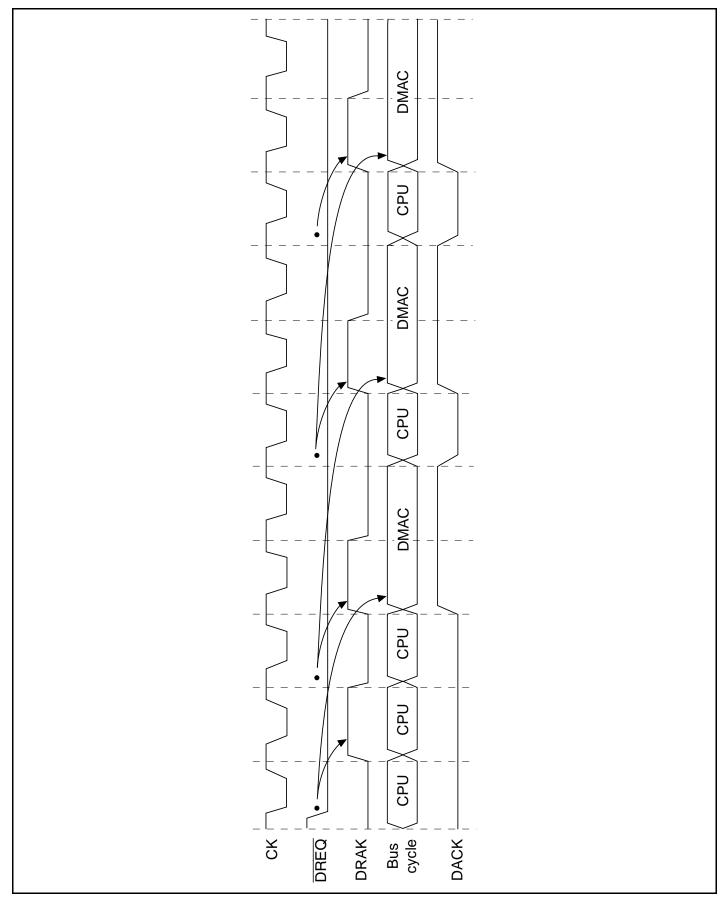

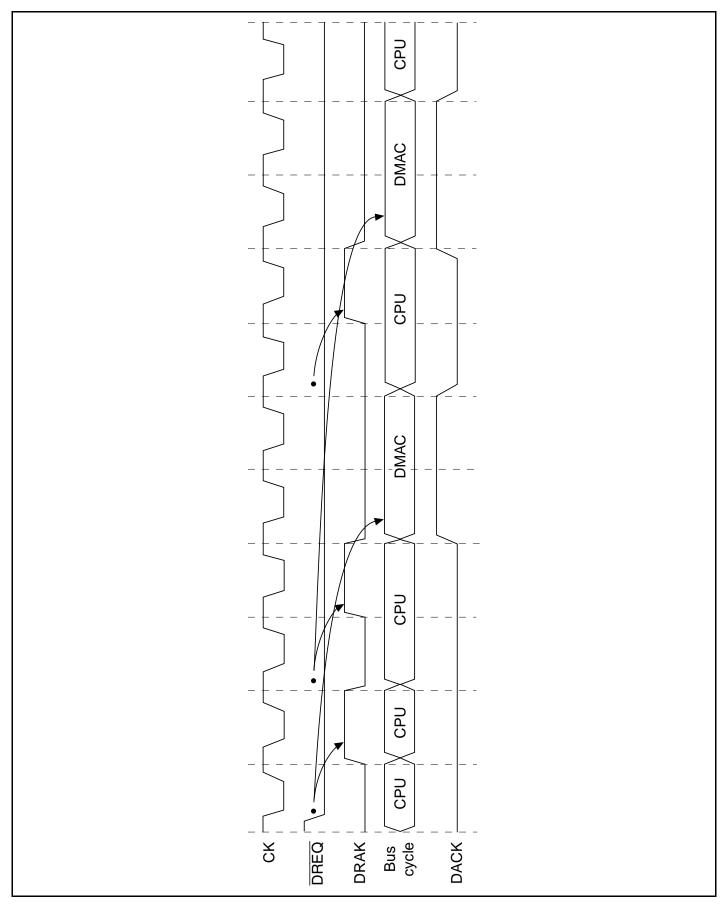

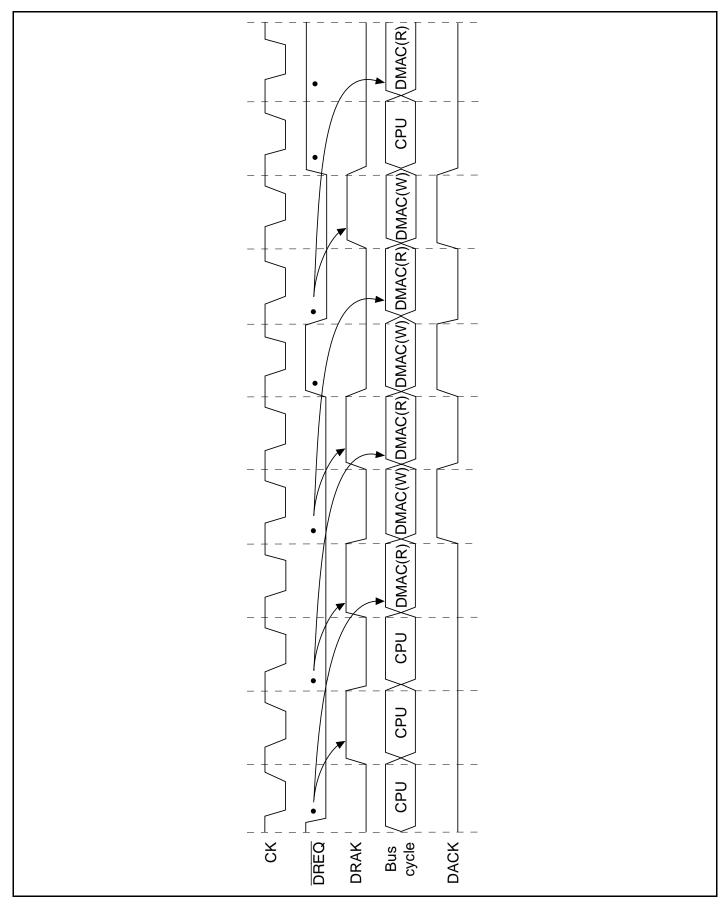

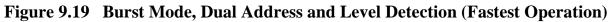

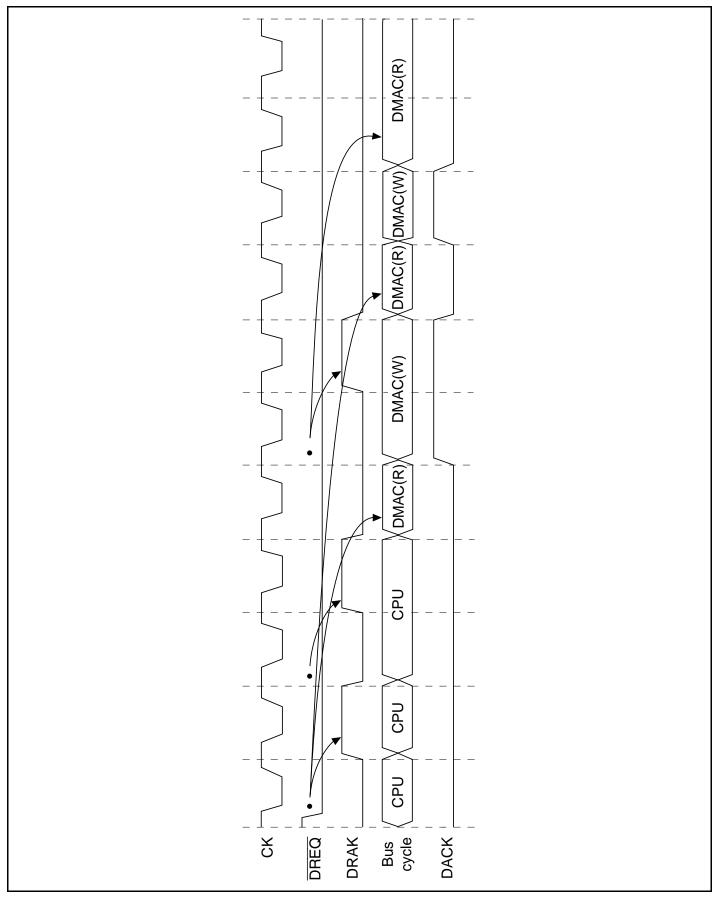

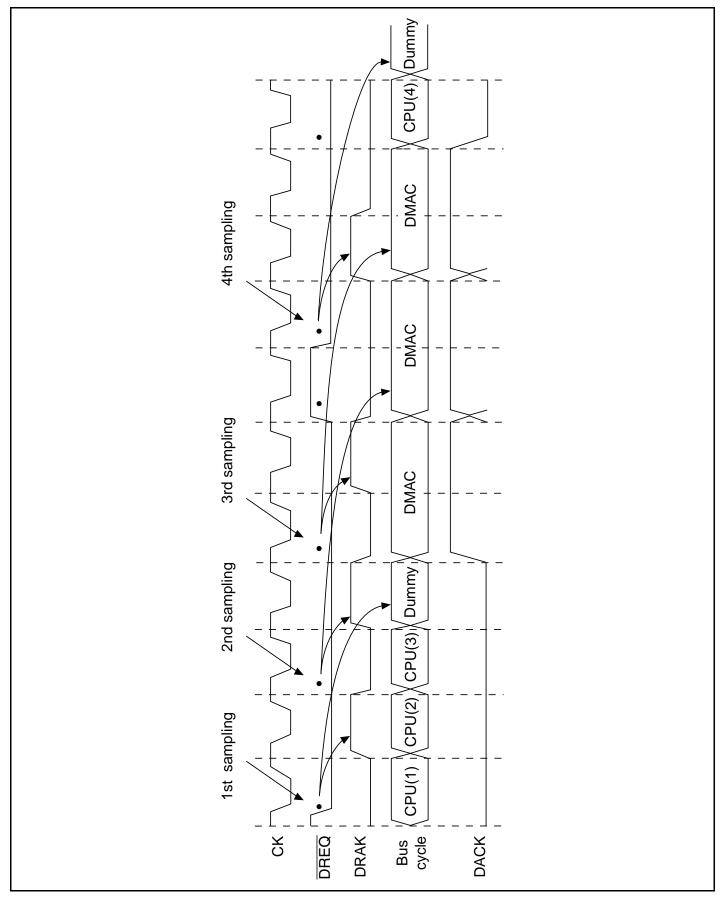

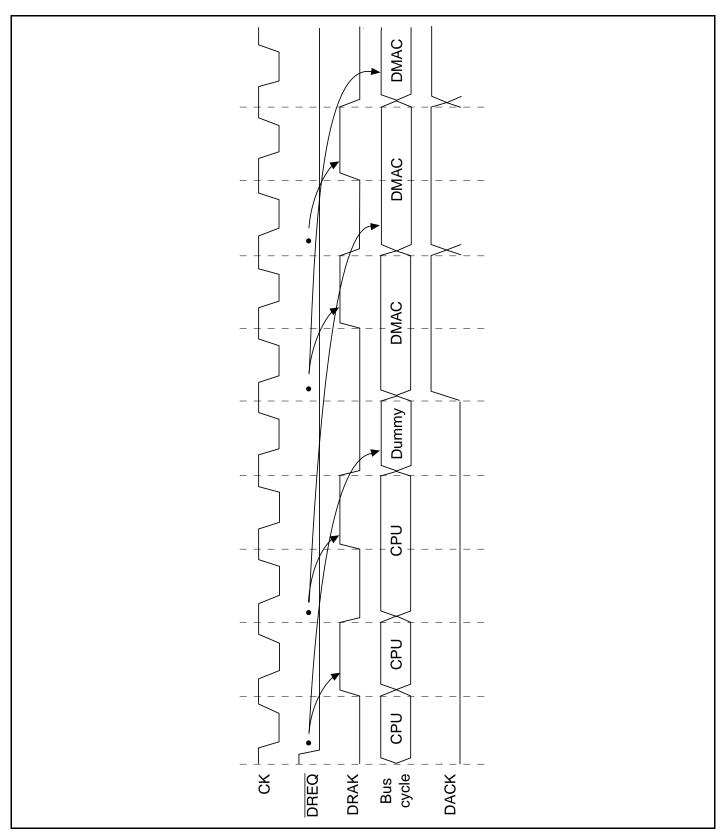

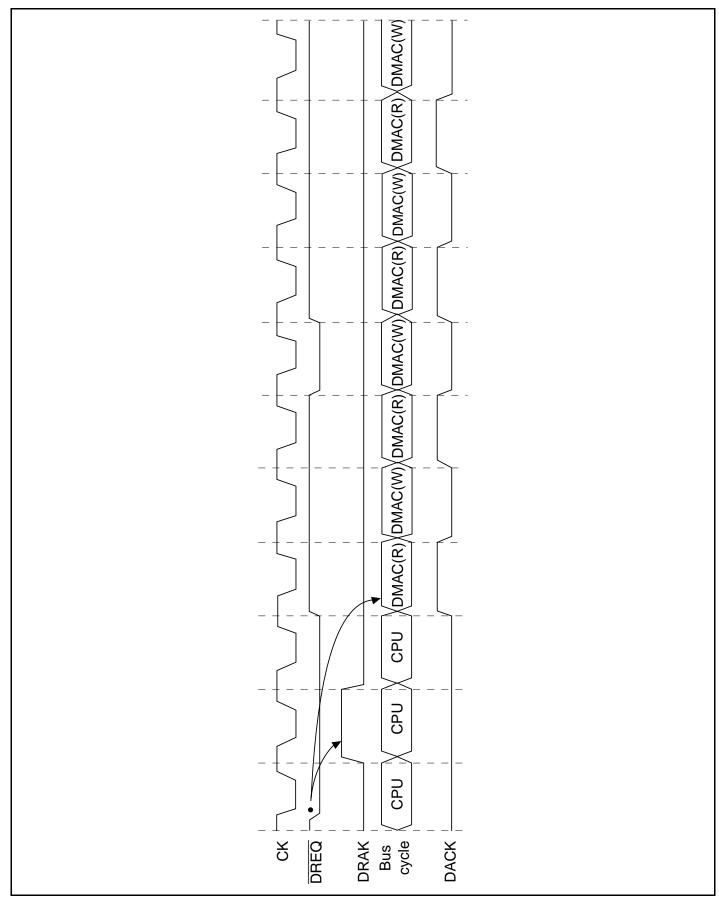

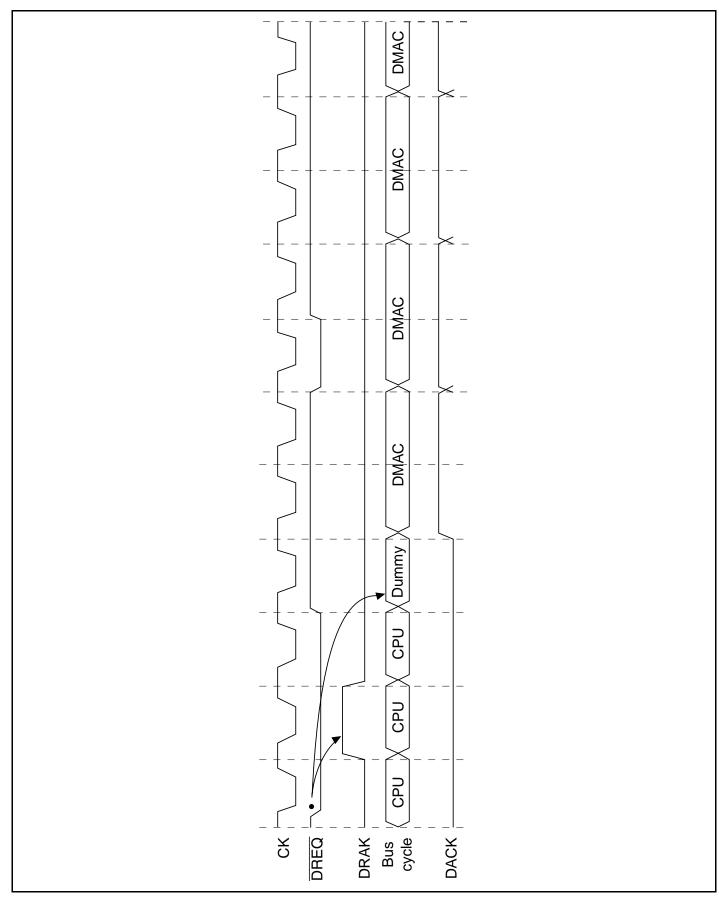

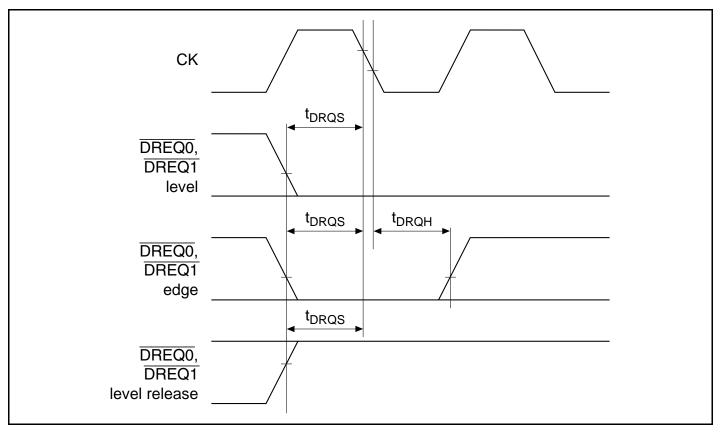

|       | 9.3.10  | Number of Bus Cycle States and DREQ Pin Sample Timing              | 169 |

|-------|---------|--------------------------------------------------------------------|-----|

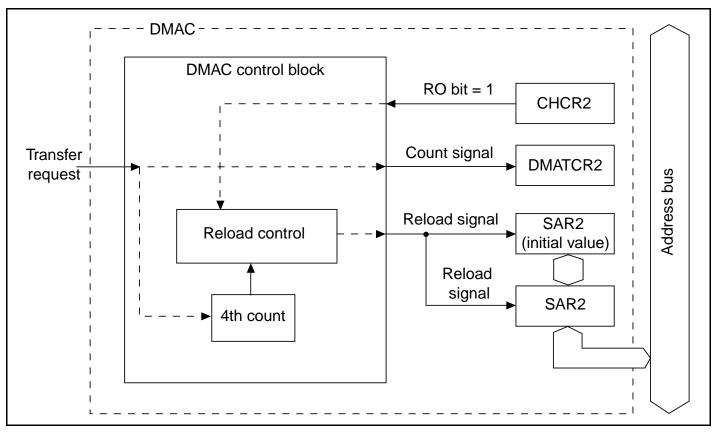

|       | 9.3.11  | Source Address Reload Function                                     | 186 |

|       | 9.3.12  | DMA Transfer Ending Conditions                                     | 188 |

|       |         | DMAC Access from CPU                                               |     |

| 9.4   | Exampl  | les of Use                                                         | 189 |

|       | 9.4.1   | Example of DMA Transfer between On-Chip SCI and External Memory    | 189 |

|       | 9.4.2   | Example of DMA Transfer between External RAM and External Device   |     |

|       |         | with DACK                                                          | 190 |

|       | 9.4.3   | Example of DMA Transfer between A/D Converter and Internal Memory  |     |

|       |         | (Address Reload On)                                                | 190 |

|       | 9.4.4   | Example of DMA Transfer between External Memory and SCI1 Send Side |     |

|       |         | (Indirect Address On)                                              | 192 |

| 9.5   | Cautior | ns on Use                                                          | 194 |

|       |         |                                                                    |     |

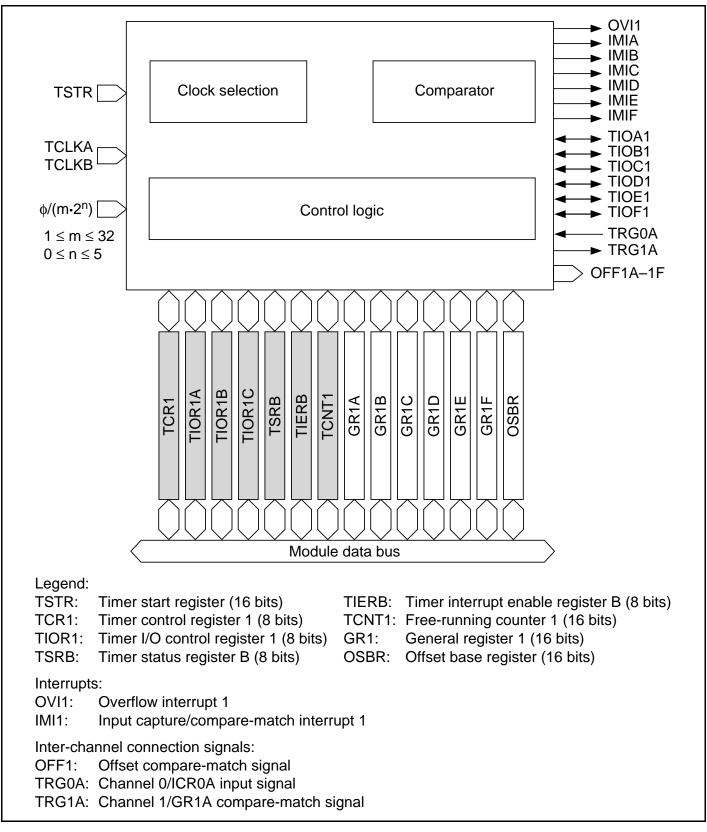

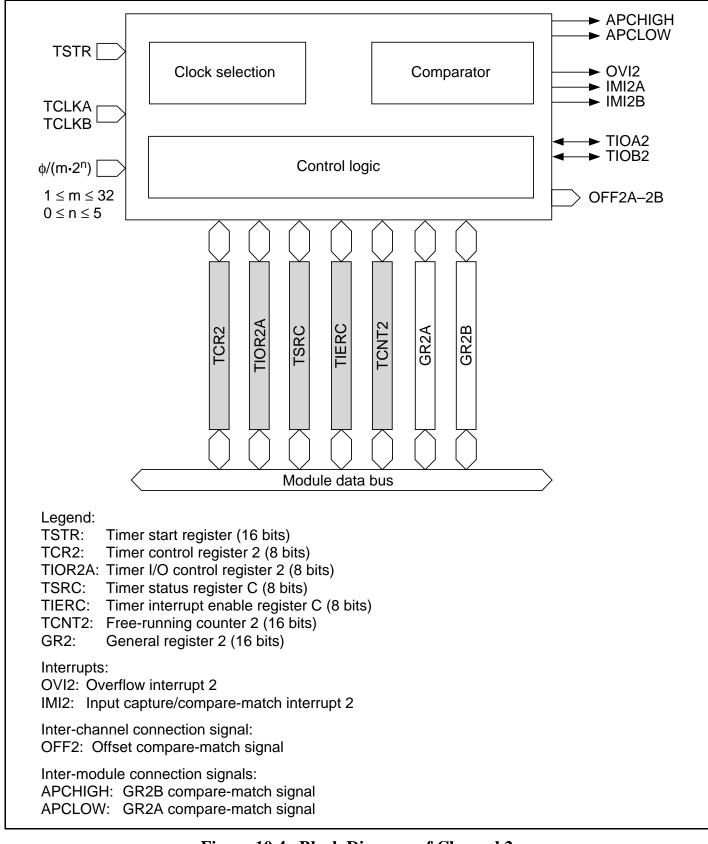

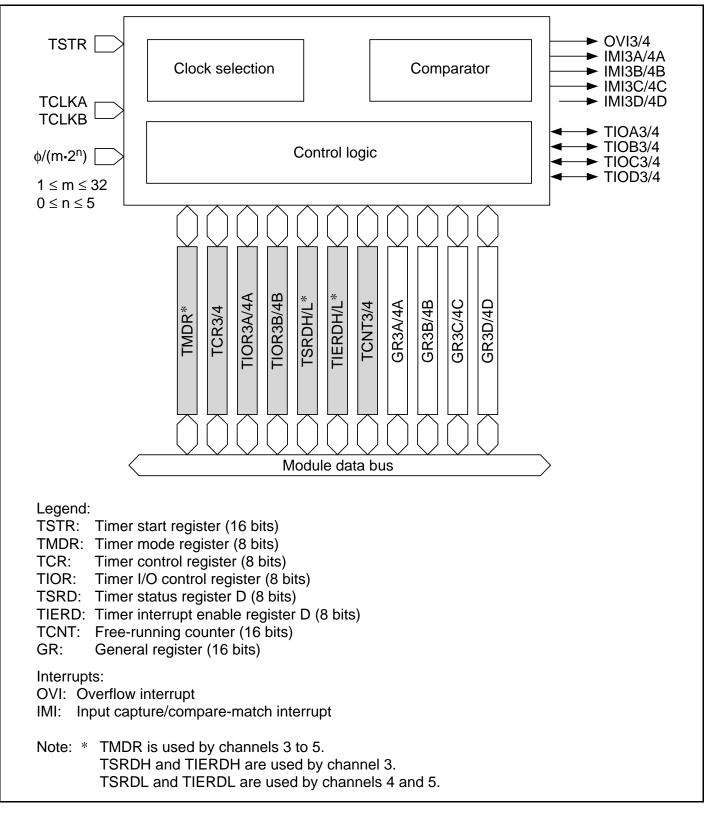

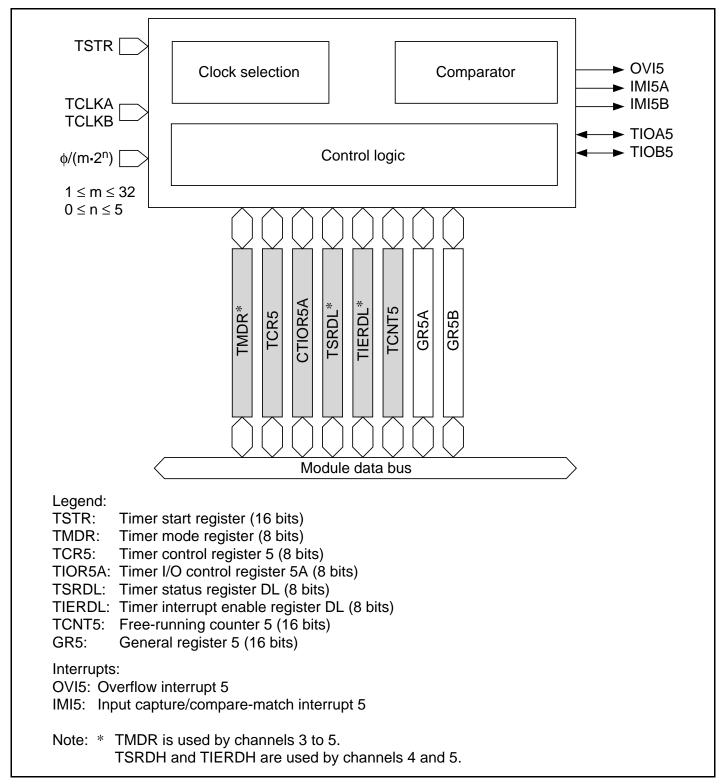

| Secti | on 10   | Advanced Timer Unit (ATU)                                          | 195 |

| 10.1  | Overvie | ew                                                                 | 195 |

|       | 10.1.1  | Features                                                           | 195 |

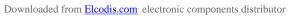

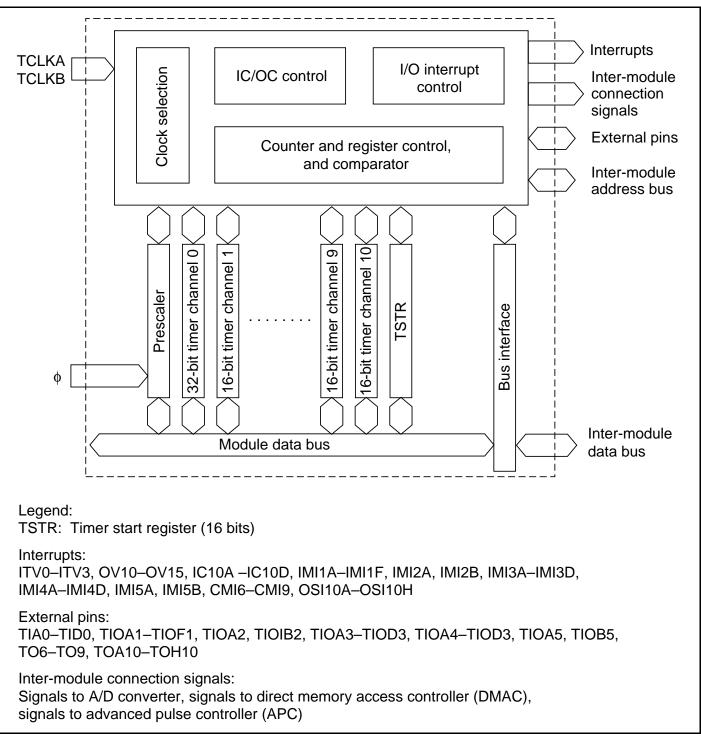

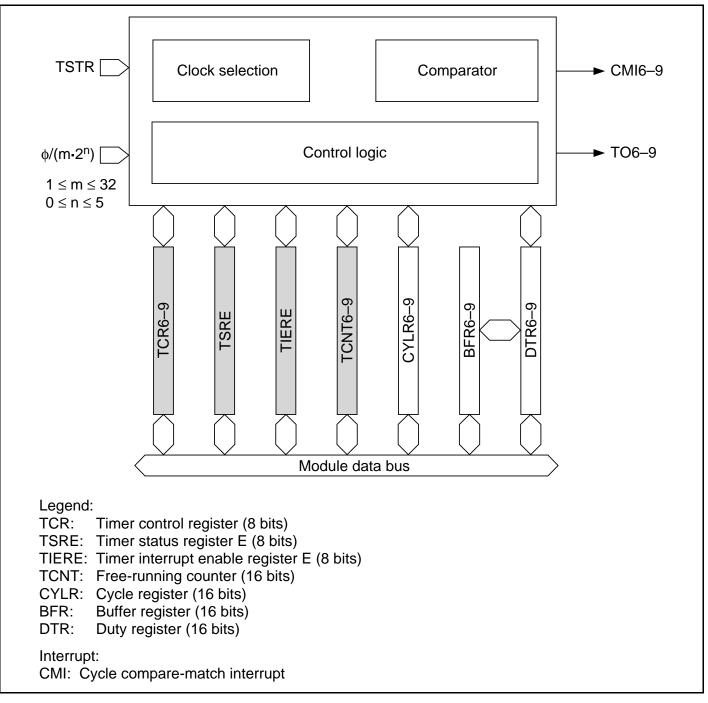

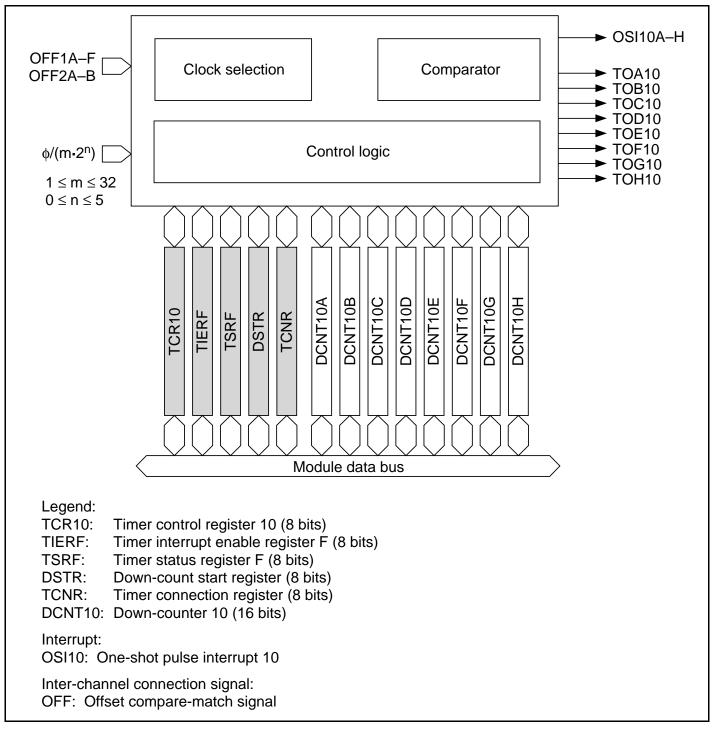

|       | 10.1.2  | Block Diagrams                                                     | 200 |

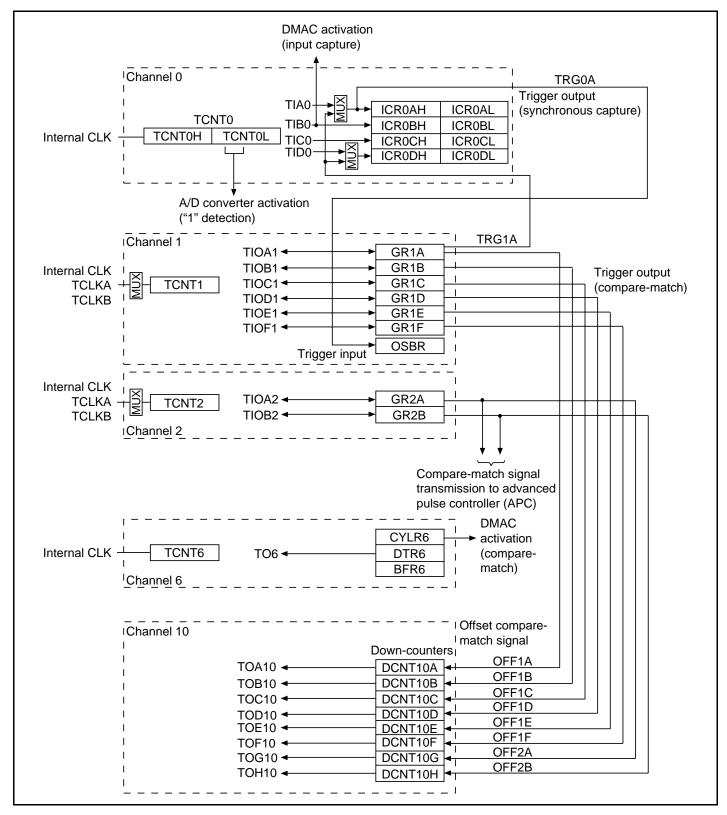

|       | 10.1.3  | Inter-Channel and Inter-Module Signal Connection Diagram           | 208 |

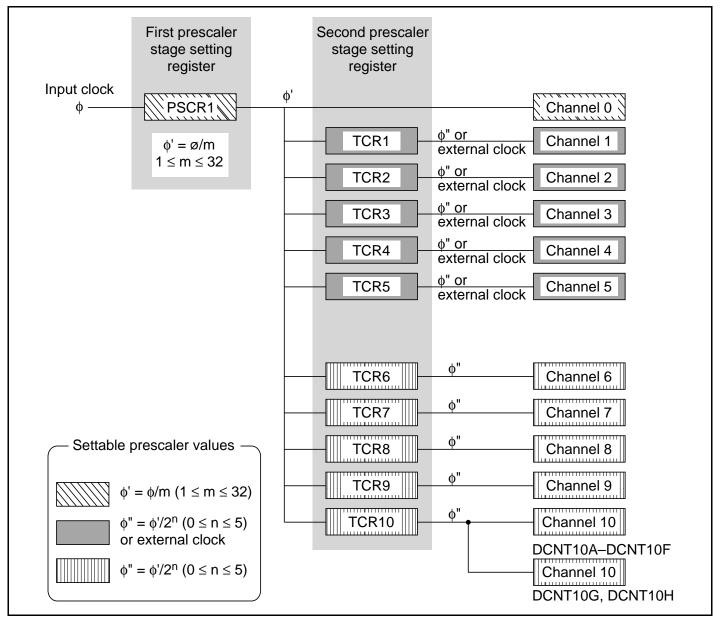

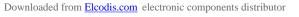

|       | 10.1.4  | Prescaler Diagram                                                  | 209 |

|       | 10.1.5  | Pin Configuration                                                  | 210 |

|       | 10.1.6  | Register and Counter Configuration                                 | 212 |

| 10.2  | Registe | r Descriptions                                                     | 216 |

|       | 10.2.1  | Timer Start Register (TSTR)                                        | 216 |

|       | 10.2.2  | Timer Mode Register (TMDR)                                         | 218 |

|       | 10.2.3  | Prescaler Register 1 (PSCR1)                                       | 220 |

|       | 10.2.4  | Timer Control Registers (TCR)                                      | 221 |

|       | 10.2.5  | Timer I/O Control Registers (TIOR)                                 | 225 |

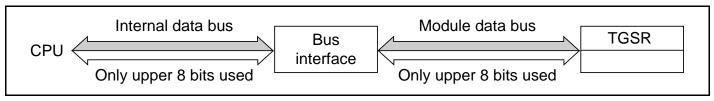

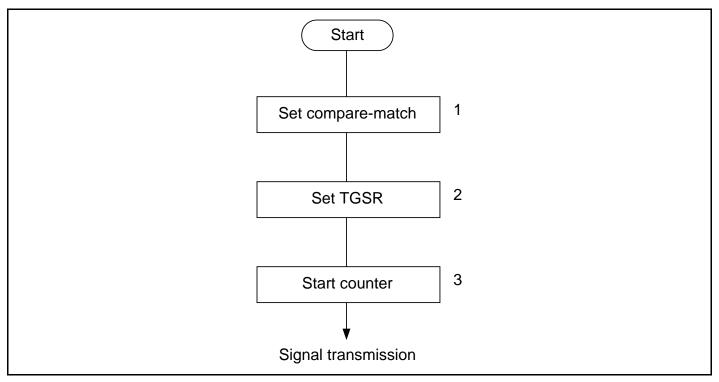

|       | 10.2.6  | Trigger Selection Register (TGSR)                                  | 233 |

|       | 10.2.7  | Timer Status Registers (TSR)                                       | 235 |

|       | 10.2.8  | Timer Interrupt Enable Registers (TIER)                            | 252 |

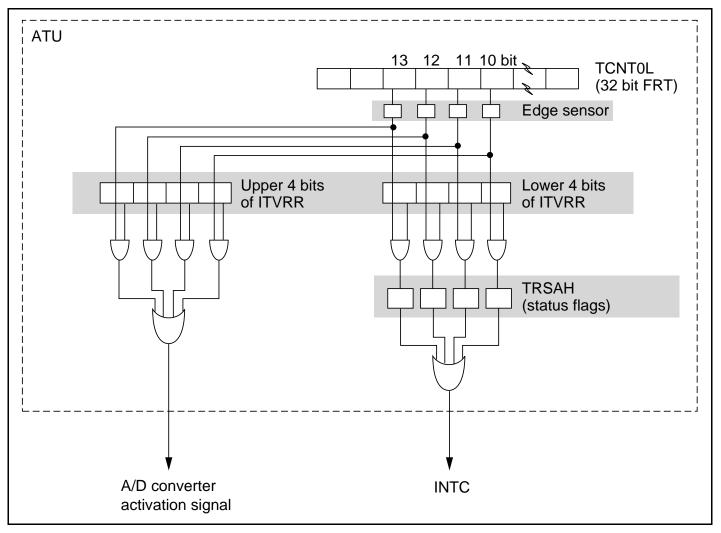

|       | 10.2.9  | Interval Interrupt Request Register (ITVRR)                        | 264 |

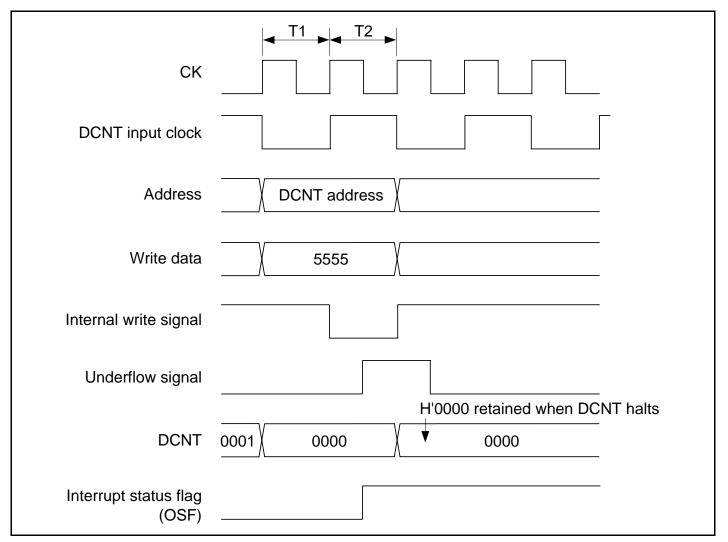

|       | 10.2.10 | Down-Count Start Register (DSTR)                                   | 267 |

|       | 10.2.11 | Timer Connection Register (TCNR)                                   | 271 |

|       | 10.2.12 | Free-Running Counters (TCNT)                                       | 274 |

|       | 10.2.13 | Input Capture Registers (ICR)                                      | 276 |

|       | 10.2.14 | General Registers (GR)                                             | 277 |

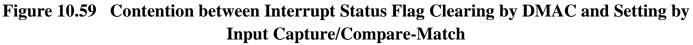

|       | 10.2.15 | Down-Counters (DCNT)                                               | 278 |

|       | 10.2.16 | Offset Base Register (OSBR)                                        | 279 |

|       | 10.2.17 | Cycle Registers (CYLR)                                             | 280 |

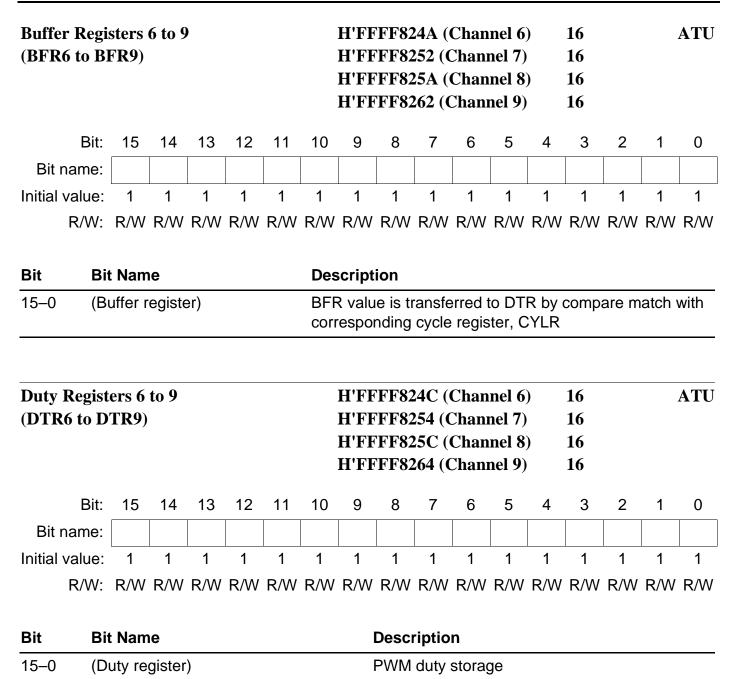

|       | 10.2.18 | Buffer Registers (BFR)                                             | 281 |

|       | 10.2.19 | Duty Registers (DTR)                                                  | 282 |

|-------|---------|-----------------------------------------------------------------------|-----|

| 10.3  | Operati | on                                                                    | 283 |

|       | 10.3.1  | Overview                                                              | 283 |

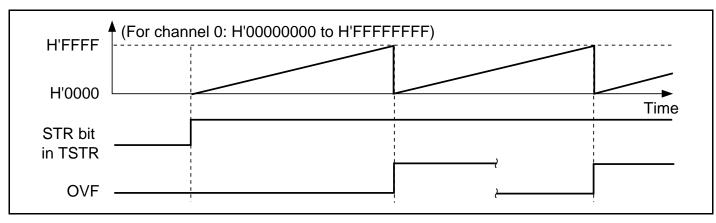

|       | 10.3.2  | Free-Running Count Operation and Cyclic Count Operation               | 285 |

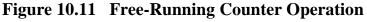

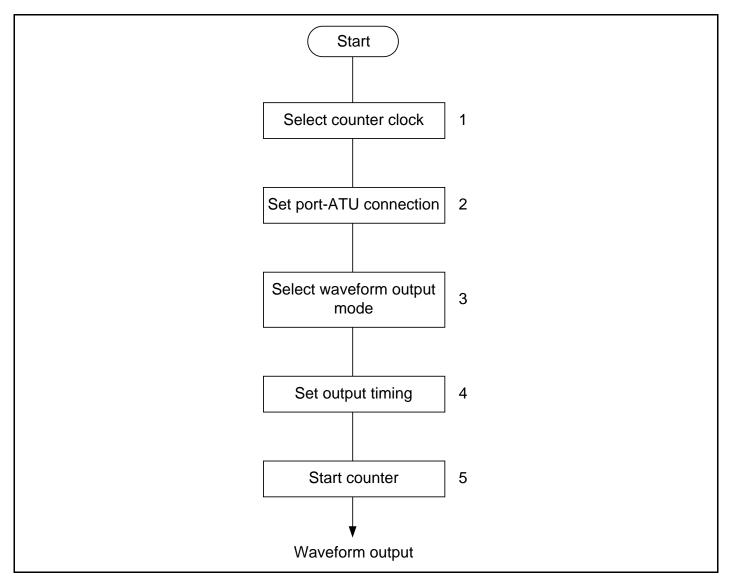

|       | 10.3.3  | Output Compare-Match Function                                         | 286 |

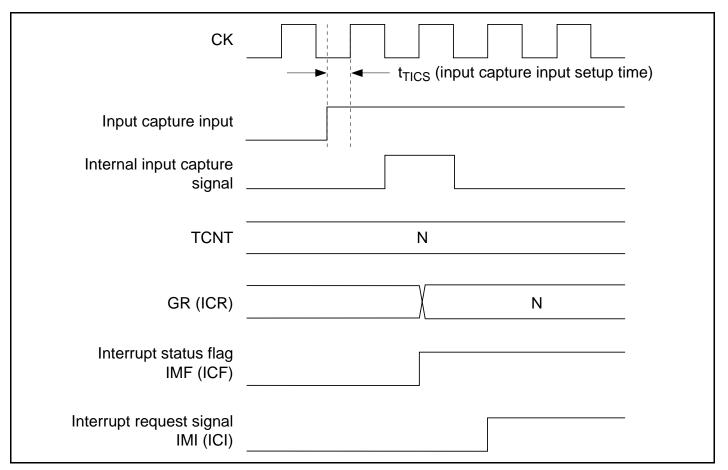

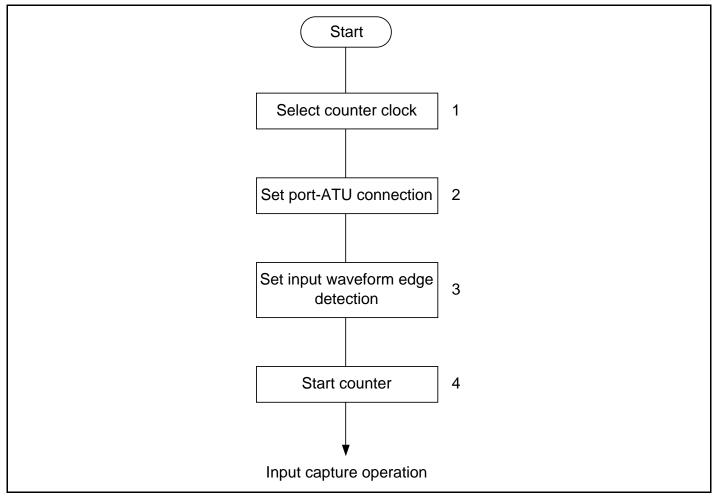

|       | 10.3.4  | Input Capture Function                                                | 288 |

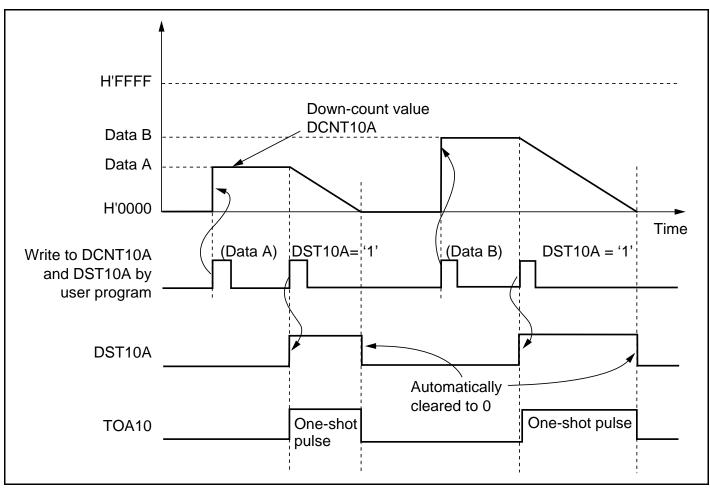

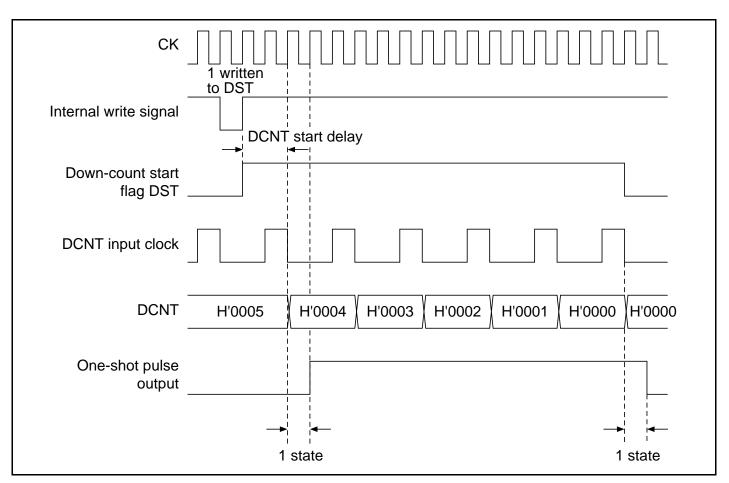

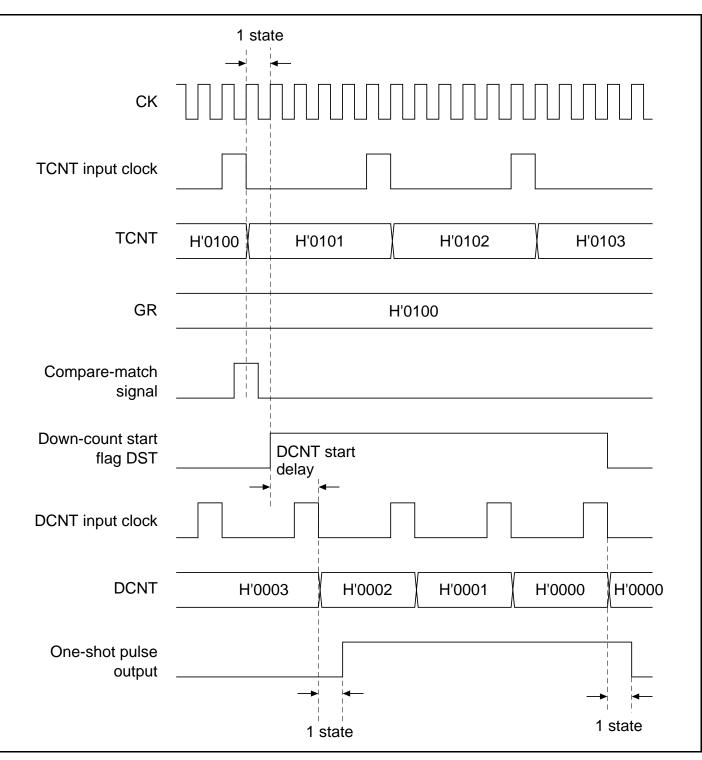

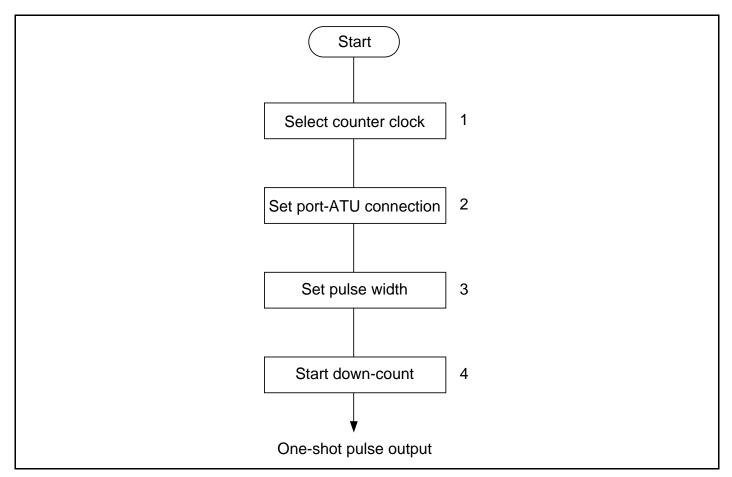

|       | 10.3.5  | One-Shot Pulse Function                                               | 289 |

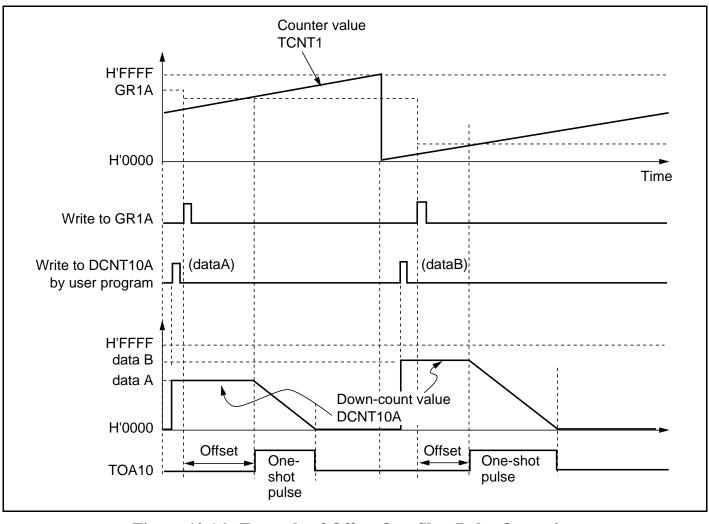

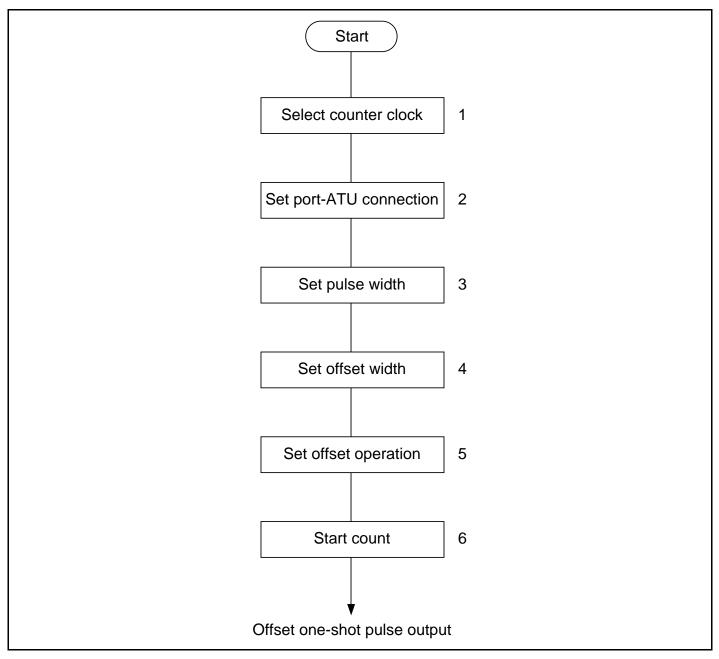

|       | 10.3.6  | Offset One-Shot Pulse Function                                        | 290 |

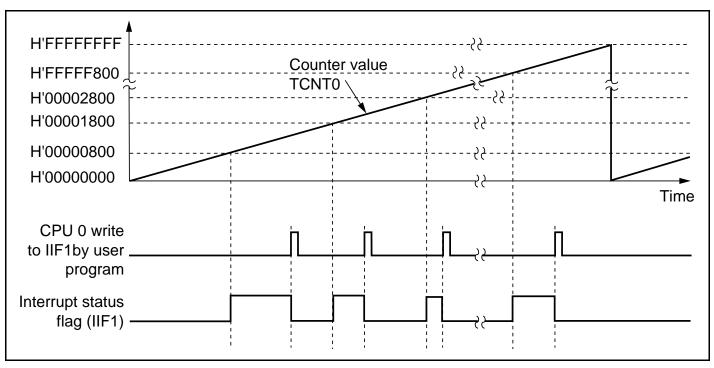

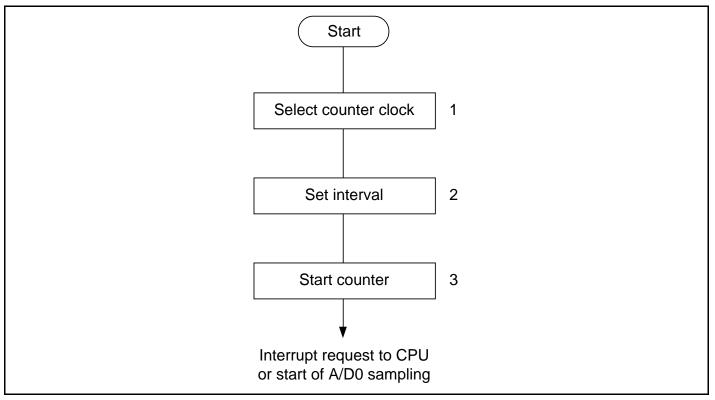

|       | 10.3.7  | Interval Timer Operation                                              | 292 |

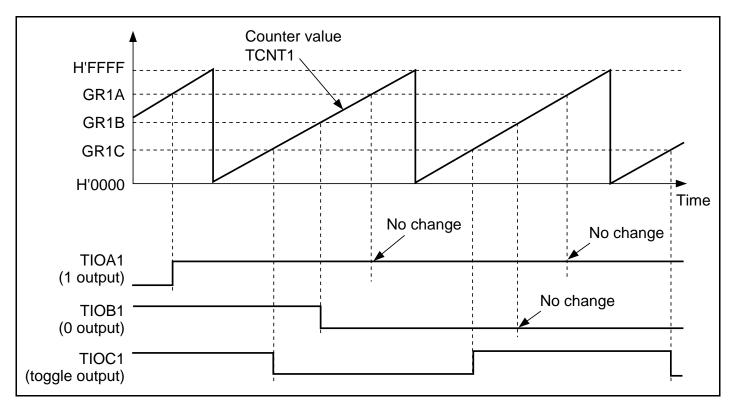

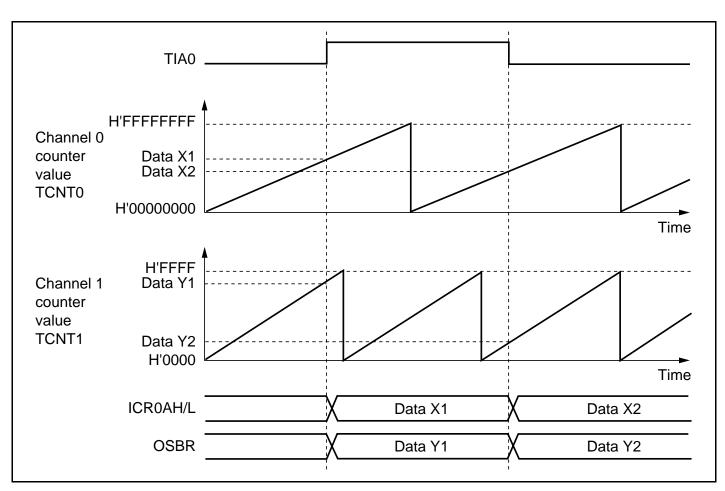

|       | 10.3.8  | Twin-Capture Function                                                 | 294 |

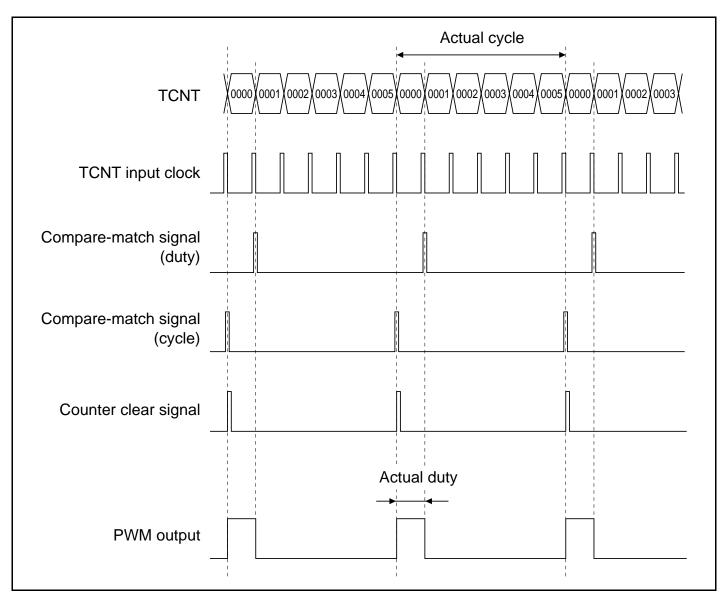

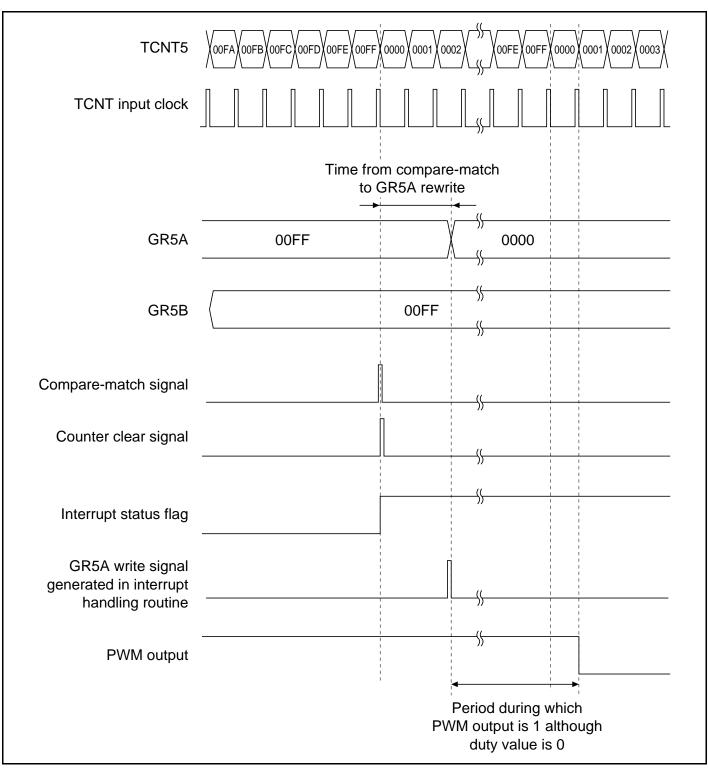

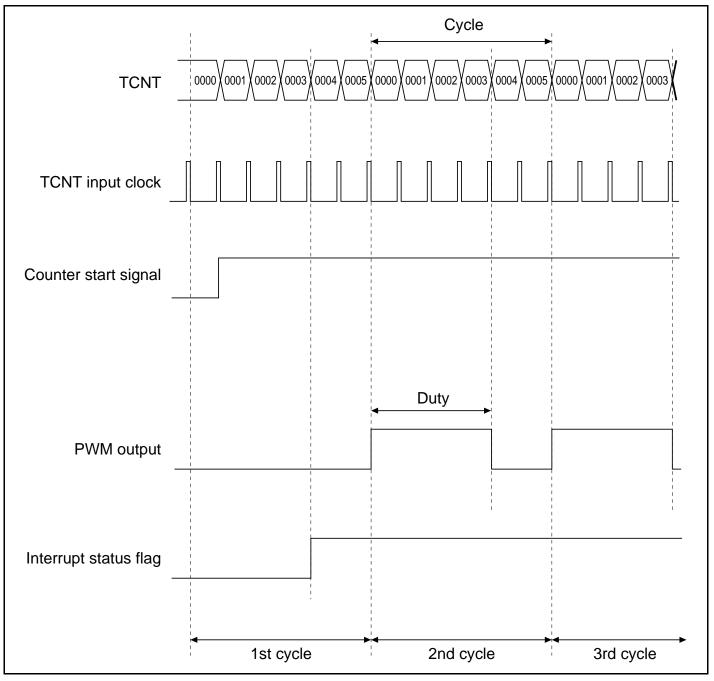

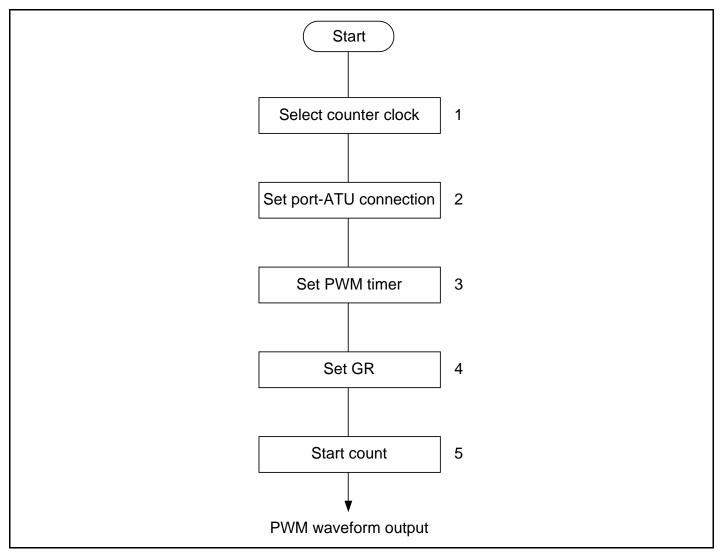

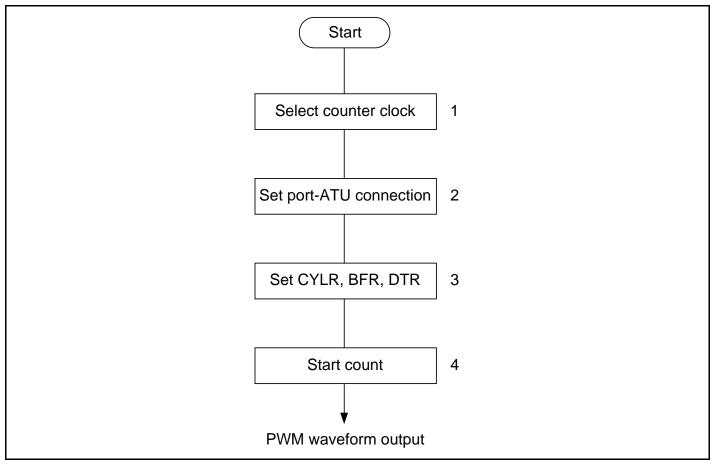

|       | 10.3.9  | PWM Timer Function                                                    | 295 |

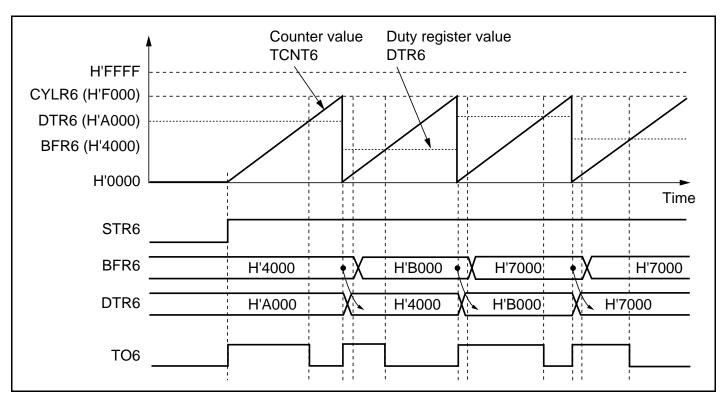

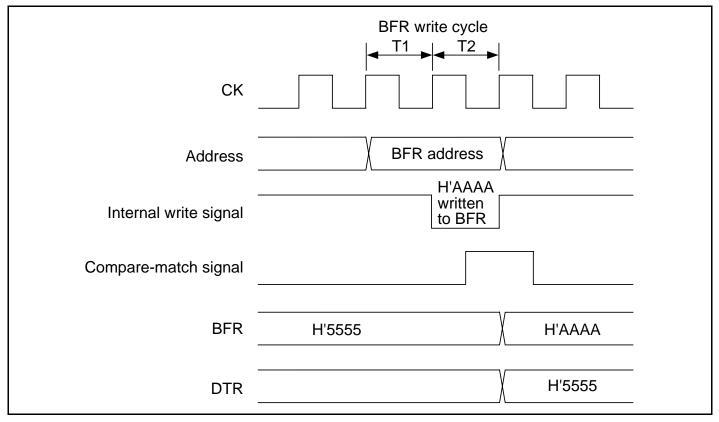

|       | 10.3.10 | Buffer Function                                                       | 297 |

|       | 10.3.11 | One-Shot Pulse Function Pulse Output Timing                           | 298 |

|       |         | 2 Offset One-Shot Pulse Function Pulse Output Timing                  |     |

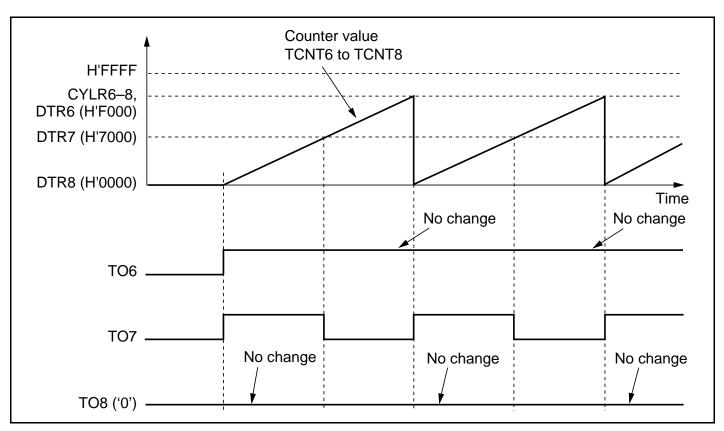

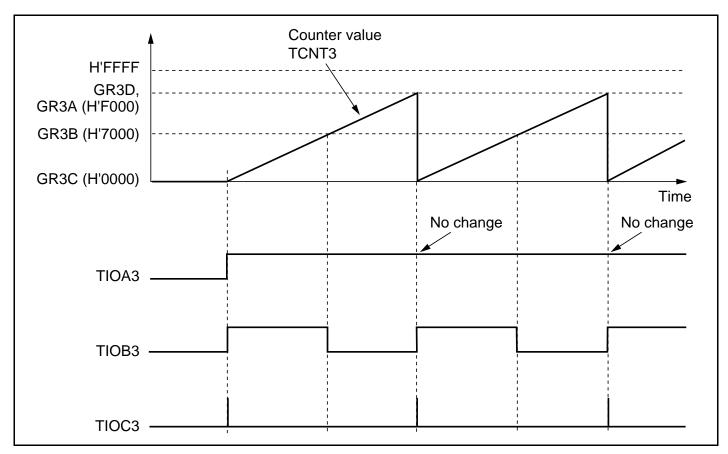

|       | 10.3.13 | Channel 3 to 5 PWM Output Waveform Actual Cycle and Actual Duty       | 300 |

|       | 10.3.14 | Channel 3 to 5 PWM Output Waveform Settings and Interrupt Handling    |     |

|       |         | Times                                                                 | 301 |

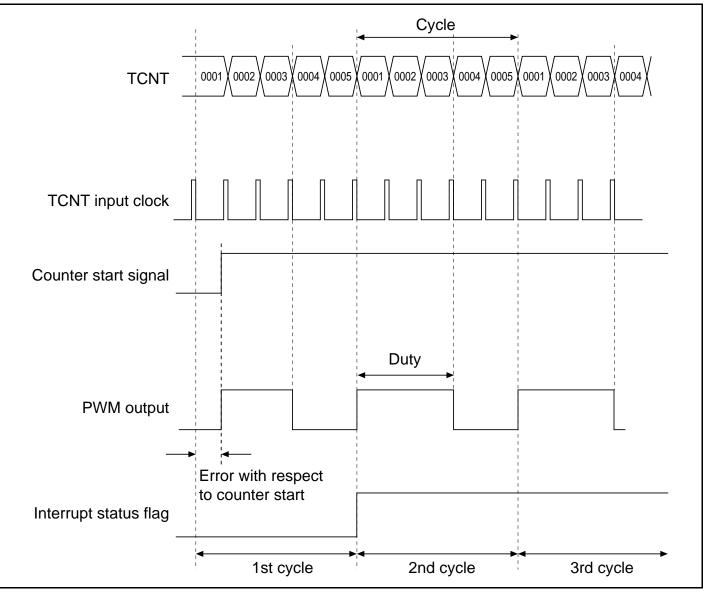

|       | 10.3.15 | PWM Output Operation at Start of Channel 3 to 5 Counter               | 303 |

|       |         | 5 PWM Output Operation at Start of Channel 6 to 9 Counter             |     |

|       |         | Timing of Buffer Register (BFR) Write and Transfer by Buffer Function |     |

| 10.4  | Interru | ots                                                                   | 306 |

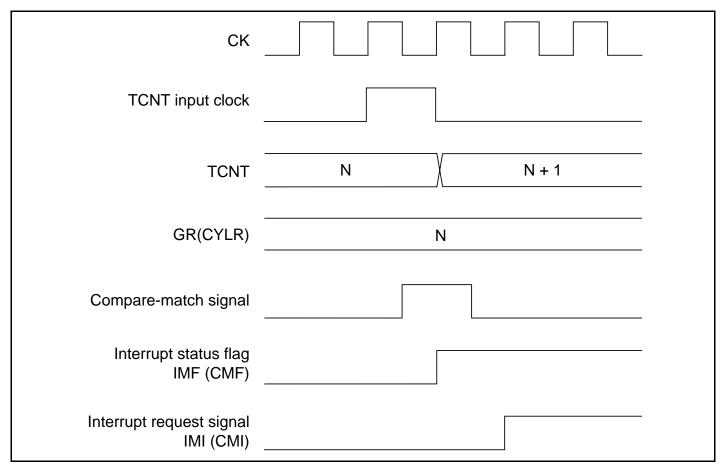

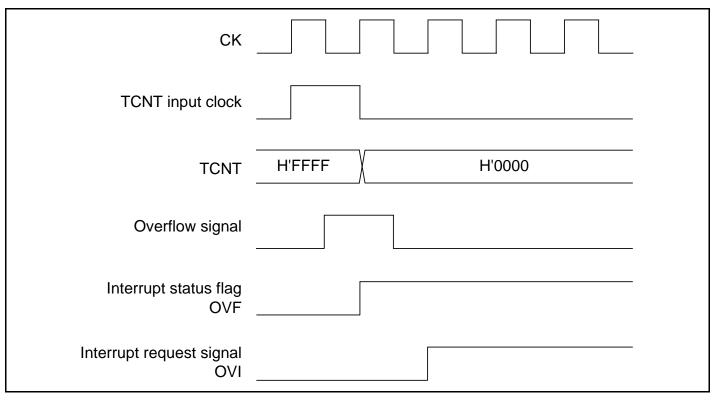

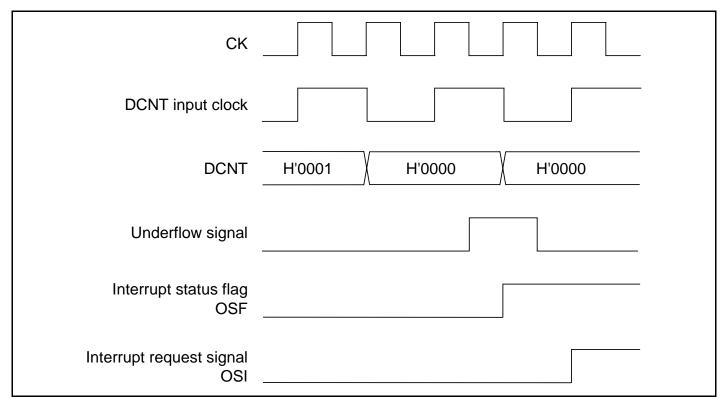

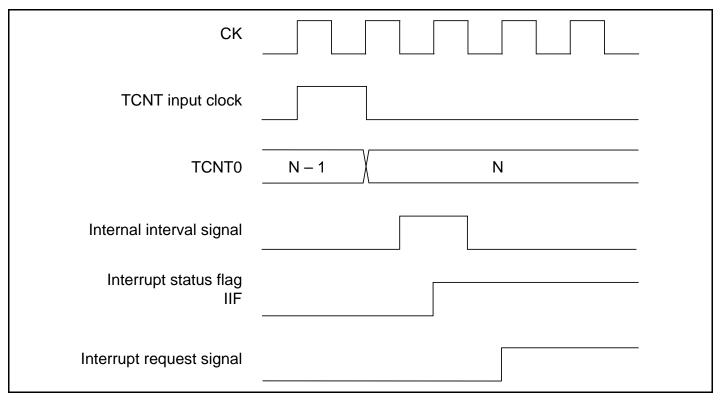

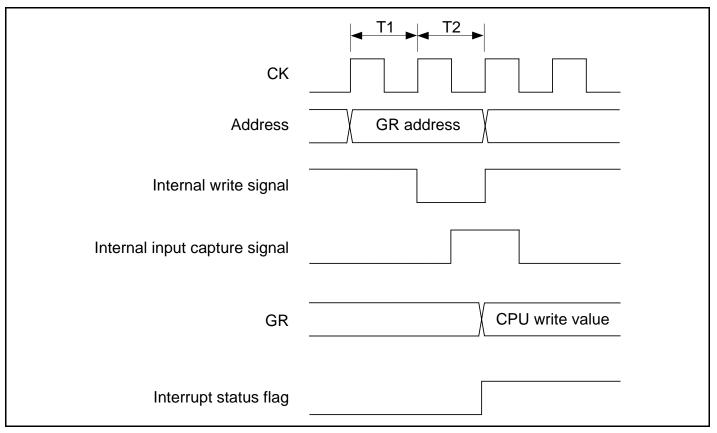

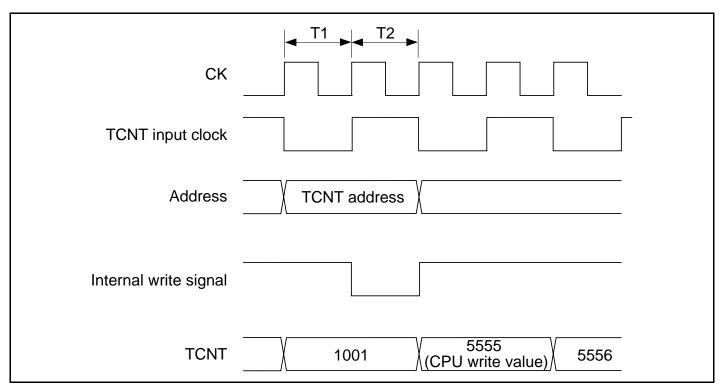

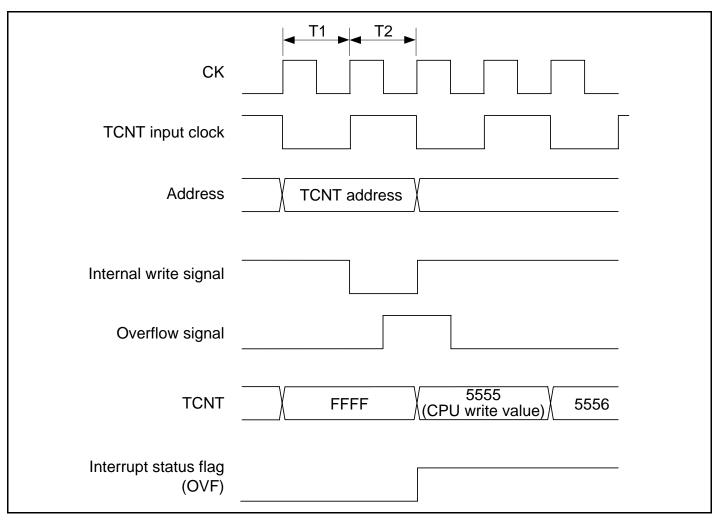

|       | 10.4.1  | Status Flag Setting Timing                                            | 306 |

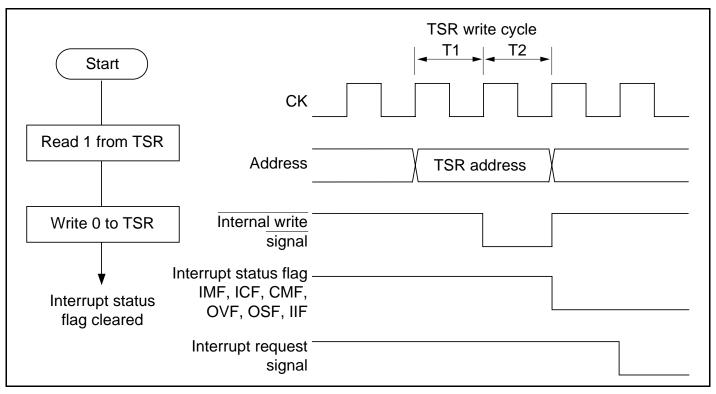

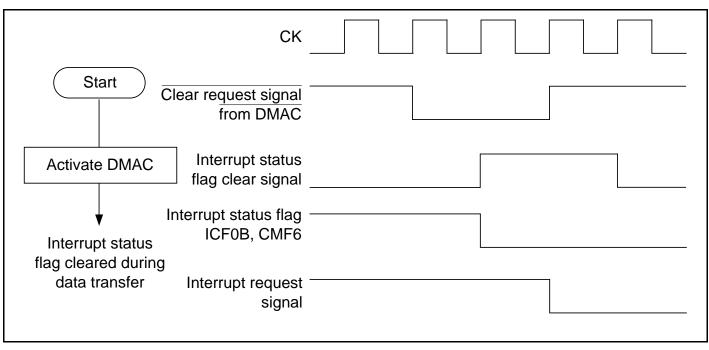

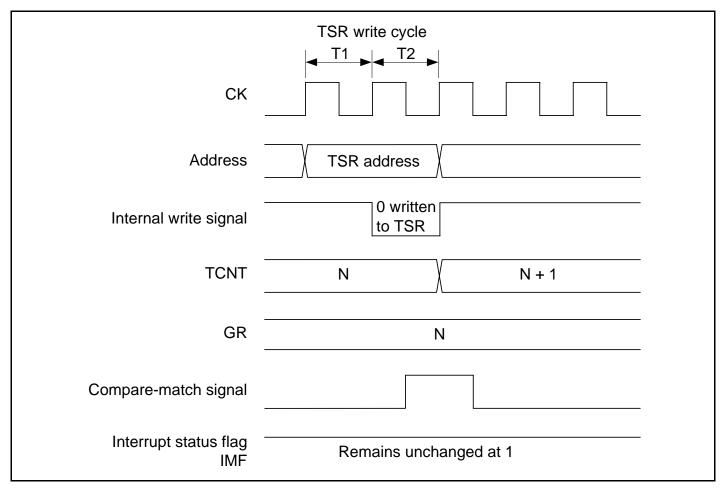

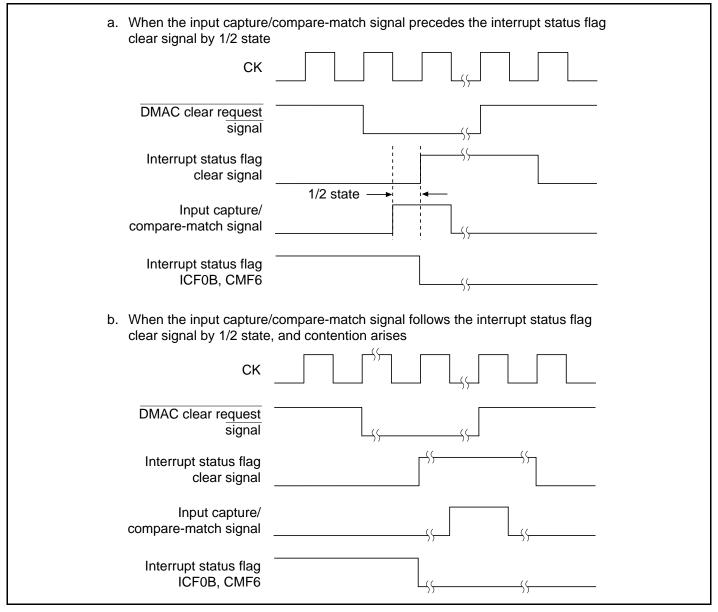

|       | 10.4.2  | Interrupt Status Flag Clearing                                        | 311 |

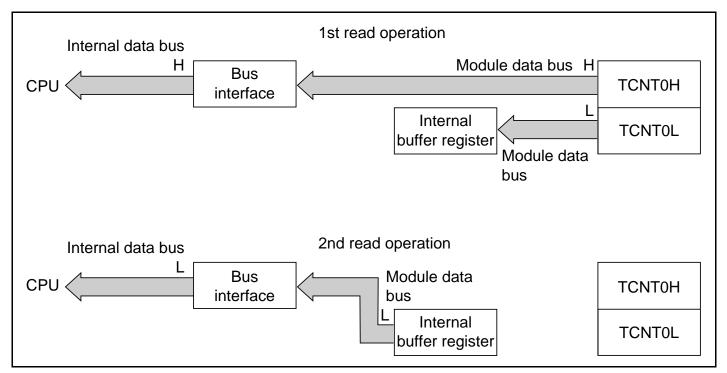

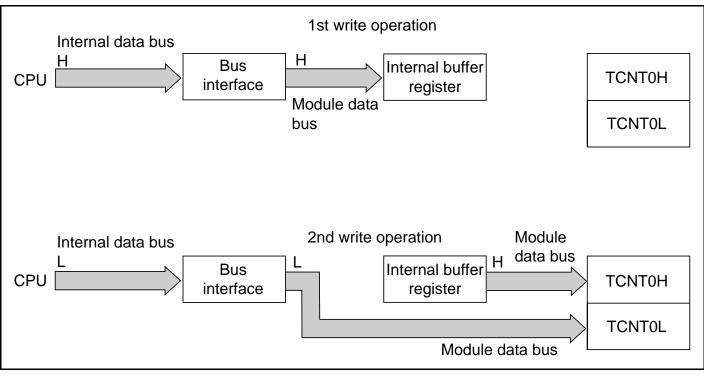

| 10.5  | CPU In  | terface                                                               | 313 |

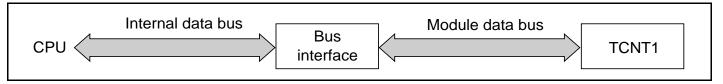

|       | 10.5.1  | Registers Requiring 32-Bit Access                                     | 313 |

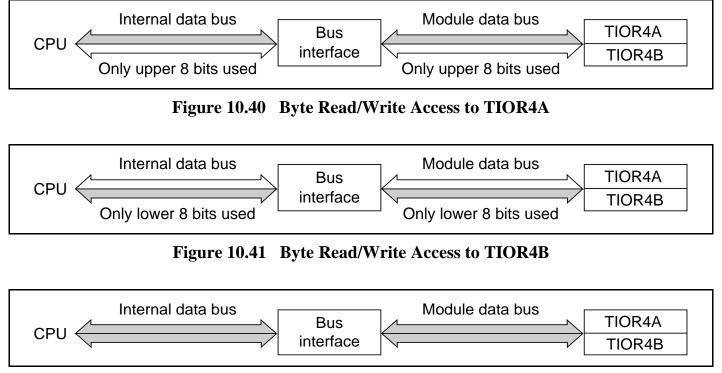

|       | 10.5.2  | Registers Requiring 16-Bit Access                                     | 314 |

|       |         | 8-Bit or 16-Bit Accessible Registers                                  |     |

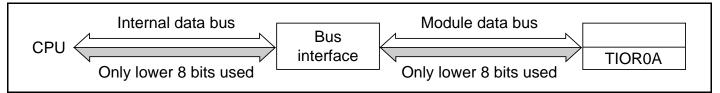

|       | 10.5.4  | Registers Requiring 8-Bit Access                                      | 316 |

| 10.6  |         | Setup Procedures                                                      |     |

| 10.7  | Usage 1 | Notes                                                                 | 329 |

| 10.8  | -       | ced Timer Unit Registers And Pins                                     |     |

|       |         |                                                                       |     |

| Secti | on 11   | Advanced Pulse Controller (APC)                                       | 345 |

| 11.1  |         | ew                                                                    |     |

|       | 11.1.1  | Features                                                              | 345 |

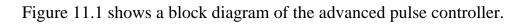

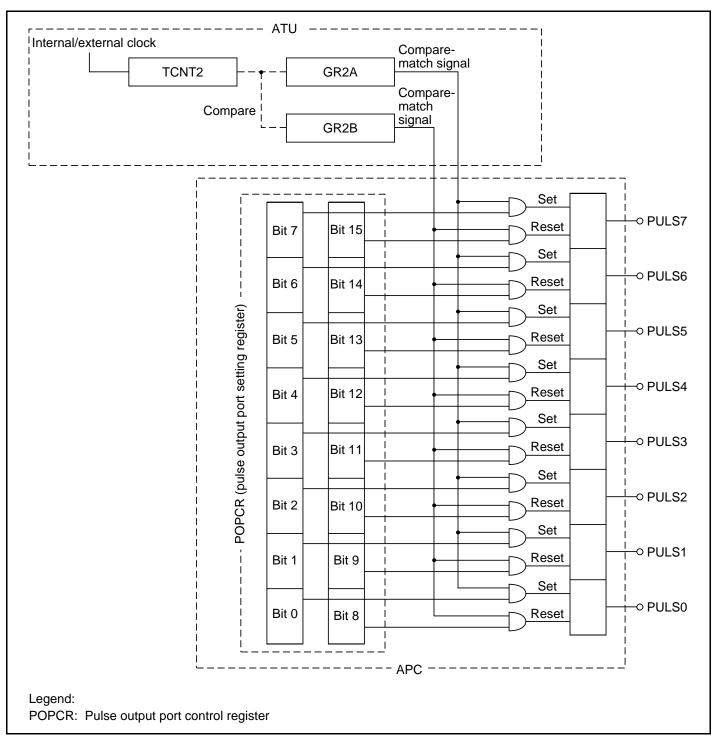

|       | 11.1.2  | Block Diagram                                                         | 346 |

|       | 11.1.3  | Pin Configuration                                                     | 347 |

|       |         | Register Configuration                                                |     |

| 11.2  |         | r Descriptions                                                        |     |

|       | -       | Pulse Output Port Control Register (POPCR)                            |     |

| 11.3  |         | on                                                                    |     |

|       | -       |                                                                       |     |

Rev. 5.00 Jan 06, 2006 page xii of xx

|       | 11.3.1  | Overview                                                  | 349 |

|-------|---------|-----------------------------------------------------------|-----|

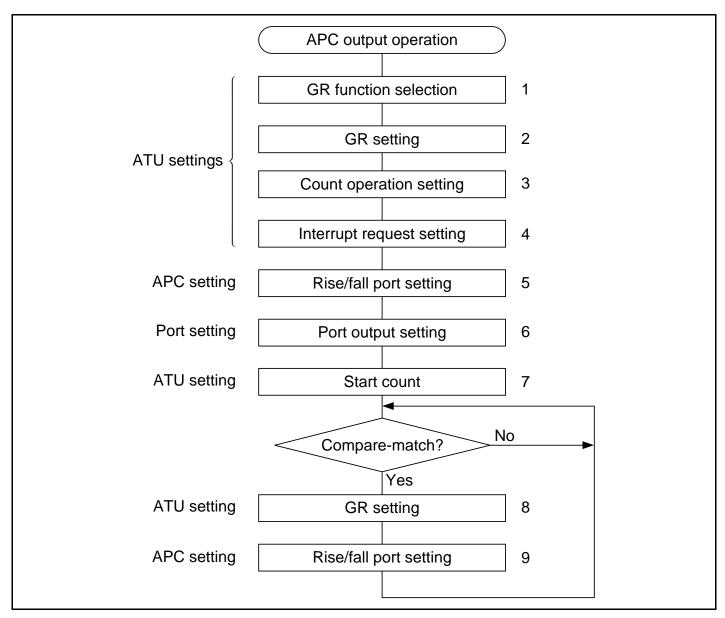

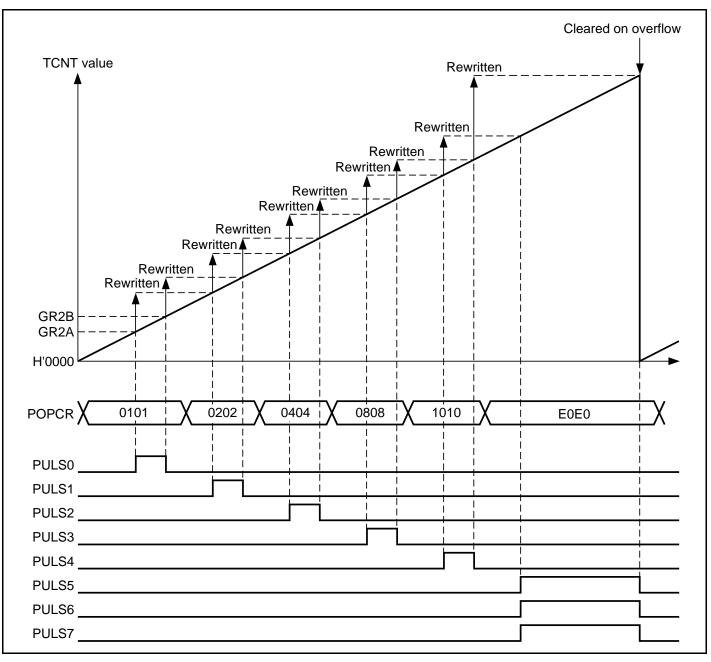

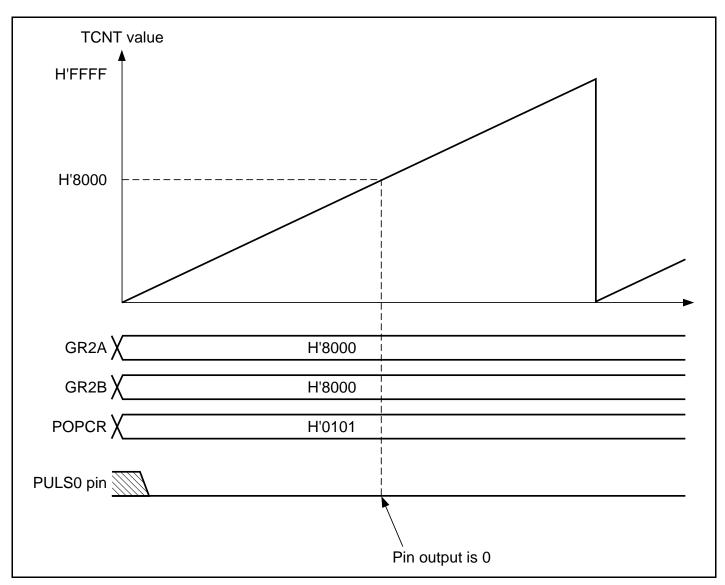

|       | 11.3.2  | Advanced Pulse Controller Output Operation                | 350 |

| 11.4  | Usage I | Notes                                                     | 353 |

|       |         |                                                           |     |

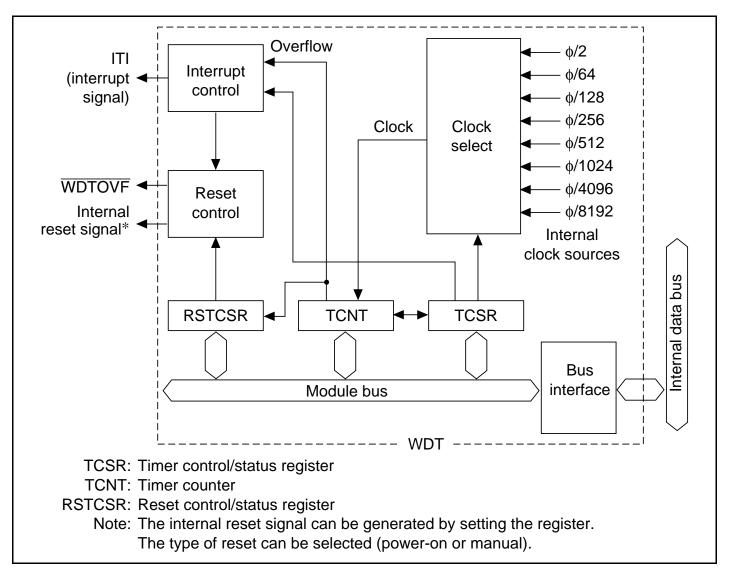

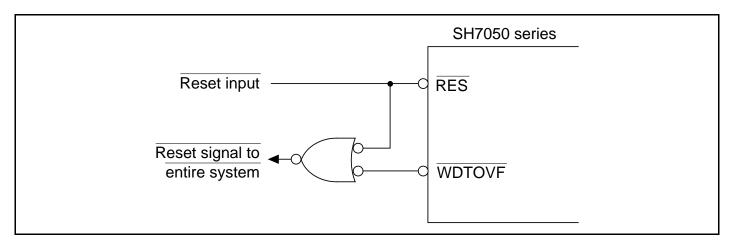

| Secti | on 12   | Watchdog Timer (WDT)                                      | 355 |

| 12.1  | Overvie | ew                                                        | 355 |

|       | 12.1.1  | Features                                                  | 355 |

|       | 12.1.2  | Block Diagram                                             | 356 |

|       | 12.1.3  | Pin Configuration                                         | 356 |

|       | 12.1.4  | Register Configuration                                    | 357 |

| 12.2  | Registe | r Descriptions                                            | 357 |

|       | 12.2.1  | Timer Counter (TCNT)                                      | 357 |

|       | 12.2.2  | Timer Control/Status Register (TCSR)                      | 358 |

|       | 12.2.3  | Reset Control/Status Register (RSTCSR)                    | 360 |

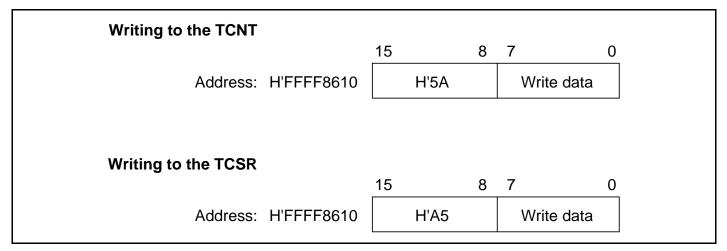

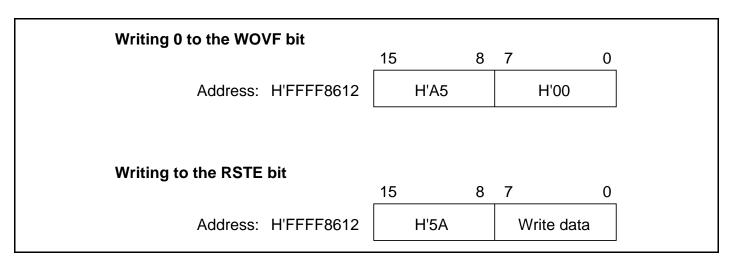

|       | 12.2.4  | Register Access                                           | 361 |

| 12.3  | Operati | on                                                        | 362 |

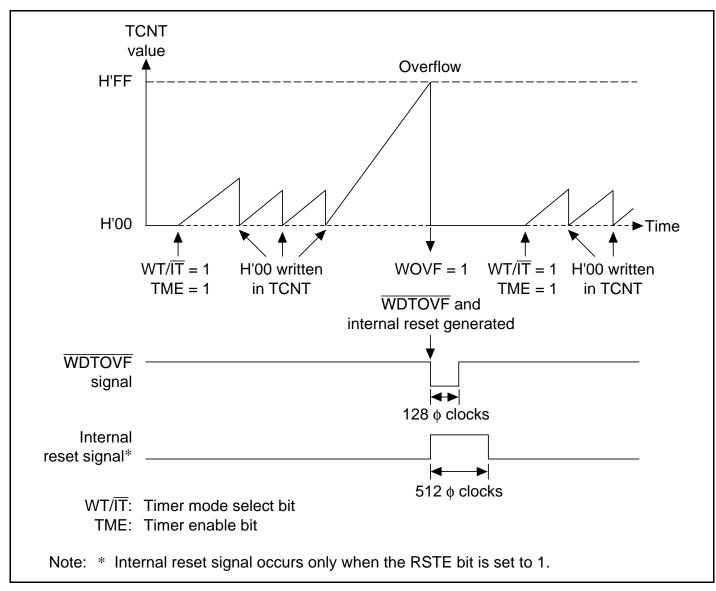

|       | 12.3.1  | Watchdog Timer Mode                                       | 362 |

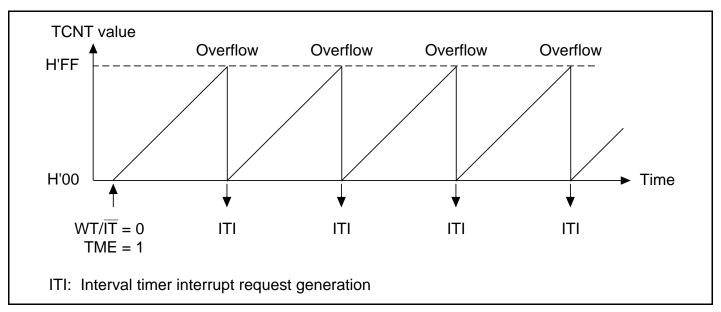

|       | 12.3.2  | Interval Timer Mode                                       | 364 |

|       | 12.3.3  | Clearing the Standby Mode                                 | 364 |

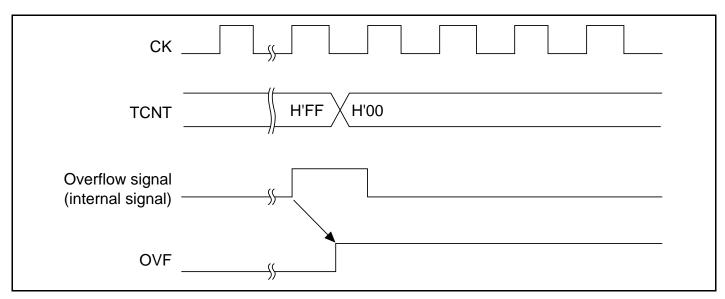

|       | 12.3.4  | Timing of Setting the Overflow Flag (OVF)                 | 365 |

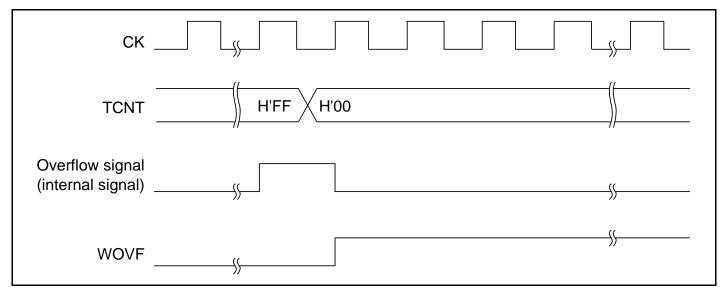

|       | 12.3.5  | Timing of Setting the Watchdog Timer Overflow Flag (WOVF) | 365 |

| 12.4  | Notes c | on Use                                                    | 366 |

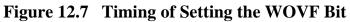

|       | 12.4.1  | TCNT Write and Increment Contention                       | 366 |

|       | 12.4.2  | Changing CKS2 to CKS0 Bit Values                          | 366 |

|       | 12.4.3  | Changing between Watchdog Timer/Interval Timer Modes      | 366 |

|       | 12.4.4  | System Reset With WDTOVF                                  | 367 |

|       | 12.4.5  | Internal Reset With the Watchdog Timer                    | 367 |

|       |         |                                                           |     |

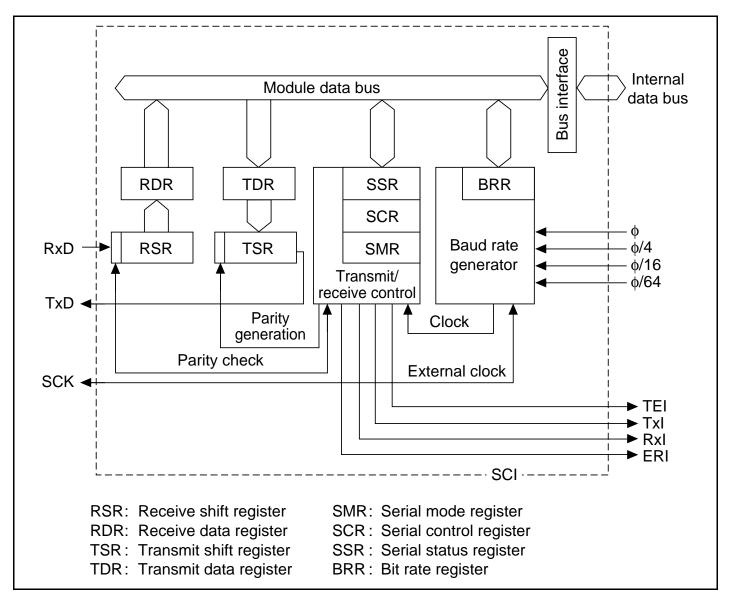

| Secti | on 13   | Serial Communication Interface (SCI)                      | 369 |

| 13.1  |         | ew                                                        |     |

|       |         | Features                                                  |     |

|       | 13.1.2  | Block Diagram                                             | 370 |

|       | 13.1.3  | Pin Configuration                                         | 371 |

|       | 13.1.4  | Register Configuration                                    | 371 |

| 13.2  | Registe | r Descriptions                                            | 373 |

|       |         | Receive Shift Register (RSR)                              |     |

|       | 13.2.2  | Receive Data Register (RDR)                               |     |

|       | 13.2.3  | Transmit Shift Register (TSR)                             |     |

|       | 13.2.4  | Transmit Data Register (TDR)                              |     |

|       | 13.2.5  |                                                           |     |

|       | 13.2.6  | Serial Control Register (SCR)                             | 377 |

Rev. 5.00 Jan 06, 2006 page xiii of xx

|                      | 13.2.7                                                                                                                                                                              | Serial Status Register (SSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 380                                                                                                                                      |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 13.2.8                                                                                                                                                                              | Bit Rate Register (BRR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 384                                                                                                                                      |

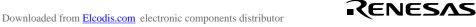

| 13.3                 | Operati                                                                                                                                                                             | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 394                                                                                                                                      |

|                      | 13.3.1                                                                                                                                                                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 394                                                                                                                                      |

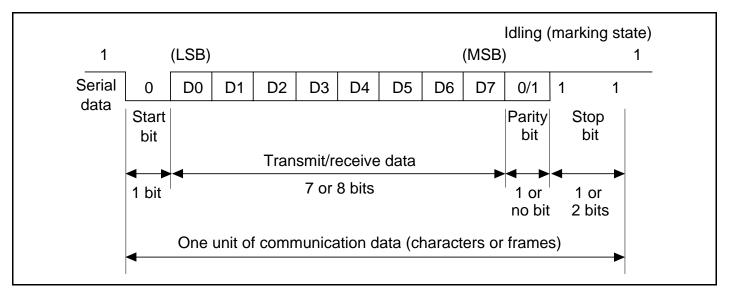

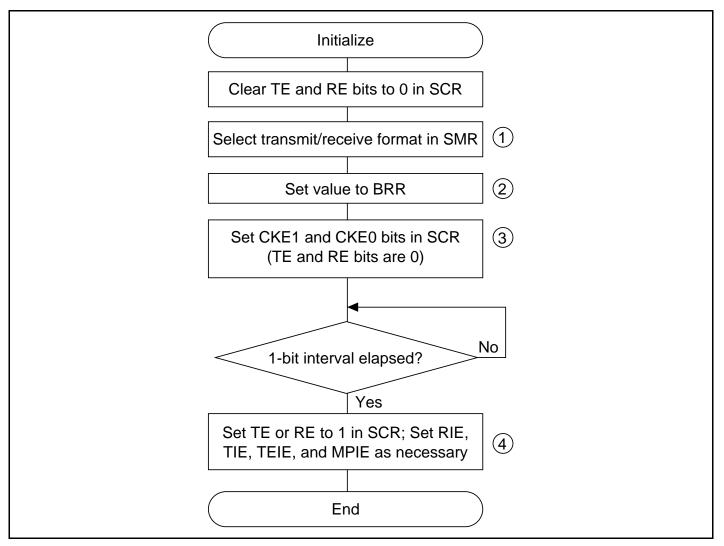

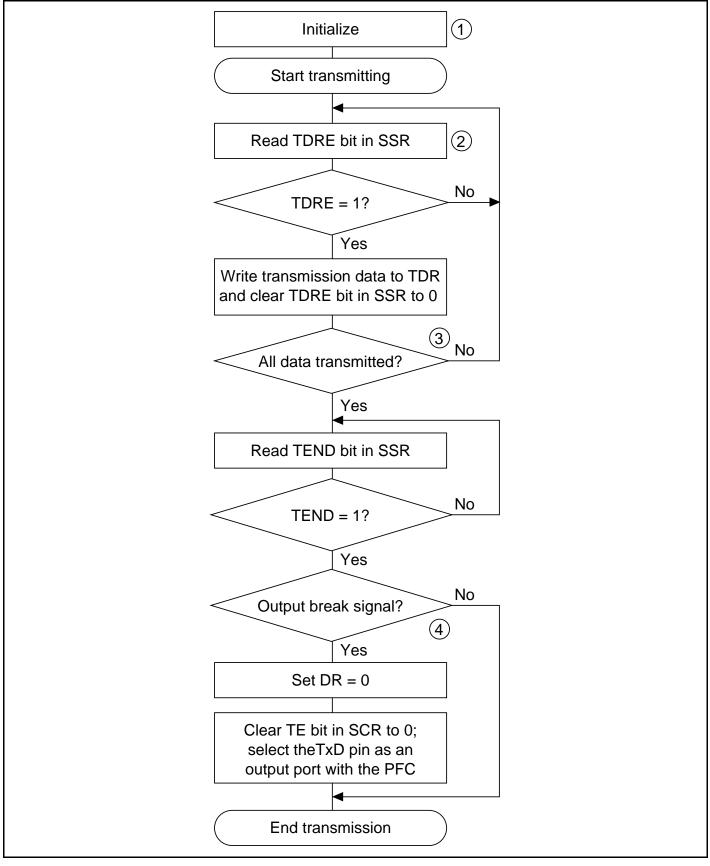

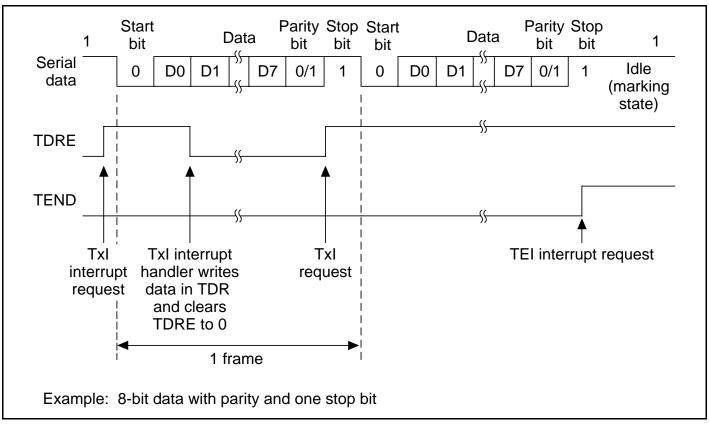

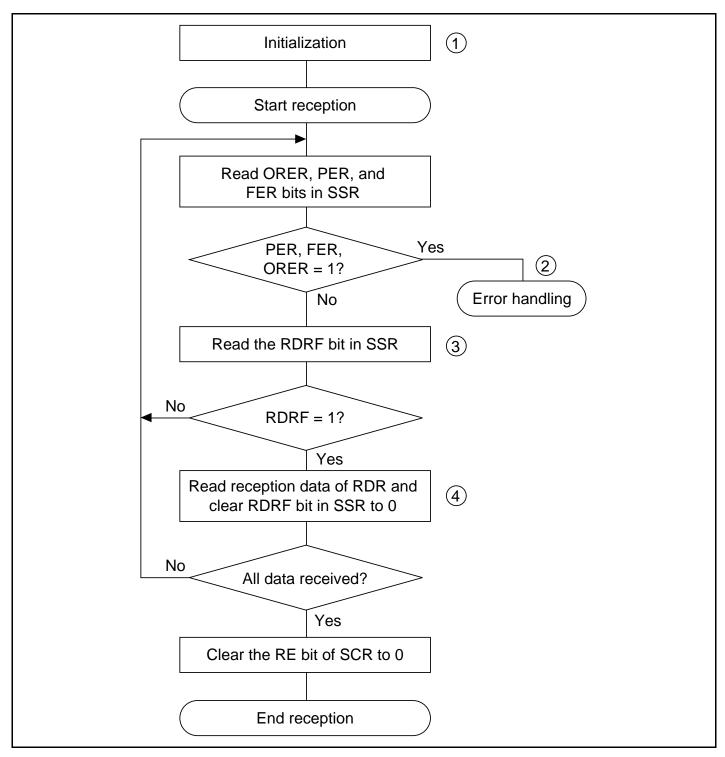

|                      | 13.3.2                                                                                                                                                                              | Operation in Asynchronous Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 396                                                                                                                                      |

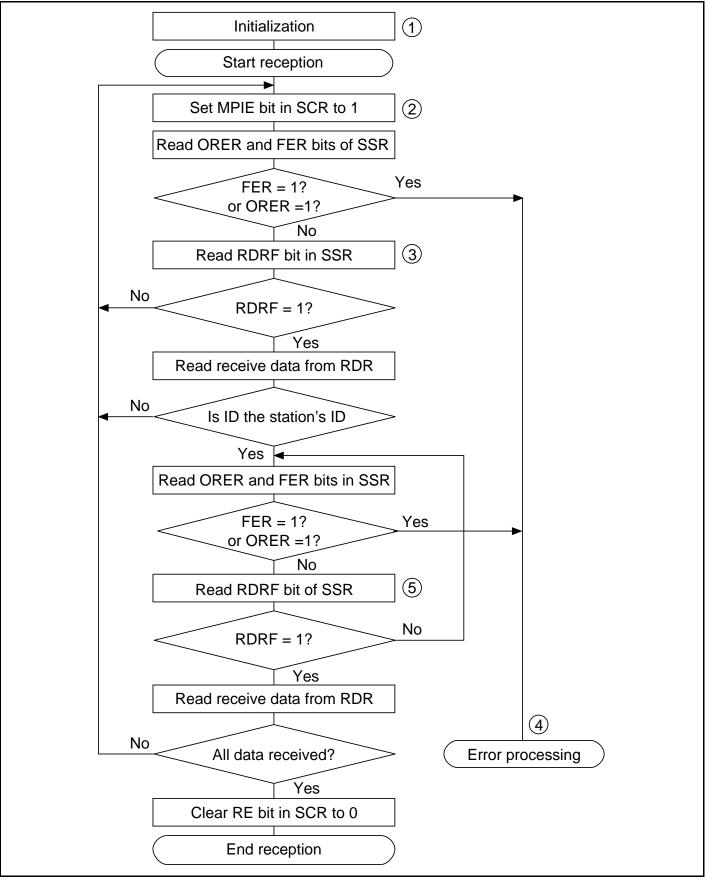

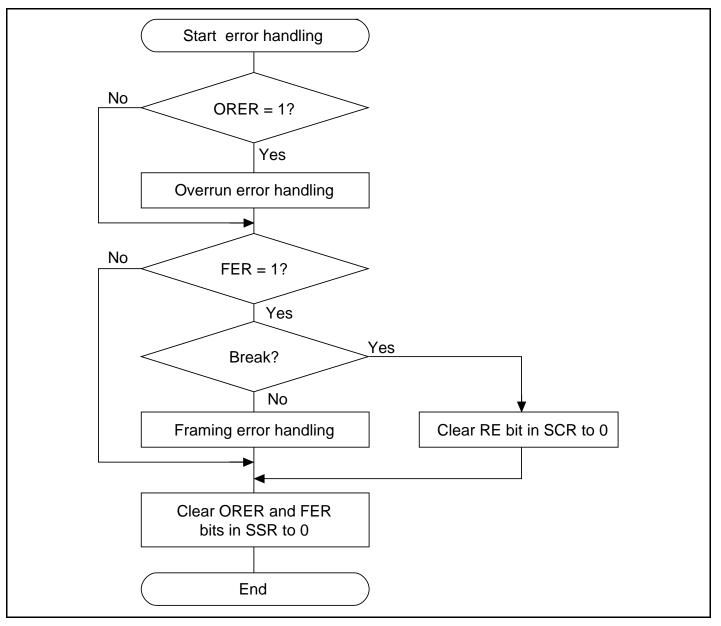

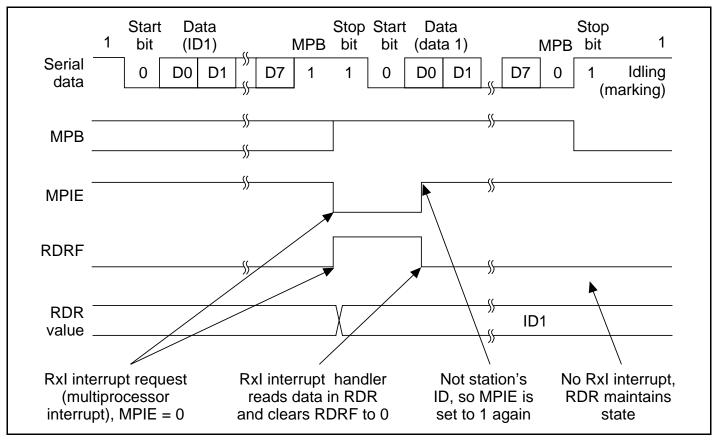

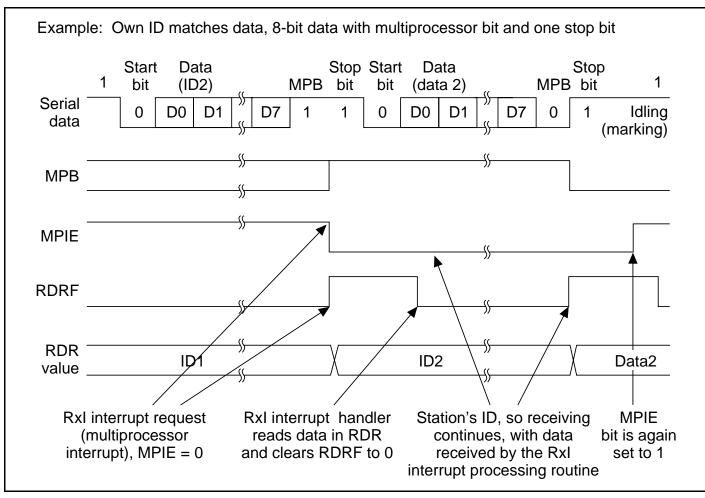

|                      | 13.3.3                                                                                                                                                                              | Multiprocessor Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 406                                                                                                                                      |

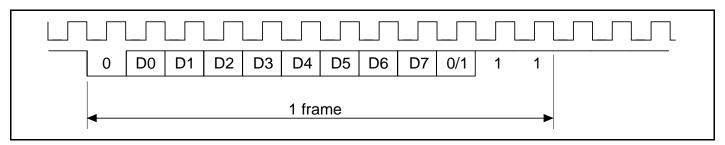

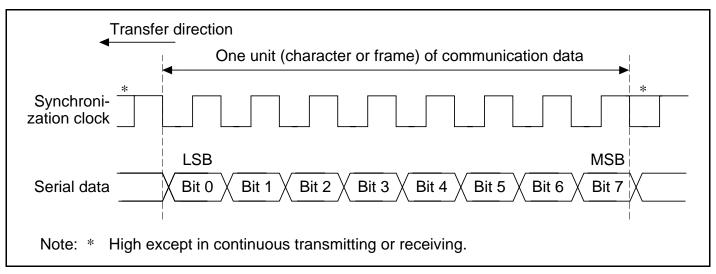

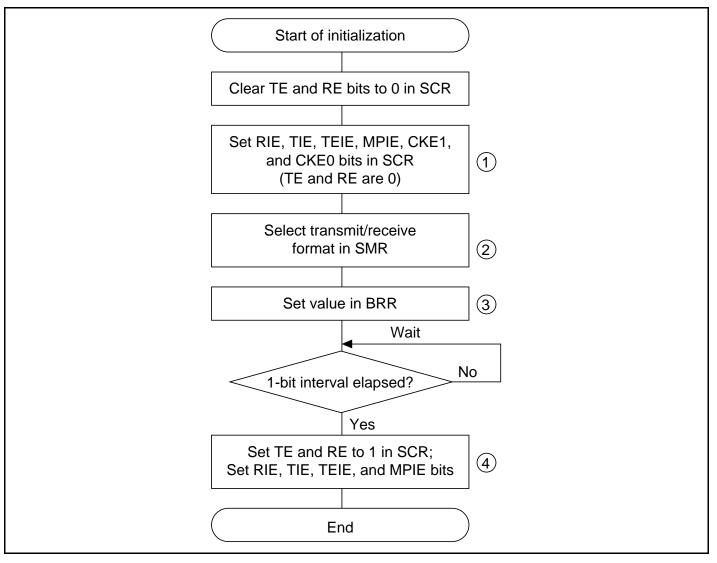

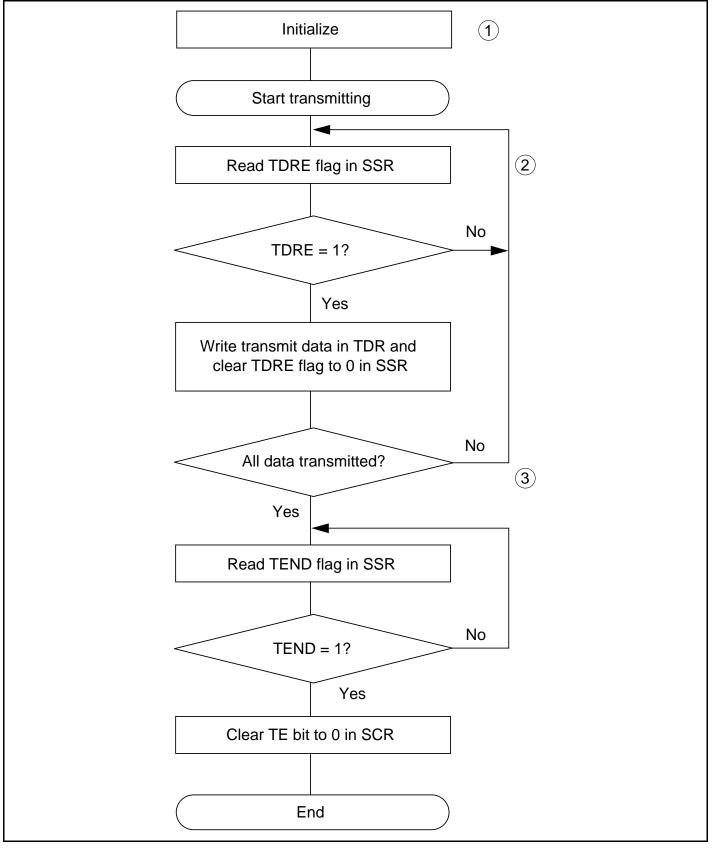

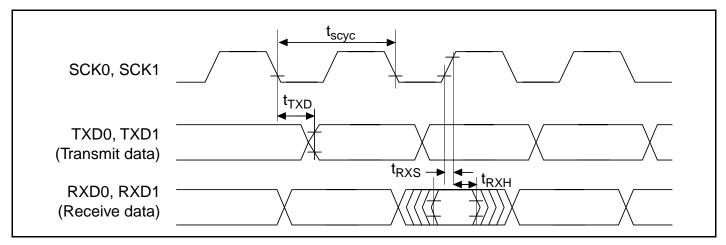

|                      | 13.3.4                                                                                                                                                                              | Clock Synchronous Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 414                                                                                                                                      |

| 13.4                 | SCI Int                                                                                                                                                                             | errupt Sources and the DMAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 425                                                                                                                                      |

| 13.5                 | Notes of                                                                                                                                                                            | on Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 426                                                                                                                                      |

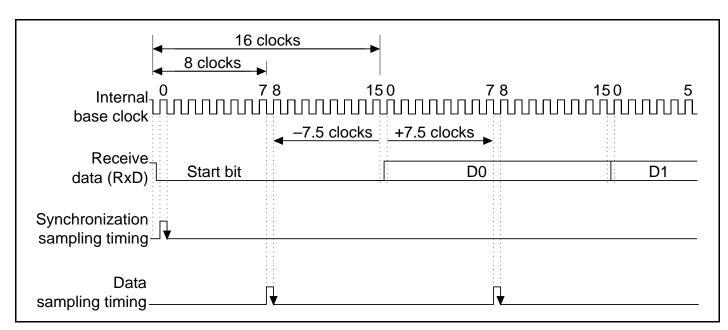

|                      | 13.5.1                                                                                                                                                                              | TDR Write and TDRE Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 426                                                                                                                                      |

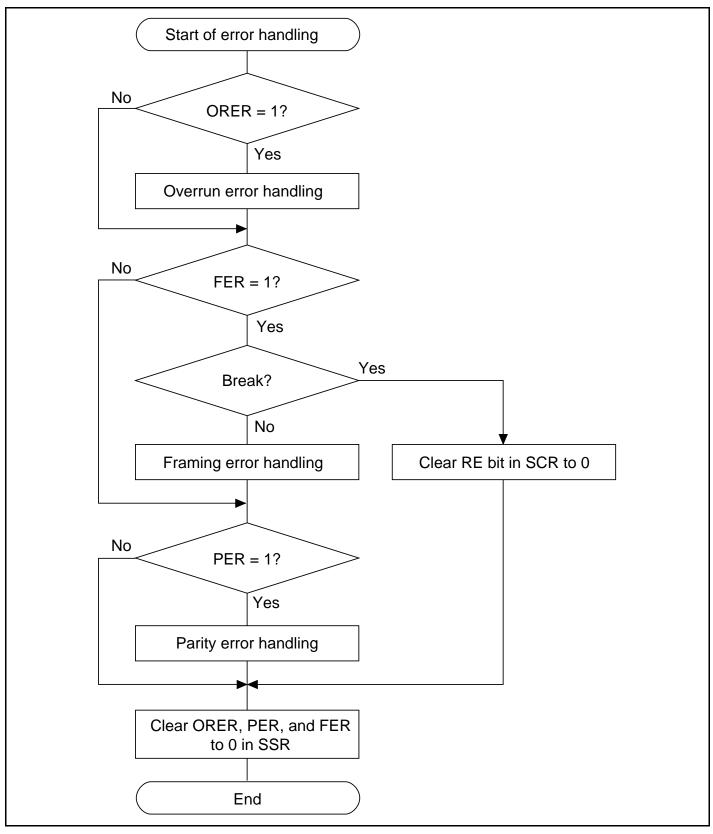

|                      | 13.5.2                                                                                                                                                                              | Simultaneous Multiple Receive Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 426                                                                                                                                      |

|                      | 13.5.3                                                                                                                                                                              | Break Detection and Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 427                                                                                                                                      |

|                      | 13.5.4                                                                                                                                                                              | Sending a Break Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 427                                                                                                                                      |

|                      | 13.5.5                                                                                                                                                                              | Receive Error Flags and Transmitter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |

|                      |                                                                                                                                                                                     | (Clock Synchronous Mode Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 427                                                                                                                                      |

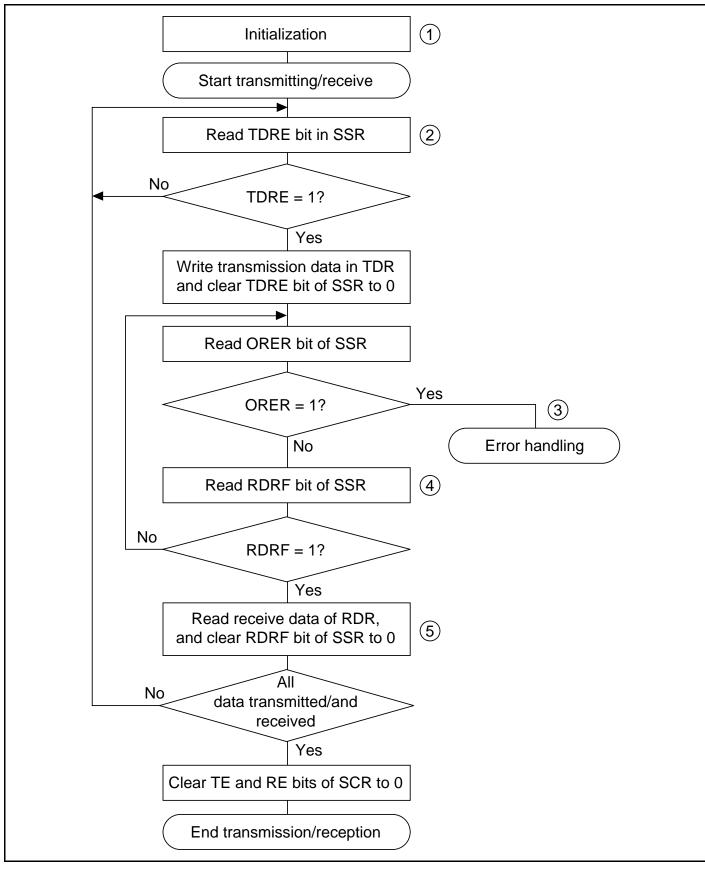

|                      | 13.5.6                                                                                                                                                                              | Receive Data Sampling Timing and Receive Margin in the Asynchronous                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

|                      |                                                                                                                                                                                     | Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 427                                                                                                                                      |

|                      | 13.5.7                                                                                                                                                                              | Constraints on DMAC Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 429                                                                                                                                      |

|                      | 13.5.8                                                                                                                                                                              | Cautions for Clock Synchronous External Clock Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 429                                                                                                                                      |

|                      | 13.5.9                                                                                                                                                                              | Caution for Clock Synchronous Internal Clock Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 429                                                                                                                                      |

|                      |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

| ~ .                  |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

|                      |                                                                                                                                                                                     | A/D Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |

| Secti<br>14.1        | Overvie                                                                                                                                                                             | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 431                                                                                                                                      |

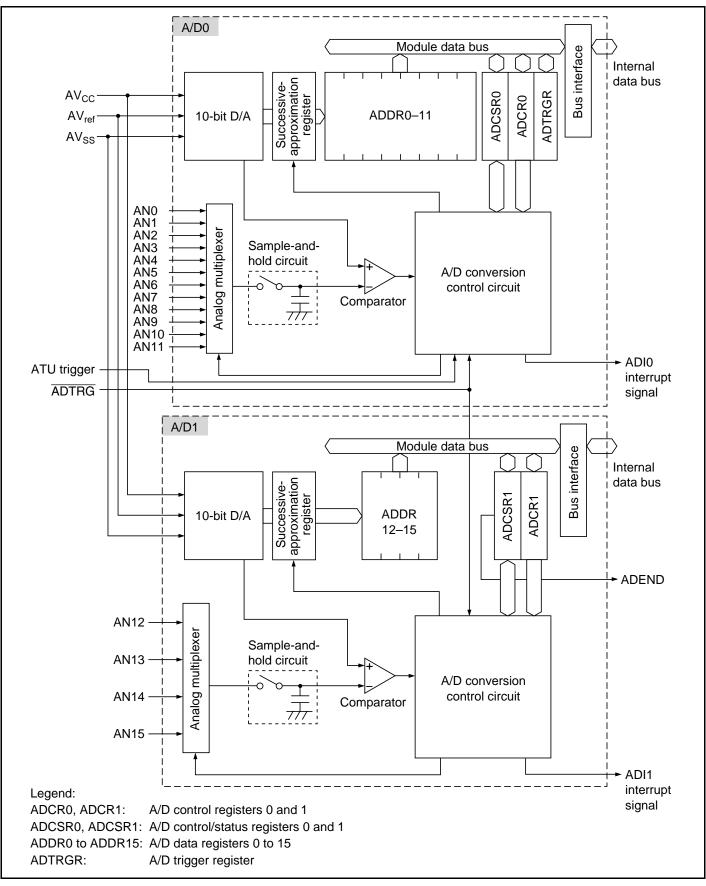

|                      | Overvie<br>14.1.1                                                                                                                                                                   | ew<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 431<br>431                                                                                                                               |

|                      | Overvie<br>14.1.1<br>14.1.2                                                                                                                                                         | ew<br>Features<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 431<br>431<br>432                                                                                                                        |

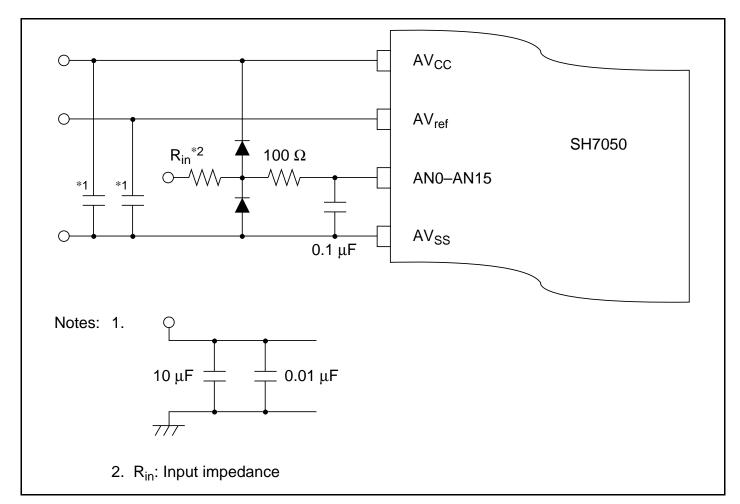

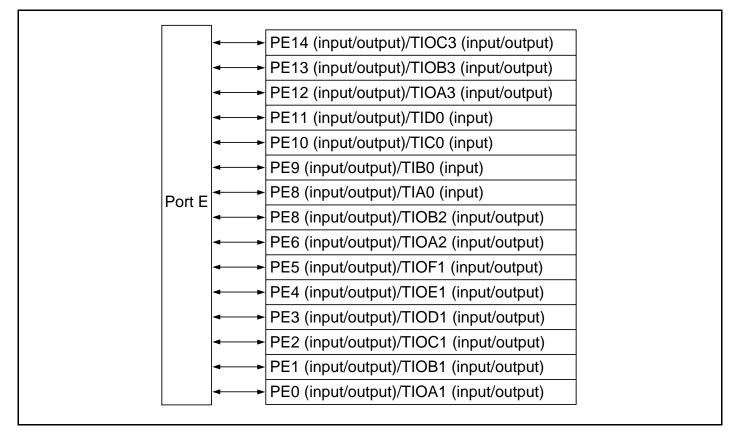

|                      | Overvie<br>14.1.1<br>14.1.2<br>14.1.3                                                                                                                                               | ew<br>Features<br>Block Diagram<br>Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 431<br>431<br>432<br>434                                                                                                                 |

|                      | Overvie<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4                                                                                                                                     | ew<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                    | 431<br>431<br>432<br>434<br>436                                                                                                          |

|                      | Overvie<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe                                                                                                                          | ew<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration<br>r Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                  | 431<br>431<br>432<br>434<br>436<br>437                                                                                                   |

| 14.1                 | Overvie<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1                                                                                                                | Features<br>Flock Diagram<br>Pin Configuration<br>Register Configuration<br>r Descriptions<br>A/D Data Registers 0 to 15 (ADDR0 to ADDR15)                                                                                                                                                                                                                                                                                                                                                                        | 431<br>431<br>432<br>434<br>436<br>437<br>437                                                                                            |

| 14.1                 | Overvie<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2                                                                                                      | Features<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration<br>r Descriptions<br>A/D Data Registers 0 to 15 (ADDR0 to ADDR15)<br>A/D Control/Status Register 0 (ADCSR0)                                                                                                                                                                                                                                                                                                                  | 431<br>432<br>434<br>436<br>437<br>437<br>438                                                                                            |

| 14.1                 | Overvie<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3                                                                                            | Features<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration<br>r Descriptions<br>A/D Data Registers 0 to 15 (ADDR0 to ADDR15)<br>A/D Control/Status Register 0 (ADCSR0)<br>A/D Control Register 0 (ADCR0)                                                                                                                                                                                                                                                                                | 431<br>432<br>434<br>436<br>437<br>437<br>438<br>442                                                                                     |

| 14.1                 | Overvie<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4                                                                                  | Features         Block Diagram         Pin Configuration         Register Configuration         r Descriptions         A/D Data Registers 0 to 15 (ADDR0 to ADDR15)         A/D Control/Status Register 0 (ADCSR0)         A/D Control/Status Register 1 (ADCSR1)                                                                                                                                                                                                                                                 | 431<br>432<br>434<br>436<br>437<br>437<br>437<br>438<br>442<br>444                                                                       |

| 14.1                 | Overvie<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5                                                                        | <ul> <li>Features.</li> <li>Flock Diagram.</li> <li>Pin Configuration.</li> <li>Register Configuration.</li> <li>r Descriptions.</li> <li>A/D Data Registers 0 to 15 (ADDR0 to ADDR15).</li> <li>A/D Control/Status Register 0 (ADCSR0).</li> <li>A/D Control Register 0 (ADCR0).</li> <li>A/D Control/Status Register 1 (ADCSR1).</li> <li>A/D Control Register 1 (ADCR1).</li> </ul>                                                                                                                            | 431<br>432<br>434<br>436<br>437<br>437<br>438<br>442<br>444<br>445                                                                       |

| 14.1                 | Overvia<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6                                                              | ew.Features.Block Diagram.Pin Configuration.Register Configuration.r Descriptions .A/D Data Registers 0 to 15 (ADDR0 to ADDR15).A/D Control/Status Register 0 (ADCSR0).A/D Control Register 0 (ADCR0).A/D Control/Status Register 1 (ADCSR1).A/D Control Register 1 (ADCR1).A/D Trigger Register (ADTRGR)                                                                                                                                                                                                         | 431<br>432<br>434<br>436<br>437<br>437<br>438<br>442<br>444<br>445<br>446                                                                |

| 14.1<br>14.2<br>14.3 | Overvia<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>CPU In                                                    | ewFeaturesBlock DiagramPin ConfigurationRegister Configurationr DescriptionsA/D Data Registers 0 to 15 (ADDR0 to ADDR15)A/D Control/Status Register 0 (ADCSR0)A/D Control Register 0 (ADCR0)A/D Control/Status Register 1 (ADCSR1)A/D Control Register 1 (ADCR1)A/D Trigger Register (ADTRGR)terface                                                                                                                                                                                                              | 431<br>432<br>434<br>436<br>437<br>437<br>437<br>438<br>442<br>444<br>445<br>446<br>447                                                  |

| 14.1                 | Overvia<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>CPU In<br>Operati                                         | ew       Features         Block Diagram       Pin Configuration         Register Configuration       r         r Descriptions       A/D Data Registers 0 to 15 (ADDR0 to ADDR15)         A/D Data Registers 0 to 15 (ADDR0 to ADDR15)       A/D Control/Status Register 0 (ADCSR0)         A/D Control Register 0 (ADCR0)       A/D Control/Status Register 1 (ADCR1)         A/D Control Register 1 (ADCR1)       A/D Control Register 1 (ADCR1)         A/D Trigger Register (ADTRGR)       terface.         on | 431<br>432<br>434<br>436<br>437<br>437<br>438<br>442<br>444<br>445<br>446<br>447<br>448                                                  |

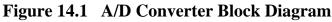

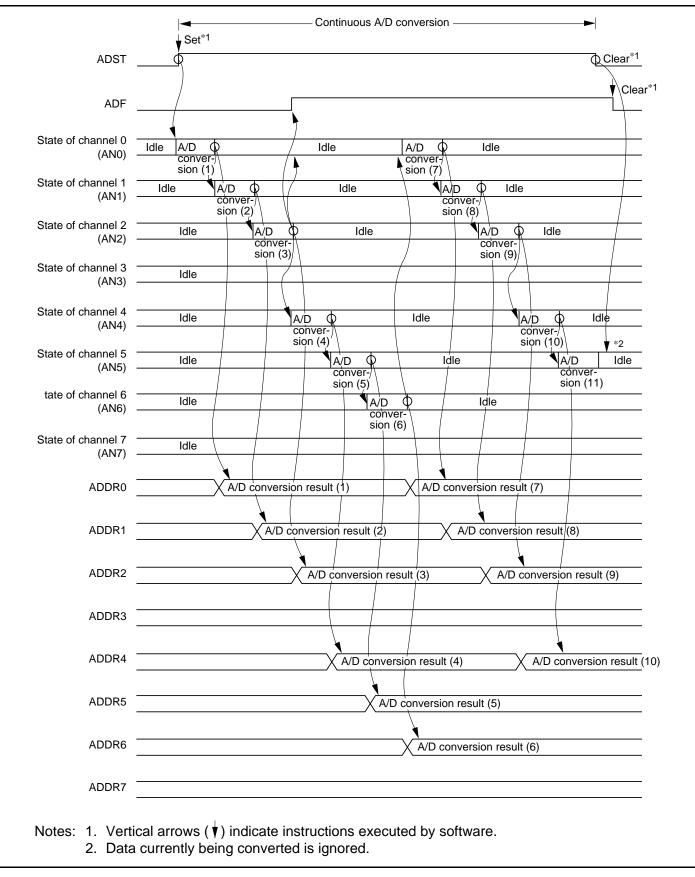

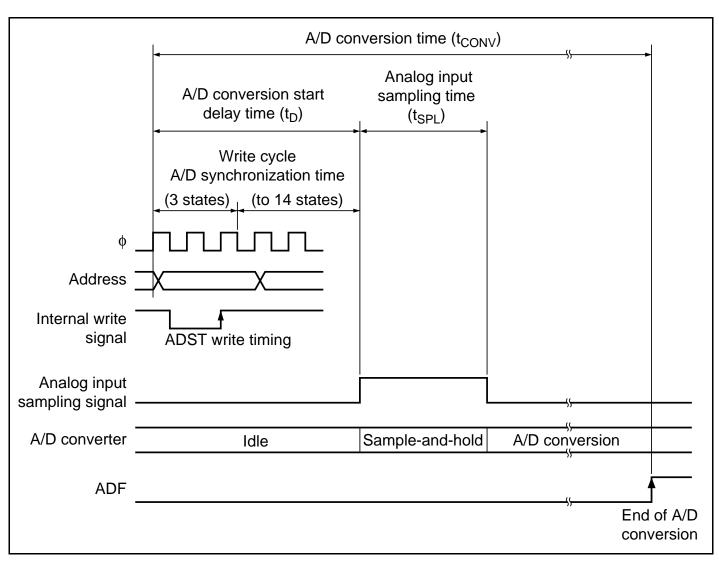

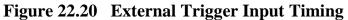

| 14.1<br>14.2<br>14.3 | Overvia<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>CPU In<br>Operati<br>14.4.1                               | ew<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration<br>r Descriptions<br>A/D Data Registers 0 to 15 (ADDR0 to ADDR15)<br>A/D Control/Status Register 0 (ADCSR0)<br>A/D Control Register 0 (ADCR0)<br>A/D Control Register 1 (ADCSR1)<br>A/D Control Register 1 (ADCSR1)<br>A/D Trigger Register 1 (ADCR1)<br>A/D Trigger Register (ADTRGR)<br>terface                                                                                                                                  | 431<br>432<br>434<br>436<br>437<br>437<br>438<br>442<br>444<br>445<br>446<br>447<br>448<br>448                                           |

| 14.1<br>14.2<br>14.3 | Overvia<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>CPU In<br>Operati<br>14.4.1<br>14.4.2                     | ew         Features         Block Diagram         Pin Configuration         Register Configuration         r Descriptions         A/D Data Registers 0 to 15 (ADDR0 to ADDR15)         A/D Control/Status Register 0 (ADCSR0)         A/D Control Register 0 (ADCR0)         A/D Control Register 1 (ADCR1)         A/D Control Register 1 (ADCR1)         A/D Trigger Register (ADTRGR)                                                                                                                          | 431<br>432<br>434<br>436<br>437<br>437<br>437<br>438<br>442<br>444<br>445<br>446<br>447<br>448<br>448<br>448<br>450                      |

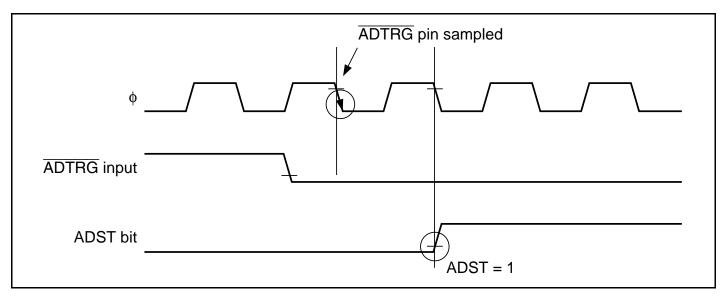

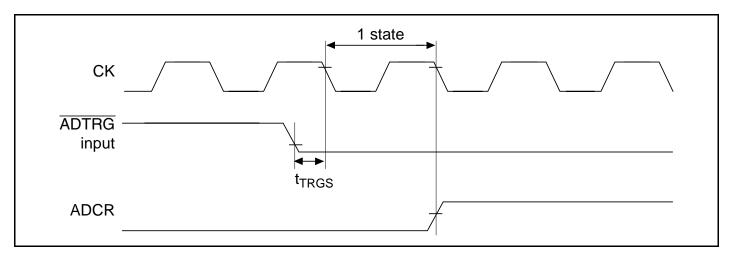

| 14.1<br>14.2<br>14.3 | Overvia<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>CPU In<br>Operati<br>14.4.1<br>14.4.2<br>14.4.3           | ew         Features         Block Diagram         Pin Configuration         Register Configuration         r Descriptions         A/D Data Registers 0 to 15 (ADDR0 to ADDR15)         A/D Control/Status Register 0 (ADCSR0)         A/D Control Register 0 (ADCR0)         A/D Control Register 1 (ADCR1)         A/D Trigger Register 1 (ADCR1)         A/D Trigger Register (ADTRGR)         terface                                                                                                          | 431<br>432<br>434<br>436<br>437<br>437<br>438<br>442<br>444<br>445<br>444<br>445<br>446<br>447<br>448<br>448<br>448<br>450<br>452        |

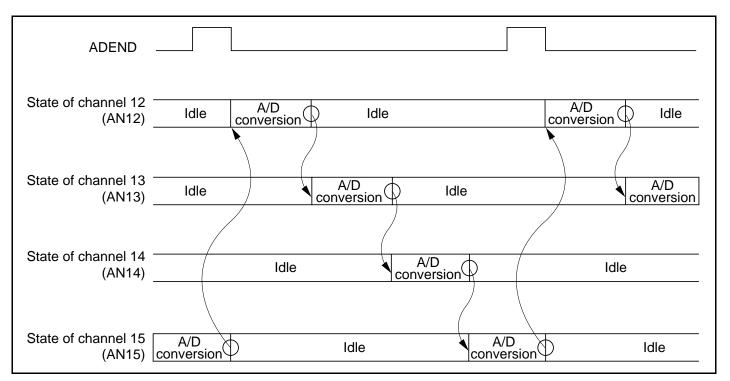

| 14.1<br>14.2<br>14.3 | Overvia<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>Registe<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>CPU In<br>Operati<br>14.4.1<br>14.4.2<br>14.4.3<br>14.4.4 | ew         Features         Block Diagram         Pin Configuration         Register Configuration         r Descriptions         A/D Data Registers 0 to 15 (ADDR0 to ADDR15)         A/D Control/Status Register 0 (ADCSR0)         A/D Control Register 0 (ADCR0)         A/D Control Register 1 (ADCR1)         A/D Control Register 1 (ADCR1)         A/D Trigger Register (ADTRGR)                                                                                                                          | 431<br>432<br>434<br>436<br>437<br>437<br>437<br>438<br>442<br>444<br>445<br>444<br>445<br>446<br>447<br>448<br>448<br>450<br>452<br>454 |

Rev. 5.00 Jan 06, 2006 page xiv of xx

|       | 14.4.6   | ADEND Output Pin                                       | 455 |

|-------|----------|--------------------------------------------------------|-----|

| 14.5  | Interrup | ot Sources and DMA Transfer Requests                   | 456 |

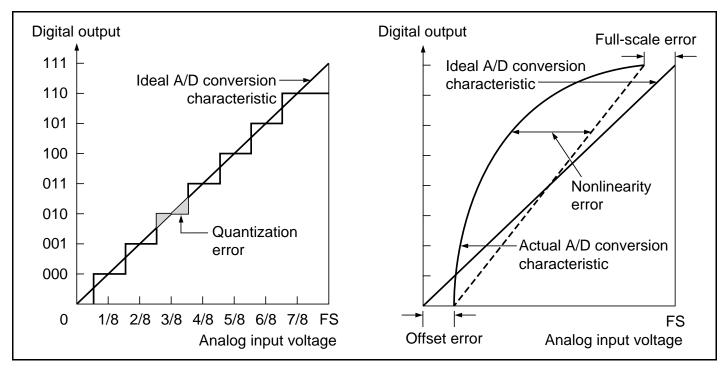

| 14.6  | Usage 1  | Notes                                                  | 456 |

|       |          |                                                        |     |

| Secti | on 15    | Compare Match Timer (CMT)                              | 459 |

| 15.1  | Overvie  | ew                                                     | 459 |

|       | 15.1.1   | Features                                               | 459 |

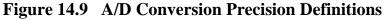

|       | 15.1.2   | Block Diagram                                          | 460 |

|       | 15.1.3   | Register Configuration                                 | 461 |

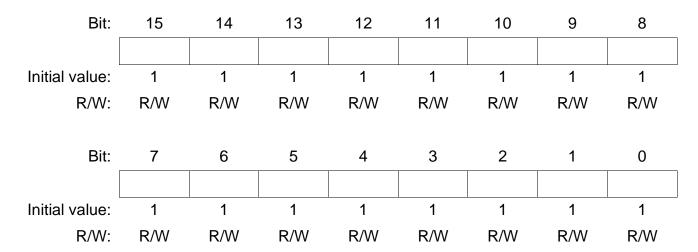

| 15.2  | Registe  | r Descriptions                                         | 462 |

|       | 15.2.1   | Compare Match Timer Start Register (CMSTR)             | 462 |

|       | 15.2.2   | Compare Match Timer Control/Status Register (CMCSR)    | 463 |

|       |          | Compare Match Timer Counter (CMCNT)                    |     |

|       | 15.2.4   | Compare Match Timer Constant Register (CMCOR)          | 465 |

| 15.3  |          | on                                                     |     |

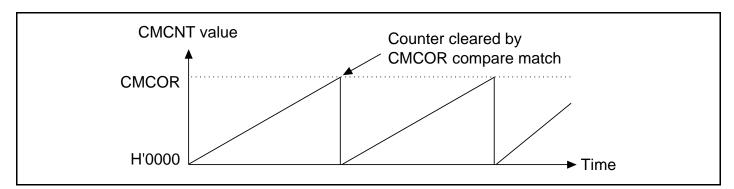

|       | 15.3.1   | Period Count Operation                                 | 465 |

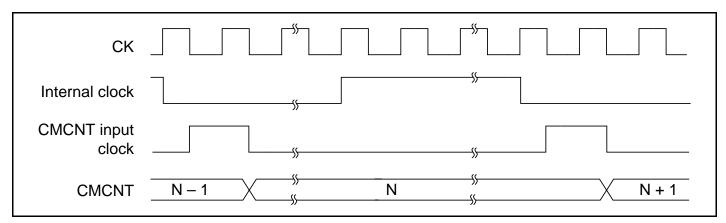

|       | 15.3.2   | CMCNT Count Timing                                     | 466 |

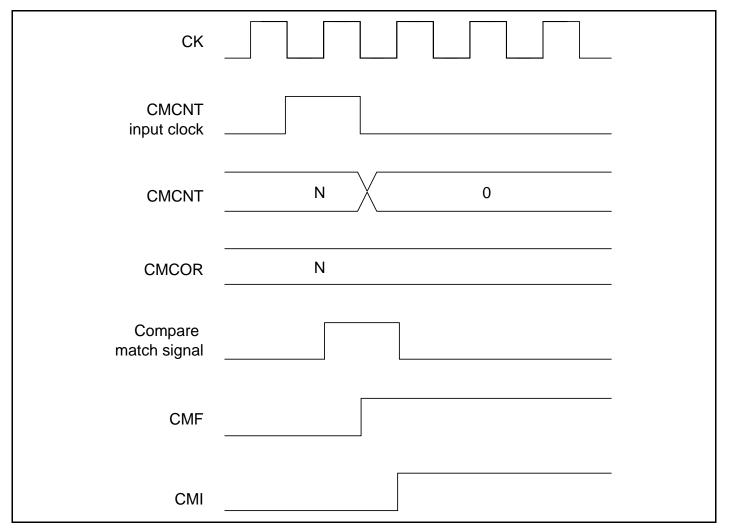

| 15.4  | Interrup | Dts                                                    | 466 |

|       | 15.4.1   | Interrupt Sources and DTC Activation                   | 466 |

|       | 15.4.2   | Compare Match Flag Set Timing                          | 467 |

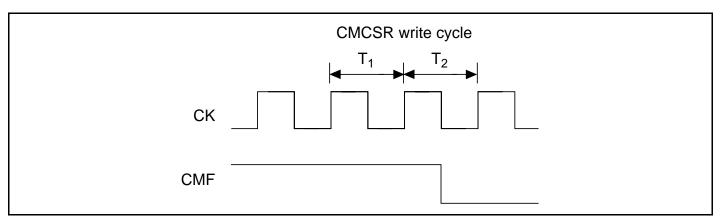

|       | 15.4.3   | Compare Match Flag Clear Timing                        | 468 |

| 15.5  | Notes of | n Use                                                  | 469 |

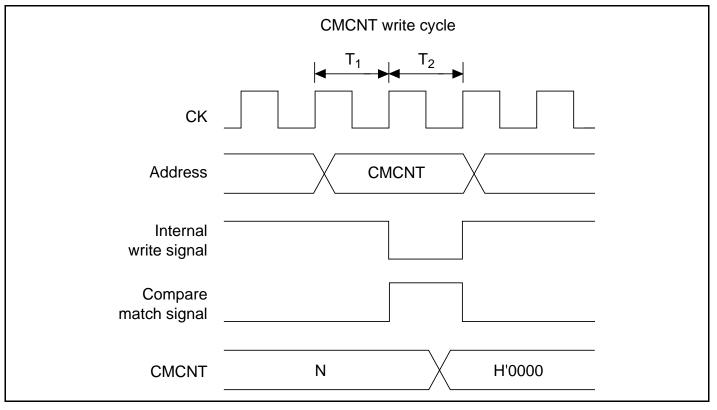

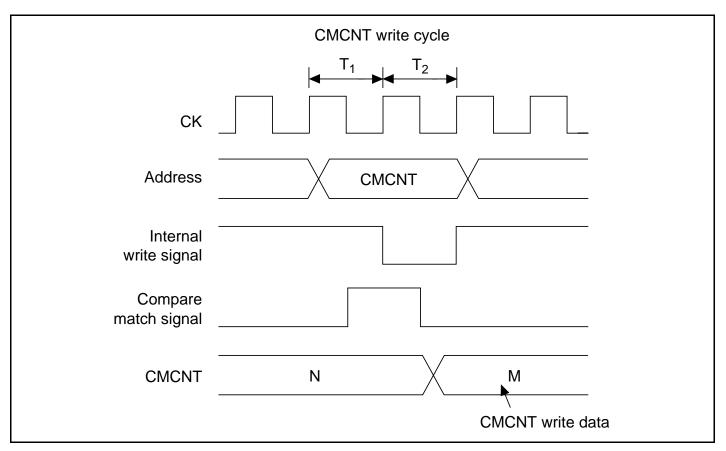

|       | 15.5.1   | Contention between CMCNT Write and Compare Match       | 469 |

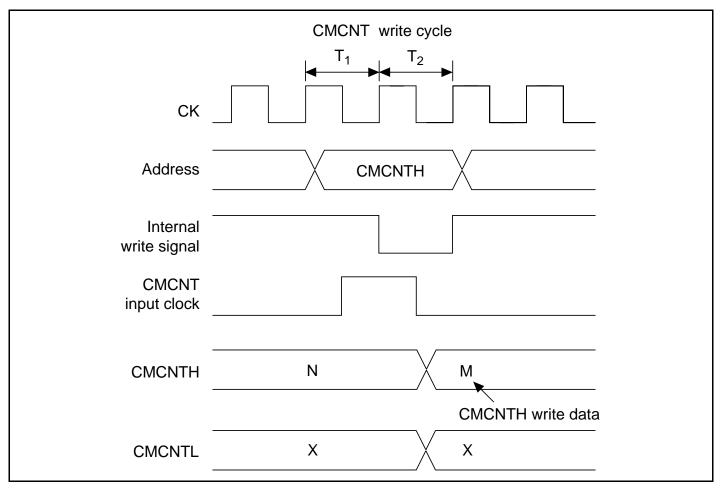

|       | 15.5.2   | Contention between CMCNT Word Write and Incrementation | 470 |

|       | 15.5.3   | Contention between CMCNT Byte Write and Incrementation | 471 |

|       |          |                                                        |     |

| Secti | on 16    | Pin Function Controller (PFC)                          | 473 |

| 16.1  |          | ew                                                     |     |

| 16.2  | Registe  | r Configuration                                        | 478 |

| 16.3  | -        | r Descriptions                                         |     |

|       | 16.3.1   | Port A IO Register (PAIOR)                             | 479 |

|       | 16.3.2   | Port A Control Register (PACR)                         | 479 |

|       | 16.3.3   | Port B IO Register (PBIOR)                             | 484 |

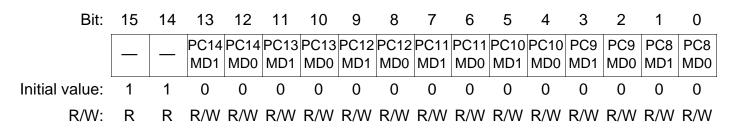

|       | 16.3.4   | Port B Control Register (PBCR)                         | 484 |

|       |          | Port C IO Register (PCIOR)                             |     |

|       | 16.3.6   | Port C Control Registers 1 and 2 (PCCR1, PCCR2)        | 488 |

|       | 16.3.7   | Port D IO Register (PDIOR)                             | 494 |

|       |          | Port D Control Register (PDCR)                         |     |

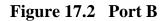

|       |          | Port E IO Register (PEIOR)                             |     |

|       |          | Port E Control Register (PECR)                         |     |

|       | 16.3.11  | Port F IO Register (PFIOR)                             | 504 |

Rev. 5.00 Jan 06, 2006 page xv of xx

|       | 16.3.12 | Port F Control Registers 1 and 2 (PFCR1, PFCR2)     | 504   |

|-------|---------|-----------------------------------------------------|-------|

|       | 16.3.13 | Port G IO Register (PGIOR)                          | 510   |

|       | 16.3.14 | Port G Control Registers 1 and 2 (PGCR1, PGCR2)     | 510   |

|       | 16.3.15 | CK Control Register (CKCR)                          | 516   |

| C     | 17      |                                                     | - 1 - |

|       |         | I/O Ports (I/O)                                     |       |

| 17.1  |         | ew                                                  |       |

| 17.2  |         |                                                     |       |

|       |         | Register Configuration                              |       |

| . – . |         | Port A Data Register (PADR)                         |       |

| 17.3  |         |                                                     |       |

|       |         | Register Configuration                              |       |

|       |         | Port B Data Register (PBDR)                         |       |

| 17.4  |         |                                                     |       |

|       |         | Register Configuration                              |       |

|       |         | Port C Data Register (PCDR)                         |       |

| 17.5  |         |                                                     |       |

|       | 17.5.1  | Register Configuration                              | 525   |

|       | 17.5.2  | Port D Data Register (PDDR)                         | 525   |

| 17.6  | Port E. |                                                     | 527   |

|       | 17.6.1  | Register Configuration                              | 527   |

|       | 17.6.2  | Port E Data Register (PEDR)                         | 528   |

| 17.7  | Port F  |                                                     | 529   |