Triple 80 MHz Video Amplifier with DC Restore

#### **Features**

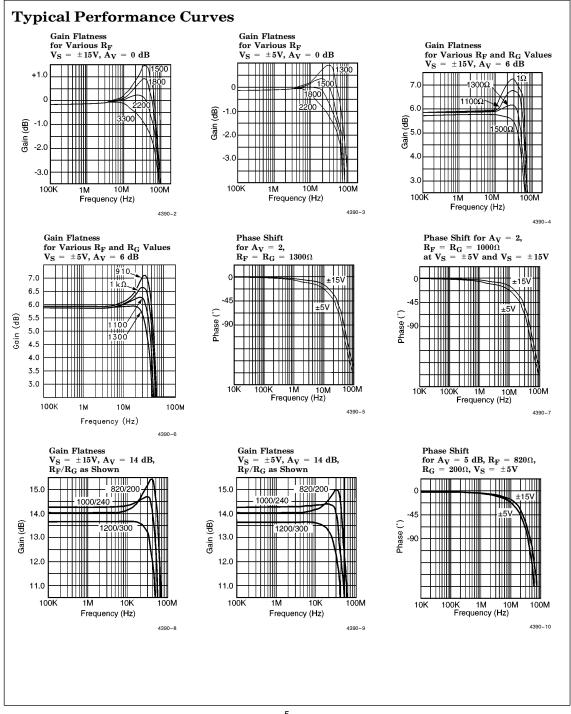

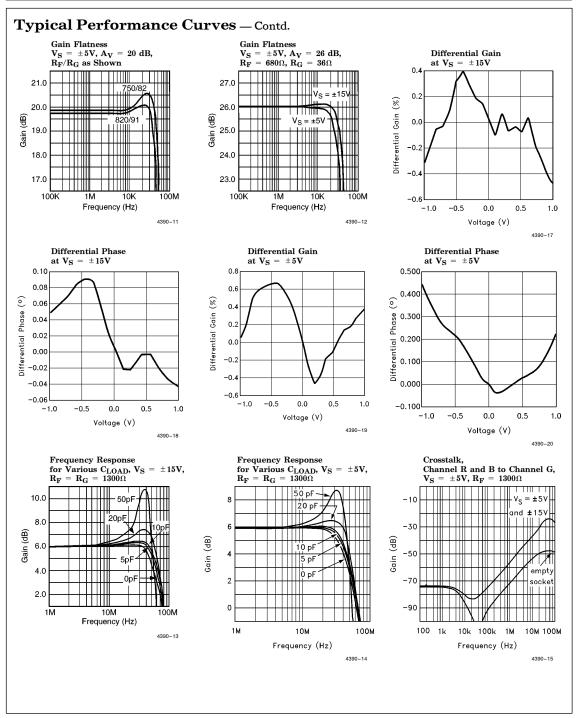

- 80 MHz -3 dB bandwidth for gains of 1 to 10

- 800 V/µs slew rate

- 15 MHz bandwidth flat to 0.1 dB

- Excellent differential gain and phase

- TTL/CMOS compatible DC restore function

- Available in 16 lead P-DIP, 16 lead SOL

#### **Applications**

- RGB drivers requiring DC restoration

- RGB multiplexers requiring DC restoration

- RGB building blocks

- Video gain blocks requiring DC restoration

- Sync and color burst processing

#### **Ordering Information**

| Part No. | Temp. Range                                    | Package      | Outline # |

|----------|------------------------------------------------|--------------|-----------|

| EL4390CN | -40°C to +85°C                                 | 16-Pin P-DIP | MDP0031   |

| EL4390CM | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | 16-Lead SOL  | MDP0027   |

#### **General Description**

The EL4390C is three wideband current-mode feedback amplifiers optimized for video performance, each with a DC restore amplifier. The DC restore function is activated by a common TTL/CMOS compatible control signal while each channel has a separate restore reference.

Each amplifier can drive a load of  $150\Omega$  at video signal levels. The EL4390C operates on supplies as low as  $\pm 4V$  up to  $\pm 15V$ .

Being a current-mode feedback design, the bandwidth stays relatively constant at approximately 80MHz over the  $\pm 1$  to  $\pm 10$  gain range. The EL4390C has been optimized for use with  $1300\Omega$  feedback resistors.

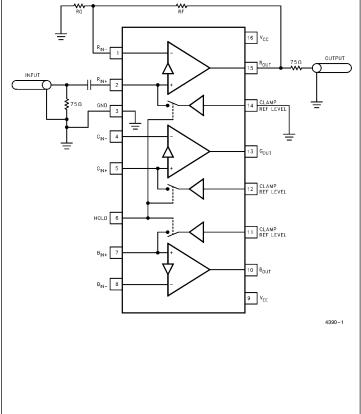

#### **Connection Diagram**

Note: All information contained in this data sheet has been carefully checked and is believed to be accurate as of the date of publication; however, this data sheet cannot be a "controlled document". Current revisions, if any, to these specifications are maintained at the factory and are available upon your request. We recommend checking the revision level before finalization of your design documentation.

© 1994 Elantec, Inc.

### Triple 80 MHz Video Amplifier with DC Restore

#### Absolute Maximum Ratings $(T_A = 25^{\circ}C)$

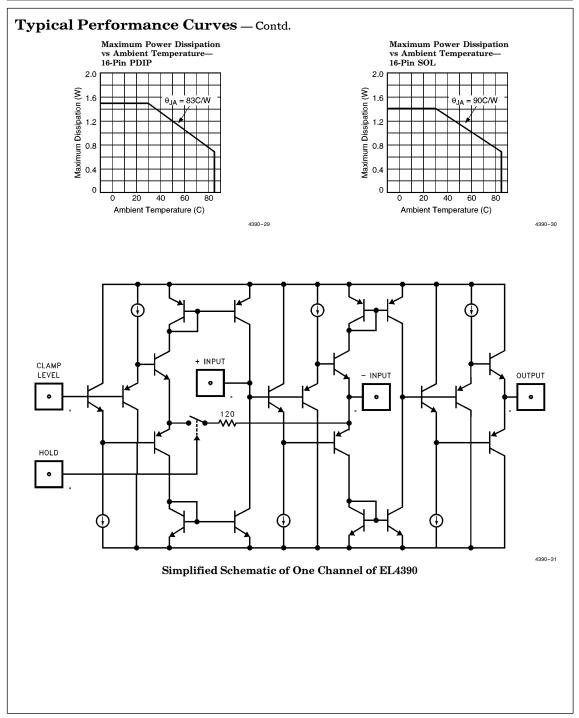

| Voltage between $V_S+$ and $V_S-$                    | +33V    | Internal Power Dissipation     | See Curves                         |

|------------------------------------------------------|---------|--------------------------------|------------------------------------|

| Voltage at V <sub>S</sub> +                          | +18V    | Operating Ambient Temp. Range  | $-40^{\circ}$ C to $+85^{\circ}$ C |

| Voltage at V <sub>S</sub> –                          | -18V    | Operating Junction Temperature | 150°C                              |

| Voltage between $ m V_{IN}+$ and $ m V_{IN}-$        | $\pm6V$ | Storage Temperature Range      | -65°C to $+150$ °C                 |

| Current into V <sub>IN</sub> + and V <sub>IN</sub> - | 5mA     |                                |                                    |

#### Important Note:

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefore  $T_J = T_C = T_A$ .

| Test Level | Test Procedure                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------|

| I          | 100% production tested and QA sample tested per QA test plan QCX0002.                                       |

| II         | 100% production tested at $T_{ m A}=25^{\circ}{ m C}$ and QA sample tested at $T_{ m A}=25^{\circ}{ m C}$ , |

|            | The are and Theres per OA test plan OCX0002                                                                 |

III QA sample tested per QA test plan QCX0002.

$\begin{array}{ll} IV & \text{Parameter is guaranteed (but not tested) by Design and Characterization Data.} \\ V & \text{Parameter is typical value at } T_A = 25^{\circ}\text{C for information purposes only.} \\ \end{array}$

#### Open Loop DC Electrical Characteristics Supplies at $\pm 15$ V, Load = 1K $\Omega$

| Parameter                        | Description                                     | Temp   | Min | Тур | Max | Test<br>Level | Units |  |

|----------------------------------|-------------------------------------------------|--------|-----|-----|-----|---------------|-------|--|

| Amplifier Section (not restored) |                                                 |        |     |     |     |               |       |  |

| V <sub>OS</sub>                  | Input Offset Voltage                            | + 25°C |     | 2   | 15  | II            | mV    |  |

| I <sub>B</sub> +                 | I <sub>IN</sub> + Input Bias Current            | + 25°C |     | 0.2 | 5   | II            | μΑ    |  |

| I <sub>B</sub> -                 | I <sub>IN</sub> — Input Bias Current            | + 25°C |     | 10  | 65  | II            | μΑ    |  |

| R <sub>OL</sub>                  | Transimpedance (Note 1)                         | + 25°C | 100 | 220 |     | II            | kΩ    |  |

| R <sub>IN</sub> -                | I <sub>N</sub> - Resistance                     | + 25°C |     | 50  |     | v             | Ω     |  |

| CMRR                             | Common-Mode Rejection Ratio (Note 2)            | + 25°C | 50  | 56  |     | II            | dB    |  |

| PSRR                             | Power Supply Rejection Ratio (Note 4)           | + 25°C | 50  | 70  |     | II            | dB    |  |

| v <sub>o</sub>                   | Output Voltage Swing; R $_{ m L}=1{ m k}\Omega$ | + 25°C | ±12 | ±13 |     | II            | v     |  |

| I <sub>SC</sub>                  | Short-Circuit Current                           | + 25°C | 45  | 70  | 100 | II            | mA    |  |

| I <sub>SY</sub>                  | Supply Current (Quiescent)                      | + 25°C | 10  | 20  | 32  | II            | mA    |  |

| Restoring Sec                    | etion                                           |        |     |     |     |               |       |  |

| V <sub>OS</sub> , COMP           | Composite Input Offset Voltage (Note 3)         | + 25°C |     | 8   | 35  | II            | mV    |  |

| $I_B^+, R$                       | Restore I <sub>N</sub> + Input Bias Current     | + 25°C |     | 0.2 | 5   | II            | μΑ    |  |

| I <sub>OUT</sub>                 | Restoring Current Available                     | + 25°C | 2   | 4   |     | II            | mA    |  |

| PSRR                             | Power Supply Rejection Ratio (Note 4)           | + 25°C | 50  | 70  |     | II            | dB    |  |

| G <sub>OUT</sub>                 | Conductance                                     | + 25°C |     | 8   |     | v             | mA/V  |  |

| I <sub>SY</sub> , RES            | Supply Current, Restoring                       | + 25°C | 10  | 23  | 37  | II            | mA    |  |

| V <sub>IL</sub> , RES            | RES Logic Low Threshold                         | + 25°C |     | 1.0 | 1.4 | II            | v     |  |

| V <sub>IH</sub> , RES            | RES Logic High Threshold                        | + 25°C | 1.4 | 1.8 |     | II            | v     |  |

### Triple 80 MHz Video Amplifier with DC Restore

| Open Loop DC Electrical Characteristics Supplies at $\pm 15$ V, Load = $1$ K $\Omega$ — Contd. |                              |        |     |     |     |               |       |

|------------------------------------------------------------------------------------------------|------------------------------|--------|-----|-----|-----|---------------|-------|

| Parameter                                                                                      | arameter Description         |        | Min | Тур | Max | Test<br>Level | Units |

| Restoring Section                                                                              |                              |        |     |     |     |               |       |

| I <sub>IL</sub> , RES                                                                          | RES Input Current, Logic Low | + 25°C | ·   | 2   | 10  | II            | μΑ    |

+ 25°C

Note 1: For current feedback amplifiers,  $A_{VOL} = R_{OL}/R_{IN}$ -.

Note 2:  $V_{CM} = \pm 10V$  for  $V_S = \pm 15V$ .

Note 3: Measured from  $V_{\text{CL}}$  to amplifier output, while restoring.

Note 4:  $V_{OS}$  is measured at  $V_S = \pm 4.5 V$  and  $V_S = \pm 16 V$ , both supplies are changed simultaneously.

#### **Closed Loop AC Electrical Characteristics**

RES Input Current, Logic High

Supplies at  $\pm$  15V, Load  $=\,$  150  $\!\Omega$  and 15 pF,  $T_{\rm A}=\,$  25°C (See note 7 re: test fixture)

| Parameter         | Description                                                                  | Min | Тур          | Max | Test<br>Level | Units      |  |

|-------------------|------------------------------------------------------------------------------|-----|--------------|-----|---------------|------------|--|

| Amplifier Section |                                                                              |     |              |     |               |            |  |

| SR                | Slew Rate (Note 5)                                                           |     | 800          |     | v             | V/µs       |  |

| SR                | Slew Rate w/ ±5V Supplies (Note 5)                                           |     | 550          |     | v             | V/µs       |  |

| BW                | Bandwidth, $-3$ dB, $A_V = 1$<br>$\pm 5$ V Supplies, $-3$ dB                 |     | 95<br>72     |     | v<br>v        | MHz<br>MHz |  |

| BW                | Bandwidth, $-0.1\mathrm{dB}$<br>$\pm5\mathrm{V}$ Supplies, $-0.1\mathrm{dB}$ |     | 20<br>14     |     | v<br>v        | MHz<br>MHz |  |

| dG                | Differential Gain at 3.58 MHz at $\pm$ 5V Supplies (Note 6)                  |     | 0.02<br>0.02 |     | V<br>V        | %<br>%     |  |

| $\mathrm{d}	heta$ | Differential Phase at 3.58 MHz at $\pm$ 5V Supplies (Note 6)                 |     | 0.03<br>0.06 |     | v<br>v        | (°)<br>(°) |  |

| Restoring Sec     | tion                                                                         | •   |              |     |               |            |  |

| $T_{ m RE}$       | Time to Enable Restore                                                       |     | 35           |     | v             | ns         |  |

| $	au_{ m RD}$     | Time to Disable Restore                                                      |     | 35           |     | v             | ns         |  |

Note 5: SR is measured at 20% to 80% of 4V pk-pk square wave, with  $A_V=$  5,  $R_F=$  820 $\Omega$ ,  $R_G=$  200 $\Omega$ .

Note 6: DC offset from -0.714 V to +0.714 V, AC amplitude is 286m Vp-p, equivalent to 40 ire.

Note 7: Test fixture was designed to minimize capacitance at the  $I_N-$  input. A "good" fixture should have less than 2 pF of stray capacitance to ground at this very sensitive pin. See application notes for further details.

### Triple 80 MHz Video Amplifier with DC Restore

Table 1. Charge Storage Capacitor Value vs. Droop and Charging Rates

| Cap Value (nF) | Droop in 60μS (mV) | Charge in 2μS (mV) | Charge in<br>4μS (mV) |

|----------------|--------------------|--------------------|-----------------------|

| 10             | 30                 | 400                | 800                   |

| 22             | 13.6               | 182                | 364                   |

| 47             | 6.4                | 85                 | 170                   |

| 100            | 3.0                | 40                 | 80                    |

| 220            | 1.36               | 18                 | 36                    |

These numbers represent the worst case bias current, and the worst case charging current. Note that to get the full (2mA+) charging current, the clamp input must have >250mV of error voltage.

Note that the magnitude of the bias current will decrease as temperature increases.

The basic droop formula is:

V (droop) =  $I_{B+}$   $\times$  (Line time — Charge time) / capacitor value

and the basic charging formula is:

$V (charge) = I_{OUT} \times Charge time / capacitor value$

Where  $I_{OUT}$  is:

$I_{OUT} = (Clamp \ voltage - IN + \ voltage) / 120$

#### **Applications Information**

#### **Circuit Operation**

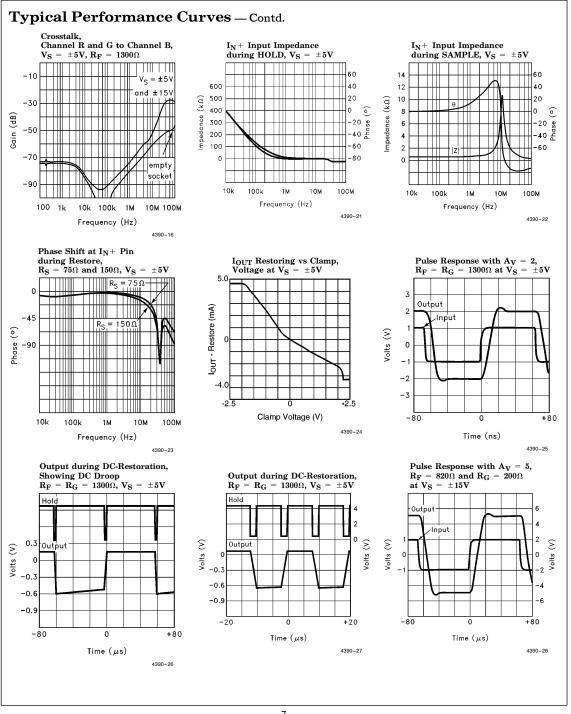

Each channel of the EL4390 contains a current feedback amplifier and a TTL/CMOS compatible clamp circuit. The current that the clamp can source or sink into the non-inverting input is approximately:

$$I = (V_{\text{CLAMP}} - V_{\text{IN}+}) / 120$$

So, when the non-inverting input is at the same voltage as the clamp reference, no current will flow, and hence no charge is added to the capacitor. When there is a difference in voltage, current will flow, in an attempt to cancel the error AT THE NON-INVERTING input. The amplifier's offset voltage and ( $I_{B-}\times R_{F}$ ) DC errors are not cancelled with this loop. It is purely a method of adding a controlled DC offset to the signal.

As well as the offset voltage error, which goes up with gain, and the  $I_{\rm B-} \times R_{\rm F}$  error which drops with gain, there is also the  $I_{\rm B+}$  error term. Since the amplifier is capacitively coupled, this small current is slowly integrated and shows up as a very slow ramp voltage. Table below shows the output voltage drift in  $60\mu S$  for various values of coupling capacitor, all assuming the very worst  $I_{\rm B+}$  current.

Table 1. Charge Storage Capacitor Value vs.

Droop and Charging Rates

| Cap Value<br>(nF) | Droop in 60μS (mV) | Charge in 2μS (mV) | Charge in 4μS (mV) |

|-------------------|--------------------|--------------------|--------------------|

| 10                | 30                 | 400                | 800                |

| 22                | 13.6               | 182                | 364                |

| 47                | 6.4                | 85                 | 170                |

| 100               | 3.0                | 40                 | 80                 |

| 220               | 1.36               | 18                 | 36                 |

In normal circuit operation, the picture content will also cause a slow change in voltage across the capacitor, so at every back porch time period, these error terms can be corrected.

When a signal source is being switched, eg. from two different surveillance cameras, it is recommended to synchronize the switching with the vertical blanking period, and to drive the HOLD pin (pin 6) low, during these lines. This will ensure that the system has been completely restored, regardless of the average intensity of the two pictures.

#### **Application Hints**

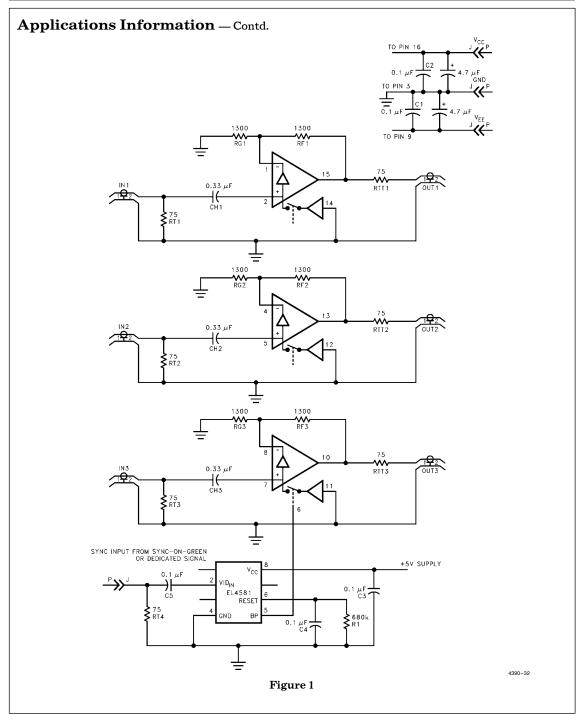

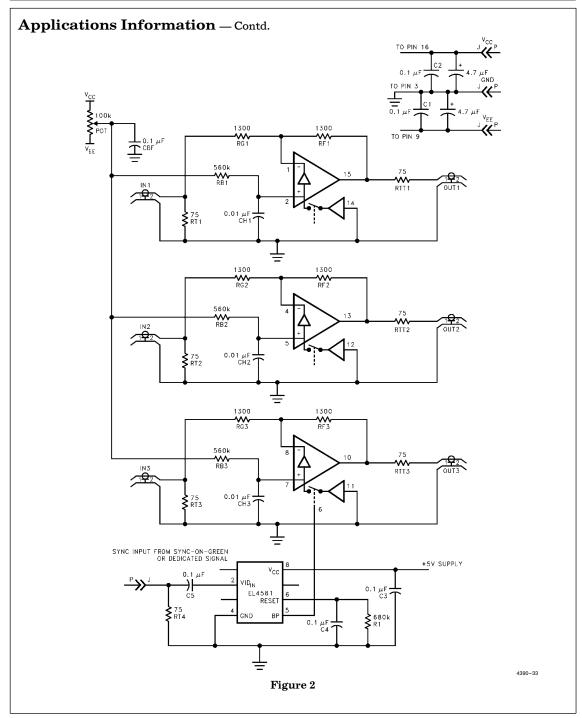

Figures 1 & 2 shows a three channel DC-restoring system, suitable for R-G-B or Y-U-V component video, or three synchronous composite signals.

Figure 1 shows the amplifiers configured for non-inverting gain, and Figure 2 shows the amplifiers configured for inverting gains. Note that since the DC-restoring function is accomplished by clamping the amplifier's non-inverting input, during the back porch period, any signal on the non-inverting input will be distorted. For this reason, it is recommended to use the inverting configuration for composite video, since this avoids the color burst being altered during the clamp time period.

Since all three amplifiers are monolithic, they run at the same temperature, and will have very similar input bias currents. This can be used to advantage, in situations where the droop voltage needs to be compensated, since a single trim circuit can be used for all three channels. A  $560 \text{K}\Omega$  or similar value resistor helps to isolate each signal. See Figure 2. The advantage of compensating for the droop voltage, is that a smaller capacitor can be used, which allows a larger level restoration within one line. See Table 1 for values of capacitor and charge/droop rates.

#### Applications Information — Contd.

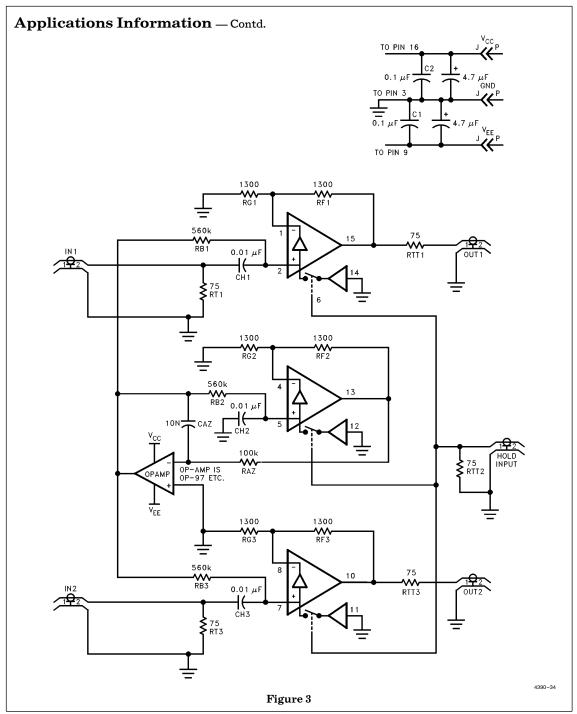

In Figure 3, one of the three channels is used, together with a low-offset op-amp, to automatically trim the bias current of the other two channels. The two remaining channels are shown in the non-inverting configuration, but could equally well be set to provide inverting gains. Two DC-restored channels are typically needed in fader applications. See the EL4094 and EL4095 for suitable, monolithic video faders.

#### Layout and Dissipation Considerations

As with all high frequency circuits, the supplies should be bypassed with a  $0.1\mu F$  ceramic capacitor very close to the supply pins, and a  $4.7\mu F$  tantalum capacitor fairly close, to handle the high current surges. While a ground plane is recommended, the amplifier will work well with a "star" grounding scheme. The pin 3 ground is only used for the internal bias generator and the reference for the TTL compatible "HOLD" input.

As with all current feedback capacitors, all stray capacitance to the inverting inputs should be kept as low as possible, to avoid unwanted peaking at the output. This is especially true if the value of Rf has already been reduced to raise the bandwidth of the part, while tolerating some peaking. In this situation, additional capacitance on the inverting input can lead to an unstable amplifier.

Since there are three amplifiers all in one package, and each amplifier can sink or source typically more than 70mA, some care is needed to avoid excessive die temperatures. Sustained, DC currents, of over 30mA, are not recommended, due to the limited current handling capability of the metal traces inside the IC. Also, the short circuit protection can be tripped with currents as low as 45mA, which is seen as excessive distortion in the output waveform. As a quick rule of thumb, both the SOL and DIP 16 pin packages can dissipate about 1.4 watts at 25°C, and with  $\pm$  15V supplies and a worst case quiescent current of 32mA, yields 0.96 watts, before any load is driven.

Dissipation of the EL4390 can be reduced by lowering the supply voltage. Although some performance is degraded at lower supplies, as seen in the characteristic curves, it is often found to be a useful compromise. The bandwidth can be recovered, by reducing the value of  $R_{\rm F}$ , and  $R_{\rm G}$  as appropriate.

### Triple 80 MHz Video Amplifier with DC Restore

#### General Disclaimer

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

Elantec, Inc. 1996 Tarob Court Milpitas, CA 95035

Telephone: (408) 945-1323

(800) 333-6314 Fax: (408) 945-9305

European Office: 44-71-482-4596

#### WARNING — Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. products in Life Support Systems are requested to contact Elantec, Inc. factory headquarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.

November 1994, Rev A

16 Printed in U.S.A.