### LM3553

# 1.2A Dual Flash LED Driver System with I<sup>2</sup>C Compatible Interface

### **General Description**

The LM3553 is a fixed frequency, current mode step-up DC/DC converter with two regulated current sinks. The device is capable of driving loads up to 1.2A from a single-cell Li-lon battery.

One or more high current flash LEDs can be driven in series either in a high power Flash mode or a lower power Torch mode controlled by either an internal register or the  $F_{\rm EN}$  pin. Additionally a low current (20mA) indicator mode and a fixed output voltage mode are also available.

The LM3553 has 128 current levels and 16 flash safety timer durations that are user adjustable via an I<sup>2</sup>C compatible interface. Internal soft-start eliminates large inrush currents at start-up. Over-voltage protection circuitry and 1.2MHz switching frequency allow for the use of small, low-cost output capacitors with lower voltage ratings.

The LM3553 includes a TX pin that forces Torch mode during a flash event allowing for synchronization between the RF power amplifier and Flash/Torch modes. It also includes a multi-function pin (M/F) that can serve as a GPIO and a hardware RESET pin.

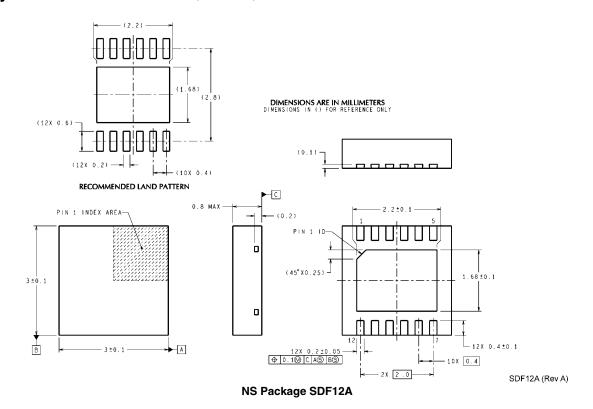

The LM3553 is available in National's 3mm by 3mm LLP12 package.

#### **Features**

- Accurate and Programmable LED Current up to 1.2A in 128 Steps

- Total Solution Size < 30mm²</p>

- 90% Peak Efficiency

- Drives 2 LEDs in Series with 1.2A from 5V Input

- Drives 2 LEDs in Series with 600mA from 3.0V Input

- Drives 1 LED with 1.2A from 3.0V Input

- Adjustable Over-Voltage Protection Allows for Single or Series LED Operation

- Four Operating Modes: Torch, Flash, Indicator, and Voltage Mode (4.98V)

- Programmable Flash Pulse Safety Timer in 16 Steps

- TX Input Ensures Synchronization with RF Power Amplifier Pulse or Prevents LED from Overheating

- LED Disconnect During Shutdown

- Flash/Imager Synchronization via F<sub>EN</sub> Pin

- Active Low Hardware Reset

- Multi-Function Pin (RESET and GPIO)

- Low Profile 12-pin LLP Package (SDF12A: 3mm x 3mm x 0.8mm, 0.4mm pitch)

### **Applications**

- Camera Phone LED Flash

- Smartphone and PDA Flash

- LED Backlight

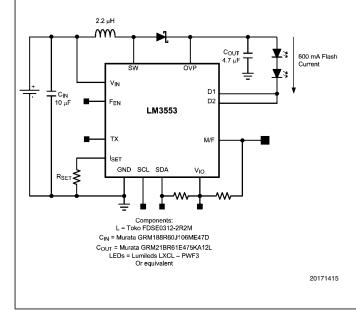

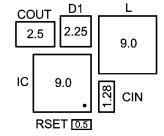

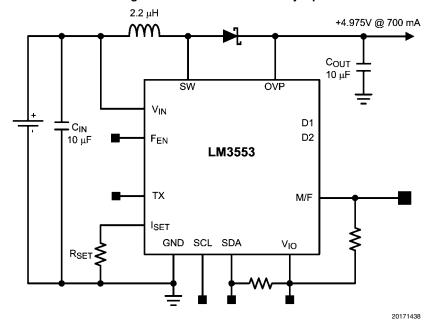

### **Typical Application Circuits**

29.25mm<sup>2</sup> with 0.4mm spacing around large components (IC and L)

**Solution Size**

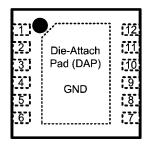

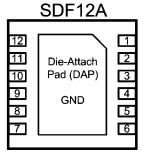

### **Connection Diagram**

# 12 Pin 3mm x 3mm LLP Package

Top View

**Bottom View**

Package Marking Top View

**Note:** The actual physical placement of the package marking will vary from part to part. The package marking "XXX" designates the date code. "YY" is a NSC internal code for die traceability. Both will vary considerably. "LM3553" identifies the device (part number, option, etc.).

20171416

### **Pin Descriptions**

| Pin   | Name             | Function                                                                                       |

|-------|------------------|------------------------------------------------------------------------------------------------|

| 4     | V <sub>IN</sub>  | Input Voltage. Input range: 2.7V to 5.5V.                                                      |

| 5     | SW               | Switch Pin                                                                                     |

| 6     | OVP              | Over Voltage Protection Pin                                                                    |

| 2, 11 | D1, D2           | Regulated current sink inputs                                                                  |

| DAP   | GND              | Ground                                                                                         |

| 1     | I <sub>SET</sub> | Current sense input. Connect a 1% 16.5kΩ resistor to ground to set the full scale LED current. |

| 3     | F <sub>EN</sub>  | Flash enable pin.                                                                              |

| 8     | SCL              | Serial clock pin.                                                                              |

| 10    | SDA              | Serial data I/O pin.                                                                           |

| 9     | VIO              | Digital Reference Voltage level input pin.                                                     |

| 7     | TX               | RF PA synchronization control pin. High = Forced Torch mode.                                   |

| 12    | M/F              | Hardware RESET or General purpose I/O. Function set through Multi-Function Control Register    |

### **Ordering Information**

| Order Number   | Туре                         | Package | Package Marking | Supplied As               |

|----------------|------------------------------|---------|-----------------|---------------------------|

| LM3553SD-NOPB  | No Lead, Non-<br>Halogenated | SDF12A  | L3553           | 1000 units, Tape-and-Reel |

| LM3553SDX-NOPB | No Lead, Non-<br>Halogenated | SDF12A  | L3553           | 4500 units, Tape-and-Reel |

| LM3553SD-HALF  | No Lead,<br>Halogenated      | SDF12A  | L3553           | 1000 units, Tape-and-Reel |

| LM3553SDX-HALF | No Lead,<br>Halogenated      | SDF12A  | L3553           | 4500 units, Tape-and-Reel |

#### **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{\rm IN}$  pin: Voltage to GND -0.3V to 6V SW, OVP pin: Voltage to GND -0.3V to 25V D1, D2 pins: Voltage to GND -0.3V to 25V VIO, SCL, SDA -0.3V to 6V TX, FEN, M/F -0.3V to 6V Continuous Power Dissipation (Note 3) Internally Limited

Junction Temperature (T<sub>J-MAX</sub>) 150°C Storage Temperature Range -65°C to +150

Maximum Lead Temperature

(Soldering) (Note 4)

ESD Rating(Note 5)

Human Body Model 2.5kV

### Operating Ratings (Notes 1, 2)

Input Voltage Range 2.7V to 5.5V Junction Temperature (T<sub>.I</sub>) -30°C to +125°C Range

Ambient Temperature (T<sub>A</sub>) -30°C to +85°C

Range (Note 6)

### Thermal Properties

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ), SDF12A

Package(Note 7) 36.7°C/W

**ESD Caution Notice** National Semiconductor recommends that all integrated circuits be handled with appropriate ESD precautions. Failure to observe proper ESD handling techniques can result in damage to the device.

#### **Electrical Characteristics**

Limits in standard typeface are for  $T_A = +25$ °C. Limits in boldface type apply over the full operating junction temperature range  $(-30^{\circ}\text{C} \le \text{T}_{\text{J}} \le +125^{\circ}\text{C}). \text{ Unless otherwise noted: } V_{\text{IN}} = 3.6\text{V}, \text{ R}_{\text{SET}} = 16.5\text{k}\Omega, \text{ V}_{\text{D1}} = \text{V}_{\text{D2}} = 500\text{mV}, \text{ VFB bit = '0'}, \text{ FEN = '0'}, \text{ TX = '0'},$ Flash Current Level = Full-Scale. (Notes 2, 8, 9)

| Symbol                                               | Parameter                                 | arameter Conditions                                     |                          | Тур   | Max   | Units |  |

|------------------------------------------------------|-------------------------------------------|---------------------------------------------------------|--------------------------|-------|-------|-------|--|

|                                                      | Floch I ED Current                        | Flash Mode<br>VDX = Regulation Voltage                  | 930                      | 1020  | 1110  |       |  |

| $I_{LED-SUM}$   Flash LED Current: $I_{D1} + I_{D2}$ |                                           | Flash Mode<br>VDX = Regulation Voltage<br>RSET = 13.7kΩ | VDX = Regulation Voltage |       |       | mA    |  |

| I <sub>LED-IND</sub>                                 | Indicator Current Level                   | Indicator Mode                                          |                          | 20    |       | mA    |  |

| VM <sub>REG</sub>                                    | Output Voltage Regulation in Voltage Mode | VM = '1', EN1 = EN0 = '0'<br>No Load                    | 4.65                     | 4.98  | 5.30  | V     |  |

| I <sub>Q</sub>                                       | Quiescent Supply Current                  | V <sub>D1,D2</sub> = 0V<br>(Switching)                  |                          | 1.0   | 1.2   | mA    |  |

| I <sub>SD</sub>                                      | Shutdown Supply Current                   | Device Disabled                                         |                          | 3.8   | 6.0   | μA    |  |

| I <sub>Dx</sub> / I <sub>SET</sub>                   | LED Current to Set Current<br>Ratio       | I <sub>Dx</sub> = 500mA                                 |                          | 6770  |       | A / A |  |

| V <sub>SET</sub>                                     | I <sub>SET</sub> Pin Voltage              |                                                         |                          | 1.24  |       | V     |  |

| \/                                                   | Current Sink Regulation                   | VFB Bit = '0'                                           |                          | 450   | 50    |       |  |

| $V_{D1,D2}$                                          | Voltage                                   | VFB Bit = '1'                                           |                          | 350   |       | mV    |  |

| I <sub>Dx-MATCH</sub>                                | Current Sink Matching                     | VDX = Regulation Voltage                                |                          | 2     |       | %     |  |

| R <sub>DSON</sub>                                    | NMOS Switch Resistance                    |                                                         |                          | 0.25  |       | Ω     |  |

|                                                      | NMOS Switch Current Limit                 | OCL Bit = '0'                                           | 2.2                      | 2.5   | 2.8   | Α     |  |

| I <sub>CL</sub>                                      | NWOS SWIICH CUITERII LIIIIII              | OCL Bit = '1'                                           | 1.53                     | 1.70  | 1.87  | ] ^   |  |

| I <sub>L-SW</sub>                                    | SW Pin Leakage Current                    | Switch Off, V <sub>SW</sub> =3.6V, OVP<br>Mode = '0'    |                          | 10    |       | nA    |  |

| I <sub>L-Dx</sub>                                    | D1, D2 Pin Leakage                        | VDx = 3.5V                                              |                          | 10    |       | nA    |  |

|                                                      | Output Over-Voltage                       | OVP Mode = '1'                                          | 18.00                    | 18.90 | 19.65 | .,    |  |

| $V_{OVP}$                                            | Protection Trip Point                     | OVP Mode = '0'                                          | 5.4                      | 5.6   | 5.85  | V     |  |

|                                                      | Over-Voltage Protection                   | OVP Mode = '1'                                          |                          | 1.6   |       |       |  |

| OVP <sub>Hyst</sub>                                  | Hysteresis OVP to Normal Operation        | OVP Mode = '0'                                          |                          | 0.6   |       | V     |  |

| I <sub>L-OVP</sub>                                   | OVP Pin Leakage Current                   | V <sub>OVP</sub> =3.6V                                  |                          | 10    |       | nA    |  |

| Symbol                 | Parameter                                   | Conditions                              | Min        | Тур  | Max       | Units |

|------------------------|---------------------------------------------|-----------------------------------------|------------|------|-----------|-------|

| f <sub>SW</sub>        | Switching Frequency                         |                                         | 1.0        | 1.2  | 1.35      | MHz   |

| t <sub>FD-MIN</sub>    | Minimum Flash Duration Step                 | $t_{FD-MIN} = 16 \div f_{SW}$           |            | 12.8 |           | µsec. |

| D <sub>MAX</sub>       | Maximum Duty Cycle                          |                                         |            | 92   |           | %     |

| D <sub>MIN</sub>       | Minimum Duty Cycle                          |                                         |            | 6    |           | %     |

|                        | TX, F <sub>FN</sub> Pin Threshold           | On                                      | 1.0        |      | VIN       | V     |

| Th <sub>TX,F-EN</sub>  | TA, FEN FIII THIESHOID                      | Off                                     | 0          |      | 0.6       | V     |

| Multi-Func             | tion Pin (M/F) Voltage Specific             | ations                                  |            |      |           |       |

| V                      | Multi-Function Pin Threshold                | Input Logic High "1"                    | 0.94       |      | VIN       | V     |

| V <sub>M/F</sub>       | Voltages                                    | Input Logic Low "0"                     | 0          |      | 0.64      |       |

| V <sub>OL</sub>        | Output Logic Low "0"                        | I <sub>LOAD</sub> = 4.2mA,<br>GPIO Mode |            |      | 400       | mV    |

| I <sup>2</sup> C Compa | tible Voltage Specifications (S             | CL, SDIO, VIO)                          | •          |      | '         |       |

| VIO                    | Serial Bus Voltage Level                    |                                         | 1.45       |      | VIN       | V     |

| V <sub>IL</sub>        | Input Logic Low "0"                         | VIO = 3.0V                              | 0          |      | 0.38 ×VIO | V     |

| V <sub>IH</sub>        | Input Logic High "1"                        | VIO = 3.0V                              | 0.55 × VIO |      | VIO       | V     |

| V <sub>OL</sub>        | Output Logic Low "0"                        | $I_{LOAD} = 3.7 \text{mA}$              |            |      | 400       | mV    |

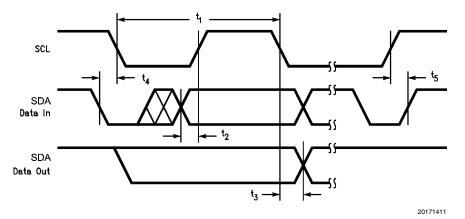

| I <sup>2</sup> C Compa | tible Interface Timing Specifica            | ations (SCL, SDIO, VIO)                 |            |      |           |       |

|                        | COL (Ola ala Dania al)                      |                                         | 0.5        |      |           |       |

| t <sub>1</sub>         | SCL (Clock Period)                          |                                         | 2.5        |      |           | μs    |

| t <sub>2</sub>         | Data In Setup Time to SCL<br>High           |                                         | 100        |      |           | ns    |

| t <sub>3</sub>         | Data Out stable After SCL Low               |                                         | 0          |      |           | ns    |

| t <sub>4</sub>         | SDA Low Setup Time to SCL<br>Low (Start)    |                                         | 100        |      |           | ns    |

| t <sub>5</sub>         | SDA High Hold Time After SCL<br>High (Stop) |                                         | 100        |      |           | ns    |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: Internal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J$ =140°C (typ.) and disengages at  $T_J$ =120°C (typ.).

Note 4: For detailed soldering specifications and information, please refer to National Semiconductor Application Note: AN-1187 for Recommended Soldering Profiles

$\textbf{Note 5:} \ \ \textbf{The human body model is a 100pF capacitor discharged through a 1.5k} \\ \Omega \ \ \textbf{resistor into each pin. (MIL-STD-883 3015.7)} \\$

Note 6: In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A-MAX})$  is dependent on the maximum operating junction temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power dissipation of the device in the application  $(P_{D-MAX})$ , and the junction-to-ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 7: Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

| Note 8: Min and Max limits are guaranteed by design, test, or statistical analysis. Typical (Typ) numbers are not guaranteed, but do represent the most likely norm. Unless otherwise specified, conditions for Typ specifications are: V <sub>IN</sub> = 3.6V and T <sub>A</sub> = 25°C.  Note 9: All testing for the LM3553 is done open-loop. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                  |

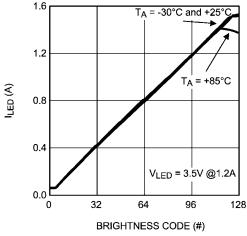

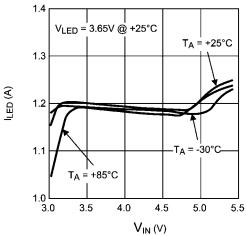

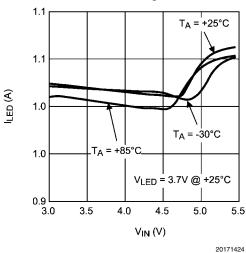

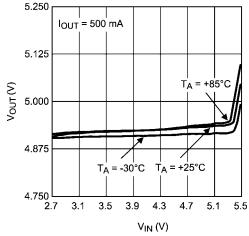

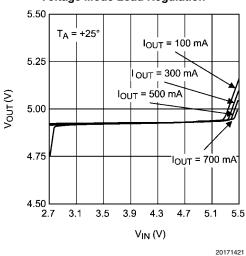

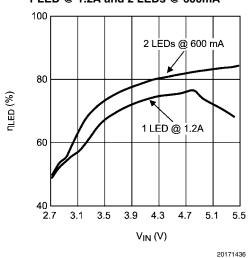

**Typical Performance Characteristics** Unless otherwise specified:  $T_A = 25^{\circ}\text{C}$ ;  $V_{\text{IN}} = 3.6\text{V}$ ;  $V_{\text{M/F}} = V_{\text{IN}}$ ;  $R_{\text{SET}} = 16.5\text{k}\Omega$ ;  $C_{\text{IN}} = 10\mu\text{F}$ ,  $C_{\text{OUT}} = 10\mu\text{F}$ ;  $L = 2.2\mu\text{H}$ ; VFB bit = CL bit = '0'; OVP bit = '0' for 1 LED and VFB = '1' for two series LEDs;.

20171422

6

### 1.2A Flash Line Regulation

20171423

#### 1.0A Flash Line Regulation

**Voltage Mode Line Regulation**

20171420

#### **Voltage Mode Load Regulation**

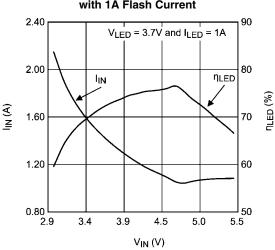

Input Current and LED Efficiency with 1A Flash Current

20171429

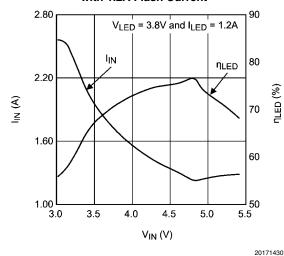

# Input Current and LED Efficiency with 1.2A Flash Current

# Input Current and LED Efficiency with 500mA Flash Current through 2 Series LEDs

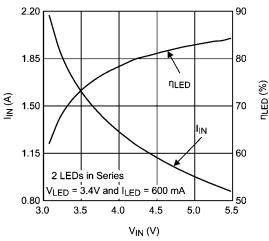

20171432

# Input Current and LED Efficiency with 600mA Flash Current through 2 Series LEDs

20171431

7

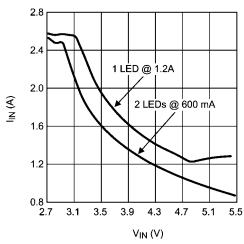

#### Input Current vs V<sub>IN</sub> 1 LED @ 1.2A and 2 LEDs @ 600mA

20171435

#### LED Efficiency vs V<sub>IN</sub> 1 LED @ 1.2A and 2 LEDs @ 600mA

Converter Efficiency vs VIN 100 Voltage Mode with  $I_{OUT}$  = 500 mA 90 1CONVERTER (%) 80 2 LEDs @ 500 mA with  $V_{LED}(total) = 6.725V$ 70 60 1 LED @ 1A with  $V_{LED} = 3.7V$ 50 3.1 3.5 4.3 4.7 3.9 5.1 VIN (V)

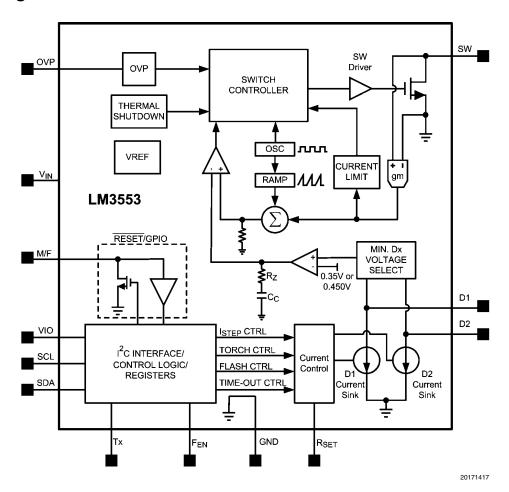

### **Block Diagram**

### **Circuit Description**

#### **CIRCUIT COMPONENTS**

#### F<sub>FN</sub> Pin

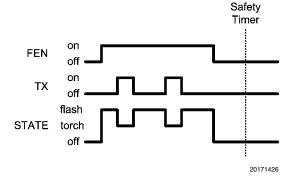

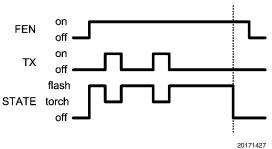

The flash enable pin,  $F_{EN}$ , provides an external method (non-I²C) for starting the flash pulse. When  $F_{EN}$  is pulled high, logic '1', the flash current level defined through the I2C interface, will be delived to the Flash LED. If the  $F_{EN}$  pin is driven low during the flash pulse, the flash event will stop. In the event that  $F_{EN}$  is not pulled low during the flash pulse, the LM3553 will continue to deliver the flash current until the safety timer duration (set through the I2C interface) is reached.

The LM3553 does not provide a fixed off-time after the flash pulse has ended. Most flash LED manufacturers require that the flash pulse duration be 10% of the total Flash cycle. Example: If the flash pulse duration is set to be 200 milliseconds (Flash Duration Code= 0011), the recommended off time for the LED would be 1.8 seconds. Please consult the LED manufacturers datasheet for exact timing requirements.

If the LM3553 is placed in indicator mode or torch mode through the I $^2$ C interface and the F $_{EN}$  pin is pulled high and then low, at the end of the flash event, the LM3553 will return to the mode stored in the General Purpose Register.

It is recommended that an external pull-down be placed between the  $F_{\rm EN}$  pin and GND to prevent unwanted LED flashing during system start-up due to unknown control logic states.

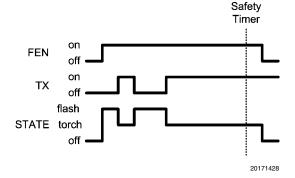

#### T<sub>X</sub> Pin

The transmission pin  $(T_X)$  can be used to limit the current drawn from the battery during a PA transmission. When the  $T_X$  pin is driven high (logic '1') during a flash pulse, the LM3553 will switch to the programmed torch current level. Once the  $T_X$  pin is driven low (logic '0'), the LM3553 will return to the flash current if this event occurs within the original flash duration.

It is recommended that an external pull-down be placed between the  $T_{\chi}$  pin and GND to prevent unwanted LED flashing during system start-up due to unknown control logic states.

#### M/F Pin

The multi-function pin (M/F) can be configured to provide hardware RESET or a general purpose input/output (GPIO). All functionality is programmed through the I<sup>2</sup>C compatible interface and set in the M/F pin functionality control register (address 0x20). The default function is a RESET, where a logic '1' places the part in the normal operating mode, and a logic '0' places the part into a RESET state. A reset condition will place all LM3553 registers into their default states.

#### **Connection Diagram**

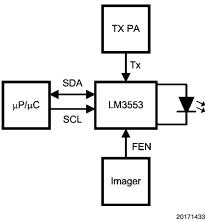

#### **Typical System Configuration**

#### I<sup>2</sup>C Compatible Interface

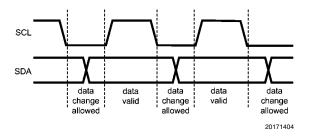

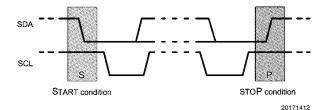

#### **DATA VALIDITY**

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, the state of the data line can only be changed when CLK is LOW.

FIGURE 1. Data Validity Diagram

A pull-up resistor between VIO and SDA must be greater than [ (VIO-V $_{

m OL}$ ) / 3.7mA] to meet the V $_{

m OL}$  requirement on SDA. Using a larger pull-up resistor results in lower switching current with slower edges, while using a smaller pull-up results in higher switching currents with faster edges.

#### START AND STOP CONDITIONS

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session. A START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I<sup>2</sup>C bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise. The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, the state of the data line can only be changed when CLK is LOW.

FIGURE 2. Start and Stop Conditions

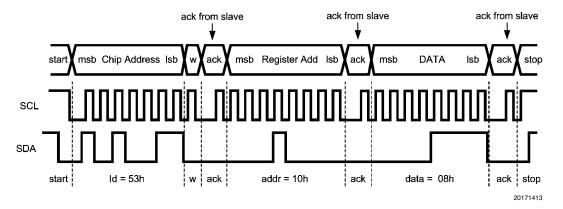

#### TRANSFERRING DATA

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock pulse. The LM3553 pulls down the SDA line during the 9th clock pulse, signifying an acknowledge. The LM3553 generates an acknowledge after each byte has been received.

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM3553 address is 53h. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

FIGURE 3. Write Cycle

w = write (SDA = "0")

ack = acknowledge (SDA pulled down by the slave)

id = chip address, 53h for LM3553

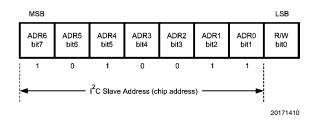

#### I<sup>2</sup>C COMPATIBLE CHIP ADDRESS

The chip address for LM3553 is 1010011, or 53hex.

FIGURE 4.

#### **INTERNAL REGISTERS OF LM3553**

| Register                               | Internal Hex<br>Address | Power On<br>Value |

|----------------------------------------|-------------------------|-------------------|

| General Purpose Register               | 0x10                    | 0001 1000         |

| Multi-Function Pin Control<br>Register | 0x20                    | 1110 0000         |

| Current Step Time<br>Register          | 0x50                    | 1111 1100         |

| Torch Current Control<br>Register      | 0xA0                    | 1000 0000         |

| Flash Current Control<br>Register      | 0xB0                    | 1000 0000         |

| Flash Duration Control<br>Register     | 0xC0                    | 1111 0000         |

#### **General Purpose Register**

| MSB  | General Purpose Control<br>Register Address: 0x10 LSB |      |      |      |      |      |      |

|------|-------------------------------------------------------|------|------|------|------|------|------|

| 0    | 0                                                     | VFB  | 1    | 1    | VM   | EN1  | EN0  |

| bit7 | bit6                                                  | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

20171405

FIGURE 5.

EN0-EN1: Set Flash LED mode

Indicator Mode sets  $I_{LED}$  = 20mA. In this mode, D1 is enabled and D2 is disabled.

VM: Enables Voltage Mode. Current sinks D1 and D2 are turned off and the LM3553 will operate in a regulated voltage boost mode. Setting the VM bit to a '1' does not override the EN0 and EN1 bits stored in the general purpose register. The default setting is '0'. If the LM3553 is in Voltage Mode and an indicator, torch or flash command is issued, the LM3553 will turn on the D1 and D2 current sources and begin regulating the output voltage to a value equal to VFB (350mV or 450mV) + VLED.

| VM | EN1 | EN0 | Function       |

|----|-----|-----|----------------|

| 0  | 0   | 0   | Shutdown       |

| 0  | 0   | 1   | Indicator Mode |

| 0  | 1   | 0   | Torch Mode     |

| 0  | 1   | 1   | Flash Mode     |

| 1  | 0   | 0   | Voltage Mode   |

| 1  | 0   | 1   | Indicator Mode |

| 1  | 1   | 0   | Torch Mode     |

| 1  | 1   | 1   | Flash Mode     |

**VFB**: Selects the regulation voltage for the LM3553. Setting this VFB bit to a '0' sets the regulation voltage to 450mV while setting the VFB bit to a '1' sets the regulation voltage to 350mV. Setting the VFB bit to a '1' during torch mode and/or lower current flash modes ( $I_{LED}$  < 1A) will help improve the LED efficiency of the LM3553.

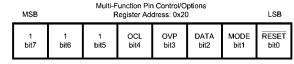

#### M/F Pin Control Register

20171409

#### FIGURE 6.

**RESET**: Enables M/F as hardware RESET. '0' = Hardware RESET, .'1' = GPIO or current sink depending on the MODE bit. Default = '0'

**MODE**: Sets M/F mode. Default for M0DE = '0'. '0' = GPI, and '1' = GPO

Note: When M/F is configured as an input, data is transfered from GPI to DATA whenever an I<sup>2</sup>C write command is issued to the LM3553. When configuring M/F as a GPO, the first write needs to take the LM3553 out of RESET mode and a second write can then set the pin to the GPO.

**DATA**: GPIO Data. When the M/F is configured as an output (GPO), DATA sets the GPO level. Example: DATA = '1', M/F is set high or logic '1'. When the M/F pin is configured as an input (GPI), DATA stores the GPI level. Example: M/F = '1', DATA will be set to a '1'. Default for DATA = '0'.

**OVP**: Enables high-voltage OVP (OVP Bit ='1') or low-voltage OVP (OVP Bit ='0'). Default = low-voltage mode '0'

**OCL**: SW Pin Current Limit Selector Bit: If OCL = '0', the inductor current limit is 2.5A typ. If OCL = '1', the inductor current limit is 1.7A typ.

M/F Functionality Configuration Table

| RESET | MODE | M/F Function |

|-------|------|--------------|

| 0     | Х    | RESET        |

| 1     | 0    | GPI          |

| 1     | 1    | GPO          |

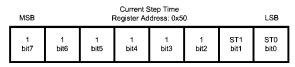

#### **Current Step Time Register**

20171418

#### FIGURE 7.

**ST1-ST0**: Sets current level stepping time for D1 and D2 during the beginning and end of the flash or torch current waveform. '00' =  $25\mu s$ , '01' =  $50\mu s$ , '10' =  $100\mu s$ , '11' =  $200\mu s$ .

The current ramp-up/ramp-down times can be approximated by the following equation:

$T_{RAMPUP/RAMPDOWN} = (N_{FLASH} - N_{START} + 1) \times t_{STEP}$  where N is equal to the decimal value of the brightness level (0  $\leq$   $N_{FLASH} \leq$  127 and 0  $\leq$   $N_{START} \leq$  31).  $N_{START} = N_{TORCH}$  if Torch is enabled before going into a flash. If going straight into a flash from an off-state,  $N_{START} = 0$

#### **Torch Current Control Register**

MSB

TORCH Current Control Register Address: 0xA0

LSB

1

0

0

TC4

TC3

TC2

TC1

TC0

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

20171406

#### FIGURE 8.

**TC6-TC0**: Sets Torch current level for D1 and D2. xxx1 1111 = Fullscale

#### Flash Current Control Register

FIGURE 9.

**FC6-FC0**: Sets Flash current level for D1 and D2. x111 1111 = Fullscale

#### **Current Level Equation**

The Full-Scale Flash Current Level is set through the use of an external resistor ( $R_{\text{SET}}$ ) connected to the  $I_{\text{SET}}$  pin. The  $R_{\text{SET}}$  selection equation can be used to set the current through each of the two current sinks, D1 and D2.

$R_{SET} = 6770 \times 1.24V \div I_{Dx}$

#### **R<sub>SET</sub> Selection Table**

| I <sub>Flash</sub> = ID1 + ID2 | R <sub>SET</sub> |

|--------------------------------|------------------|

| 500mA                          | 33.6kΩ           |

| 600mA                          | 28kΩ             |

| 1A                             | 16.8kΩ           |

| 1.2A                           | 14kΩ             |

The current through each current sink, D1 and D2, can be approximated by the following equation using the values stored in either the Torch or Flash Current Control registers.

#### I<sub>FLASH</sub>≊ (N + 1) × I<sub>LED TOTAL</sub> ÷ 128

where N is the decimal equivalent number ( $0 \le N \le 127$  for Flash and  $0 \le N \le 31$  for Torch) stored in the Torch or Flash Current control registers and  $I_{LED\_TOTAL} = I_{D1} + I_{D2}$  @ Full-scale. Brightness codes 0 through 4 are repeated and each sets the total LED current to approximately 40mA.

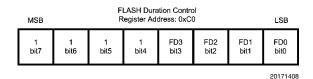

#### Flash Safety Timer Control Register

FIGURE 10.

**FD3-FD0**: Sets Flash Duration for D1 and D2. 1111 = Fullscale

| Sa | fety Timer Duration<br>Code (Binary) | Typical Safety Timer  Duration |

|----|--------------------------------------|--------------------------------|

|    |                                      | (milliseconds)                 |

|    | 0000                                 | 50                             |

|    | 0001                                 | 100                            |

|    | 0010                                 | 200                            |

|    | 0011                                 | 300                            |

|    | 0100                                 | 400                            |

|    | 0101                                 | 500                            |

|    | 0110                                 | 600                            |

|    | 0111                                 | 700                            |

|    | 1000                                 | 800                            |

|    | 1001                                 | 900                            |

|    | 1010                                 | 1000                           |

|    | 1011                                 | 1100                           |

|    | 1100                                 | 1200                           |

|    | 1101                                 | 1300                           |

|    | 1110                                 | 1400                           |

|    | 1111                                 | 3200                           |

#### LM3553 Functionality Truth Table

| EN1 | EN0 | F <sub>EN</sub> | T <sub>X</sub> | Result    |  |  |  |  |

|-----|-----|-----------------|----------------|-----------|--|--|--|--|

| 0   | 0   | 0               | 0              | Shutdown  |  |  |  |  |

| 0   | 0   | 0               | 1              | Shutdown  |  |  |  |  |

| 0   | 0   | 1               | 0              | Flash     |  |  |  |  |

| 0   | 0   | 1               | 1              | Torch     |  |  |  |  |

| 0   | 1   | 0               | 0              | Indicator |  |  |  |  |

| 0   | 1   | 0               | 1              | Indicator |  |  |  |  |

| 0   | 1   | 1               | 0              | Flash     |  |  |  |  |

| 0   | 1   | 1               | 1              | Torch     |  |  |  |  |

| 1   | 0   | 0               | 0              | Torch     |  |  |  |  |

| 1   | 0   | 0               | 1              | Torch     |  |  |  |  |

| 1   | 0   | 1               | 0              | Flash     |  |  |  |  |

| 1   | 0   | 1               | 1              | Torch     |  |  |  |  |

| 1   | 1   | 0               | 0              | Flash     |  |  |  |  |

| 1   | 1   | 0               | 1              | Torch     |  |  |  |  |

| 1   | 1   | 1               | 0              | Flash     |  |  |  |  |

| 1   | 1   | 1               | 1              | Torch     |  |  |  |  |

### **FEN Terminated Pulse**

### **Application Information**

#### **INDUCTOR SELECTION**

The LM3553 is designed to use a 2.2 $\mu$ H inductor. When the device is boosting ( $V_{OUT} > V_{IN}$ ) the inductor is one of the biggest sources of efficiency loss in the circuit. Therefore, choosing an inductor with the lowest possible series resistance is important. Additionally, the saturation rating of the inductor should be greater than the maximum operating peak current of the LM3553. This prevents excess efficiency loss that can occur with inductors that operate in saturation and prevents over heating of the inductor and possible damage. For proper inductor operation and circuit performance ensure that the inductor saturation and the peak current limit setting of the LM3553 (2.6A or 1.8A) is greater than  $I_{PEAK}$ .  $I_{PEAK}$  can be calculated by:

$$I_{\text{PEAK}} = \frac{I_{\text{LOAD}}}{\eta} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} + \Delta I_{\text{L}}$$

where

$$\Delta I_{L} = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{2 \times f_{SW} \times L \times V_{OUT}}$$

#### **Recommended Inductors**

| Manufacturer | Part#             | L/I <sub>SAT</sub> |

|--------------|-------------------|--------------------|

| Toko         | FDSE312-2R2M      | 2.2µH / 2.3A       |

| Coilcraft    | LPS4012-222ML     | 2.2µH / 2.3A       |

| TDK          | VLF4014ST-2R2M1R9 | 2.2µH / 2.0A       |

#### **CAPACITOR SELECTION**

The LM3553 requires 2 external capacitors for proper operation ( $C_{\text{IN}} = 10 \mu \text{F}$  recommended (4.7  $\mu \text{F}$  min.) and  $C_{\text{OUT}} = 10 \mu \text{F}$  (single LED) or 4.7  $\mu \text{F}$  (series LEDs)). Surface-mount multilayer ceramic capacitors are recommended. These capacitors are small, inexpensive and have very low equivalent series resistance (ESR <20 m $\Omega$  typ.). Tantalum capacitors, OS-CON capacitors, and aluminum electrolytic capacitors are not recommended for use with the LM3553 due to their high ESR, as compared to ceramic capacitors.

For most applications, ceramic capacitors with X7R or X5R temperature characteristic are preferred for use with the LM3553. These capacitors have tight capacitance tolerance (as good as  $\pm 10\%$ ) and hold their value over temperature (X7R:  $\pm 15\%$  over -55°C to 125°C; X5R:  $\pm 15\%$  over -55°C to 85°C).

Capacitors with Y5V or Z5U temperature characteristic are generally not recommended for use with the LM3553. Capacitors with these temperature characteristics typically have wide capacitance tolerance (+80%, -20%) and vary significantly over temperature (Y5V: +22%, -82% over -30°C to +85°C range; Z5U: +22%, -56% over +10°C to +85°C range). Under some conditions, a nominal 1 $\mu$ F Y5V or Z5U capacitor could have a capacitance of only 0.1 $\mu$ F. Such detrimental deviation is likely to cause Y5V and Z5U capacitors to fail to meet the minimum capacitance requirements of the LM3553.

The recommended voltage rating for the input capacitor is 10V (min = 6.3V). For a single flash LED, the recommended output capacitor voltage rating is 10V (min = 6.3V), and for series LEDs the recommended voltage is 25V (min = closest voltage rating above the sum of ( $V_{LED} \times N_{LEDs}$ ) and  $V_{FB}$ ). The recommended value takes into account the DC bias capacitance losses, while the minimum rating takes into account the OVP trip levels.

#### SCHOTTKY DIODE SELECTION

The output diode must have a reverse breakdown voltage greater than the maximum output voltage. The diodes average current rating should be high enough to handle the LM3553's output current. Additionally, the diodes peak current rating must be high enough to handle the peak inductor current. Schottky diodes are recommended due to their lower forward voltage drop (0.3V to 0.5V) compared to (0.8V) for PN junction diodes.

#### LAYOUT CONSIDERATIONS

The LLP is a leadless package with very good thermal properties. This package has an exposed DAP (die attach pad) at the underside center of the package measuring 1.86mm x 2.2mm. The main advantage of this exposed DAP is to offer low thermal resistance when soldered to the thermal ground pad on the PCB. For good PCB layout a 1:1 ratio between the package and the PCB thermal land is recommended. To further enhance thermal conductivity, the PCB thermal ground pad may include vias to a 2nd layer ground plane. For more detailed instructions on mounting LLP packages, please refer to National Semiconductor Application Note AN-1187.

The high switching frequencies and large peak currents make the PCB layout a critical part of the design. The proceeding steps must be followed to ensure stable operation and proper current source regulation.

If possible, divide ground into two planes, one for the return terminals of C<sub>OUT</sub>, C<sub>IN</sub> and the I<sup>2</sup>C Bus, the other for the return terminals of R<sub>SET</sub>. Connect both planes to the exposed DAP, but nowhere else.

- Connect the inductor and the anode of D1(schottky) as close together as possible and place this connection as close as possible to the SW pin. This reduces the inductance and resistance of the switching node which minimizes ringing and excess voltage drops.

- Connect the return terminals of the input capacitor and the output capacitor as close as possible to the exposed DAP and through low impedance traces.

- 4. Bypass  $V_{\rm IN}$  with at least a 4.7 $\mu$ F ceramic capacitor. Connect the positive terminal of this capacitor as close as possible to  $V_{\rm IN}$ .

- Connect C<sub>OUT</sub> as close as possible to the cathode of D1 (schottky). This reduces the inductance and resistance of the output bypass node which minimizes ringing and voltage drops. This will improve efficiency and decrease the noiseinjected into the current sources.

- Route the trace for R<sub>SET</sub> away from the SW node to minimize noise injection.

- 7. Do not connect any external capacitor to the R<sub>SET</sub> pin.

#### THERMAL PROTECTION

Internal thermal protection circuitry disables the LM3553 when the junction temperature exceeds 150°C (typ.). This feature protects the device from being damaged by high die temperatures that might otherwise result from excessive power dissipation. The device will recover and operate normally when the junction temperature falls below 140°C (typ.). It is important that the board layout provide good thermal conduction to keep the junction temperature within the specified operating ratings.

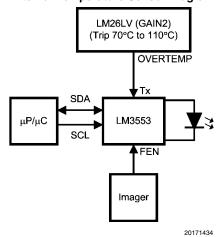

#### **External Temperature Sensor Diagram**

Using an external temperature sensor, such as the LM26LV, can help aid in the thermal protection of the flash LEDs as well as other components in a design. Connecting the OVERTEMP pin of the LM26LV to the TX pin on the LM3553 prevents the high current flash from turning on when the set temperature threshold on the LM26LV is reached. When the temperature trip point is reached, the OVERTEMP pin on the LM26LV will transition from a '0' to a '1' which in turn enables the LM3553's TX mode. When a flash is instantiated by either the imager or microprocessor, the LM3553 will only allow the flash LED current to reach the current level set in the Torch Current register as long as the temperature sensor is registering an over-temperature condition. Placing the temperature sensor close to the flash LEDs can help prevent the LEDs from reaching a temperature above the maximum specified limit due to high-current flashing in a high temperature ambient environment.

#### **LM3553 CONFIGURATIONS**

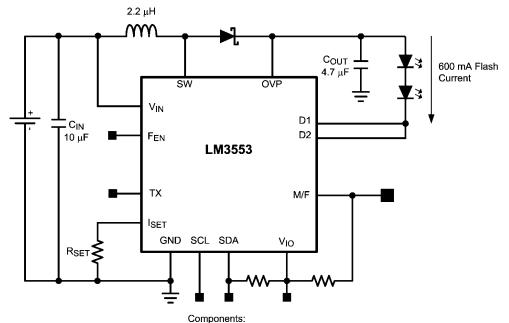

#### 2 LEDs @ 600mA with Battery Input

Components: L = Toko FDSE0312-2R2M C<sub>IN</sub> = Murata GRM188R60J106ME47D C<sub>OUT</sub> = Murata GRM21BR61E475KA12L

COUT = MURATA GRM21BR61E475RA12 LEDs = Lumileds LXCL – PWF3 Or equivalent

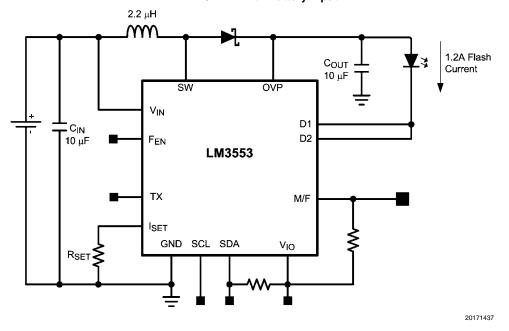

#### 1 LED @ 1.2A with Battery Input

20171415

20171439

#### 2 LEDs @ 1.2A with +5V Input 2.2 μΗ V<sub>IN</sub> = +5V M C<sub>OUT</sub> 4.7 μF 1.2A Flash Current SW OVP $V_{\text{IN}}$ VREF D1 C<sub>IN</sub> 10 μF $\mathsf{F}_{\mathsf{EN}}$ D2 LM3553 $\mathsf{TX}$ M/F ISET GND SCL SDA $V_{IO}$

#### Voltage Mode @ 700mA with Battery Input

## Physical Dimensions inches (millimeters) unless otherwise noted

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support          |                                |

|--------------------------------|------------------------------|-------------------------|--------------------------------|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |

| Switching Regulators           | www.national.com/switchers   |                         |                                |

| LDOs                           | www.national.com/ldo         |                         |                                |

| LED Lighting                   | www.national.com/led         |                         |                                |

| PowerWise                      | www.national.com/powerwise   |                         |                                |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email:

new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com