# NOT RECOMMENDED FOR NEW DESIGNS See HMP8115 *HMP8112*

# NTSC/PAL Video Decoder

#### March 1998

#### Features

- Supports ITU-R BT.601 (CCIR601) and Square Pixel

- 3 Composite Analog Inputs with Sync Tip AGC, Black **Clamping and White Peak Control**

- Patented Decoding Scheme with Improved 2-Line Comb Filter, Y/C Separation

- NTSC M, N, and PAL (B, D, G, H, I, M, N, CN) Operation

- · Composite or S-Video Input

- User-Selectable Color Trap and Low Pass Video Filters

- User Selectable Hue, Saturation, Contrast, Sharpness, and Brightness Controls

- User Selectable Data Transfer Output Modes

- 16-Bit 4:2:2 YCbCr

- 8-Bit 4:2:2 YCbCr

- User Selectable Clock Range from 20MHz 30MHz

- I<sup>2</sup>C Interface

- VMI Compatible Video Data Bus

# Applications

- Multimedia PCs

- Video Conferencing

- Video Editing

- Video Security Systems

- Settop Boxes (Cable, Satellite, and Telco)

- Digital VCRs

- Related Products

- NTSC/PAL Encoders: HMP8154, HMP8156, HMP8171, HMP8173

- NTSC/PAL Decoders: HMP8115

# Description

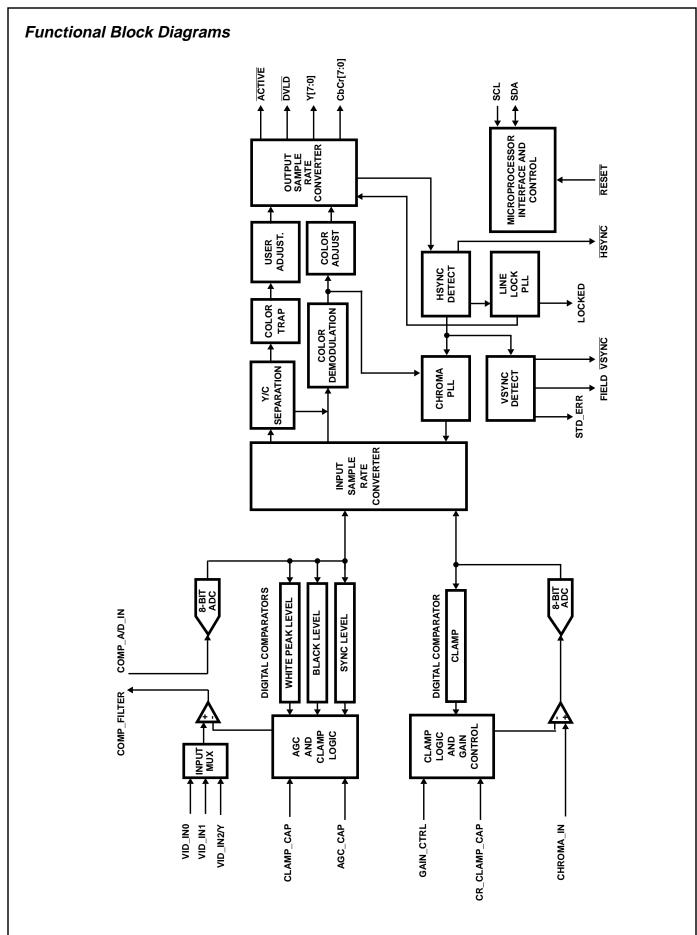

The HMP8112 is a high quality, digital video, color decoder with internal A/D converters. The A/D function includes a 3:1 analog input mux, Sync Tip AGC, Black clamping and two 8-bit A/D Converters. The high quality A/D converters minimize pixel jitter and crosstalk.

The decoder function is compatible with NTSC M, PAL B, D, G, H, I, M, N and special combination PAL N video standards. Both composite (CVBS) and S-Video (Y/C) input formats are supported. A 2 line comb filter plus a user selectable Chrominance trap filter provide high quality Y/C separation. Various adjustments are available to optimize the image such as Brightness, Contrast, Saturation, Hue and Sharpness controls. Video synchronization is achieved with a 4xf<sub>SC</sub> chroma burst lock PLL for color demodulation and line lock PLL for correct pixel alignment. A chrominance subsampling 4:2:2 scheme is provided to reduce chrominance bandwidth.

The HMP8112 is ideally suited as the analog video interface to VCR's and camera's in any multimedia or video system. The high quality Y/C separation, user flexibility and integrated phase locked loops are ideal for use with today's powerful compression processors. The HMP8112 operates from a single 5V supply and is TTL/CMOS compatible.

# Ordering Information

| PART NUMBER  | TEMP.<br>RANGE ( <sup>o</sup> C)                  | PACKAGE     | PKG.NO.   |

|--------------|---------------------------------------------------|-------------|-----------|

| HMP8112CN    | 0 to 70                                           | 80 Ld PQFP† | Q80.14x20 |

| HMP8112EVAL2 | PCI Reference Design (Includes Part)              |             |           |

| HMP8156EVAL2 | Frame Grabber Evaluation Board<br>(Includes Part) |             |           |

† PQFP is also known as QFP and MQFP

# Table of Contents

| Functional Block Diagrams             |

|---------------------------------------|

| Functional Operation Introduction6    |

| Internal Register Description Tables  |

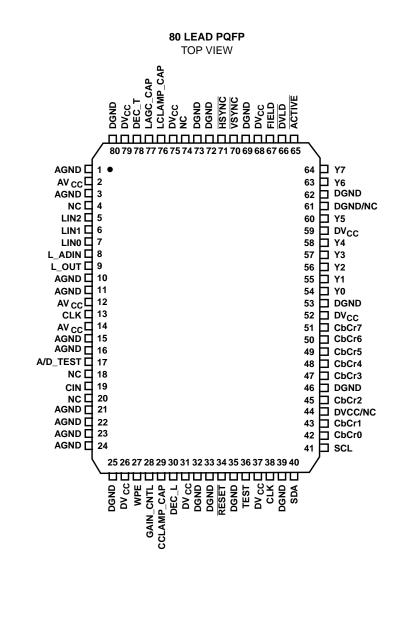

| Pinout                                |

| Pin Descriptions                      |

| AC and DC Electrical Specifications24 |

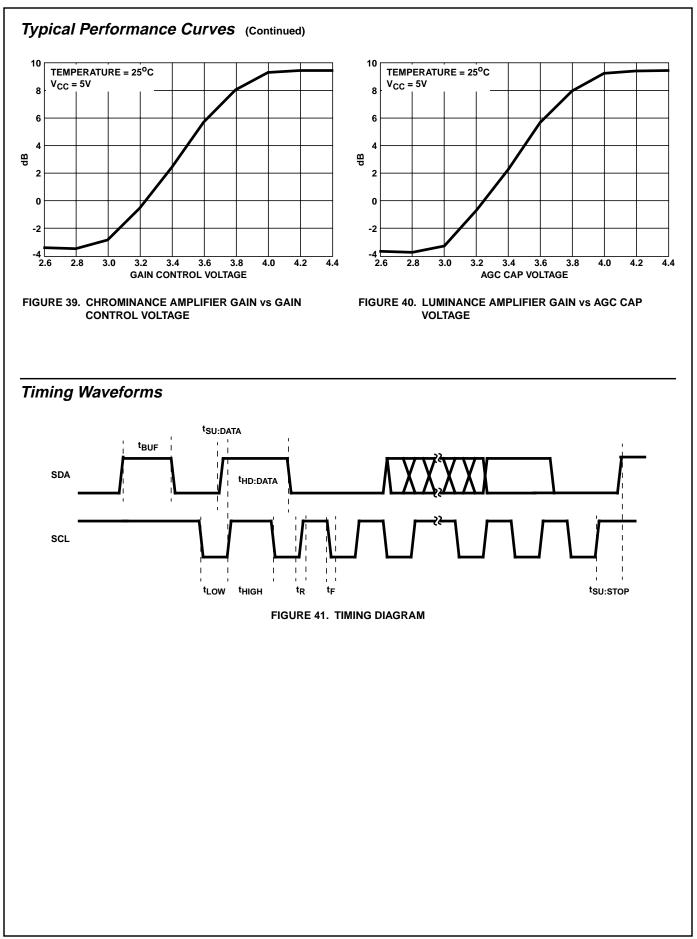

| Typical Performance Curves            |

| Applications Information              |

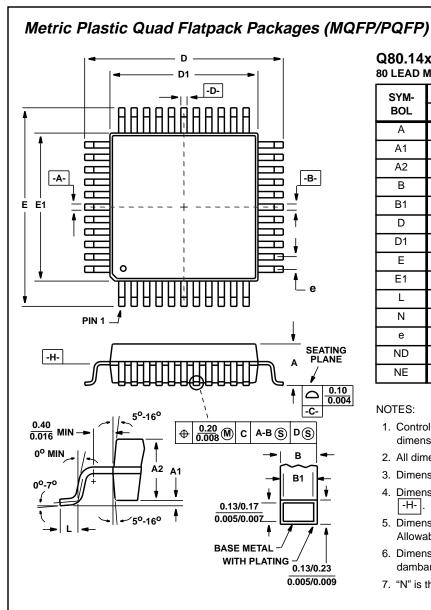

| Package Dimensions40                  |

|                                       |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. Copyright C Harris Corporation 1998

Page

# Introduction

The HMP8112 is an NTSC/PAL compatible Video Decoder with both chroma burst and line locked digital phase locked loops. The HMP8112 contains two 8-bit A/D converters and an  $l^2C$  port for programming internal registers.

#### Analog Video/Mux Inputs

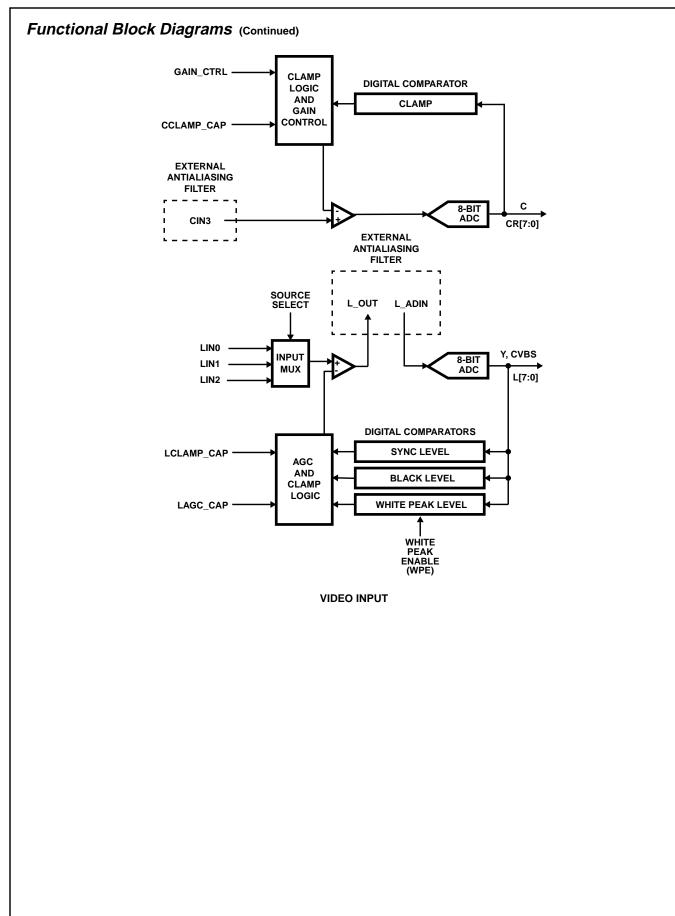

The Luminance channel has three analog video inputs that can be used for composite or the Y input of a S-Video signal, and one analog input for chrominance. LIN2 is used with CIN to interface an S-Video input. Three composite or two composite and one S-Video inputs can be applied to the HMP8112 at any one time. Control of the analog front end is selected by bits 2 and 1 of the Video Input Control Register.

#### **Anti-Aliasing Filter**

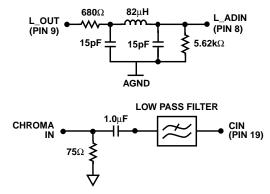

An external anti-alias filter is required to achieve optimum performance and prevent high frequency components from being aliased back into the video image. For the LIN inputs a single filter is connected to L\_OUT and L\_ADIN. For CIN the anti-aliasing filter should be connected to the CIN input. A recommended filter is shown below.

FIGURE 1. RECOMMENDED ANTI-ALIASING FILTER

#### AGC And Clamp Circuit

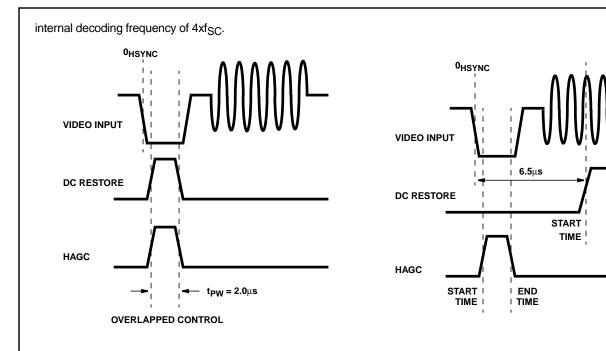

Inputs LIN0-2 contain a sync tip AGC amplifier. During the sync tip the value of the A/D is driven to code 0 by gaining up the video input signal. The sync tip AGC is sampled during the HAGC pulse time which is controlled by the HAGC Pulse Start Time and End Time registers. The LIN0-2 inputs apply a DC clamp reference to the back porch of the video. This is controlled by the DC-RESTORE Pulse Start Time and End Time Registers.

After a **RESET**, a change of the video standard, or a PLL Chrominance Subcarrier Ratio Register load, HAGC and DC RESTORE are overlapped, until LOCKED is asserted. (the PLL has acquired a stable line lock). This is the acquisition mode of the PLL where the decoder is trying to lock to a new video source. Once the PLL is LOCKED, HAGC and DC RESTORE are moved out to the default programmed values in the user programming registers. The HAGC should be set coincident to the incoming horizontal sync signal. The HAGC pulse should be set to a width of  $2\mu$ s.

Once the PLL is locked the DC RESTORE signal is moved out to the default programmed values in the user programming registers. The DC RESTORE pulse can be programmed with the DC RESTORE Start and End time control registers. DC RESTORE should be asserted 6.5 $\mu$ s after the falling edge of horizontal sync (0<sub>HSYNC</sub>) and held for a duration of 2 $\mu$ s. Both HAGC and DC RESTORE are synchronous to the output sample rate (OSR) converter and are clocked in OSR (pixel clock) clock periods. The OSR clock rate is dependent on the input standard used. See Table 1 for the register values used for the different video standards.

| VIDEO<br>OUTPUT<br>STANDARD     | HAGC<br>START/END<br>VALUES | DC<br>RESTORE<br>START/END<br>VALUES | HSYNC<br>START/END<br>VALUES |

|---------------------------------|-----------------------------|--------------------------------------|------------------------------|

| Square Pixel<br>NTSC<br>640x480 | 02F8/0008 <sub>H</sub>      | 0028/0040 <sub>H</sub>               | 0020/0050 <sub>H</sub>       |

| CCIR601 NTSC<br>720x480         | 033F/0000 <sub>H</sub>      | 0037/0052 <sub>H</sub>               | 033B/0060 <sub>H</sub>       |

| CCIR601<br>PAL<br>720X512       | 033F/0000 <sub>H</sub>      | 0037/0052 <sub>H</sub>               | 033B/0060 <sub>H</sub>       |

| Square Pixel<br>PAL<br>768X512  | 03A0/0018 <sub>H</sub>      | 0040/0054 <sub>H</sub>               | 0020/0070 <sub>H</sub>       |

#### White Peak Enable

The white peak enable input, (WPE) enables or disables the white peak control. Enabled, (logic high) when the digital outputs exceed code 248, the AGC will reduce the gain of the video amplifier to prevent over-ranging the A/D. If disabled, the AGC operates normally, keeping the horizontal sync tip at code 0 and allowing the A/D's range to go to 255 at the maximum peak input.

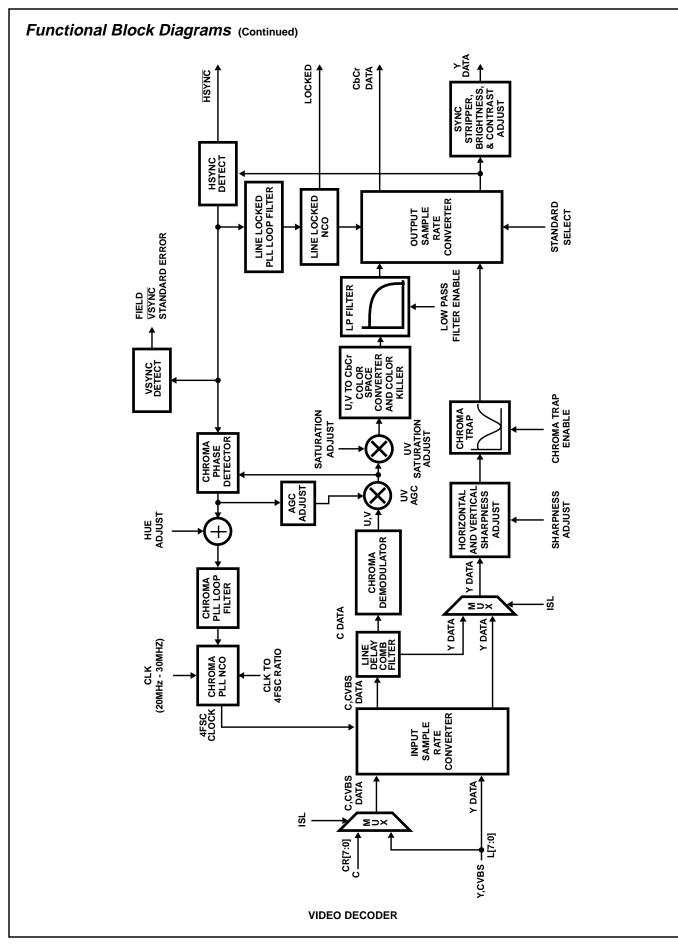

#### NTSC/PAL Decoder

The NTSC/PAL decoder is designed to convert incoming Composite or Separated (SVHS, Y/C) video into it's YCbCr component parts. The digital phase locked loops are designed to synchronize to the various NTSC/PAL standards. They provide a stable internal  $4xf_{SC}$  (Frequency of the Color Sub-Carrier) video clock for color demodulation, and a line locked clock for vertical spatial pixel alignment.

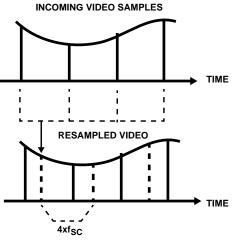

The decoder uses the CLK to run the A/D converters and the phase locked loops. This asynchronous master clock for the decoder eliminates the need for a unique clock source in a Multimedia application. CLK can run from 20MHz to 30MHz when using the 16-bit Synchronous Data output Mode. The user must program the CLK to Color Sub-Carrier Ratio to match the CLK frequency used (see Internal Phase Locked Loops discussion). When using the 8-bit Burst Data Output Mode the CLK should be a 24.5454MHz, 27MHz or 29.5MHz depending on the output video standard chosen. The crystal oscillator must have a  $\pm$ 50ppm accuracy and a 60/40% duty cycle symmetry to ensure proper operation. Since the video data from the external A/D's are sampled at the CLK frequency a sample rate converter is employed to convert the data from the CLK rate to the

FIGURE 2A. PLL ACQUISITION MODE

The input sample rate converter will interpolate between existing CLK samples to create the chroma locked ( $4xf_{SC}$ ) samples needed for the color decoder. An interpolation is done to create the  $4xf_{SC}$  pixel and a correction factor is then applied.

FIGURE 3. SAMPLE RATE CONVERSION

The decoder can be used with the following video sources:

Analog Composite - NTSC M, - PAL B, D, G, H, I, N And Special Combination PAL N

Analog S - VHS (Y/C) - NTSC M, PAL B, D, G, H, I, N And Special Combination PAL N

#### **Color Separation, And Demodulation**

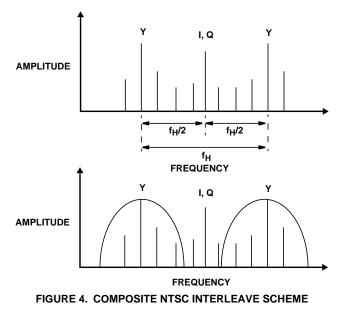

To separate the chrominance modulated color information from the baseband luminance signal, a 2 line comb filter is employed. In NTSC signals the color information changes phase 180<sup>o</sup> from one line to the next. This interleaves the

END

<sup>1</sup> TIME

chrominance information at half line intervals throughout the NTSC video spectrum. Therefore, NTSC has 227.5 cycles of chrominance per NTSC line. The half of a cycle causes the next reference burst to be 180<sup>o</sup> out of phase with the previous line's burst. The two line comb efficiently removes the chrominance information from the baseband luminance signal. When decoding NTSC, the decoder maintains full luminance bandwidth horizontally throughout the chrominance carrier frequency range. Unlike most 2 line comb filter separation techniques, vertical bandwidth is maintained by means of a proprietary transform technique.

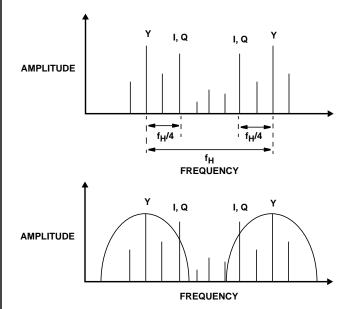

For PAL systems there are 283.75 cycles of chrominance per line. Chrominance information is spaced at quarter line intervals with a reference phase of  $135^{\circ}$ . The reference

phase alternates from line to line by 90<sup>0</sup>. To fully separate the PAL chrominance and luminance signals the user selectable filters should be enabled. The chroma notch filter built into the luminance channel should be enabled for PAL systems to reduce cross luminance effects. The low pass filter in the chrominance processing chain helps to reduce cross color products.

FIGURE 5. COMPOSITE PAL INTERLEAVE SCHEME

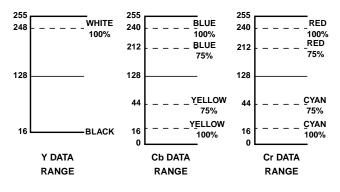

The demodulator in the decoder decodes the color components into U and V. The U and V components are converted to Cb and Cr components after the decoding process. YCbCr has a usable data range as shown in Figure 4. The data range for Y is limited to a minimum of 16.

FIGURE 6. YCbCr DATA RANGES

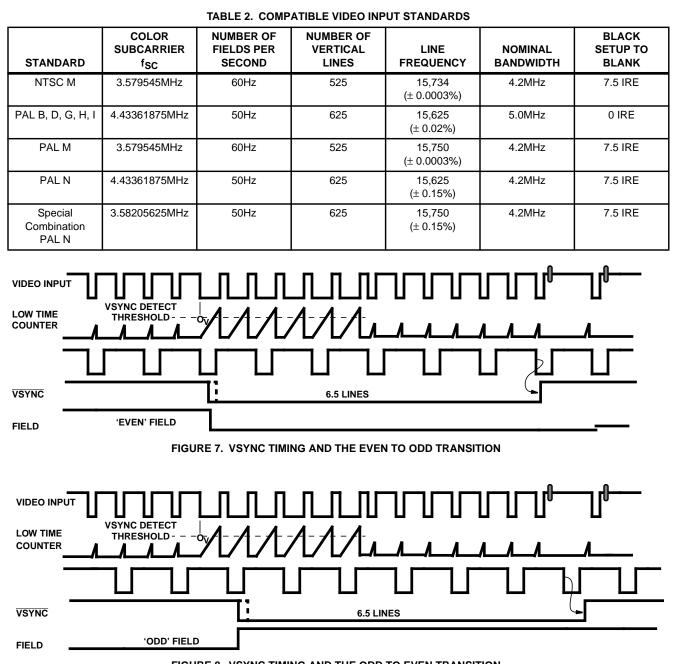

The decoder is compatible with all NTSC and PAL video formats available throughout the world. Table 2 shows the compatible video standards.

# Horizontal Sync Detection

Horizontal sync is detected in the Output Sample Rate converter (OSR). The OSR spatially aligns the pixels in the vertical direction by using the horizontal sync information embedded in the digital video data stream. The HSYNC sync pulse out of the decoder is a video synchronous output

pin. This signal follows the horizontal sync of an input video source. If there is no source the  $\overrightarrow{\text{HSYNC}}$  pin will continue to run at video rates due to the Line Locked PLL free-running. <u>HSYNC</u> can be moved throughout the video line using the HSYNC Start and End time registers. This 10-bit register allows the  $\overrightarrow{\text{HSYNC}}$  to be moved in OSR clock increments (12.27MHZ, 13.5MHz or 14.75MHz).

# Vertical Sync And Field Detection

The vertical sync and field detect circuit of the decoder uses a low time counter to detect the vertical sync sequence in the video data stream. The low time counter accumulates the low time encounted after the horizontal sync edge or at the start of each line. When the low time count exceeds the vertical sync detect threshold,  $\overrightarrow{VSYNC}$  is asserted immediately.  $\overrightarrow{VSYNC}$  will remain asserted for a minimum of 1 line. The FIELD flag is updated at the same time as the  $\overrightarrow{VSYNC}$  line. The FIELD pin is a '0' for ODD fields and a '1' for even fields.

In the case of lost vertical sync or excessive noise that would prevent the detection of vertical sync, the FIELD flag will continue to toggle. Lost vertical sync is declared if after 337 lines a vertical sync period was not detected for 3 successive lines. When this occurs the phase locked loops are initialized to the acquisition state.

The  $\overline{\text{VSYNC}}$  pulse out of the decoder follows the vertical sync detection and is typically 6.5 lines long. The  $\overline{\text{VSYNC}}$  will run at the field rate of the selected video standard selected. For NTSC the field rate is 60Hz and for PAL the field rate is 50Hz. This signal will continue to run even in the event of no incoming video signal.

# Internal Phase Locked Loops

The HMP8112 has two independent digital phase locked loops on chip. A chroma phase-locked loop is implemented to maintain chroma lock for demodulation of the color channel, and a line locked phase lock loop is implemented to maintain vertical spatial alignment. The phase locked loops are designed to maintain lock even in the event of VCR headswitches and multipath noise.

The HMP8112 can use a main crystal (CLK) of 20MHz to 30MHz. The crystal is used as a reference frequency for the internal phase locked loops. The ratio of the crystal frequency to the video standard is programmed into an internal register for the PLLs to correctly decode video.

The HMP8112 decoder contains 2 sample rate converters and 2 phase locked loops that lock to the incoming video. The input sample rate converter synchronizes the digitized video from the CLK rate to a  $4xf_{SC}$  rate. The chrominance is separated from the luminance and then demodulated. The Chroma phase locked loop uses the CLK source as the PLL reference frequency. To initialize the chroma PLL, the CLK to  $4xf_{SC}$  ratio must be loaded. For example, if the CLK was 27MHz and the video signal is NTSC (4 x 3.579545MHz = 14.318MHz) then the ratio loaded is 0.5302895 in 16-bit precision.

FIGURE 8. VSYNC TIMING AND THE ODD TO EVEN TRANSITION

(4 x f<sub>SC</sub>)/CLK = Chroma PLL Value (4 x 3.579545MHz) / 27MHz = 0.5302895

This value must be loaded to correctly separate and decode the video signal. A default Chroma PLL Value is used after a system  $\overline{\text{RESET}}$  is applied. The default assumes a CLK of 27MHz and NTSC as the video standard. The default value is 0.5302895. An ideal  $4 x f_{SC}$  line should have 910 pixels for NTSC and 1135 for PAL.

The Output Sample rate converter is locked to the horizontal line frequency and is used to spatially align pixels in a field. The LOCKED flag signals when the phase locked loop is within a  $\pm 4$  pixel range of the horizontal sync edge. When line errors exceed that range the LOCKED flag is cleared.

In cases where VCRs are used in Pause, Fast Forward or Fast Reverse, lines are typically dropped or added by the VCR. In a worst case scenario a VCR line tolerance will vary by  $\pm 8\%$ . The standard detect logic checks the line count against the given standard to determine an error. VCRs in trick mode cannot cause a standard error. With an NTSC standard VCR the number of lines in a field should not exceed 285. Greater than 285 lines in a field is interpreted as a PAL video source. An ideal NTSC source should have 262.5 lines per field and a PAL source should have 312.5 lines per field.

The HMP8112 can detect a STANDARD Error that signals when the video received does not match the standard that was programmed into the Video Input Control Register. This

flag, when asserted, tells the user that the video standard that was expected was not found and a different standard should be selected in the Video Input Control register. The error flag is cleared after a  $\overline{\text{RESET}}$  or after the Chroma PLL Clock Ratio register has been loaded via the  $I^2C$  bus. After the flag is cleared the standard error logic verifies the video standard. The error flag is set after 2 vertical sync periods have passed and the line count did not match the expected line count.

# Video Adjustments

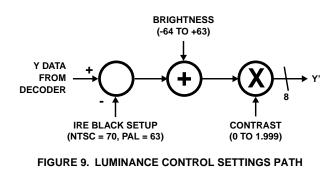

The HMP8112 allows the user to vary such video parameters as Contrast, Brightness, Sharpness, Hue and Color Saturation. These adjustments can be made via the  $I^2C$ interface. Contrast, brightness and sharpness are luminance controls. The full dynamic range of the luminance channel can be used by selecting the IRE setup cancellation mode. This mode will remove the IRE setup and blanking level offset to take advantage of the full dynamic range of the luminance processing path. The sharpening filters allow the enhancement of low, mid and high frequency components of the luminance signal to compensate for low amplitude video. Vertical sharpness is also controlled via the  $I^2C$  interface. Hue and Color saturation controls enhance the CbCr components of the incoming video, all under user control.

#### TABLE 3. USER CONTROLLED SETTINGS

| USER VIDEO SETTINGS  |

|----------------------|

| Brightness           |

| Contrast             |

| Hue or Tint          |

| Horizontal Sharpness |

| Vertical Sharpness   |

| Color Saturation     |

#### Luminance Adjustments

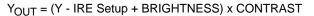

The Luminance data can be adjusted in the HMP8112. The user can adjust brightness and contrast of the Y or luminance data. The user can also set the IRE or setup subtraction value to eliminate the black pedestal offset from NTSC signals. The Contrast adjustment range can exceed a value of one so as to take full advantage of the 8-bit dynamic range for Y. The user control settings executes the equation

#### Brightness

The user can control the brightness of the incoming video by programming the Brightness register. The brightness adjustment will offset the Y component. The brightness register is an 8-bit register where the bottom 7 bits are brightness control and the top bit is the IRE setup. The IRE setup for NTSC is 70 and the setup for PAL is 63.

When the IRE bit is set (1) then the value of 70 is subtracted from the Y data, and if the IRE bit is cleared (0) then the values of 63 is subtracted. The brightness control bits BR[6-0] will brighten the picture as the value is increased. BR = -64 is the darkest and BR = +63 is the brightest. The default value of the register after a  $\overrightarrow{\text{RESET}}$  is 0 (80<sub>H</sub>).

#### Contrast

The contrast adjustment will allow the user to increase and decrease the gain of the Y data. The contrast factor is an 8-bit number (as shown below) that ranges from 0 to 1.999.

#### X.XXXXXXX

The default value after a RESET is 1.47 (BD<sub>H</sub>).

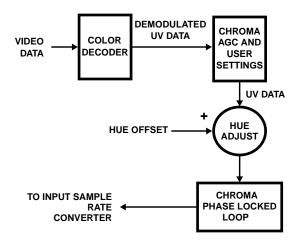

# Hue or Tint Adjust

The Hue adjustment is applied to the U and the V color difference signal. The Hue adjusts the phase of the given UV data. The Hue can be adjusted by  $\pm 30^{\circ}$  in  $1/4^{\circ}$  increments. This is achieved by changing the Burst Phase Locked reference point. Figure 10 shows the block diagram for the color adjustment section. This default value for this register is 0 (00<sub>H</sub>).

FIGURE 10. HUE ADJUST BLOCK DIAGRAM

# Horizontal/Vertical Sharpness

The frequency characteristics of the video waveform can be altered to enhance the sharpness of the picture. The Horizontal Sharpness register acts as a 4 band equalizer where the amplitude of specific frequency ranges can be enhanced or diminished. The Sharpness Control Register allows the Low (LF), Mid (MF) and High Frequency (HF) bands of the luminance signal to be enhanced. Vertical Sharpness can be adjusted to 1 or a factor of 0. The RESET default is a factor of 1.0

The 2-bit values allow 4 choices of scaling factors. The sharpness control helps to compensate for losses in the scaling interpolators that can reduce the amplitude of high frequency components.

| XF1 | XF0 | GAIN FACTOR   |

|-----|-----|---------------|

| 0   | 0   | SCALED BY 1.0 |

| 0   | 1   | SCALED BY 2.0 |

| 1   | 0   | SCALED BY 4.0 |

| 1   | 1   | SCALED BY 0   |

TABLE 4. SHARPNESS GAIN FACTOR SELECTS

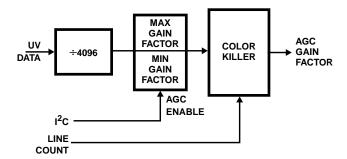

# The Color Killer (AGC Hysteresis and Loop Limits)

The color killer will disable the color difference path and set the U and V components to zero. The automatic color killer circuitry uses the AGC threshold to determine the maximum and minimum gain factor limits. The loop filter determines how much the AGC gain factor can be changed within one line. The maximum gain factor (Max = 8) and the minimum gain factor (Min = 0.5) will limit the range of the AGC. When the gain factor exceeds the maximum gain factor of 8, the gain factor is limited to 8. Once the signal has an amplitude of 1/16th, the nominal video the color killer is enabled and the chroma phase locked loop holds it's last phase reference. While the color killer is enabled, the U and V components are forced to zero. Once the input video signal reaches 1/7th the optimum amplitude the color killer is disabled and the color is returned.

The dynamic range of the AGC allows it to compensate for video that is 1/8 to 2 times the specified nominal of  $1V_{P-P}$ .

# Saturation

The color saturation component is controlled via the Color Saturation Registers. The color saturation is applied to the UV components after the AGC function. The saturation value is multiplied by the UV data to increase the color intensity. The data range is from 0 to 1.96875 where 1.96875 is the brightest intensity. This is an 8-bit number in the form:

X.XXX XXXX

The default value after a  $\overline{\text{RESET}}$  is 1.2074 (9D<sub>H</sub>).

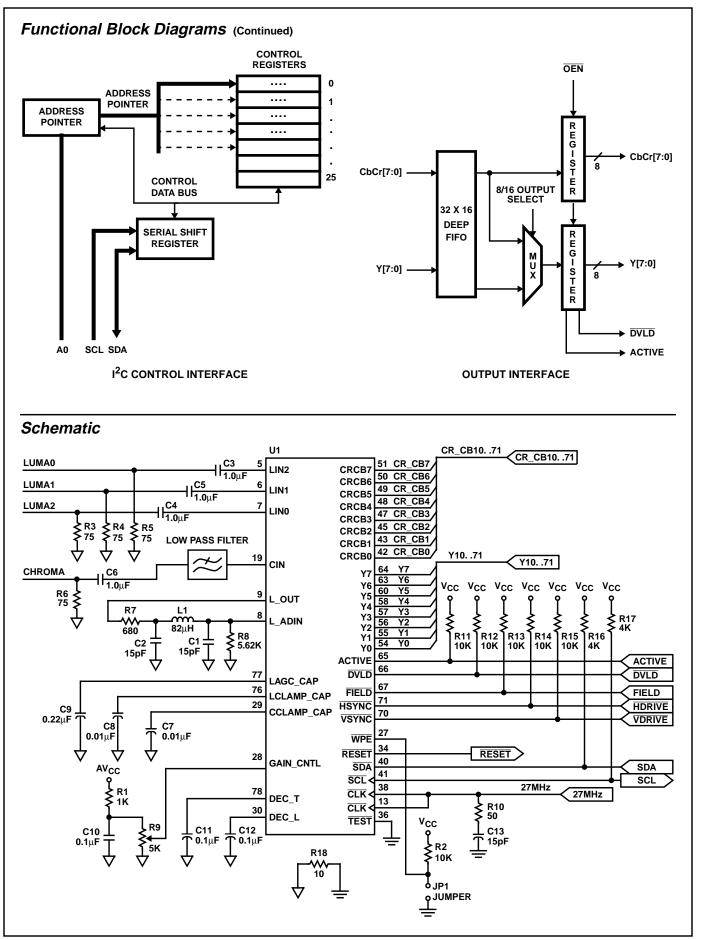

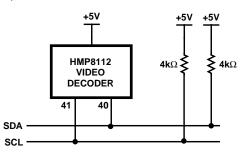

# I<sup>2</sup>C Control Interface

The HMP8112 utilizes an I<sup>2</sup>C control bus interface to program the internal configuration registers. This standard mode (up to 100 KBPS) interface consists of the bidirectional Serial Data Line (SDA) and the Serial Clock Line (SCL). The implementation on the HMP8112 is a simple slave interface that will not respond to general calls and cannot initiate a transfer. When the device is not active, the SDA and SCL control pins should be pulled high through external 4k $\Omega$  pullup resistors.

FIGURE 12. PULLUP RESISTOR CONFIGURATION

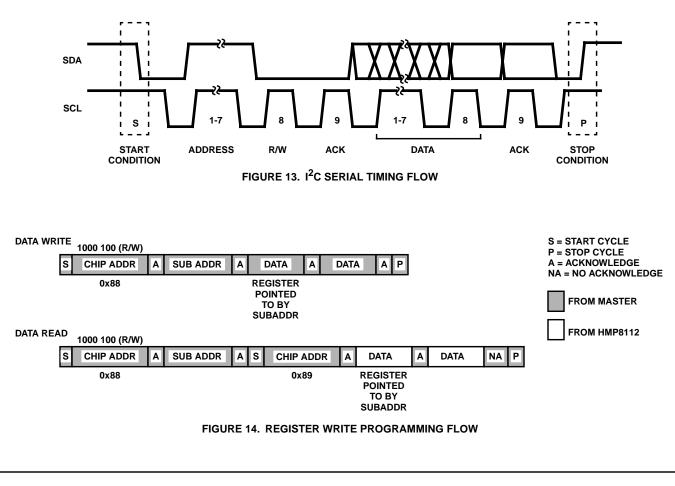

The  $l^2C$  clock/data timing is shown below in Figure 13. The HMP8112 contains 29 internal registers used to program and configure the Decoder. The  $l^2C$  control port contains a pointer register that auto-increments through the entire register space and can be written. The autoincrement pointer will wrap after the last register has been accessed (Product ID Register) and should be set to the desired starting address each time an access is started. For a write transfer, the  $l^2C$  device base address is the first part of a serial transfer. Then the internal register pointer is loaded. Then a series of registers can be written. If multiple registers are written, the pointer register will autoincrement up through the register address space. A stop cycle is used to end the transfer after the desired number of registers are programmed.

For a read transfer, the I<sup>2</sup>C device address is the first part of the serial transfer. Then the internal register pointer is loaded. At this point another start cycle is initiated to access the individual registers. Figure 14 shows the programming flow for read transfer of the internal registers. Multiple registers can be read and the pointer register will autoincrement up through the pointer register address space. On the last data read, an acknowledge should not be issued. A stop cycle is used to end the transfer after the desired number of registers are read.

# Product ID Register

The HMP8112 contains a product ID register that can be used to identify the presence of a board during a Plug 'n Play detection software algorithm. The Product ID code is  $12_H$  and the register is the last register in the HMP8112 ( $1B_H$ ).

# **Output Data Port Modes**

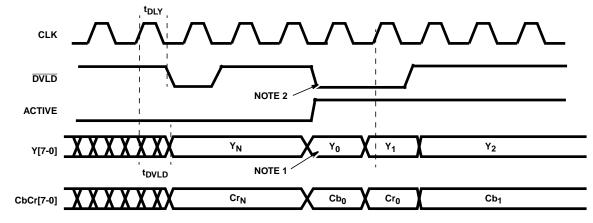

The HMP8112 can output data in 2 formats, an 8-bit Burst mode and a 16-bit Synchronous Pixel Transfer mode. In 16-bit Synchronous Pixel Transfer Mode pixel data is output at the

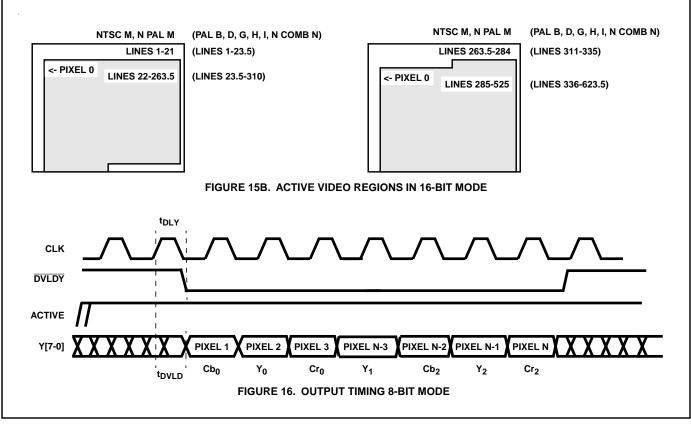

CLK frequency and Table 5 shows the number of data points per video line to expect for a given standard. Data is output as 4:2:2 subsampled data in a Y-Cb/Y-Cr 16-bit sequence. The Data Valid (DVLD) flag is asserted when video data is present on the 16-bit output port of the HMP8112 (Y[7:0], CbCr[7:0]). The ACTIVE flag is asserted when the active video portion of the horizontal scan line is present on the data output port. See Figure 15 for Synchronous Pixel Transfer Mode timing. DVLD is asserted every time the output sample rate converter has a valid output. When DVLD and ACTIVE are used together the visual portion of the image can be captured. When DVLD is used alone all valid data during the Horizontal, Vertical and Reference Burst Timing are available. ACTIVE is asserted from lines 22 through 262.5 and lines 285.5 through 525 for NTSC (and PAL M). Active is asserted from lines 23.5 through 310 and lines 336 through 623.5 for PAL (B, D, G, H, I, N, Comb N).

The CLK can be run on a 20MHz - 30MHz clock source. Data will be output (on average) at the Output Data Rate shown in Table 5 for a given standard. Data is clocked out synchronous to CLK and will come in bursts. To smooth out the data rate to a regular rate a CLK of 2X the average output data rate can be used. In the 16-bit pixel transfer, data is sequenced on the CbCr[7:0] data bus, starting with Cb and then Cr.

#### TABLE 5. OUTPUT MODE STANDARDS

| STANDARD                                 | OUTPUT<br>DATA<br>RATE | ACTIVE<br>PIXELS/<br>LINE | TOTAL<br>PIXELS/<br>LINE | TOTAL<br>LINES/<br>FIELD |

|------------------------------------------|------------------------|---------------------------|--------------------------|--------------------------|

| NTSC Square Pixel                        | 12.27MHz               | 640                       | 780                      | 262.5                    |

| NTSC CCIR 601                            | 13.5MHz                | 720                       | 858                      | 262.5                    |

| PAL B, D, G, H, I, N,<br>COMB N, CCIR601 | 13.5MHz                | 720                       | 864                      | 312.5                    |

| PAL M CCIR 601                           | 13.5MHz                | 720                       | 858                      | 262.5                    |

| PAL B, D, G, H, I, N<br>Square Pixel     | 14.74MHz               | 768                       | 944                      | 312.5                    |

| PAL M Square Pixel                       | 14.74MHz               | 640                       | 780                      | 312.5                    |

For Burst Mode output format the Y[7:0] output bus is used to transfer all YCbCr data in 8-bit format. The data is also 4:2:2 subsampled but will only contain the active video portion of the line. The HMP8112 uses an internal 32 deep fifo to handle latencies between the output sample rate and the CLK frequency. In this mode, the data is clocked out at the CLK rate and only clock frequencies of 24.5454MHz, 27MHz and 29.5MHz can be used. In 8-bit data mode, the data is sequenced on the Y[7:0] bus in Cb, Y, Cr, Y format. ACTIVE is asserted as soon as the mode is selected. DVLD when asserted indicates a valid active pixel is available. Pixels during the horizontal and vertical blanking are not available. Only the active portions of the video line are output.

#### Reset

The RESET pin is used to return the decoder to an initialization state. This pin should be used after a power-up to set the part into a known state. The internal registers are returned to their RESET state and the Serial I<sup>2</sup>C port is returned to inactive state. The RESET pin is an active low signal and should be asserted for minimum of 1 CLK cycle. After a RESET or a software reset has occurred all output pins are three-stated. The following pins must be pulled high to ensure proper operation:

| HSYNC  |

|--------|

| VSYNC  |

| DVLD   |

| ACTIVE |

| FIELD  |

|        |

A 10K or smaller pullup resistor to  $V_{CC}$  is recommended.

NOTES:

- 1. Y0 is the first active luminance pixel of a line. Cb0 and Cr0 are first active chrominance pixels in a line. Cb and Cr will alternate every cycle due to the 4:2:2 subsampling.

- 2. Active is asserted for lines 22-262.5 and 285.5-525. DVLD is asserted for every valid pixel during both active and blanking regions. DVLD is asserted during vertical and horizontal sync.

#### FIGURE 15A. OUTPUT TIMING 16-BIT MODE

|               | DESTINATION ADDRESS = 00 <sub>H</sub>  |                                                                                                                                                                                                                                                                                                                                                                                        |                 |

|---------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| BIT<br>NUMBER | FUNCTION                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                            | RESET<br>STATE  |

| 7 - 6         | Video Input<br>Standard                | These bits select the video input standard.<br>00 = PAL B, G, H, I, N; 4.43MHz subcarrier; 50fps; 625 lines/frame;<br>01 = PAL M; 3.58MHz subcarrier; 60fps; 525 lines/frame;<br>10 = Special PAL N; 3.58MHz subcarrier; 50fps; 625 lines/frame;<br>11 = NTSC M; 3.58MHz subcarrier; 60fps; 525 lines/frame (default);                                                                 | 11 <sub>B</sub> |

| 5             | Color Trap Filter<br>Disable           | This bit enables the color subcarrier trap filter. The filter removes the color subcarrier infor-<br>mation from the luminance channel. The filter should be enabled for PAL Standard systems.<br>0 = Enabled<br>1 = Disabled (default)                                                                                                                                                | 1 <sub>B</sub>  |

| 4             | Chrominance Low<br>Pass Filter Disable | This bit enables the chrominance low pass filter. This filter band limits the chrominance channel to remove luminance artifacts. This filter should be enabled for PAL Standard systems.<br>0 = Enabled<br>1 = Disabled (default)                                                                                                                                                      | 1 <sub>B</sub>  |

| 3             | Automatic Color<br>Gain Control        | This bit enables the color AGC function. When this bit is set the color AGC will automatically adjust the chrominance channel gain, to drive the color reference burst to a nominal $\pm 20$ IRE's. When this bit is cleared the color AGC gain factor is set to 1.0 and the color saturation must be adjusted to obtain nominal CrCb values.<br>0 = Disabled<br>1 = Enabled (default) | 1 <sub>B</sub>  |

| 2 - 1         | A/D Converter<br>Multiplexor Selects   | These bits control the A/D input select multiplexers and whether S-Video is being input as follows: MUXSEL1,0 =<br>0, 0 = Select Composite Video Input #0, set decoder for Composite<br>1, 0 = Select Composite Video Input #1, set decoder for Composite<br>0, 1 = Select Composite Video Input #2, set decoder for Composite<br>1, 1 = Select S-Video Y and C Inputs                 | 00 <sub>B</sub> |

| 0             | Not Used                               | Write Ignored, Read 0's                                                                                                                                                                                                                                                                                                                                                                | X <sub>B</sub>  |

#### TABLE 7. LUMINANCE BRIGHTNESS CONTROL

| DESTINATION ADDRESS = 01 <sub>H</sub> |                                   |                                                                                                                                                                                                                                                                                                                                                        |                       |

|---------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| BIT<br>NUMBER                         | FUNCTION                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                            | RESET<br>STATE        |

| 7                                     | IRE Setup<br>Cancellation Control | This bit enables the black setup cancelation circuit for NTSC sources. When this bit is set<br>a value of 73 is used to strip the sync information from the video signal. When this bit is<br>cleared a value of 64 is used to strip the sync information.<br>0 =  subtract 64 from the luminance signal<br>1 =  subtract 73 from the luminance signal | 1 <sub>B</sub>        |

| 6 - 0                                 | Luminance<br>Brightness Control   | These bits control the brightness adjustment to the luminance channel. The brightness adjustment value is a number that ranges from +63 to -64. This register is in the two's complement format, where bit 6 is the sign bit.                                                                                                                          | 000 0000 <sub>B</sub> |

#### TABLE 8. LUMINANCE CONTRAST ADJUST REGISTER

# DESTINATION ADDRESS = 02<sub>H</sub> BIT FUNCTION RESET NUMBER FUNCTION DESCRIPTION STATE 7 - 0 Luminance Contrast This register sets the contrast adjust factor. This value is multiplied by the luminance data and allows the data to be scaled from 0 to a factor of +1.96875. This 8-bit number is a fractional number as shown below: $2^0 2^{-1} 2^{-2} 2^{-3} 2^{-4} 2^{-5} 2^{-6} 2^{-7}$ The contrast factor is applied after the brightness. 1011 1101<sub>B</sub>

#### TABLE 9. HUE ADJUST REGISTER

|               | DESTINATION ADDRESS = 03 <sub>H</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |  |

|---------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| BIT<br>NUMBER | FUNCTION                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                     | RESET<br>STATE         |  |

| 7 - 0         | Hue Phase Adjust                      | This register sets the hue phase offset adjustment. This 8-bit number is applied as a phase offset to the CbCr data coming out of the demodulator. This 8-bit number is a in the range of $+127$ to $-128$ . The hue adjust has as range of $30^{\circ}$ with each count in this register allowing a $0.25^{\circ}$ phase adjustment. This register is in two's complement format, where bit 7 is the sign bit. | 0000 0000 <sub>B</sub> |  |

| BIT<br>NUMBER | FUNCTION                                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                              | RESET<br>STATE  |

|---------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 7 - 6         | High Frequency<br>Enhancement Factor                | These bits adjust the amplitude of high frequency components in the luminance video signal. The attenuation or multiplication of the high frequency components is adjusted as shown below:<br>00 = Multiply high frequency components by 1.0<br>01 = Multiply high frequency components by 2.0<br>10 = Multiply high frequency components by 4.0<br>11 = Zero out high frequency components.             | 00 <sub>B</sub> |

| 5 - 4         | Middle Frequency<br>Enhancement<br>Factor           | These bits adjust the amplitude of middle frequency components in the luminance video signal. The attenuation or multiplication of the middle frequency components is adjusted as shown below:<br>00 = Multiply middle frequency components by 1.0<br>01 = Multiply middle frequency components by 2.0<br>10 = Multiply middle frequency components by 4.0<br>11 = Zero out middle frequency components. | 00 <sub>B</sub> |

| 3-2           | Low Frequency<br>Enhancement<br>Factor              | These bits adjust the amplitude of low frequency components in the luminance video sig-<br>nal. The attenuation or multiplication of the low frequency components is adjusted as<br>shown below:<br>00 = Multiply low frequency components by 1.0<br>01 = Multiply low frequency components by 2.0<br>10 = Multiply low frequency components by 4.0<br>11 = Zero out low frequency components.           | 00 <sub>B</sub> |

| 1 - 0         | Vertical High<br>Frequency<br>Enhancement<br>Factor | These bits adjust the amplitude of vertical high frequency components in the luminance video signal. The attenuation or multiplication of the vertical high frequency components is adjusted as shown below:<br>00 = Multiply vertical high frequency components by 1.0<br>01 = Reserved.<br>10 = Reserved.<br>11 = Zero out vertical high frequency components.                                         | 00 <sub>B</sub> |

#### TABLE 10. LUMINANCE SHARPNESS CONTROL REGISTER

#### TABLE 11. COLOR SATURATION ADJUST FACTOR

|               | DESTINATION ADDRESS = 05 <sub>H</sub> |                                                                                                                                                                                                                                                                                                                                                                      |                        |  |

|---------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| BIT<br>NUMBER | FUNCTION                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          | RESET<br>STATE         |  |

| 7 - 0         | Color Saturation<br>Adjust Factor     | This register sets the color saturation adjust factor. This value is multiplied by the chromi-<br>nance (CbCr) data and allows the data to be scaled from 0 to a factor of +1.96875. This 8-bit<br>number is a fractional number as shown below:<br>$2^{0} 2^{-1} 2^{-2} 2^{-3} 2^{-4} 2^{-5} 2^{-6} 2^{-7}$<br>The contrast factor is applied after the brightness. | 1001 1101 <sub>B</sub> |  |

#### TABLE 12. PHASE LOCKED LOOP CHROMINANCE SUBCARRIER TO BUS CLOCK FREQUENCY RATIO

|               | DESTINATION ADDRESS = 06 <sub>H</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |  |

|---------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| BIT<br>NUMBER | FUNCTION                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RESET<br>STATE         |  |

| 7 - 0         | Chroma PLL Ratio                      | These bits are used to program the ratio of the incoming video chrominance color sub-<br>carrier frequency to the BUS Clock used. This number serves as the reference frequency<br>of the chrominance PLL and must be very accurate. This is the lower byte of the ratio and<br>encompasses the following range:<br>$2^{-9} 2^{-10} 2^{-11} 2^{-12} 2^{-13} 2^{-14} 2^{-15} 2^{-16}$<br>The default value is for a CLK frequency of 27MHz and a color subcarrier of 3.579545<br>MHz. | 1100 0001 <sub>B</sub> |  |

#### TABLE 13. PHASE LOCKED LOOP CHROMINANCE SUBCARRIER TO BUS CLOCK FREQUENCY RATIO

|               | DESTINATION ADDRESS = 07 <sub>H</sub> |                                                                                                                                                                                                                                                                                                                                                                               |                        |  |  |

|---------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|

| BIT<br>NUMBER | FUNCTION                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                   | RESET<br>STATE         |  |  |

| 15 - 8        | Chroma PLL Ratio                      | These bits are used to program the ratio of the incoming video chrominance color sub-<br>carrier frequency to the BUS Clock used. This number serves as the reference frequency<br>of the chrominance PLL and must be very accurate. This is the upper byte of the ratio<br>and encompasses the following range:<br>$2^{-1} 2^{-2} 2^{-3} 2^{-4} 2^{-5} 2^{-6} 2^{-7} 2^{-8}$ | 1000 0111 <sub>B</sub> |  |  |

#### TABLE 14. HORIZONTAL AGC START TIME REGISTER

| DESTINATION ADDRESS = 08 <sub>H</sub> |                                                    |                                                                                                                                                                                                                                                                                                                                                                                     |                        |

|---------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| BIT<br>NUMBER                         | FUNCTION                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                         | RESET<br>STATE         |

| 7 - 0                                 | Horizontal AGC<br>Pulse Programmable<br>Start Time | This register provides a programmable delay for the HAGC pulse that control the sync tip AGC in the A/D converters. The start time of the HAGC pulse is set from the detection of horizontal sync in the video data. HAGC is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the lower byte of the 10-bit word. | 0011 1111 <sub>B</sub> |

#### TABLE 15. HORIZONTAL AGC START TIME REGISTER

|               | DESTINATION ADDRESS = 09 <sub>H</sub> |                          |                |  |

|---------------|---------------------------------------|--------------------------|----------------|--|

| BIT<br>NUMBER | FUNCTION                              | DESCRIPTION              | RESET<br>STATE |  |

| 15 - 10       | Not Used                              | Write Ignored, Read 0's. | XXXX XX        |  |

#### TABLE 15. HORIZONTAL AGC START TIME REGISTER (Continued)

| DESTINATION ADDRESS = 09 <sub>H</sub> |                                                    |                                                                                                                                                                                                                                                                                                                                                                                     |                 |

|---------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| BIT<br>NUMBER                         | FUNCTION                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                         | RESET<br>STATE  |

| 9 - 8                                 | Horizontal AGC<br>Pulse Programmable<br>Start Time | This register provides a programmable delay for the HAGC pulse that control the sync tip AGC in the A/D converters. The start time of the HAGC pulse is set from the detection of horizontal sync in the video data. HAGC is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the upper byte of the 10-bit word. | 11 <sub>B</sub> |

#### TABLE 16. HORIZONTAL AGC END TIME REGISTER

|               | DESTINATION ADDRESS = 0A <sub>H</sub>            |                                                                                                                                                                                                                                                                                                                                                                                   |                        |  |

|---------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| BIT<br>NUMBER | FUNCTION                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       | RESET<br>STATE         |  |

| 7 - 0         | Horizontal AGC<br>Pulse Programmable<br>End Time | This register provides a programmable delay for the HAGC pulse that control the sync tip AGC in the A/D converters. The end time of the HAGC pulse is set from the detection of horizontal sync in the video data. HAGC is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the lower byte of the 10-bit word. | 0000 0000 <sub>B</sub> |  |

#### TABLE 17. HORIZONTAL AGC END TIME REGISTER

| DESTINATION ADDRESS = 0B <sub>H</sub> |                                                  |                                                                                                                                                                                                                                                                                                                                                                                   |                 |

|---------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| BIT<br>NUMBER                         | FUNCTION                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       | RESET<br>STATE  |

| 15 - 10                               | Not Used                                         | Write Ignored, Read 0's                                                                                                                                                                                                                                                                                                                                                           | XXXX XX         |

| 9 - 8                                 | Horizontal AGC<br>Pulse Programmable<br>End Time | This register provides a programmable delay for the HAGC pulse that control the sync tip AGC in the A/D converters. The end time of the HAGC pulse is set from the detection of horizontal sync in the video data. HAGC is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the upper byte of the 10-bit word. | 00 <sub>B</sub> |

#### TABLE 18. HORIZONTAL SYNC START TIME REGISTER

|               | DESTINATION ADDRESS = 0C <sub>H</sub>          |                                                                                                                                                                                                                                                                                                                                                 |                        |  |

|---------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| BIT<br>NUMBER | FUNCTION                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     | RESET<br>STATE         |  |

| 7 - 0         | Horizontal Drive<br>Programmable Start<br>Time | This register provides a programmable delay for the external HDRIVE signal. The start time of the HDRIVE pulse is set from the detection of horizontal sync in the video data. HDRIVE is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the lower byte of the 10-bit word. | 0011 1011 <sub>B</sub> |  |

#### TABLE 19. HORIZONTAL SYNC START TIME REGISTER

| DESTINATION ADDRESS = 0D <sub>H</sub> |                                                |                                                                                                                                                                                                                                                                                                                                                 |                 |

|---------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| BIT<br>NUMBER                         | FUNCTION                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     | RESET<br>STATE  |

| 15 - 10                               | Not Used                                       | Write Ignored, Read 0's                                                                                                                                                                                                                                                                                                                         | XXXX XX         |

| 9 - 8                                 | Horizontal Drive<br>Programmable Start<br>Time | This register provides a programmable delay for the external HDRIVE signal. The start time of the HDRIVE pulse is set from the detection of horizontal sync in the video data. HDRIVE is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the upper byte of the 10-bit word. | 11 <sub>B</sub> |

#### TABLE 20. HORIZONTAL SYNC END TIME REGISTER

|               | DESTINATION ADDRESS = 0E <sub>H</sub>        |                                                                                                                                                                                                                                                                                                                                               |                        |  |

|---------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| BIT<br>NUMBER | FUNCTION                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                   | RESET<br>STATE         |  |

| 7 - 0         | Horizontal Drive<br>Programmable End<br>Time | This register provides a programmable delay for the external HDRIVE signal. The end time of the HDRIVE pulse is set from the detection of horizontal sync in the video data. HDRIVE is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the lower byte of the 10-bit word. | 0010 0000 <sub>B</sub> |  |

#### TABLE 21. HORIZONTAL SYNC END TIME REGISTER

|               | DESTINATION ADDRESS = 0F <sub>H</sub>        |                                                                                                                                                                                                                                                                                                                                               |                 |  |  |  |

|---------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| BIT<br>NUMBER | FUNCTION                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                   | RESET<br>STATE  |  |  |  |

| 15 - 10       | Not Used                                     | Write Ignored, Read 0's                                                                                                                                                                                                                                                                                                                       | XXXX XX         |  |  |  |

| 9 - 8         | Horizontal Drive<br>Programmable End<br>Time | This register provides a programmable delay for the external HDRIVE signal. The end time of the HDRIVE pulse is set from the detection of horizontal sync in the video data. HDRIVE is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the upper byte of the 10-bit word. | 00 <sub>B</sub> |  |  |  |

#### TABLE 22. PHASE LOCKED LOOP ADJUST REGISTER

|               | DESTINATION ADDRESS = 10 <sub>H</sub>               |                                                                                                                                                                                        |                        |  |  |

|---------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|

| BIT<br>NUMBER | FUNCTION                                            | DESCRIPTION                                                                                                                                                                            | RESET<br>STATE         |  |  |

| 7 - 0         | Phase Locked Loop<br>Filter Adjust Test<br>Register | The Phase Locked Loop time constants can be changed for testing purposes. It is recommended that the default value of $(20_{\rm H})$ always be used. The reset state is $00_{\rm H}$ . | 0000 0000 <sub>B</sub> |  |  |

#### TABLE 23. PHASE LOCKED LOOP SYNC DETECT WINDOW REGISTER

|               | DESTINATION ADDRESS = 11 <sub>H</sub>                 |                                                                                                                                                                                                                                                                                                                                                          |                        |  |  |

|---------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|

| BIT<br>NUMBER | FUNCTION                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                              | RESET<br>STATE         |  |  |

| 7 - 0         | Phase Locked Loop<br>Horizontal Sync<br>Detect Window | These bits control the PLL horizontal sync detect window. This window sets the length of time that the line lock PLL will allow the detection of the HSYNC. HSYNC outside of this window are declared missing and will cause the missing sync logic to start counting missing syncs. For NTSC this value should be $DD_H$ and for PAL, FF <sub>H</sub> . | 1101 1101 <sub>B</sub> |  |  |

#### TABLE 24. DC RESTORE START TIME REGISTER

|               | DESTINATION ADDRESS = 12 <sub>H</sub>    |                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |  |  |  |

|---------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|

| BIT<br>NUMBER | FUNCTION                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                     | RESET<br>STATE         |  |  |  |

| 7 - 0         | DC Restore<br>Programmable Start<br>Time | This register provides a programmable delay for the internal DC RES signal. The start time of the DC RES pulse is set from the detection of horizontal sync in the video data. DC RES is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This signal is used to run the GATE B pin of the A/D converter. This is the lower byte of the 10-bit word. | 0011 0111 <sub>B</sub> |  |  |  |

#### TABLE 25. DC RESTORE START TIME REGISTER

|               | DESTINATION ADDRESS = 13 <sub>H</sub>    |                                                                                                                                                                                                                                                                                                                                                 |                 |  |  |

|---------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| BIT<br>NUMBER | FUNCTION                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     | RESET<br>STATE  |  |  |

| 15 - 10       | Not Used                                 |                                                                                                                                                                                                                                                                                                                                                 | XXXX XX         |  |  |

| 9 - 8         | DC Restore<br>Programmable Start<br>Time | This register provides a programmable delay for the internal DC RES signal. The start time of the DC RES pulse is set from the detection of horizontal sync in the video data. DC RES is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the upper byte of the 10-bit word. | 00 <sub>B</sub> |  |  |

#### TABLE 26. DC RESTORE END TIME REGISTER

| DESTINATION ADDRESS = 14 <sub>H</sub> |

|---------------------------------------|

|---------------------------------------|

| BIT<br>NUMBER | FUNCTION                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                   | RESET<br>STATE         |  |  |  |

|---------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|

| 7 - 0         | DC Restore<br>Programmable End<br>Time | This register provides a programmable delay for the internal DC RES signal. The end time of the DC RES pulse is set from the detection of horizontal sync in the video data. DC RES is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This signal is used to run the GATE B pin of the A/D converter. This is the lower byte of the 10-bit word. | 0101 0010 <sub>B</sub> |  |  |  |

#### TABLE 27. DC RESTORE END TIME REGISTER

|               | DESTINATION ADDRESS = 15 <sub>H</sub>  |                                                                                                                                                                                                                                                                                                                                               |                 |  |  |

|---------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| BIT<br>NUMBER | FUNCTION                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                   | RESET<br>STATE  |  |  |

| 15 - 10       | Not Used                               |                                                                                                                                                                                                                                                                                                                                               | XXXX XX         |  |  |

| 9 - 8         | DC Restore<br>Programmable End<br>Time | This register provides a programmable delay for the external DC RES signal. The end time of the DC RES pulse is set from the detection of horizontal sync in the video data. DC RES is programmable in CLK increments and has a fixed 1 clock delay following the falling edge of horizontal sync. This is the upper byte of the 10-bit word. | 00 <sub>B</sub> |  |  |

#### TABLE 28. OUTPUT FORMAT CONTROL REGISTER

| DESTINATION ADDRESS = 16 <sub>H</sub> |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |  |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| BIT<br>NUMBER                         |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |  |

| 7                                     | Square Pixel/ITU-R<br>BT601 Select      | When "1", Square pixel output is selected, when "0" ITU-R BT601 output rate is selected.                                                                                                                                                                                                                                                                                                                                                           | 0 <sub>B</sub>   |  |

| 6, 5, 4                               | Output Field Control<br>"FLD_CONT(2-0)" | These bits control the field capture rate of the HMP8112. The user can select every 4th<br>field, every other field or every field of video to be output to the data port.<br>000 = No Capture Enabled<br>001 = Capture every 4th field<br>010 = Capture every 2nd field<br>011 = Capture every 2nd odd field<br>100 = Capture every 2nd even field<br>101 = Capture every odd field<br>110 = Capture every even field<br>111 = Capture all fields | 000 <sub>B</sub> |  |

| 3                                     | 8/16 output Select                      | When "1", the 8-bit Burst Transfer output mode is selected. When "0", the 16-bit Synchro-<br>nous Pixel Transfer output mode is selected.                                                                                                                                                                                                                                                                                                          | 0 <sub>B</sub>   |  |