### Freescale Semiconductor

Advance Information

# NICAM 728 - Stereo Encoder

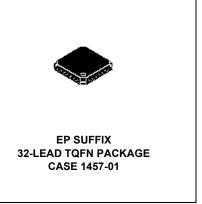

The MC44C404 NICAM Stereo Encoder is the industry's first single-chip CMOS implementation of a Near Instantaneous Companding Audio Multiplex 728 (NICAM) stereo encoder.

- Intended for use in set-top boxes, VCRs, DVD players/recorders, game stations, and other applications that are required to output high-quality stereo sound through a single RF coaxial cable.

- Engineered to process analog audio signals to generate a QPSK modulated signal in compliance with the EN 300 163 standard.

- Designed to output this signal to a Freescale RF modulator, which in turn produces a stereo encoded RF channel for use with any NICAM stereo television receiver.

#### **Features**

- Supports B, G, H, I, K1, L system standards

- NICAM digital audio processing encodes and transports stereo signals

- · Integrated A/D converter input and D/A converter output circuitry

- Extended low frequency response (below 25 Hz)

- Simple passive interface to MC44BS373/4 UHF modulators

- Low power consumption typically < 50 mW</li>

- RoHS compliant

#### **Benefits**

- Preservation of original surround sound fidelity

- Multi standard

- Low system component count, small board size and significantly low overall system cost

- · No manual alignment of filters or phase controls

#### **Reference Documentation**

NICAM 728: Transmission of two-channel digital sound with terrestrial television systems B, G, H, I, K1 and L. (EN 300 163 V1.2.1)

**VRoHS**

## MC44C404

#### **NICAM STEREO ENCODER**

| ORDERING INFORMATION |                 |         |      |  |  |

|----------------------|-----------------|---------|------|--|--|

| Device               | Temp.<br>Range  | Package | RoHS |  |  |

| MC44C404EP           | 0°C to<br>+70°C | 32TQFN  | Yes  |  |  |

| MC44C404EPR2         | Tape            | Yes     |      |  |  |

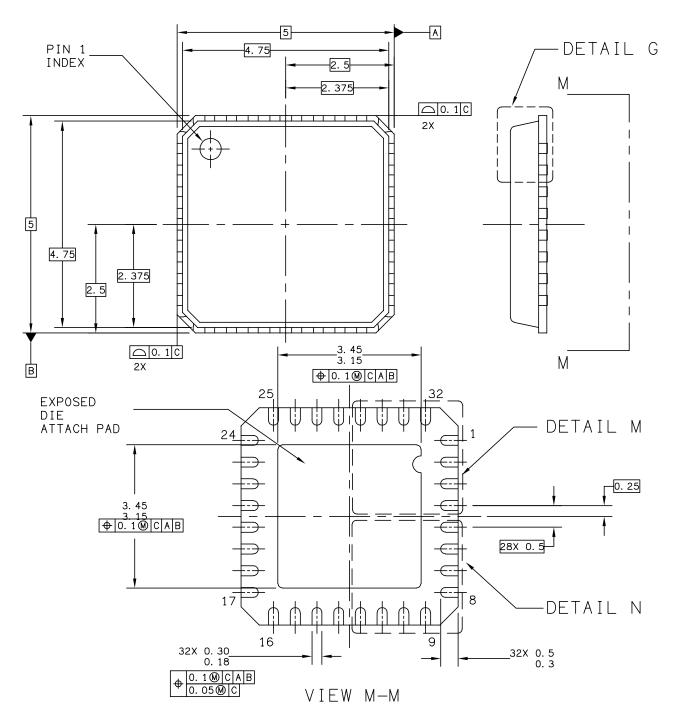

MC44C404 32TQFN Package

This document contains information on a preproduction product. Specifications and information herein are subject to change without notice.

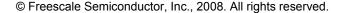

Figure 1. MC44C404 Block Diagram

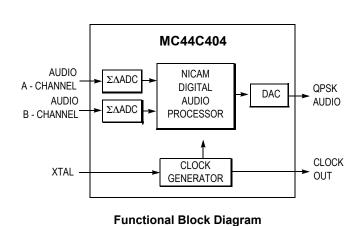

## **PIN DESCRIPTION**

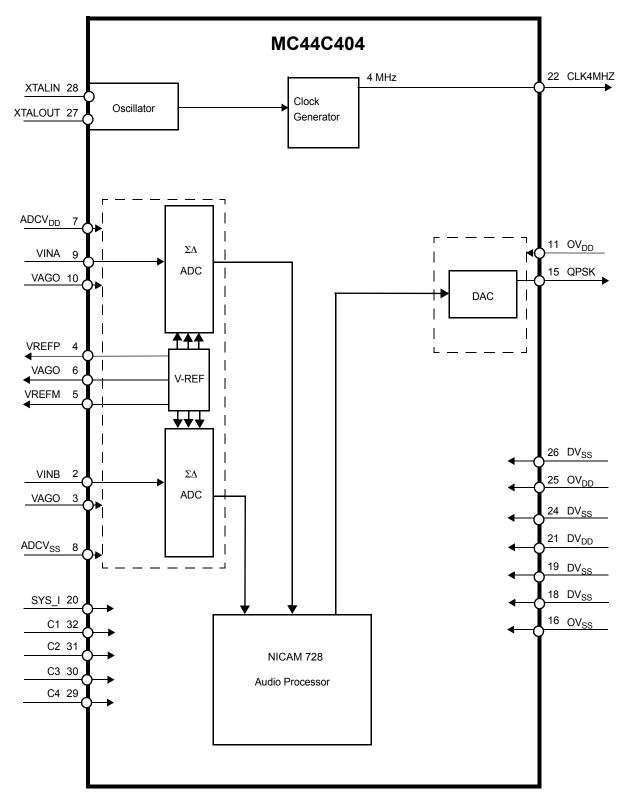

Figure 2. MC44C404 32-Lead TQFN Package

Table 1. Pin Descriptions (Listed by Function)

| Signal Name                           | Pin#                  | Description                                                                                                                                                                                                                  |

|---------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog                                | _                     |                                                                                                                                                                                                                              |

| VINA                                  | 9                     | A channel input                                                                                                                                                                                                              |

| VREFP                                 | 4                     | ADC voltage ref. bypass plus                                                                                                                                                                                                 |

| VAGO                                  | 3, 6, 10              | Analog virtual ground                                                                                                                                                                                                        |

| VREFM                                 | 5                     | ADC voltage ref. bypass minus                                                                                                                                                                                                |

| VINB                                  | 2                     | B channel input                                                                                                                                                                                                              |

| Digital                               |                       |                                                                                                                                                                                                                              |

| C1                                    | 32                    | Control inputs 1, 2 and 3.                                                                                                                                                                                                   |

| C2                                    | 31                    | See Table 2, Application Control Bits for setting these application control bits.                                                                                                                                            |

| C3                                    | 30                    |                                                                                                                                                                                                                              |

| C4                                    | 29                    | Control input 4 is the reserve sound switching flag.  C4 = 0: The analog signal is not carrying the same program as the digital signal.  C4 = 1: The analog sound signal is carrying the same program as the digital signal. |

| SYS_I                                 | 20                    | Output system format select.  SYS_I = 0: The output format is System B, G, H, K1 or L.  SYS_I = 1: The output format is System I.                                                                                            |

| QPSK                                  | 15                    | QPSK NICAM audio output                                                                                                                                                                                                      |

| NC                                    | 1, 12, 13, 14, 17, 23 | No connection                                                                                                                                                                                                                |

| Clocks                                |                       |                                                                                                                                                                                                                              |

| XTALIN                                | 28                    | Crystal oscillator input                                                                                                                                                                                                     |

| XTALOUT                               | 27                    | Crystal oscillator output                                                                                                                                                                                                    |

| CLK4MHZ                               | 22                    | 4 MHz clock output for Audio/Video modulator IC                                                                                                                                                                              |

| Power Supply                          | _                     |                                                                                                                                                                                                                              |

| ADCV <sub>DD</sub>                    | 7                     | ADC analog supply voltage, 3.3 V                                                                                                                                                                                             |

| ADCV <sub>SS</sub>                    | 8                     | ADC analog ground                                                                                                                                                                                                            |

| DV <sub>DD</sub>                      | 21                    | Digital logic supply voltage, 1.8 V                                                                                                                                                                                          |

| DV <sub>SS</sub> and OV <sub>SS</sub> | 16, 18, 19, 24, 26    | Digital logic/I/O ground                                                                                                                                                                                                     |

| OV <sub>DD</sub>                      | 11, 25                | I/O supply voltage, 3.3 V                                                                                                                                                                                                    |

**Table 2. Application Control Bits**

| C1 | C2 | C3 | Contents of the 704-Bit Sound/Data Blocks          |

|----|----|----|----------------------------------------------------|

| 0  | 0  | 0  | Stereo signal                                      |

| 0  | 1  | 0  | Two independent mono sound signals                 |

| 1  | 0  | 0  | One mono signal and one 352 Kbits/sec data channel |

| 1  | 1  | 0  | One 704 Kbits/sec data channel                     |

| Х  | Х  | 1  | Reserved                                           |

### **ELECTRICAL SPECIFICATIONS**

### **Table 3. Absolute Maximum Ratings**

Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

| Characteristic                | Symbol             | Min         | Max                    | Units |

|-------------------------------|--------------------|-------------|------------------------|-------|

| Digital Logic Supply Voltage  | $DV_DD$            | -0.3        | +2.0                   | V     |

| Digital Output Supply Voltage | $OV_{DD}$          | -0.3        | +4.0                   | V     |

| ADC Supply Voltage            | ADCV <sub>DD</sub> | -0.3        | +4.0                   | V     |

| Input Voltage                 | V <sub>in</sub>    | -0.3        | xV <sub>DD</sub> + 0.3 | V     |

| Storage Temperature Range     | T <sub>stg</sub>   | <b>-</b> 55 | +150                   | °C    |

### **Table 4. General Specifications**

| Characteristic                       | Symbol | Min  | Тур | Max | Units |

|--------------------------------------|--------|------|-----|-----|-------|

| ESD Protection (Charge Device Model) | CDM    | 500  | _   | _   | V     |

| ESD Protection (Human Body Model)    | HBM    | 2000 | _   | _   | V     |

| Latch-Up Immunity                    | LU     | 200  | _   | _   | mA    |

### **Table 5. Recommended Operating Conditions**

| Characteristic                | Symbol             | Min  | Тур | Max  | Units           |

|-------------------------------|--------------------|------|-----|------|-----------------|

| Digital Logic Supply Voltage  | $DV_DD$            | 1.62 | 1.8 | 1.98 | V               |

| Digital Output Supply Voltage | $OV_{DD}$          | 2.97 | 3.3 | 3.63 | V               |

| ADC Supply Voltage            | ADCV <sub>DD</sub> | 2.97 | 3.3 | 3.63 | V               |

| A/B Channel Input Level       | VINA, VINB         | _    | _   | 1.8  | V <sub>pp</sub> |

| Ambient Temperature           | T <sub>A</sub>     | 0    | _   | 70   | °C              |

### **Table 6. DC Characteristics**

| Characteristic <sup>(1)</sup>           | Symbol              | Min  | Тур | Max  | Units |

|-----------------------------------------|---------------------|------|-----|------|-------|

| Digital Logic Supply Current            | IDV <sub>DD</sub>   | _    | 7.5 | 8.5  | mA    |

| Digital Output Supply Current           | IOV <sub>DD</sub>   | _    | 2.0 | 8.0  | mA    |

| ADC Supply Current                      | IADCV <sub>DD</sub> | _    | 7.0 | 9.0  | mA    |

| ADC Voltage Ref. Bypass Plus            | VREFP               | _    | 2.0 | _    | V     |

| ADC Voltage Ref. Bypass Minus           | VREFM               | _    | 1.0 | _    | V     |

| ADC Voltage Ref. Ground                 | VAGO                | _    | 1.5 | _    | V     |

| CLK4MHZ, Clock Output Low @ I = 0.6 mA  | V <sub>ol</sub>     | 2.97 | _   | _    | V     |

| CLK4MHZ, Clock Output High @ I = 0.6 mA | V <sub>oh</sub>     | _    | _   | 3.63 | V     |

<sup>1.</sup> Unless other wise noted: DV<sub>DD</sub> = 1.8  $\pm$  0.18 Vdc, OV<sub>DD</sub> = ADCV<sub>DD</sub> = 3.3  $\pm$  0.33 Vdc, GND = 0 Vdc, 0  $\leq$  T<sub>A</sub>  $\leq$  70°C

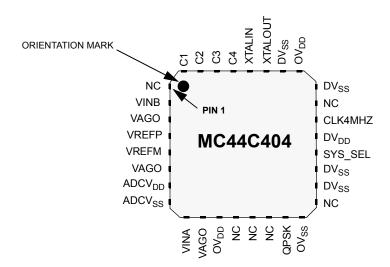

Table 7. AC Characteristics (Test setup as shown in Figure 3, MC44C404 Typical Application Circuit for B, G and H Systems)

| Characteristic <sup>(1)</sup>                | Symbol          | Min | Тур  | Max   | Units           |

|----------------------------------------------|-----------------|-----|------|-------|-----------------|

| Input Impedance (A/B Input)                  | R <sub>in</sub> | _   | 22   | _     | ΚΩ              |

| QPSK Audio Output Level <sup>(2)</sup>       |                 | _   | 0.85 | _     | V <sub>pp</sub> |

| QPSK Output Level                            |                 | _   | _    | 2.2   | V <sub>pp</sub> |

| Signal to Noise Ratio <sup>(2),(3)</sup>     | SNR             | 72  | 75   | _     | dB              |

| Total Harmonic Distortion <sup>(2),(3)</sup> | THD             | _   | 0.1  | 0.3   | %               |

| -1 dB Bandwidth                              | BW              | 20  | _    | 14500 | Hz              |

- 1. Unless other wise noted: DV<sub>DD</sub> = 1.8  $\pm$  0.18 Vdc, OV<sub>DD</sub> = ADCV<sub>DD</sub> = 3.3  $\pm$  0.33 Vdc, GND = 0 Vdc, 0  $\leq$  T<sub>A</sub>  $\leq$  70°C 2. Test conditions, mono, 1 kHz @ 1.5 V<sub>pp</sub>

- 3. Measured in 20 Hz to 13.5 kHz bandwidth

### SYSTEM APPLICATION NOTES

#### **DESIGN CONSIDERATIONS**

When developing an application using the MC44C404 NICAM Stereo Encoder, the user can significantly improve performance by following the suggestions below.

- There must be a notch in the video because video spectra that fall into the audio range will severely impact the audio performance.

- 2. A band pass filter is required on the QPSK output.

#### **Modulator Interface**

- The 4 MHz clock drive to the MC44BS373 must be filtered and the level set correctly. This can be achieved by using a Low Pass Filter (LPF), as shown in LPF1 in Figure 3, MC44C404 Typical Application Circuit for B, G and H Systems.

- 4. To set the application control bits see Table 1, Pin Descriptions (Listed by Function) and Table 2. **Application Control Bits**

Figure 3. MC44C404 Typical Application Circuit for B, G and H Systems

### MC44C404

6

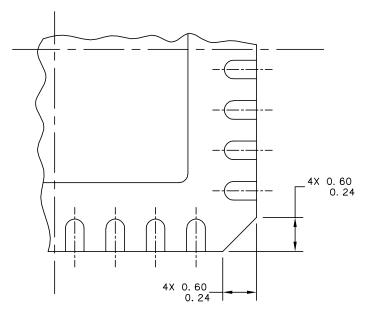

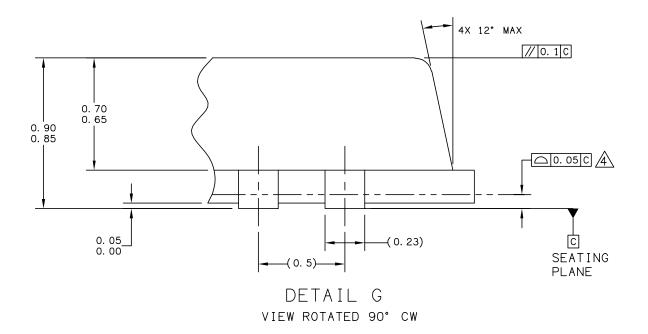

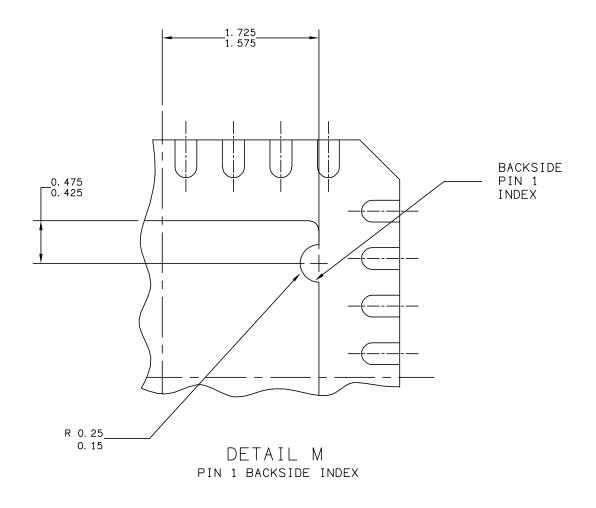

### **PACKAGE DATA**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.         | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|--------------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: THERMALLY ENHANCE                                     |           | DOCUMENT NO  | : 98ASA10560D    | REV: A      |

| FLAT NON-LEADED PACKAGE (QFN) 32 TERMINAL, 0.5 PITCH (5X5X1) |           | CASE NUMBER  | : 1457–01        | 07 JUN 2005 |

| CASE-OUTLIN                                                  |           | STANDARD: NO | N-JEDEC          |             |

DETAIL N

CORNER CONFIGURATION

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: THERMALLY ENHANCE                             | •         | DOCUMENT NO  | : 98ASA10560D    | REV: A      |

| FLAT NON-LEADED PACK<br>32 TERMINAL, 0.5 PIT         |           | CASE NUMBER  | : 1457–01        | 07 JUN 2005 |

| CASE-OUTLIN                                          |           | STANDARD: NO | N-JEDEC          |             |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.            | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|-----------------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: THERMALLY ENHANCE                                        |           | DOCUMENT NO  | : 98ASA10560D    | REV: A      |

| FLAT NON-LEADED PACKAGE (QFN)<br>32 TERMINAL, O.5 PITCH (5X5X1) |           | CASE NUMBER  | : 1457-01        | 07 JUN 2005 |

| CASE-OUTLIN                                                     |           | STANDARD: NO | N-JEDEC          |             |

### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFP-N.

- 4. COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| ELAT NON LEADED DACKACE (OEN)                        |           | DOCUMENT NO  | ): 98ASA10560D   | REV: A      |

|                                                      |           | CASE NUMBER  | R: 1457–01       | 07 JUN 2005 |

|                                                      |           | STANDARD: NO | N-JEDEC          |             |

### MC44C404

10 Freescale Semiconductor

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008. All rights reserved.