# HT6550 Super I/O Controller

#### **Features**

- 100% compatible to IBM PC AT/XT

- Fully uPD765b and IBM-BIOS compatible floppy disk controller

- 48mA floppy drive interface buffers

- Support two floppy drives with capability of supporting up to four drives with an external decoder

- Support 360K/720K/1.2M/1.44M formats

- Support 250Kb/s, 300Kb/s, 500Kb/s data rate

- Digital data separator eliminates critical analog adjustments

- Two 16450/8250 compatible UARTs

- Independent control of transmit, receive, line status and data set interrupts on each channel

- Individual modem control signals for each channel

- Programmable serial interface characteristics for each channel:

- # 5-, 6-, 7-, or 8-bit characters

- # Even,odd or no parity bit generation and detection

- #1-, 1.5-, or 2-stop bit generation

- Programmable baud rate generator for each channel which allows division of the timing reference clock input by 1 to  $(2^{16}-1)$

- Only one 24MHz crystal for FDC and UARTs

- One IBM PC AT/XT bidirection parallel port for printer

- One parallel bus mouse compatible to IBM, Logitech and Zwix Bus Mouse

- Support AT/XT Game port decode

- Support AT/XT hard disk IDE interface

- Hardware/software configuration setup available

- Individual disable feature available

- Power saving feature available

- 100 pin PQFP package

## **Applications**

• Super (Multi) I/O interface card

## **General Description**

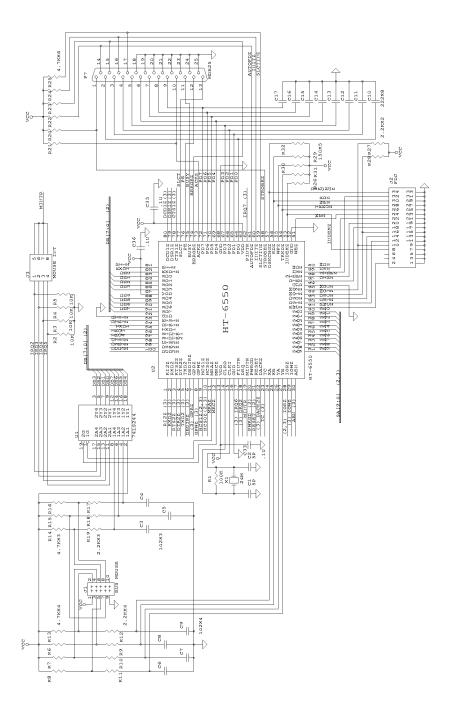

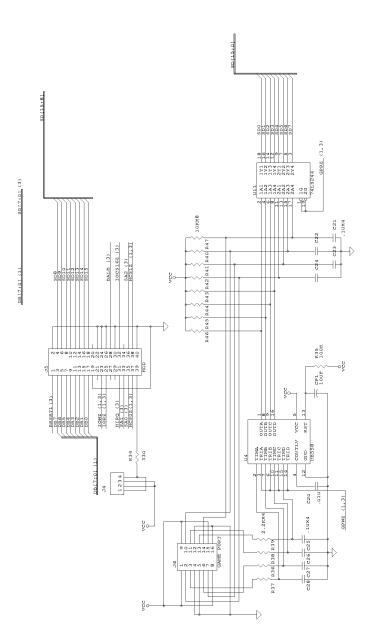

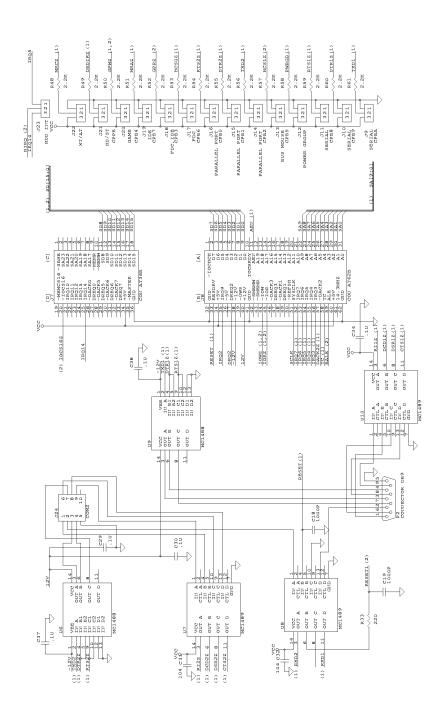

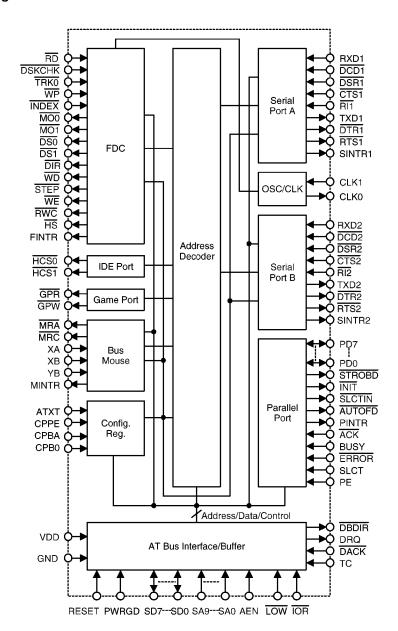

The HT6550 super Multi I/O chip, is an advanced CMOS single chip controller offering the complete I/O solutions for the IBM AT/XT environments. It incorporates one floppy disk controller (FDC), two full function UARTs, one parallel port, one bus mouse port, one game port controller, IDE hard disk drive interface, standard AT/XT address decoding for on-chip function and four configuration registers in one chip. It is fabricated with HOLTEK's high-reliability CMOS technology.

The HT6550 super Multi I/O chip contains one floppy disk controller which supports two floppy drives with capability of supporting up to four drives with an external decoder and is compatible to support 360K, 720K, 1.2M, 1.44M formats. Two full function UARTs of HT6550 which can be programmed serial interface characteristics for each channel, and a programmable baud rate generator is also included that can divide the timing reference clock input by a

divisor between 1 and  $(2^{16}-1)$  and can produce a 16X clock for driving the internal transmitter logic. Provisions are also included to use this 16X clock to drive the receiver logic.

The HT6550 also contains one parallel Bus Mouse controller which is compatible to IBM, Logitech and Zwix Bus Mouse and works with any application software which uses the Microsoft concept. It supports all Bus Mouse signal transfers and 4 IRQ selections.

The IDE (Intelligent Drive Electronics) port of HT6550 decoding strobes IDE type Winchester drives and supports data buffer. The Game port controller decoding strobes Game port for read and write. The HT6550 has 4 very flexible and easy to select configuration registers. It will be also easy to enable or disable any supported functions. For a cost effective and space efficient design, the HT6550 is packaged in an industry standard 100-pin EIA-J PQFP package.

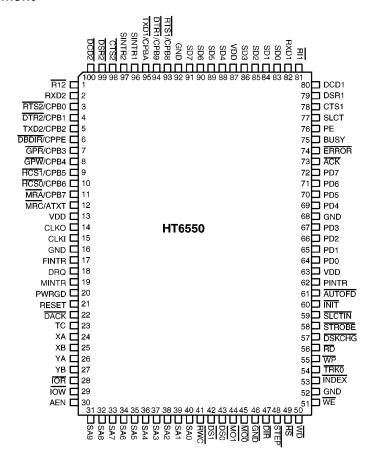

## **Pin Assignment**

3

## **Block Diagram**

## **Pin Description**

| Pin No.      | Pin Name | I/O        | Description                                                                                                         |

|--------------|----------|------------|---------------------------------------------------------------------------------------------------------------------|

|              |          | Host Inte  | rface (30 pins)                                                                                                     |

| 31~40        | SA9~SA0  | I          | Host address bus                                                                                                    |

| 83~86, 88~91 | SD0~SD7  | I/O        | Host data bus                                                                                                       |

| 28           | ĪOR      | I          | Active low I/O read                                                                                                 |

| 29           | ĪOW      | I          | Active low I/O write                                                                                                |

| 21           | RESET    | I          | Schmitt-trigger input reset from host                                                                               |

| 30           | AEN      | I          | DMA address enable active high                                                                                      |

| 22           | DACK     | I          | Active low DMA acknowledge from host                                                                                |

| 18           | DRQ      | О          | DMA request to host                                                                                                 |

| 23           | TC       | I          | Terminate DMA data transfer                                                                                         |

| 19           | MINTR    | О          | Mouse port interrupt request                                                                                        |

| 17           | FINTR    | О          | Floppy controller interrupt request                                                                                 |

| 96           | SINTR1   | О          | Serial port COM1 interrupt request                                                                                  |

| 97           | SINTR2   | О          | Serial port COM2 interrupt request                                                                                  |

| 62           | PINTR    | О          | Parallel port interrupt request                                                                                     |

|              | Par      | allel port | Interface (17 pins)                                                                                                 |

| 58           | STROBE   | О          | Data strobe, This signal indicates to the peripheral that the data at the parallel port is valid                    |

| 59           | SLCTIN   | О          | Line printer select, This signal is used to select the printer when it is low                                       |

| 60           | ĪNĪT     | О          | Printer initialize, This signal initializes the printer when it is low                                              |

| 61           | AUTOFD   | О          | Autofeed, When this output is low the printer should automatically line feed after each line printed                |

| 73           | ACK      | I          | Acknowledge. This signal is set low by the printer to indicate that it has received data and is ready for next data |

| 74           | ERROR    | I          | Printer error. This input is set by the printer when it has detected an error                                       |

| 75           | BUSY     | I          | Printer busy. This input is set high by the printer when it can't accept another character                          |

| 76           | PE       | I          | Paper empty. This input is set high by the printer when it is out of paper                                          |

| Pin No.      | Pin Name  | I/O       | Description                                                                                                                                                                                          |

|--------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 77           | SLCT      | I         | Printer select. This input is set by the printer when it is selected                                                                                                                                 |

| 64~67, 69~72 | PD0~PD7   | I/O       | Parallel port data bus                                                                                                                                                                               |

|              | Bus       | Mouse C   | Controller (6 pins)                                                                                                                                                                                  |

| 24           | XA        | I         | X-direction input from bus mouse                                                                                                                                                                     |

| 25           | XB        | I         | X-direction input from bus mouse                                                                                                                                                                     |

| 26           | YA        | I         | Y-direction input from bus mouse                                                                                                                                                                     |

| 27           | YB        | I         | Y-direction input from bus mouse                                                                                                                                                                     |

| 11           | MRA/CPB7  | I/O       | During normal operation this pin is mouse port A read signal. When RESET is high this pin becomes CPB7 input and reads data for IDE hardware setup                                                   |

| 12           | MRC/ATXT  | I/O       | During normal operation this pin is mouse port C read signal. When RESET is high this pin becomes AT/XT input and reads data for AT/XT mode selection, 1=AT mode, 0=XT mode                          |

|              |           | IDE Inte  | erface (2 pins)                                                                                                                                                                                      |

| 10           | HCS0/CPB6 | I/O       | During normal operation this pin is IDE port<br>enable to enable 1F0-1F7H/170-177H (AT), 320-<br>323H(XT)<br>When RESET is high this pin becomes CPB6<br>input and reads data for FDC hardware setup |

| 9            | HCS1/CPB5 | I/O       | During normal operation this pin is IDE port enable to enable 3F6-3F7H/376-377H When RESET is high this pin becomes CPB5 input and reads data for bus mouse hardware setup                           |

|              | Ga        | me port I | nterface (2 pins)                                                                                                                                                                                    |

| 7            | GPR/CPB3  | I/O       | During normal operation this pin is game port read signal When RESET is high this pin becomes CPB3 input and reads data for FDC, IDE hardware setup                                                  |

| 8            | GPW/CPB4  | I/O       | During normal operation this pin is game port write signal When RESET is high this pin becomes CPB4 input and reads data for game port hardware setup                                                |

|              | F         | loppy Int | erface (15 pins)                                                                                                                                                                                     |

| Pin No. | Pin Name                  | I/O          | Description                                                                                                                                          |  |  |

|---------|---------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 45      | MO0                       | О            | FDD motor A enable, active low open drain output                                                                                                     |  |  |

| 44      | MO1                       | О            | FDD motor B enable, active low open drain output                                                                                                     |  |  |

| 43      | $\overline{\mathrm{DS0}}$ | О            | FDD drive A enable, active low open drain output                                                                                                     |  |  |

| 42      | $\overline{\mathrm{DS1}}$ | О            | FDD drive B enable, active low open drain output                                                                                                     |  |  |

| 47      | DIR                       | О            | Direction of the head stepper motor, open drain output, 1=outward, 0=inward motion movement                                                          |  |  |

| 50      | $\overline{ m WD}$        | 0            | Write data, active low open drain output                                                                                                             |  |  |

| 48      | $\overline{\text{STEP}}$  | О            | Step output pulses, active low open drain output                                                                                                     |  |  |

| 51      | $\overline{ m WE}$        | О            | Enable write to FDD, active low open drain output                                                                                                    |  |  |

| 41      | RWC                       | О            | Reduced write current, open drain output used to select the transfer rate, 0=250 Kb/s, 1=500 Kb/s                                                    |  |  |

| 49      | HS                        | 0            | Head select, open drain output                                                                                                                       |  |  |

| 56      | $\overline{	ext{RD}}$     | I            | Read data from FDD, schmitt-trigger input                                                                                                            |  |  |

| 57      | DSKCHG                    | I            | Diskette change, schmitt-trigger input                                                                                                               |  |  |

| 54      | TRK0                      | I            | Track 00, head is on track 0, schmitt-trigger input                                                                                                  |  |  |

| 55      | WP                        | I            | Write protected, schmitt-trigger input                                                                                                               |  |  |

| 53      | INDEX                     | I            | FDC index,indicates the beginning of a disk track                                                                                                    |  |  |

|         | Se                        | rial port ii | nterface (16 pins)                                                                                                                                   |  |  |

| 78      | $\overline{\text{CTS1}}$  | I            | Serial 1 clear to send input, active low                                                                                                             |  |  |

| 79      | DSR1                      | I            | Serial 1 data set ready input, active low                                                                                                            |  |  |

| 80      | $\overline{	ext{DCD1}}$   | I            | Serial 1 data carrier detect input, active low                                                                                                       |  |  |

| 81      | RI1                       | I            | Serial 1 ring indicator input active low                                                                                                             |  |  |

| 82      | RXD1                      | I            | Serial 1 receive data input                                                                                                                          |  |  |

| 93      | RTS1/CPB8                 | I/O          | During normal operation this pin is serial 1 request to send. When RESET is high this pin becomes CPB8 input and reads data for UARTs hardware setup |  |  |

| 94      | DTR1/CPB9                 | I/O          | During normal operation this pin is serial 1 daterminal ready. When RESET is high this pecomes CPB9 input and reads data for UAR hardware setup      |  |  |

| Pin No.         | Pin Name                   | I/O       | Description                                                                                                                                                                                            |

|-----------------|----------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95              | TXD1/CPBA                  | I/O       | During normal operation this pin is serial 1 transmit data. When RESET is high this pin becomes CPBA input and reads data for UARTs hardware setup                                                     |

| 98              | $\overline{\text{CTS2}}$   | I         | Serial 2 clear to send input, active low                                                                                                                                                               |

| 99              | $\overline{\mathrm{DSR2}}$ | I         | Serial 2 data set ready input, active low                                                                                                                                                              |

| 100             | $\overline{	ext{DCD2}}$    | I         | Serial 2 data carrier detect input, active low                                                                                                                                                         |

| 1               | RI2                        | I         | Serial 2 ring indicator input, active low                                                                                                                                                              |

| 2               | RXD2                       | I         | Serial 2 receive data input                                                                                                                                                                            |

| 3               | RTS2/CPB0                  | I/O       | During normal operation this pin is serial 2 request to send. When RESET is high this pin becomes CPB0 input and reads data for parallel port hardware setup                                           |

| 4               | DTR2/CPB1                  | I/O       | During normal operation this pin is serial 2 data terminal ready. When RESET is high this pin becomes CPB1 input and reads data for parallel port hardware setup                                       |

| 5               | TXD2/CPB2                  | I/O       | During normal operation this pin is serial 2 transmit data. When RESET is high this pin becomes CPB2 input and reads data for parallel port hardware setup                                             |

|                 | I                          | Miscellan | eous (12 pins)                                                                                                                                                                                         |

| 6               | DBDIR/CPPE                 | I/O       | During normal operation this pin is data bus direction control sIgnal When RESET is high this pin becomes CPPE input and reads data for configuration setup select. 1=software setup, 0=hardware setup |

| 20              | PWRGD                      | I         | HT6550 is fully function when PWRGD is high<br>If PWRGD is low and VDD still active then<br>HT6550 is isolated from the reset of the circuit, all<br>inputs are disabled and all outputs tri-stated    |

| 15              | CLKI                       | I         | Oscillator input (24 MHz)                                                                                                                                                                              |

| 14              | CLKO                       | О         | Oscillator driver output                                                                                                                                                                               |

| 13,63,87        | VDD                        | I         | +5V supply                                                                                                                                                                                             |

| 16,46,52, 68,92 | GND                        | I         | Ground                                                                                                                                                                                                 |

## **Absolute Maximum Ratings**

| Supply voltage0.3V to 5.5V                                       | Storage temperature–50°C to 125°C |

|------------------------------------------------------------------|-----------------------------------|

| Input/Output voltageV <sub>SS</sub> —0.3 to V <sub>DD</sub> +0.3 | Operating temperature0°C to 70°C  |

## **Electrical Characteristics**

## DC Characteristics $(V_{DD}=5V, TA=25^{\circ}C)$

| (186-61, 111-26         |                             |                                       |       |        |                   |      |  |

|-------------------------|-----------------------------|---------------------------------------|-------|--------|-------------------|------|--|

| Symbol                  | Parameter                   | Test Conditions                       | Min.  | Тур.   | Max.              | Unit |  |

|                         | Host Interface (SD0~SD7, DR | Q, MINTR, FINTR, SINTR1,              | SINT  | R2 PIN | ΓR)               |      |  |

| $V_{\mathrm{OLB}}$      | Output Low Voltage          | I <sub>OL</sub> =10mA                 | _     | _      | 0.4               | V    |  |

| $V_{\mathrm{OHB}}$      | Output High Voltage         | I <sub>OH</sub> =-2mA                 | 2.4   | _      | $V_{\mathrm{DD}}$ | V    |  |

| т                       | I all a Camara              | V <sub>IN</sub> =5V                   | _     | _      | 10                | μΑ   |  |

| $I_{LOB}$               | Leakage Current             | V <sub>IN</sub> =0V                   | _     | _      | -10               | μА   |  |

|                         | C                           | lock Input (CLKI)                     |       |        | !                 | •    |  |

| $V_{\rm ILX}$           | Clock Input Low Voltage     | _                                     | -0.3  | _      | 0.8               | V    |  |

| $V_{\rm IHX}$           | Clock Input High Voltage    | _                                     | 2     | _      | $V_{\mathrm{DD}}$ | V    |  |

| Floppy Interface Output |                             |                                       |       |        |                   |      |  |

| $V_{\mathrm{OLF}}$      | Output Low Voltage          | I <sub>OL</sub> =48mA                 | _     | _      | 0.4               | V    |  |

| IDE Interface Output    |                             |                                       |       |        |                   |      |  |

| $V_{\mathrm{OLH}}$      | Output Low Voltage          | I <sub>OL</sub> =10mA                 | _     | _      | 0.4               | V    |  |

| $v_{\mathrm{OHH}}$      | Output High Voltage         | I <sub>OH</sub> =-2mA                 | 2.4   | _      | $V_{\mathrm{DD}}$ | v    |  |

| $I_{LOH}$               | Leakage Current             | V <sub>IN</sub> =V <sub>DD</sub>      | _     | _      | 10                | μА   |  |

| $I_{ m LOL}$            | Leakage Current             | V <sub>IN</sub> =0                    | _     |        | -10               | μА   |  |

|                         | Para                        | llel Interface Output                 |       |        |                   | •    |  |

| $V_{\mathrm{OL}}$       | Output Low Voltage          | I <sub>OL</sub> =10mA                 | _     | _      | 0.4               | V    |  |

| $V_{\mathrm{OH}}$       | Output High Voltage         | I <sub>OH</sub> =-2mA                 | 2.4   | _      | $V_{\mathrm{DD}}$ | v    |  |

|                         | Bus Mouse, Flor             | ppy Interface Input and RES           | ET    | •      |                   | •    |  |

| $V_{\rm ILM}$           | Input Low Voltage           | _                                     | -0.3  | _      | 0.8               | V    |  |

| $V_{IHM}$               | Input High Voltage          | _                                     | 2.4   | _      | $V_{\mathrm{DD}}$ | V    |  |

| $V_{\mathrm{H}}$        | Input Hysteresis            | _                                     | 0.25  | _      | _                 | V    |  |

|                         | Game Port, Bus Mous         | e, UART Interface output an           | d DBD | ĪR     |                   |      |  |

| $V_{\rm OLG}$           | Output Low Voltage          | I <sub>OL</sub> =2mA                  | _     | _      | 0.4               | V    |  |

| $V_{\mathrm{OHG}}$      | Output High Voltage         | I <sub>OH</sub> =-400μA               | 2.4   |        | $V_{\mathrm{DD}}$ | V    |  |

| All Other Input         |                             |                                       |       |        |                   |      |  |

| $V_{\mathrm{IL}}$       | Input Low Voltage           | _                                     | -0.3  | _      | 0.8               | V    |  |

| $V_{\mathrm{IH}}$       | Input High Voltage          | _                                     | 2.4   |        | $V_{\mathrm{DD}}$ | V    |  |

| $ m V_{LIH}$            | Input Leakage Current       | $V_{\mathrm{IN}}$ = $V_{\mathrm{DD}}$ | _     |        | 10                | μА   |  |

| $V_{ m LIL}$            | Input Leakage Current       | V <sub>IN</sub> =0                    | _     | _      | -10               | μA   |  |

## **AC Characteristics**

$(V_{DD}=5V, TA=25^{\circ}C)$

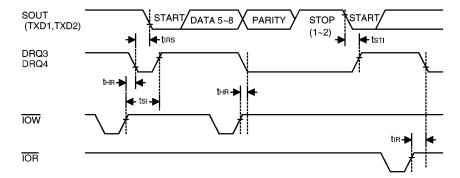

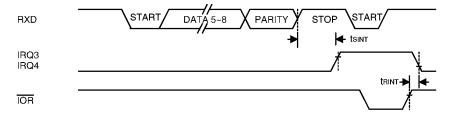

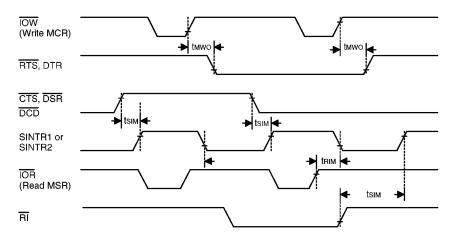

## • UART/PARALLEL

| Symbol                | Parameter                                              | Test<br>Conditions | Min. | Тур. | Max.         | Unit         |

|-----------------------|--------------------------------------------------------|--------------------|------|------|--------------|--------------|

| $	ext{T}_{	ext{IRS}}$ | Delay From Initial IRQ Reset To<br>Transmit Start      | _                  | 1/16 |      | 8/16         | Baud<br>Rate |

| ${ m T_{STI}}$        | Delay From Stop To Interrupt                           | _                  | 9/16 | _    | _            | Baud<br>Rate |

| $T_{ m HR}$           | Delay From $\overline{\text{IOW}}$ To Reset Interrupt  | 100pf Loading      | _    |      | 175          | $_{ m ns}$   |

| $T_{ m SI}$           | Delay From Initial $\overline{	ext{IOW}}$ To Interrupt | _                  | 9/16 | _    | 16/16        | Baud<br>Rate |

| $\mathrm{T_{IR}}$     | Delay From $\overline{\text{IOR}}$ To Reset            | 100pf Loading      | _    |      | 1            | $_{ m ns}$   |

| $T_{ m SINT}$         | Delay From Stop To Set Interrupt                       |                    | _    | _    | 1/2          | Baud<br>Rate |

| $T_{ m RINT}$         | Delay Form $\overline{\text{IOR}}$ Reset Interrupt     | 100pf Loading      | _    |      | 250          | $_{ m ns}$   |

| $T_{ m MWO}$          | Delay From $\overline{\mathrm{IOW}}$ To Output         | 100pf Loading      | _    |      | 200          | $_{ m ns}$   |

| $T_{ m SIM}$          | Set Interrupt Delay From MODEM<br>Input                | 100pf Loading      | _    | _    | 250          | ns           |

| $T_{ m RIM}$          | Reset Interrupt Delay From $\overline{	ext{IOR}}$      | 100pf Loading      | _    |      | 250          | ns           |

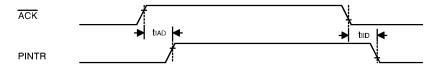

| $T_{OAD}$             | Interrupt Active Delay                                 | 100pf Loading      | _    | _    | 30           | ns           |

| $\mathrm{T_{IID}}$    | Interrupt Inactive Delay                               | 100pf Loading      | _    |      | 30           | ns           |

| N                     | Baud Rate Divisor                                      | 100pf Loading      | _    | _    | $2^{16} - 1$ | unit         |

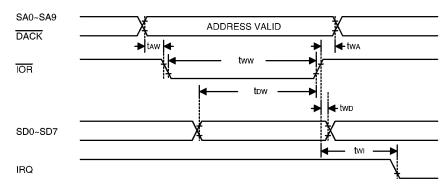

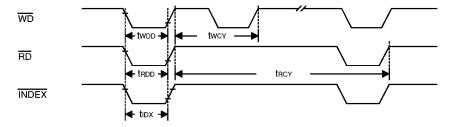

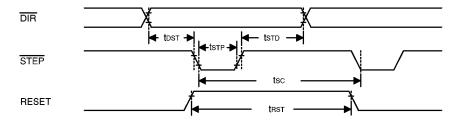

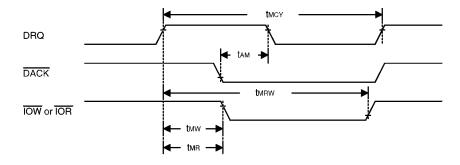

## • FDC: Data rate= 500 /300 /250 KB/SEC

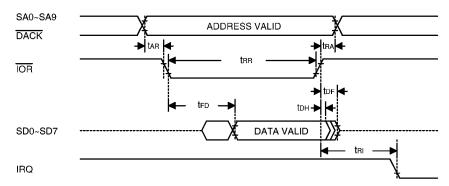

| Symbol                     | Parameter                                                                                | Test<br>Conditions | Min. | Тур.* | Max. | Unit |

|----------------------------|------------------------------------------------------------------------------------------|--------------------|------|-------|------|------|

| $\mathrm{T_{AR}}$          | $SA9$ –SA0, AEN, $\overline{DACK}$ Setup Time To $\overline{IOR} \downarrow$             | _                  | 25   | _     | _    | ns   |

| $\mathrm{T}_{\mathrm{RA}}$ | $\frac{SA9 - SA0, AEN, \overline{DACK} \text{ Hold Time From}}{\overline{IOR} \uparrow}$ | 100pf Loading      | 0    | _     | _    | ns   |

| $T_{ m RR}$                | IOR Width                                                                                | 100pf Loading      | 200  | _     | _    | ns   |

| $\mathrm{T_{FD}}$          | Data Access Time From $\overline{	ext{IOR}}\downarrow$                                   | 100pf Loading      | _    | _     | 80   | ns   |

| $T_{ m DH}$                | Data Hold Time From $\overline{	ext{IOR}}\downarrow$                                     |                    | 10   | _     |      | ns   |

| $T_{ m DF}$                | SD To Float From <del>IOR</del> ↑                                                        | _                  | 10   | _     | 50   | ns   |

| Symbol                     | Parameter                                                                                 | Test<br>Conditions | Min.                | Тур.* | Max.                | Unit |

|----------------------------|-------------------------------------------------------------------------------------------|--------------------|---------------------|-------|---------------------|------|

| $	ext{T}_{	ext{RI}}$       | IRQ Delay From <del>IOR</del> ↑                                                           | _                  | _                   | _     | 360/<br>570/<br>675 | ns   |

| $\mathrm{T}_{\mathrm{AW}}$ | $SA9$ – $SA0$ , AEN, $\overline{DACK}$ Setup Time To $\overline{IOW}$ $\downarrow$        | _                  | 25                  | _     |                     | ns   |

| $T_{ m WA}$                | $\frac{SA9{-}SA0, AEN, \overline{DACK} \text{ Hold Time From }}{\overline{IOW}} \uparrow$ | _                  | 0                   | _     |                     | ns   |

| $T_{WW}$                   | IOW Width                                                                                 | _                  | 200                 | _     |                     | ns   |

| $T_{\mathrm{DW}}$          | Data Setup Time To <del>IOW</del> ↑                                                       | _                  | 60                  | _     |                     | ns   |

| $T_{ m WD}$                | Data Hold Time From $\overline{	ext{IOW}}$ $\uparrow$                                     | _                  | 0                   | _     | _                   | ns   |

| $\mathrm{T_{WI}}$          | IRQ Delay From <del>IOW</del> ↑                                                           | _                  | _                   | _     | 360/<br>570/<br>675 | ns   |

| $T_{MCY}$                  | DMA Cycle Time                                                                            | <del></del>        | 27                  | _     | _                   | μs   |

| $T_{AM}$                   | DMA Reset Delay Time From $\overline{\mathrm{DACK}}\downarrow$                            |                    | _                   | _     | 50                  | ns   |

| $T_{MA}$                   | $\overline{\mathrm{DRQ}}$ To $\overline{\mathrm{DACK}}$ Delay                             |                    | 0                   | _     |                     | ns   |

| $\mathrm{T}_{\mathrm{AA}}$ | DACK Width                                                                                | _                  | 260/<br>430/<br>510 | _     | _                   | ns   |

| $T_{ m MR}$                | TOR Delay From DRQ                                                                        | _                  | 0                   | _     | _                   | ns   |

| $T_{MW}$                   | IOW Dleay From DRQ                                                                        | <u>—</u>           | 0                   | _     |                     | ns   |

| ${ m T_{MRW}}$             | $\overline{10W}$ Or $\overline{10R}$ Response Time From DRQ                               | _                  | _                   | _     | 12/<br>20<br>24     | μs   |

| ${ m T_{TC}}$              | TC Width                                                                                  | _                  | 135/<br>220/<br>260 | _     | _                   | ns   |

| ${ m T}_{ m RST}$          | RESET Width                                                                               | _                  | 1.8/<br>3.0/<br>3.5 | _     | _                   | μs   |

| $\mathrm{T_{IDX}}$         | INDEX Width                                                                               | _                  | 0.5/<br>0.9/<br>1.0 | _     | _                   | μs   |

| $T_{ m DST}$               | DIR Setup Time To STEP                                                                    | _                  | 1.0/<br>1.6/<br>2.0 | _     | _                   | μs   |

| Symbol                      | Parameter                                               | Test<br>Conditions | Min.                  | Тур.*               | Max.                  | Unit |

|-----------------------------|---------------------------------------------------------|--------------------|-----------------------|---------------------|-----------------------|------|

| ${ m T_{STD}}$              | $\overline{ m DIR}$ Hold Time From $\overline{ m STEP}$ | _                  | 24/<br>40/<br>48      | _                   |                       | μs   |

| ${ m T}_{ m STP}$           | STEP Pulse Width                                        | _                  | 6.8/<br>11.5/<br>13.8 | 7.0/<br>11.7/<br>14 | 7.2/<br>11.9/<br>14.2 | μs   |

| $T_{SC}$                    | STEP Cycle Time                                         | _                  | **                    | **                  | **                    | μs   |

| $\mathrm{T}_{\mathrm{WDD}}$ | WD Pulse Width                                          | _                  | 100/<br>188/<br>225   | 125/<br>210/<br>250 | 150/<br>235/<br>275   | ns   |

| $T_{\mathrm{WPC}}$          | Write Precompensation                                   | _                  | 100/<br>138/<br>225   | 125/<br>210/<br>250 | 150/<br>235/<br>275   | μs   |

## Notes:

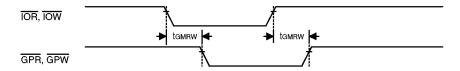

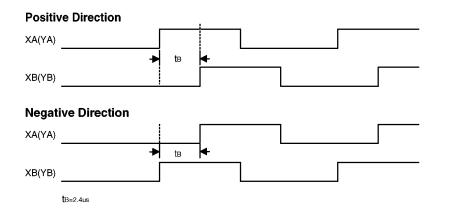

## • Game port & bus mouse

| Symbol           | Parameter                                        | Min. | Тур. | Max. | Unit                   |

|------------------|--------------------------------------------------|------|------|------|------------------------|

| $T_{ m GMRW}$    | Game Command delay time from RD/WR Game Port     | _    | _    | 150  | $\mathbf{n}\mathbf{s}$ |

| $T_{\mathrm{B}}$ | Bus Mouse delay time between XA (YA) AND XB (YB) | _    | 2.4  | _    | μs                     |

<sup>\*</sup> Typical ns values for TA=25°C and nominal value for supply voltage.

$<sup>\</sup>ensuremath{^{**}\text{Programmable}}$  from 2ms to 32ms in 2ms increments.

## **Functional Description**

#### I/O Port Address

| Function       | * Possible Port Address                                | Comment                           |

|----------------|--------------------------------------------------------|-----------------------------------|

| Serial port 1  | 3F8—3FFH<br>3E8—3EFH                                   | COM1<br>COM3                      |

| Serial port 2  | 2F8—2FFH<br>2E8—2EFH                                   | COM2<br>COM4                      |

| Parallel port  | 3BC—3BFH<br>378—37BH<br>278—27BH                       | PRT1<br>PRT2<br>PRT3              |

| FDC port       | 3F2, 3F4, 3F5, 3F7, 1F7H<br>372, 374, 375, 377, 177H   | FDC1<br>FDC2                      |

| IDE port       | 1F0—1F7H, 3F6, 3F7H<br>170—177H, 376, 377H<br>320—323H | IDE1 (AT)<br>IDE2 (AT)<br>** (XT) |

| Bus mouse port | 23C—23EH                                               |                                   |

| Game port      | 201H                                                   |                                   |

<sup>\*</sup> These ports are selected by configuration registers.

#### • Configuration setup

There are four configuration registers CR # 00,01,02,0FH which are write only. CR# 00,01H can be either hardware or software setup, CR# 02,0FH can only be accessed through software. Pin 6 CPPE is used to select hardware/software system setup during the RESET. Hardware setup when CPPE is low level and software setup when CPPE is high level.

#### \* Hardware setup

CPPE low indicates hardware setup for CR# 00H and CR# 01H. During RESET goes high, the HT6550 will read the inputs from the following pins and setup the configuration registers CR# 00H and CR# 01H.

| Pin<br>Name | СРВА | СРВ9 | СРВ8 | СРВ7 | СРВ6 | CPB5 | СРВ4 | СРВЗ | CPB2 | СРВ1 | СРВО |

|-------------|------|------|------|------|------|------|------|------|------|------|------|

| Pin<br>No.  | 95   | 94   | 93   | 11   | 10   | 9    | 8    | 7    | 5    | 4    | 3    |

<sup>\*\*</sup> AT/XT mode is selected by AT/XT (pin 12) during RESET.

Note: CPBA-CPB8: Serial port selection

| СРВА | СРВ9 | CPB8 | UART1           | UART2           |  |

|------|------|------|-----------------|-----------------|--|

| 0    | 0    | 0    | disable         | disable         |  |

| 0    | 0    | 1    | COM1 (3F8–3FFH) | disable         |  |

| 0    | 1    | 0    | disable         | COM2 (2F8–2FFH) |  |

| 0    | 1    | 1    | COM1 (3F8–3FFH) | COM2 (2F8–2FFH) |  |

| 1    | 0    | 0    | COM3 (3E8–3EFH) | COM4 (2E8–2EFH) |  |

| 1    | 0    | 1    | disable         | COM1 (3F8–3FFH) |  |

| 1    | 1    | 0    | COM2 (2F8–2FFH) | disable         |  |

| 1    | 1    | 1    | COM2 (2F8–2FFH) | COM1 (3F8–3FFH) |  |

CPB7: IDE enable. 0=disable, 1=enable.

CPB6: FDC enable. 0=disable, 1=enable.

CPB5: MOUSE enable. 0=disable, 1=enable.

CPB4: GAME enable. 0=disable, 1=enable.

CPB3: Secondary IDE,FDC selection. 0=secondary selected, 1=primary selected.

CPB2: Printer mode selection 0=extended mode, 1=normal mode.

CPB1,0: Parallel port selection.

| CPB1 | СРВО | Parallel port   |  |  |  |

|------|------|-----------------|--|--|--|

| 0    | 0    | disable         |  |  |  |

| 0    | 1    | PRT1 (3BC—3BFH) |  |  |  |

| 1    | 0    | PRT2 (378—37BH) |  |  |  |

| 1    | 1    | PRT3 (278—27BH) |  |  |  |

#### \* Software setup

CPPE high indicates software setup. After RESET the default values will be loaded into the configuration registers.

The procedures for setting up the configuration registers are described as follow:

- To enter configuration mode:

- # Write 55H to 2FAH.

- # Follow by writing AAH to 3FAH.

- To program configuration register:

- # Write XXH to 3FAH, where XXH is the configuration register index.

- # Follow by writing YYH to 2FAH, where YYH is the data for CR# XXH.

- To exit from configuration mode:

- # Write 0FH to 3FAH, then write any value YYH to 2FAH.

- # or write AAH to 3FAH.

The following describes the bit functions of each configuration registers (CR# 00, 01, 02 and 0FH)

### \* Configuration register — CR# 00H (write only)

| Bit No. | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | CPB7 | CPB6 | CPB5 | CPB4 | CPB3 | CBP2 | CPB1 | CPB0 |

Note:

CPB7: IDE enable. 0=disable, 1=enable (default).

CPB6: FDC enable. 0=disable, 1=enable (default).

CPB5: Mouse enable. 0=disable, 1=enable (default).

CPB4: GAME enable. 0=disable, 1=enable (default).

CPB3: Secondary IDE, FDC selection. 0=secondary selected, 1= primary selected

(default).

CPB2: Printer mode selection. 0=extended mode, 1=normal mode (default).

CPB1,0: Parallel port selection.

| CPB1 | СРВ0 | Paralled port             |

|------|------|---------------------------|

| 0    | 0    | disable                   |

| 0    | 1    | PRT1 (3BC–3BFH)           |

| 1    | 0    | PRT2 (378–37BH) (default) |

| 1    | 1    | PRT3 (278–27BH)           |

### \* Configuration register — CR# 01H(Write only)

| Bit No. | b7 | b6 | b5 | b4 | b3 | b2   | b1   | b0   |  |

|---------|----|----|----|----|----|------|------|------|--|

| Symbol  | _  |    | _  | _  | _  | CPBA | CPB9 | CPB8 |  |

Note: CPBA~CPB8: Serial port selection.

| СРВА | СРВ9 | CPB8 | UART1                    | UART2                     |  |  |

|------|------|------|--------------------------|---------------------------|--|--|

| 0    | 0    | 0    | disable                  | disable                   |  |  |

| 0    | 0    | 1    | COM1 (3F8–3FFH)          | disable                   |  |  |

| 0    | 1    | 0    | disable                  | COM2 (2F8–2FFH)           |  |  |

| 0    | 1    | 1    | COM1 (3F8–3FFH)(default) | COM2 (2F8–2FFH) (default) |  |  |

| 1    | 0    | 0    | COM3 (3E8–3EFH)          | COM4 (2E8–2EFH)           |  |  |

| 1    | 0    | 1    | disable                  | COM1 (3F8–3FFH)           |  |  |

| 1    | 1    | 0    | COM2 (2F8–2FFH)          | disable                   |  |  |

| 1    | 1    | 1    | COM2 (2F8–2FFH)          | COM1 (3F8–3FFH)           |  |  |

## \* Configuration register — CR# 02H (Write only)

| Bit N | Vo. | b7  | b6                     | b5                     | b4                     | b3                     | b2                     | b1                     | b0 |

|-------|-----|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|----|

| Sym   | bol | ENB | $\overline{	ext{MPD}}$ | $\overline{	ext{PDD}}$ | $\overline{	ext{SPD}}$ | $\overline{	ext{FPD}}$ | $\overline{	ext{HPD}}$ | $\overline{	ext{GPD}}$ | _  |

Where

GPD:

ENB: 1=valid configuration setup

MPD: Mouse port power down, 0=power down, 1=normal (default)

PDD: Printer port power down, 0=power down, 1=normal (default)

SPD: Serial port power down, 0=power down, 1=normal (default)

FPD: Floppy disk port power down, 0=power down, 1=normal (default)

HPD: IDE port power down, 0=power down, 1=normal (default)

\* Configuration register — CR# 0FH (Write only)

Writing any value to CR# 0FH can bring the HT6550 out of the configuration mode.

Game port power down,0=power down, 1=normal (default)

#### Serial port

The serial ports of HT6550 are fully compatible to the 16450/8250 ACE register. The programmable features allows data rates ranging from 50 baud to 56K baud; they also provide 5 to 8-bit character size with 1 start bit and 1/1.5/2 stop bits; even/odd/sticky/no parity of parity check; and prioritized interrupts.

There are three types of internal registers that used in each channel. They are control, status and data registers. The control registers are the Bit Rate Select Register DLL (Divisor latch LSB), DLM (Divisor latch MSB), LCR (Line Control Register), IER (Interrupt Enable Register), and MCR (Modem Control Register). The status registers are the LSR (Line Status Register) and MSR (Modem Status Register). The

data registers are the RBR (Receiver Buffer Register) and the THR (Transmitter Holding Register). The divisor latch access bit (DLAB) in the Line Control Register (LCR) is used to decide which register to be accessed during a read or write operation. See Table 1 for the details.

The Transmitter Buffer Register (TBR) and Receiver Buffer Register (RBR) are data registers holding from five to eight bits of data. If less than eight data bits are transmitted, data is right justified to the LSB. Bit 0 of a data word is always the first serial data bit received and transmitted. The data registers of HT6550 are double-buffered so that all read, write operations and serial-to-parallel, paralled-to-serial conversion can be performed at the same time.

| DLAB | COM1 | COM2 | сомз | COM4 | Read | Write |

|------|------|------|------|------|------|-------|

| 0    | 3F8H | 2F8H | 3E8H | 2E8H | RBR  | THR   |

| 0    | 3F9H | 2F9H | 3E9H | 2E9H | IER  | IER   |

| 0    | 3FAH | 2FAH | зЕАН | 2EAH | IIR  | _     |

| X    | 3FBH | 2FBH | зЕВН | 2EBH | LCR  | LCR   |

| X    | 3FCH | 2FCH | зЕСН | 2ECH | MCR  | MCR   |

| X    | 3FDH | 2FDH | 3EDH | 2EDH | LSR  | LCR   |

| X    | 3FEH | 2FEH | зеен | 2EEH | MSR  | MSR   |

| X    | 3FFH | 2FFH | 3EFH | 2EFH | SCR  | SCR   |

| 1    | 3F8H | 2F8H | 3E8H | 2E8H | DLL  | DLL   |

| 1    | 3F9H | 2F9H | 3E9H | 2E9H | DLM  | DLM   |

X: means "don't care"

Table 1. Serial Channel Internal Registers

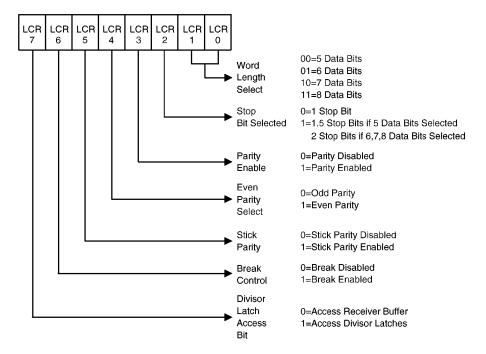

#### • Line control register (LCR)

The system programmer specifies the format of the asynchronous data communication exchange through the Line Control Register and sets the Divisor latch access bit via the Line Control Register (LCR). In addition to controlling the format, the programmer may be read the contents of the Line Control Register for inspection. The contents of the LCR are described as follow.

Figure 1. Line Control Register

## Note:

$LCR(0\sim1)$ : Specify the number of bits in each serial character that is sent or received. The encoding of LCR(0) and LCR(1) is as follows:

| LCR (1) | LCR (0) | Word Length |

|---------|---------|-------------|

| 0       | 0       | 5           |

| 0       | 1       | 6           |

| 1       | 0       | 7           |

| 1       | 1       | 8           |

LCR(2): Specifies the number of stop bits in each serial character that is sent or received. If LCR(2) is in logic 0, one stop bit is generated or checked in the data sent or received. If LCR(2) is logic 1 when a 5-bit word length is

selected through LCR(0) and LCR(1), one and a half stop bits are generated or checked. If LCR(2) is in logic 1 when either a 6, 7, or 8-bit word length is selected, 2 stop bits are generated or checked.

LCR(3): Specifies the parity enable. When LCR(3) is logic 1, a parity bit is generated (transmit data mode) or checked (receive data mode) between the last data word and stop bit of the serial data.

Note: The parity bit is used to product an even or odd number of 1's when the data-word bits and parity bit are summed.

LCR(4): Specifies the even parity select. When LCR(3) is in logic 1 and LCR(4) is in logic 0, an odd number of logic 1's is sent or checked in the data word bits and parity bit. When LCR(3) is in logic 1 and LCR(4) is in logic 1, an even number of logic 1's is sent or checked.

LCR(5): Specifies the stick parity. When LCR(3) is in logic 1 and LCR(5) is in logic 1, the parity bit is sent and then detected by the receiver as logic 0, if LCR(4) is in logic 1; or detected by the receiver as logic 1, if LCR(4) is in logic 0. If LCR(5) is in logic 0. Stick Parity is disabled.

LCR(6): Specifies the break control. When LCR(6) is set to a logic 1, the transmit data

(TXD) is forced to the spacing (logic 0) state. The break is disabled by setting LCR(6) to a logic 0. The Break Control bit acts only on TXD and has no effect on the transmitter logic. Break Control enables the CPU to alter a terminal in a computer communications system.

LCR(7): Specifies the divisor latch access bit (DLAB). This bit must be set to high to gain access to the divisor latches of the baud rate generator during a read or write operation. It must be set to low to gain access to the receiver buffer, the transmitter holding register, or the interrupt enable register.

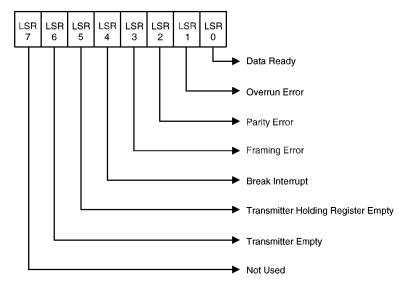

#### • Line status register (LSR)

The Line Status Register (LSR) is a single register that provides status indications. The LSR is usually the first register read by the CPU to determine the cause of an interrupt or to poll the status of each serial channel of the HT6550. The contents of the Line Status Register are described as below:

Figure 2. Line Status Register

Note:

LSR(0): This bit is the receiver data ready (DR) indicator. It is set to logic 1 whenever a complete incoming character has been received and transferred into the Receiver Buffer register. Bit 0 may be reset to logic 0 by the processor reading the data in the receiver buffer register.

LSR(1): This bit is the overrun error (OE) indicator. It indicates that data in the Receiver Buffer Register was not read by the processor before the next character was transferred into the register, thereby destroyed previous character. The OE indicator is reset whenever the processor reads the contents of the line status Register.

LSR(2): This bit is the parity error (PE) indicator. It indicates the received data character does not have the correct even or odd parity, as selected by the Even Parity Select bit LCR(4). The PE bit is set to logic 1 upon detection of a parity error, and is reset to logic 0 whenever the processor reads the contents of the Line Status Register.

LSR(3): This bit is the framing error (FE) indicator. It indicates the received character does not have a valid stop bit. LSR(3) is set to logic 1 whenever the stop bit following the last data bit or parity bit is detected as a zero bit (spacing level). The FE indicator is reset whenever the CPU reads the contents of the Line Status Register.

LSR(4): This bit is the break interrupt (BI) indicator. It is set to logic 1 whenever the received data input is held in the spacing state (logic 0) for longer than a full word transmission time (total time of the start bit+data bits+parity+stop bits). The BI indicator is reset when the CPU reads the contents of the Line Status Register.

LSR(5): This bit is the Transmitter Holding Register Empty (THRE) indicator. It indicates that the UART is ready to accept a new character for transmission. The LSR(5) bit is set to logic 1 when a character is transferred from the Transmitter Holding Register into the Transmitter Shift Register. LSR(5) is reset to logic 0 by loading the Transmitter Holding Register by the CPU. LSR(5) is not reset by a CPU read of the LSR. In addition, this bit causes the HT6550 to issue an interrupt to the CPU when the Transmit Holding Register Empty Interrupt Enable is set high in Interrupt Enable Register (IER).

LSR(6): This bit is the Transmitter Empty (TEMT) indicator. LSR(6) is set to logic 1 when the Transmitter Holding Register (THR) and the Transmitter Shift Register (TSR) are both empty. LSR(6) is reset to logic 0 when a character is loaded into the TSR. TEMT is not reset low by a CPU read of the LSR.

LSR(7): This bit is not used and always 0.

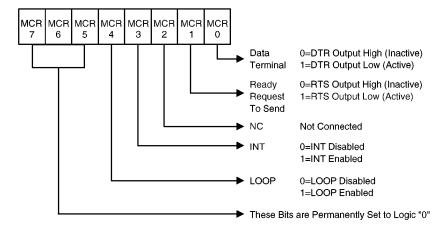

Modem control register (MCR)

The Modem Control Register (MCR) controls the interface with the MODEM or data set (or a peripheral device emulating a MODEM). The contents of the Modem Control Register are described as follow:

Figure 3. Modem Control Register

#### Note:

MCR(0): This bit controls the  $\overline{DTR}$  output. When MCR(0) is set to logic 1, the  $\overline{DTR}$  output is forced low. When MCR(0) is reset to logic 0, the  $\overline{DTR}$  output is forced inactive. The  $\overline{DTR}$  output of the serial channel may be input into an inverting line driver in order to obtain the proper polarity input at the MODEM or data set.

MCR(1): This bit controls the  $\overline{RTS}$  output. MCR(1) forces the  $\overline{RTS}$  output in a manner identical to that described above for MCR(0).

MCR(2): This bit is not connected.

MCR(3): The enable of the interrupt output can be set to an active state by programming this bit to a logic 1.

MCR(4): This bit provides a local loop back feature for diagnostic testing of the channel.

When MCR(4) is set high, Serial output (TXD) is set to the marking state (logic "1"), and the receiver data input Serial input (RXD) is disconnected. The output of the Transmitter Shift Register is looped back into the Receiver Shift Register input. The three MODEM control inputs ( $\overline{\text{CTS}}$ ,  $\overline{\text{DSR}}$ , and  $\overline{\text{RI}}$ ) are disconnected. The MODEM control outputs (DTR and RTS) are internally connected to associated bits in Modem Control Register. The MO-DEM control output pins are forced to their inactive state (high). In the diagnostic mode, data transmitted is immediately received. This allows the processor to verify the transmit and receive data paths of the selected serial channel.

Bits MCR(5)~MCR(7): These bits are permanently set to logic 0.

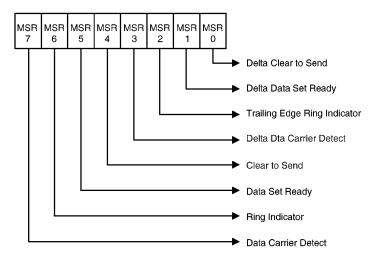

#### • Modem status register (MSR)

The MSR provides the CPU with status of the modem input lines from the MODEM or peripheral devices. The MSR allows the CPU to read each of the several channel modem signal inputs by accessing the data bus interface of the HT6550 in addition to the current

status information, four bits of the MSR indicate whether the modem inputs have changed since the last reading of the MSR. The delta starts bits are set high when a control input from the MODEM changes state, and reset low when the CPU reads the MSR.

Figure 4. Modem Status Register

21

#### Note:

MSR(0): This bit is the delta clear to send (DCTS) indicator. It indicates the  $\overline{\text{CTS}}$  input to the chip has changed state since the last time it was read by the processor.

MSR(1): This bit is the delta data set ready (DDSR) indicator. It indicates the  $\overline{DSR}$  input to the chip has changed state since last time it was read by the processor.

MSR(2): This bit is the trailing edge ring indicator (TERI). It indicates that the  $\overline{\text{RI}}$  input to the serial channel has changed state from low to high since last time it was read by the CPU.

MSR(3): This bit is the delta data carrier detect (DDCD) indicator. It indicates the  $\overline{DCD}$  input to the serial channel has changed state the last time it was read by the CPU.

MSR(4): This bit is the opposite of the  $\overline{CTS}$  input. If MCR(4) of the MCR is set to a logic 1,

this bit is equivalent to RTS of the MCR. It is the status of the CTS input from the modem indicating to the serial channel that the MO-DEM is ready to receive data from the serial channel's transmitter output (TXD).

MSR(5): This bit is the opposite of the  $\overline{DSR}$  input. If MCR(4) of the MCR is set to a logic 1, this bit is equivalent to DTR of the MCR. It is a status of the DSR input from the MODEM to the serial channel which indicates that the MODEM is ready to provide received data to the serial channel receiver circuit.

MSR(6): This bit is the opposite of the RI input. It indicates the status to the  $\overline{\text{RI}}$  input. If MCR(4) of the MCR is set to a logic 1, this bit is not connected in the MCR.

MSR(7): This bit is the opposite of the  $\overline{DCD}$  input. If MCR(4) of MCR is set to a logic 1, this bit is equivalent to INT of the MCR.

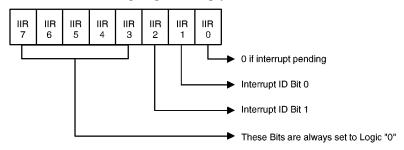

- Interrupt identification register (IIR)

- The Interrupt Identification Register (IIR) of each serial channel of the HT6550 has interrupt capability for interfacing to current microprocessors. In order to minimize software overhead during data character transfers, the serial channel prioritizes interrupts into four levels. The four levels of interrupt conditions are listed as follows:

- \* Receiver Line Status (Priority 1)

- \* Received Data Ready (Priority 2)

- \* Transmitter Holding Register Empty (Pri-

\* Modem Status (Priority 4)

Information indicating that a prioritized interrupt is pending and the type of interrupt is stored in the interrupt identification Register (IIR). When addressed during chip select time, the IIR indicates the highest priority interrupt pending. No other interrupts are acknowledged until the interrupt is serviced by the CPU. The contents of the IIR are indicated in Table 2 and are described below.

Figure 5. Interrupt Identification Register

#### Note:

IIR(0): This bit can be used in either a hard—wired prioritized or polled environment to indicate whether an interrupt is pending. When IIR(0) is logic 0, an interrupt is pending, and the IIR contents may be used as a pointer to the appropriate interrupt service routine.

When IIR(0) is logic 1, no interrupt is pending, and polling continues.

IIR(1)~(2): These two bit identify the pending interrupt that has the highest priority, as shown in Table 2 below.

IIR(3) $\sim$ (7): These five bits are always logic 0.

| In   | terru | pt Ide | entification   | Interrupt Set and Reset Functions |                                                                                             |                                                             |  |  |

|------|-------|--------|----------------|-----------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| Bit2 | Bit1  | Bit0   | Priority Level | Interrupt Flag                    | Interrupt Flag                                                                              | Interrupt Reset Control                                     |  |  |

| X    | X     | 1      |                | None                              | None                                                                                        | None                                                        |  |  |

| 1    | 1     | 0      | First          | Receiver Line<br>Status           | OE, PE FE, or BI                                                                            | LSR Read                                                    |  |  |

| 1    | 0     | 0      | Second         | Received Data<br>Available        | Received Data<br>Available                                                                  | RBR Read                                                    |  |  |

| 0    | 1     | 0      | Third          | THRE                              | THRE                                                                                        | IIR Read if THRE is<br>the interrupt Source or<br>THR write |  |  |

| 0    | 0     | 0      | Fourth         | Modem Status                      | $\overline{\text{CTS}}, \overline{\text{DSR}}, \overline{\text{RI}}, \overline{\text{DCD}}$ | MSR Read                                                    |  |  |

x=Not Defined.

Table 2. Interrupt Identification Register

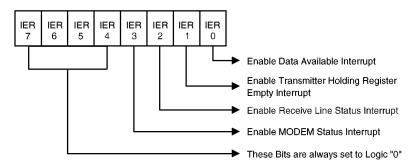

#### • Interrupt enable register (IER)

The Interrupt Enable Register (IER) is used to independently enable the four serial channel interrupts which activate the interrupt (SINTR1 or SINTR2) output. All interrupts are disable by resetting IER(0)~IER(3) of the Interrupt Enable Register. Interrupts are enabled by setting the appropriate bits of the

IER high. Disabling an interrupt prevents it from being indicated as active in the IIR and from activating the SINTR1 or SINTR2 output signal. All other system functions operate in their normal manner, including the setting of the Line Status and Modem Status Registers. The contents of the Interrupt Enable Register are described below.

Figure 6. Interrupt Enable Register

Note:

IER(0): When this bit is set to logic 1, it enables the Receive Data Available Interrupt.

IER(1): When this bit is set to logic 1, it enables the Transmitter Holding Register Empty Interrupt.

IER(2): When this bit is set to logic 1, it en-

ables the Receive Line Status Interrupt.

IER(3): When this bit is set to logic 1, it enables the Modem Status Interrupt.

IER(4)~(7): These four bits are always set to logic 0.

The table below summarize all serial channel registers:

| D          | Register Bit Number   |              |              |              |              |              |              |                        |  |  |

|------------|-----------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------------------|--|--|

| Reg.       | Bit7                  | Bit6         | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0                   |  |  |

| RBR<br>(R) | Data<br>Bit7<br>(MSB) | Data<br>Bit6 | Data<br>Bit5 | Data<br>Bit4 | Data<br>Bit3 | Data<br>Bit2 | Data<br>Bit1 | Data<br>Bit0<br>(LSB)* |  |  |

| THR (W)    | Data<br>Bit7          | Data<br>Bit6 | Data<br>Bit5 | Data<br>Bit4 | Data<br>Bit3 | Data<br>Bit2 | Data<br>Bit  | Data<br>Bit0           |  |  |

| DLL        | Bit7                  | Bit6         | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0                   |  |  |

| DLM        | Bit15                 | Bit14        | Bit13        | Bit12        | Bit11        | Bit10        | Bit9         | Bit8                   |  |  |

| Dom        |                                    |                                    |                                                           | Register                          | Bit Numb                                          | er                                              |                                                             |                                                  |

|------------|------------------------------------|------------------------------------|-----------------------------------------------------------|-----------------------------------|---------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------|

| Reg.       | Bit7                               | Bit6                               | Bit5                                                      | Bit4                              | Bit3                                              | Bit2                                            | Bit1                                                        | Bit0                                             |

| IER        | 0                                  | 0                                  | 0                                                         | 0                                 | (EDSSI)<br>Enable<br>Modem<br>Status<br>Interrupt | (ELSI) Enable Receiver Line Status Intertupt    | (ETBEI) Enable Transmitter Holding Register Empty Interrupt | (ERBFI) Enable Receiver Data Available Interrupt |

| IIR<br>(R) | 0                                  | 0                                  | 0                                                         | 0                                 | 0                                                 | Interrupt<br>ID<br>Bit(1)                       | Interrupt<br>ID<br>Bit(0)                                   | "0" if<br>Interrupt<br>Pending                   |

| LCR        | (DLAB) Divisor Latch Access bit    | Set<br>Break                       | Stick<br>Parity                                           | (EPS)<br>Even<br>Parity<br>Select | (PEN)<br>Parity<br>Enable                         | (STB)<br>Number<br>of Stop<br>Bits              | (WLSB1)<br>Word<br>Length<br>Select<br>Bit1                 | (WLSB0)<br>Word<br>Length<br>Select<br>Bit0      |

| MCR        | 0                                  | 0                                  | 0                                                         | Loop                              | Interrupt                                         | Not<br>Connected                                | (RTS)<br>Request<br>To<br>Send                              | (DTR)<br>Data<br>Terminal<br>Ready               |

| LSR        | 0                                  | (TEMT)<br>Transmitt<br>er<br>Empty | (THRE)<br>Transmitte<br>r<br>Holding<br>Register<br>Empty | (BI)<br>Break<br>Interrupt        | (FE)<br>Framing<br>Error                          | (PE)<br>Parity<br>Error                         | (OE)<br>Overrun<br>Error                                    | (DR)<br>Data<br>Ready                            |

| MSR        | (DCD)<br>Data<br>Carrier<br>Detect | (RI)<br>Ring<br>Indicator          | (DSR)<br>Data<br>Ready<br>Set                             | (CTS)<br>Clear<br>to<br>Send      | (DRSLD) Delta Receive Line Signal Detect          | (TERI)<br>Trailing<br>Edge<br>Ring<br>Indicator | (DDSR)<br>Delta<br>Data<br>Set<br>Ready                     | (DCTS) Delta Clear to Send                       |

| SCR        | Bit7                               | Bit6                               | Bit5                                                      | Bit4                              | Bit3                                              | Bit2                                            | Bit1                                                        | Bit0                                             |

(W): Write only. (R): Read only.

LSB Data Bit 0 is the first bit transmitted or received.

Table 3. Serial Channel Accessible Registers

#### • Baud rate generator (BRG)

The Baud Rate Generator is used to generate the 16X baud rate for the UART function. It is obtained by dividing the timing reference clock input by a divisor between 1 and  $(2^{16}-1)$ which is programmable by two divisor latches: DLM and DLL. The HT6550 uses 24MHz to generate the 1.8432MHz timing reference frequency. With the frequencies, standard bit rate from 50 to 38.5 Kb/s are available. Table 4 illusrates the divisors needed to obtain standard rates using a baud rate generator with crystal frequency of 1.8432MHz. For baud rates of 38400 and below, the error obtained is minimal. The accuracy of the desired baud rate is dependent on the crystal frequency chosen.

| Desired<br>Baud<br>Rate | Divisor<br>Used | Percent Error<br>Difference Between<br>Desired and Actual |  |  |  |

|-------------------------|-----------------|-----------------------------------------------------------|--|--|--|

| 50                      | 2304            | _                                                         |  |  |  |

| 75                      | 1536            | _                                                         |  |  |  |

| 110                     | 1047            | 0.026                                                     |  |  |  |

| 134.5                   | 857             | 0.058                                                     |  |  |  |

| 150                     | 768             | _                                                         |  |  |  |

| 300                     | 384             | _                                                         |  |  |  |

| 600                     | 192             | _                                                         |  |  |  |

| 1200                    | 96              | _                                                         |  |  |  |

| 1800                    | 64              | _                                                         |  |  |  |

| 2000                    | 58              | 0.69                                                      |  |  |  |

| 2400                    | 48              | _                                                         |  |  |  |

| 3600                    | 32              | _                                                         |  |  |  |

| 4800                    | 24              | _                                                         |  |  |  |

| 7200                    | 16              | _                                                         |  |  |  |

| 9600                    | 12              | _                                                         |  |  |  |

| 19200                   | 6               | _                                                         |  |  |  |

| 38400                   | 3               | _                                                         |  |  |  |

| 56000                   | 2               | 2.86                                                      |  |  |  |

Table 4. Baud Rate Using 1.8432MHz.

#### • Reset

After power on,the RESET input of the HT6550 should be held low for 500 ns to reset the HT6550 circuits to an idle mode until initialization. The effects of a reset on the HT6550 are summarized in Table 5.

| Register/Signal                                                                    | Reset<br>Control | Reset Status                               |

|------------------------------------------------------------------------------------|------------------|--------------------------------------------|

| Interrupt Enable<br>Register                                                       | Reset            | All Bits Low                               |

| Interrupt<br>Identification<br>Register                                            | Reset            | Bit 0 is high<br>and Bits 1-7<br>are low   |

| Line Control<br>Register                                                           | Reset            | All Bits Low                               |

| Line Status<br>Register                                                            | Reset            | Bits 5, 6 are<br>high, others<br>are low   |

| Modem Status<br>Register                                                           | Reset            | Bits 0-3 low,<br>Bits 4-7 input<br>signais |

| TXD1, TXD2                                                                         | Reset            | High                                       |

| $\frac{\text{RTS0, }\overline{\text{RTS1,}}}{\text{DTR0, }\overline{\text{DTR1}}}$ | Reset            | High                                       |

Table 5. Reset Control of Register and Pinout Signals

### • Programming

Each serial channel of the HT6550 is programmed by the control registers LCR, IER, DLL, DLM and MCR. These control words define the length of character, number of stop bits, parity, baud rate, and MODEM interface. While the control registers can be written in any order, the IER should be written to last, because it controls the interrupt enables. Once a serial channel is programmed and operated, these registers can be updated any time the HT6550 serial channel is not transmitting or receiving data.

#### • Software reset

A software reset of the serial channel is a useful method for returning to a completely known state without a system reset. Such a software reset consists of writing to the LCR, Divisor Latches, and MCR registers.

The LSR and RBR registers should be read prior to enable interrupts in order to clear out any residual data or status bits which may be invalid for subsequent operations.

#### Printer port (parallel port)

The printer port of HT6550 interfaces the device to a Centronics-type printer. When SLCTIN (pin 59) is low, the printer port is selected. The printer port is compatible to the IBM PC/AT printer port. When printer port is disabled, all outputs and register contents are preserved. In power down mode, all register are accessible but the input signals are tri-stated.

Upon power up the control signals are inactive, the data register is cleared and the status register reflects the status. There are three registers of printer port, the Data Register, Status Register and Control Register. They are listed in Table 6 and are described individually as following.

| PRT1 | PRT2 | PRT3 | Read             | Write            |

|------|------|------|------------------|------------------|

| звсн | 378H | 278H | Data Register    | Data Register    |

| 3BDH | 379H | 279H | Status Register  | _                |

| звен | 37AH | 27AH | Control Register | Control Register |

Table 6. Printer Port Registers Address

#### • Data register

The data written to this register is transmitted to the printer. Data read from this register is identical to that which was last written.

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| PD7  | PD6  | PD5  | PD4  | PD3  | PD2  | PD1  | PD0  |

#### Note:

Bit0~7: These 8 bits provide the data bits of printer port to be write in and read out.

## • Status register

Parallel port status Register is a read only register that provides the CPU to read the status of the printer. These bits are described as below.

| Bit7 | Bit6                   | Bit5 | Bit4 | Bit3  | Bit2 | Bit1 | Bit0 |

|------|------------------------|------|------|-------|------|------|------|

| BUSY | $\overline{	ext{ACK}}$ | PE   | SLCT | ERROR | _    | _    | _    |

#### Note:

Bit0~2: These three bits are not used.

Bit3: This bit is an error indicator. When this bit is a logic 0, it means that the printer has encountered are error condition.

Bit4: This bit is a select indicator. When this bit is a logic 1, it means that the printer is selected.

Bit5: This bit is a paper empty indicator. When this bit is a logic 1, it means that the printer has detected the empty of paper.

Bit6: This bit represents the current state of the printer's ACK signal. When this bit is a logic 0, it means that the printer has received the character and is ready to accept another. Normally, this signal will be active for approximately 5 microseconds before BUSY stops.

Bit7: This bit become logic 0 during data entry, when the printer is off-line during printing, or when the print head is changing position or in an error state. When Bit7 is logic 0, the printer is busy and can not accept data.

#### Control register

Printer control register is a read/write register that provides the CPU to send the information or command to the printer. These bits are described as below.

| В | it7 | Bit6 | Bit5                   | Bit4   | Bit3   | Bit2                    | Bit1   | Bit0   |

|---|-----|------|------------------------|--------|--------|-------------------------|--------|--------|

| - | _   | _    | $\overline{	ext{POE}}$ | PINTEN | SLCTIN | $\overline{	ext{INIT}}$ | AUTOFD | STROBE |

#### Note:

Bit0: This bit represents the strobe signal. When this bit is a logic 1, it generates STROBE signal. A 0.5 microsecond minimum high active pulse clocks data into the printer. Valid data must be present for a minimum of 0.5 microsecond before and after the strobe pulse.

Bit1: This bit represents the auto line-feed signal. When this bit is a logic 1, it causes the printer to line-feed after a line is printed.

Bit2: This bit represents the printer initialize signal. When this bit is a logic 0, it initializes the printer.

Bit3: This bit represents the printer selected signal. When this bit is a logic 1, it means that the printer is selected.

Bit4: This bit is the parallel interrupt enable signal. When this bit is a logic 1, it generates an interrupt when  $\overline{ACK}$  change from low state to high state.

Bit5: This bit is the direction control bit. When this bit is a logic 1, the output buffers in the parallel port are disabled allowing data driven from external sources to be read; when this bit is a logic 0, they work as a printer port. This bit is used only in extended mode.

#### Bit6~7 These two bits are not used.

The above three registers are summarized in the following table (Table 7).

|         | Register Bit Number        |      |      |        |        |                         |        |        |

|---------|----------------------------|------|------|--------|--------|-------------------------|--------|--------|

|         | Bit7                       | Bit6 | Bit5 | Bit4   | Bit3   | Bit2                    | Bit1   | Bit0   |

| Status  | $\overline{\mathrm{BUSY}}$ | ACK  | PE   | SLCT   | ERROR  | _                       | _      | _      |

| Control | _                          | _    | POE  | PINTEN | SLCTIN | $\overline{	ext{INIT}}$ | AUTOFD | STROBE |