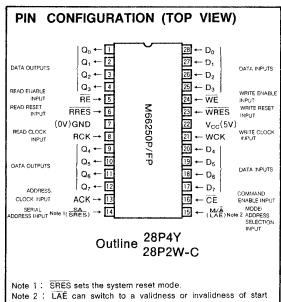

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

#### DESCRIPTION

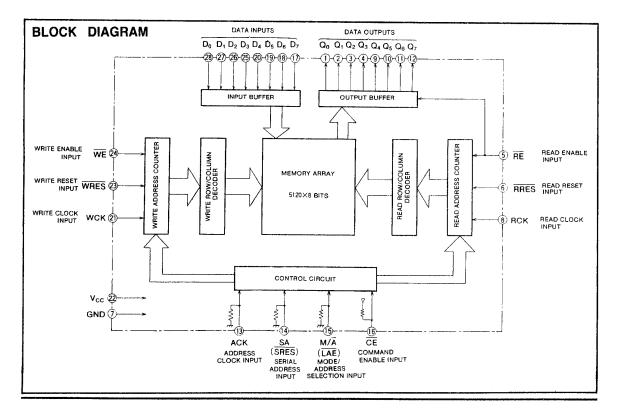

The M66250P/FP is a high-speed line memory with a FIFO (First In First Out) structure of 5120 -word $\times$ 8-bit configuration which uses high-performance silicon gate CMOS process technology.

The M66250 can also be used for LIFO (Last In First Out). The start address of reading can be specified.

It has separate clock, enable and reset signals for write and read and is most suitable as a buffer memory between devices with different data processing throughput.

#### **FEATURES**

- Memory configuration of 5120 words × 8 bits (dynamic memory)

- High-speed cycle ...... 50ns (Min.)

- High-speed access ..... 40ns(Max.)

- FIFO/LIFO switching function

- Start address specification function (at reading)

- LIFO operation on single chip

- Built in pullup/pulldown resistor for the mode control pin.

- Write and read operations can be performed separately.

- Variable-length delay bit

address except during instruction cycles.

#### APPLICATION

High-speed facsimiles, digital photocopiers, laser beam printers.

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

When RE is high-level, read is prohibited, and the read

address counter stops. The output enters the floating state

When the read reset input RRES is set to low-level, the

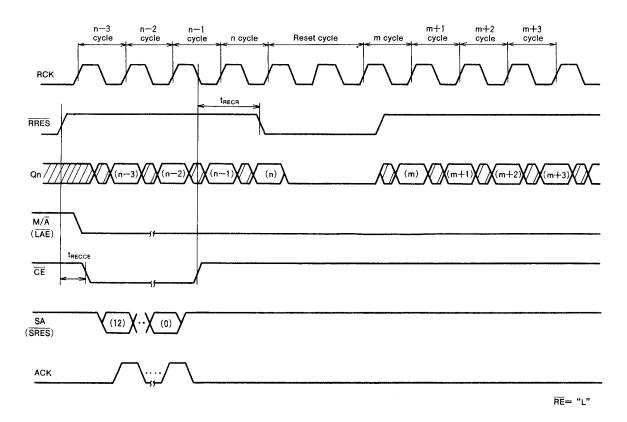

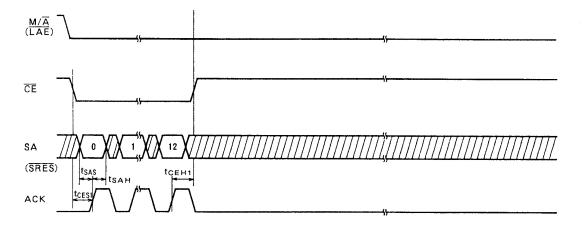

When command enable input  $\overline{CE}$  is low-level, the instruction cycle is enabled. The FIFO/LIFO mode is set by the

serial address input SA in synchronous with the rise of the

address clock input ACK during the instruction cycle when the mode/address selection input  $M/\overline{A}$  is high-level. The

start address is set by the serial address input SA in syn-

chronous with the rise of the address clock input ACK dur-

ing the instruction cycle when M/A is low-level.

(high-impedance state).

read address counter is initialized.

#### **FUNCTION**

Write is performed by taking in the content of data inputs  $D_0 \sim D_7$ , in synchronous with the rise of the write clock input WCK, when write enable input  $\overline{WE}$  is low-level, the write address counter incrementing or decrementing simultaneously. When  $\overline{WE}$  is high-level, write is prohibited and the write address counter stops. When the write reset input  $\overline{WRES}$  is set to low-level, the write address counter is initialized. When the read enable input  $\overline{RE}$  is low-level, read is performed by outputting the memory content to data output  $Q_0 \sim Q_7$  in synchronous with the rise of the read clock input RCK, and the read address counter is incremented or decremented at same time.

### FUNCTIONAL DESCRIPTION

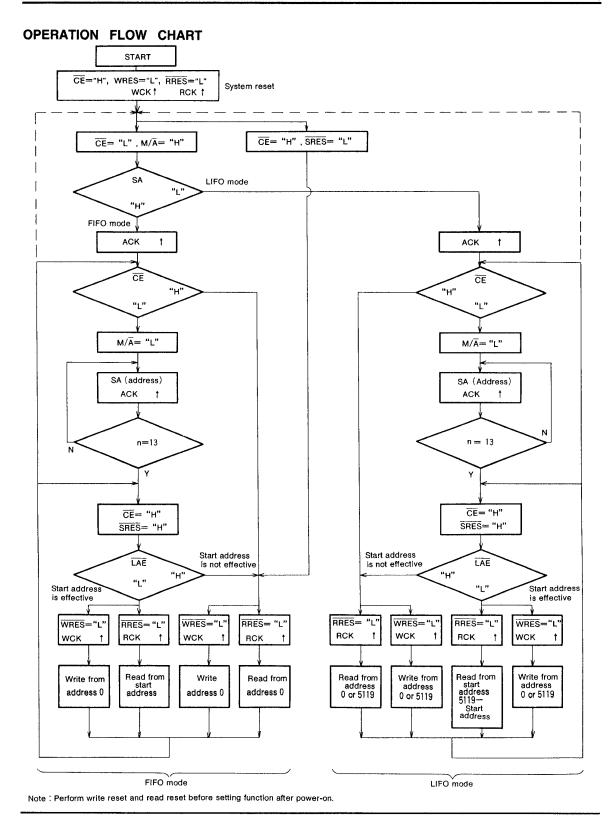

#### 1. Function Setting

(1) Function setting table

#### ① System reset setting

| CE | (SA)<br>SRES                                                    | RRES | RCK                                                     | Function |

|----|-----------------------------------------------------------------|------|---------------------------------------------------------|----------|

| Н  | H L L ↑ FIFO mode, no start address setting, read counter reset |      | FIFO mode, no start address setting, read counter reset |          |

| CE | (SA)                                                            |      |                                                         |          |

| 0E | SRES                                                            | WRES | WCK                                                     | Fuction  |

#### 2 Mode setting

| CE | M/Ā<br>(LAE) | АСК | SA<br>(SRES) | Function                        |

|----|--------------|-----|--------------|---------------------------------|

| L  | н            | t   | н            | FIFO mode setting               |

| L  | н            | t   | L            | LIFO mode setting               |

| L  | L            | 1   | ×            | Start address setting (13 bits) |

X:L or H

Note : The above mode becomes effective after the first reset.

#### ③ Effect of start address setting

| CE | SA<br>(SRES) | (M/Ā)<br>LAE | RRES | RCK | Function                               |

|----|--------------|--------------|------|-----|----------------------------------------|

| н  | Н            | L            | L    | t   | Start address setting is effective     |

| н  | н            | н            | L    | 1   | Start address setting is not effective |

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

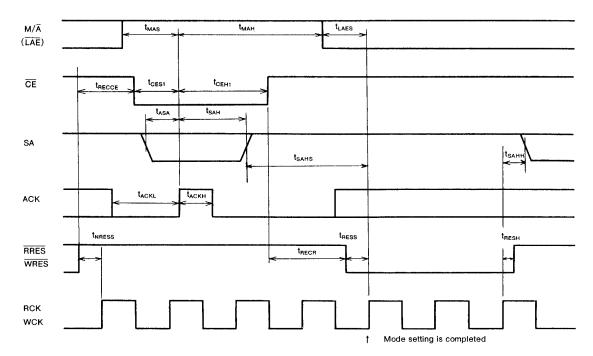

#### (2) FIFO/LIFO mode setting

When the mode/address selection input M/A is high-level and the command enable input  $\overline{CE}$  is low-level, the FIFO/-LIFO mode is selected by the serial address input SA, in synchronous with the address clock input ACK. When the command enable input  $\overline{CE}$  is high-level and the write reset input  $\overline{\mathsf{WRES}}$  is low-level, mode setting is completed in synchronous with the rise of the write clock input WCK, also provided that the write reset input  $\overline{\mathsf{WRES}}$  is low-level, in synchronous with the rise of the read clock input RCK and the read reset input  $\overline{\mathsf{RRES}}$  is low-level. The address counter is initialized at the same time.

In the FIFO mode, the write address counter moves to address 0 in synchronous with the rise of the write clock input WCK when the write reset input WRES is set to lowlevel. The address of the write address counter increases in synchronous with the rise of the write clock input WCK.

When the read reset input RRES is low-level, the read address counter moves to address 0 if the start address is not specified, and moves to the start address if the start address is specified, in synchronous with the rise of the read clock input RCK. The cycles of the read address counter increases in synchronous with the read clock input RCK.

In LIFO mode the write address counter moves to address 0 or 5119 in synchronous with the rise of write clock input WCK, when the write reset input  $\overline{\text{WRES}}$  is low-level, and, the read address counter moves to address 0 or 5119 if the start address is not specified or to the start address m or 5119-m if the start address is specified, in synchronous with the rise of the read clock input RCK. When the read reset input  $\overline{\text{RRES}}$  is low-level. The cycle of the write address counter goes up or down in synchronous with the rise of the write Clock input WCK.

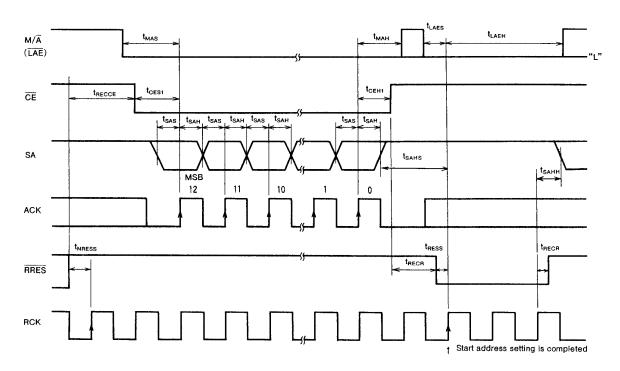

#### (3) Start address setting

When the mode/address selection input  $M/\overline{A}$  is low-level and the command enable input  $\overline{CE}$  is low-level, the address that reading starts from is set by serial address input SA in synchronous with the rise of the address clock input ACK. When the command enable input  $\overline{CE}$  is high-level and the read reset input  $\overline{RRES}$  is low-level, the read address counter moves to the specified address in synchronous with the rise of the read clock invut RCK.

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

- (4) System reset setting

- (FIFO and address counter reset setting)

When the command enable input  $\overline{CE}$  is high-level and  $\overline{SRES}$  is low-level, and if the write reset input  $\overline{WRES}$  and read reset input  $\overline{RRES}$  are set to low-level, then the FIFO mode setting and the address counter are reset in synchronous with the rise of WCK and RCK.

(Note) To uneffect system reset, SA(SRES) should be set to high-level during WRES and RRES are low-level.

### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

| FIFO and LIFO<br>mode setting | Start address setting | Write address and read address operation                                                                                                                                                                               | Write address/read address in read<br>reset/write reset operation                                                                    |

|-------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| FIFO                          | No                    | Write address 0 W A 5119                                                                                                                                                                                               | Write address : address counter is set to 0<br>Read address : address counter is set to 0                                            |

| LIFO                          | No                    | <ul> <li>Read address 0 R 5119</li> <li>Write address 0 W 5119</li> <li>Read address R read the write data 0</li> <li>Write address R read the write data 2</li> <li>Read address R W read the write data 2</li> </ul> | Write address : the set address of 0 or 5119<br>is set mutually.<br>Read address : the set address of 0 or 5119<br>is set mutually.  |

| FIFO                          | Yes                   | Write address 0 W A 5119<br>A                                                                                                                                                                                          | Write address : address counter is set to 0<br>Read address : address counter is set to m which is<br>specified by the start address |

| LIFO                          | Yes                   | <ul> <li>⑦ Read address</li> <li>5119-m R 5119</li> <li>Write address</li> <li>0 W m</li> <li>W m</li> <li>2 Read address</li> <li>K R</li> <li>Read the write data ①</li> </ul>                                       | Write address : the set address of () or 5119<br>is set mutually.                                                                    |

|                               |                       | Write address <u>W</u><br>③ Read address <u>R</u><br>read the write data ②<br>Write address <u>W</u>                                                                                                                   | Read address : address counter is set to address<br>which is specified as the start<br>address                                       |

## 2. Write address and read address operation in FIFO and LIFO mode

5120×8-BIT LINE MEMORY(FIFO/LIFO)

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

#### **ABSOLUTE MAXIMUM RATINGS** ( $T_a = -20 + 70^{\circ}C$ , unless otherwise noted)

| Symbol | Parameter                 | Conditions | Ratings                  | Unit |

|--------|---------------------------|------------|--------------------------|------|

| Vcc    | Supply voltage            |            | -0.5~+7.0                | V    |

| VI     | Input voltage             |            | $-0.5 \sim V_{cc} + 0.5$ | V    |

| Vo     | Output voltage            |            | $-0.5 \sim V_{cc} + 0.5$ | V    |

| Pd     | Maximum power dissipation | Ta=25°C    | 550(Note 1)              | mW   |

| Tstg   | Storage temperature range |            | -65 ~+150                | °C   |

Note 1 : Ta $\geq$ 68°C are derated at -9.7mw/°C (28P<sub>2</sub>W)

#### RECOMMENDED OPERATING CONDITIONS (Ta=-20~+70°C)

| Symbol | Parameter                           |      | Limits |      |      |  |

|--------|-------------------------------------|------|--------|------|------|--|

| Symbol | Parameter                           | Min. | Тур    | Max. | Unit |  |

| Vcc    | Supply voltage                      | 4.5  | 5      | 5.5  | v    |  |

| GND    | Ground                              | 1    | 0      |      | v    |  |

| Topr   | Operating ambient temperature range | -20  |        | 70   | °C   |  |

### ELECTRICAL CHARACTERISTICS (Ta=-20~+70°C, Vcc=5V±10%, unless otherwise noted)

| Symbol          | Parameter                           |                                 | Test conditions                                                    | Limits               |        |       |      |

|-----------------|-------------------------------------|---------------------------------|--------------------------------------------------------------------|----------------------|--------|-------|------|

|                 |                                     |                                 |                                                                    |                      | Тур.   | Max.  | Unit |

| VIH             | High-level input voltage            |                                 |                                                                    | 2.0                  |        |       | v    |

| VIL             | Low-level input voltage             |                                 |                                                                    |                      |        | 0.8   | v    |

| V <sub>OH</sub> | High-level output voltage           | I <sub>он</sub> =-4m/           | A                                                                  | V <sub>cc</sub> -0.8 | •••••• |       | v    |

| VOL             | Low-level output voltage            | I <sub>OL</sub> =4mA            |                                                                    |                      |        | 0.55  | v    |

| I <sub>IH</sub> | High-level input current            | V <sub>i</sub> =V <sub>cc</sub> | WE, WRES, WCK, RE, RRES,<br>RCK, CE, D0~D7                         |                      |        | 1.0   | μA   |

|                 |                                     | V <sub>I</sub> =V <sub>CC</sub> | ACK, SA(SRES), M/A(LAE)                                            |                      |        | 0.27  | mA   |

| l <sub>r∟</sub> | Low-level input current             | Vı≕GND                          | WE, WRES, WCK, RE, RRES,<br>RCK, ACK, SA(SRES),<br>M/A(LAE), D0~D7 |                      |        | -1.0  | μA   |

|                 |                                     | V <sub>I</sub> =GND             | CE                                                                 |                      |        | -0.27 | mA   |

| lozh            | Off state high-level output current | V <sub>0</sub> =V <sub>CC</sub> | A                                                                  |                      |        | 5.0   | μA   |

| lozL            | Off state low-level output current  | V <sub>0</sub> ==GND            |                                                                    |                      |        | -5.0  | μΑ   |

| lcc             | Average operating supply current    |                                 | Output open<br>100ns                                               |                      |        | 100   | mA   |

| CI              | Input capacitance                   | f=1MHz                          |                                                                    | ++                   |        | 10    | pF   |

| C0              | Output capacitance when off.        | f=1MHz                          | ·                                                                  |                      |        | 15    | pF   |

## **SWITCHING CHARACTERISTICS** ( $T_a = -20 \sim +70$ °C, $V_{cc} = 5 v \pm 10\%$ , unless otherwise noted)

| Symbol           | Parameter                    | Test conditions |      |      |      |      |

|------------------|------------------------------|-----------------|------|------|------|------|

|                  | , and motor                  |                 | Min. | Тур. | Max. | Unit |

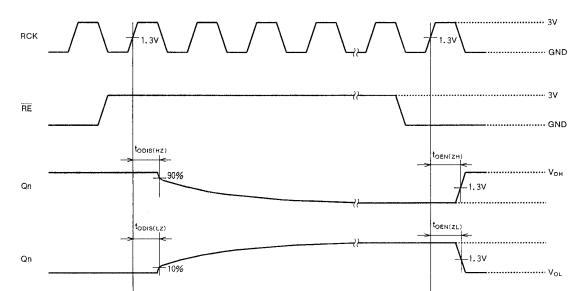

| t <sub>AC</sub>  | Access time                  |                 |      |      | 40   | ns   |

| t <sub>он</sub>  | Output hold time             |                 | 5    |      | 1    | ns   |

| t <sub>oL</sub>  | Output "L" period when reset |                 | 5    |      | 40   | ns   |

| t <sub>OEN</sub> | Output enable time           |                 | 5    |      | 40   | ns   |

| todis            | Output disable time          |                 | 5    |      | 40   | ns   |

Unit

ns

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

| Symbol                          | Parameter                             | Test conditions | Limits |      |      | Unit |

|---------------------------------|---------------------------------------|-----------------|--------|------|------|------|

| Symbol                          | Faranteter                            | Test conditions | Min.   | Тур. | Max. | Unit |

| twck                            | Write clock (WCK) cycle               |                 | 50     |      |      | ns   |

| twcкн                           | Write clock (WCK) "H" pulse width     |                 | 25     |      |      | ns   |

| twckl                           | Write clock (WCK) "L" pulse width     |                 | 25     |      |      | ns   |

| t <sub>RCK</sub>                | Read clock (RCK) cycle                |                 | 50     |      |      | ns   |

| t <sub>вскн</sub>               | Read clock (RCK) "H" pulse width      |                 | 25     |      |      | ns   |

| <b>t</b> RCKL                   | Read clock (RCK) "L" pulse width      | -               | 25     |      |      | ns   |

| tos                             | Data set up time before WCK           | -               | 15     |      |      | ns   |

| t <sub>DH</sub>                 | Data hold time after WCK              |                 | 5      |      |      | ns   |

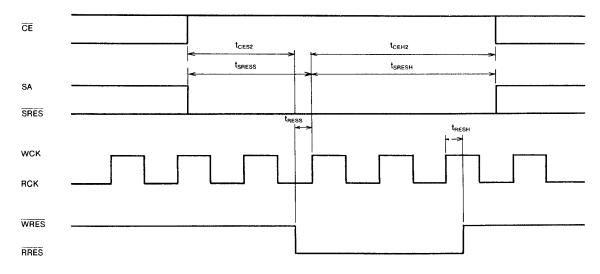

| tRESS                           | Reset set up time before WCK, RCK     | 1               | 15     |      |      | ns   |

| t <sub>RESH</sub>               | Reset hold time after WCK, RCK        |                 | 5      |      |      | ns   |

| t <sub>NRESS</sub>              | Non-reset set up time before WCK, RCK |                 | 25     |      |      | ns   |

| t <sub>NRESH</sub>              | Non-reset hold time after WCK, RCK    |                 | 5      |      |      | ns   |

| twes                            | WE set up time before WCK             |                 | 15     |      |      | ns   |

| twen                            | WE hold time after WCK                |                 | 5      |      |      | ns   |

| tNWES                           | WE non-select set up time before WCK  |                 | 15     |      |      | ns   |

| t <sub>NWEH</sub>               | WE non-select hold time after WCK     |                 | 5      |      |      | ns   |

| tRES                            | RE set up time before RCK             | -               | 15     |      |      | ns   |

| t <sub>REH</sub>                | RE hold time after RCK                |                 | 5      |      |      | ns   |

| tNRES                           | RE non-select set up time before RCK  | 1               | 15     |      |      | ns   |

| t <sub>NREH</sub>               | RE non-select hold time after RCK     | 1               | 5      |      |      | ns   |

| t <sub>r</sub> , t <sub>f</sub> | Input pulse rise and fall time        |                 |        |      | 20   | ns   |

| t <sub>H</sub>                  | Data hold time                        |                 |        |      | 20   | ms   |

#### TIMING REQUIREMENTS ( $T_a = -20 \sim +70^{\circ}C$ , $V_{cc} = 5 V \pm 10\%$ , unless otherwise noted)

Note 1 : For 1 line access, the following should be satis fild: WE "H" level period≦ 20ms--5120·t<sub>WCK</sub>- WRES "L" level period RE "H" level period≦ 20ms--5120·t<sub>RCK</sub>- RRES "L" level period

#### Limits Symbol Parameter **Test conditions** Min. Тур. Max. tMAS M/A set up time before ACK 25 t<sub>MAH</sub> M/A hold time after ACK 5 CE set up time before ACK tCESI 25 CE hold time after ACK t<sub>CEH1</sub> 5 SA set up time before ACK tsas 25 SA hold time after ACK 5 $t_{\text{SAH}}$ tLAES LAE set up time before WCK, RCK 25 LAE hold time after WCK, RCK 5 tLAEH SA "H" set up time before WCK, RCK when reset 25 tSAHS SA "H" hold time after WCK, RCK when reset t<sub>SAHH</sub> 5 CE set up time before WCK, RCK when system reset 25 $t_{\rm CES2}$ t<sub>CEH2</sub> CE hold time after WCK, RCK when system reset 5 SRES set up time before WCK, RCK when system reset t<sub>SRESS</sub> 25 SRES hold time after WCK, RCK when system reset t<sub>SRESH</sub> 5 t<sub>ACKH</sub> "H" pulse width for ACK 50 **t**ackl "L" pulse width for ACK 50 WCK, RCK recovery time after mode set 100 tRECR CE recovery time after reset tRECCE 100

#### TIMING REQUIREMENTS ( $T_a = -20 - +70$ °C, $V_{cc} = 5 V \pm 10\%$ , unless otherwise noted)

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

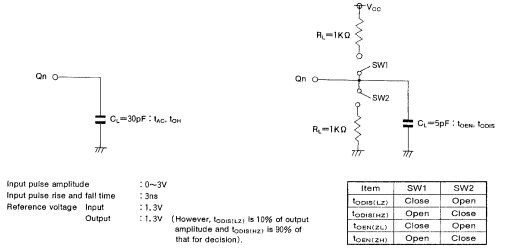

#### TEST CIRCUIT

Load capacity  $C_L$  includes float capacity of connection and input capacity of probe.

todis, tden Test Condition

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

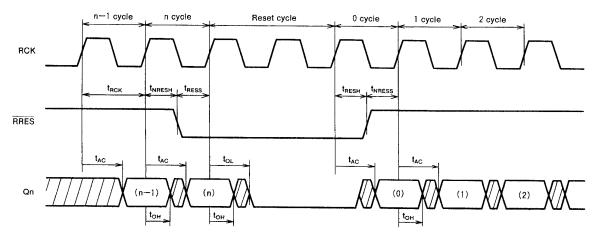

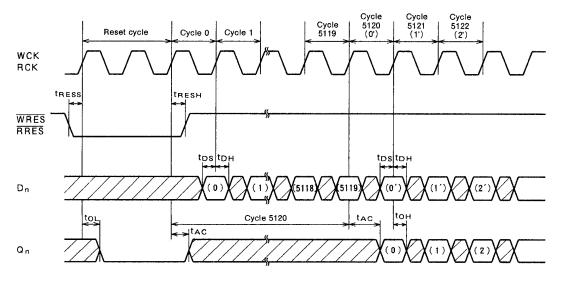

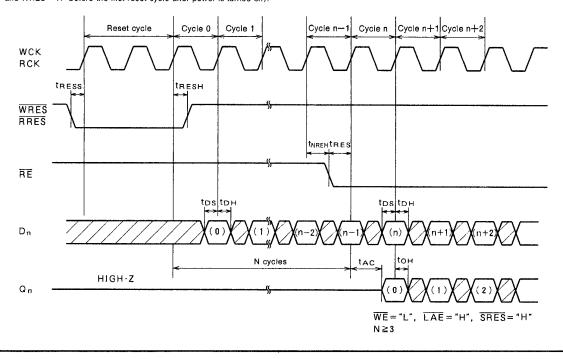

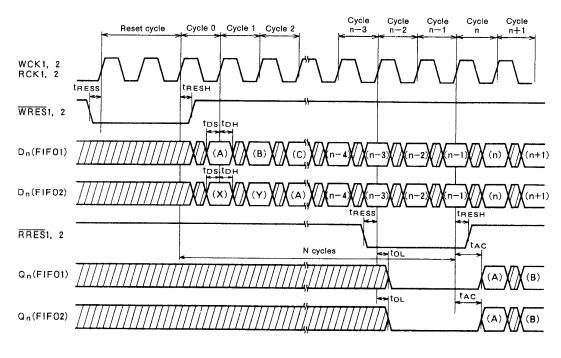

#### **OPERATION TIMING**

- 1. FIFO mode

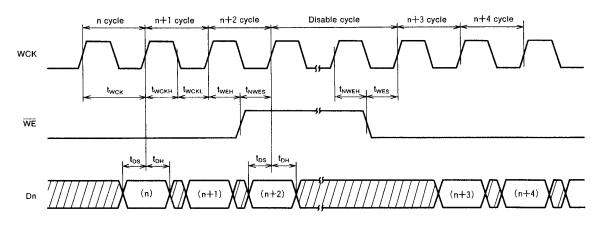

- Write cycle (This operation timing is irrelevant to start address setting)

$<sup>\</sup>overline{WRES}$  = "H",  $\overline{LAE}$  = "L" or "H"  $\overline{SRES}$  = "H"

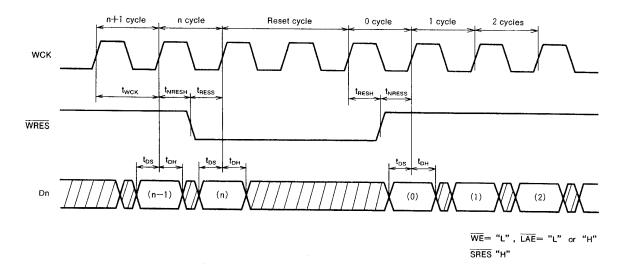

#### • Write reset cycle (Irrelevant to start address setting)

(The reset cycle requires a minimum of two cycles. Before the first reset cycle and after the power is turned on WRES should be set to high-level for 1 cycle or more.)

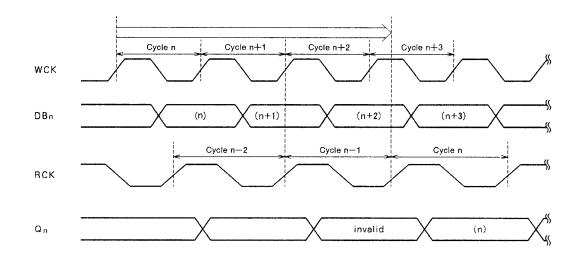

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

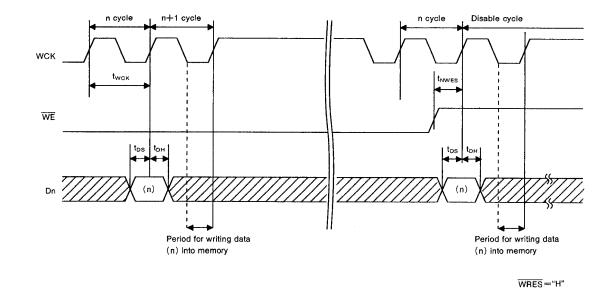

#### Matters that needs attetion when WCK stops

Input data of n cycle is read at the rising edge after WCK of n cycle and writing operation starts in the WCK low-level period of n+1 cycle. The writing operation is complete at the falling edge after n+1 cycle.

To stop reading write data at n cycle, enter WCK before the rising edge after n+1 cycle.

When the cycle next to n cycle is a disable cycle, WCK for a cycle requires to be entered after the disable cycle as well.

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

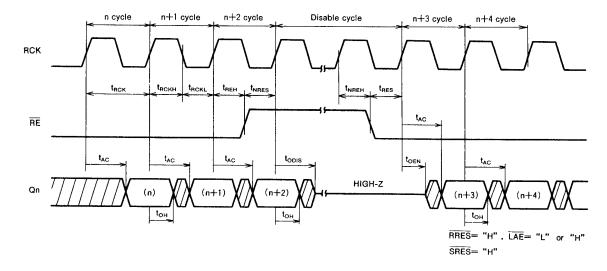

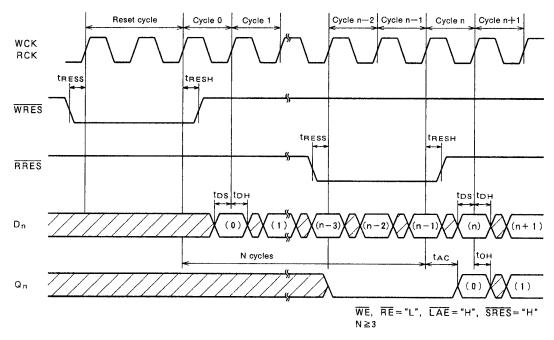

#### • Read cycle (This operation timing is irrelevant to start address setting)

#### Read reset cycle

(The reset cycle requires two cycles at minimum. During the first two cycles Qn is low-level. For one cycle or more, RRES should be set to high-level befor the first reset cycle, and after power is turned on.)

$\overline{RE}$ = "L",  $\overline{LAE}$ = "H"  $\overline{SRES}$ = "H"

### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

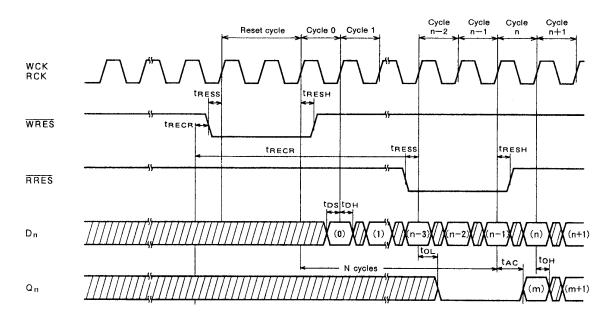

#### • Read reset cycle (start address is set)

(The reset cycle requires two cycles at minimum. During the first two cycles, Qn is low-level. For at least one cycle RRES should be set to high-level before the first reset cycle, and after power is turned on.)

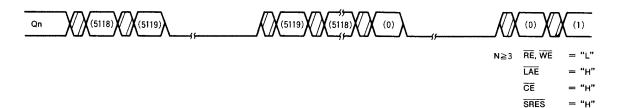

#### 2. LIFO mode

#### • Start address is not set

(The reset cycle requires two cycles at minimum. During the first two cycles, Qn is low-level. For at least one cycle, RRES should be set to high-level and WRES should be set to high-level before the first reset cycle and after power is turned on.)

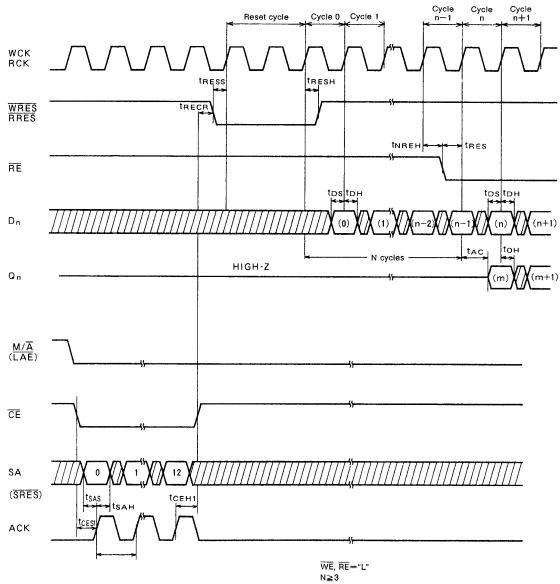

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

#### • Start address is set

(The reset cycle requires two cycles at minimum, and the first two cycles Qn is low-level. More than one cycle should be set when RRES is high-level before the first reset cycle after power on.)

N≧3 RE, WE= "L"

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

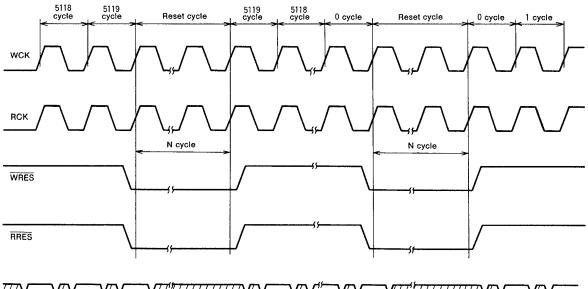

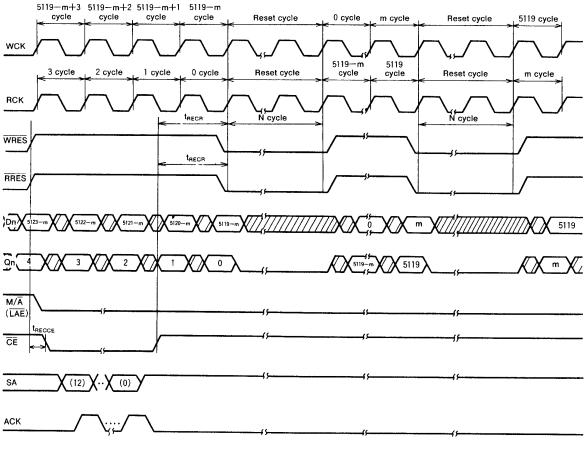

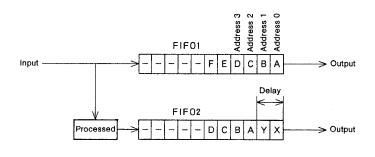

- 3. Variable length delay bits

- (1) FIFO mode/without setting of start address

- 1-line (5120 bits) delay

A write input data is written to memory at the second rise edge of WCK in the cycle, and a read output data is output from memory at the first rise edge of RCK in the cycle, so that 1-line delay can be made easily (A reset cycle requires at least 2 cycles. On goes to the "L" level during the first 2 cycles. However, it is necessary to set at least one cycle of RRES="H" and WRES="H" before the first reset cycle after power is turned on).

$\overline{WE}$ ,  $\overline{RE} = "L"$ ,  $\overline{LAE} = "H"$ ,  $\overline{SRES} = "H"$

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

#### N-bit delay 1

(Sliding input timing of WRES and RRES at a cycle corresponding to delay length) (A reset cycle requires at least 2 cycles. On goes to the L" level during the first 2 cycles. However, it is necessary to set at least one cycle of RRES= "H" and WRES="H" before the first reset cycle after power is turned on).

#### N-bit delay 2

(Disabling RE during the period corresponding to delay length to slide an address) (A reset cycle requires at least 2 cycles. On goes to the "L" level during the first 2 cycles. However, it is necessary to set at least one cycle of RRES= "H" and WRES="H" before the first reset cycle after power is turned on).

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

#### (2) FIFO mode/with setting of start address

#### • N-m bit delay 1

(Sliding input timing of WRES and RRES at a cycle corresponding to delay length) (A reset cycle requires at least 2 cycles. On goes to the L" level during the first 2 cycles. However, it is necessary to set at least one cycle of RRES= "H" and WRES="H" before the first reset cycle after power is turned on).

WE, RE="L" N≧3 m is an address specified as a start address.  $m \le n$

### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

#### N-m bit delay 2

(Disabling RE during the period corresponding to delay length to slide an address) (A reset cycle requires at least 2 cycles. On goes to the L" level during the first 2 cycles. However, it is necessary to set at least one cycle of RRES= "H" and WRES="H" before the first reset cycle after power is turned on).

m is an address specified as a start address. m<n

### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

#### (3) Inter-FIFO delay compensation by setting a start address

(A reset cycle requires at least 2 cycles. Qn goes to the "L" level during the first 2 cycles. However, it is necessary to set at least one cycle of RRES= "H" and WRES="H" before the first reset cycle after power is turned on).

$\overline{\underline{WE1}}, 2 = \overline{RE1}, 2 = "L"$  $\underline{LAE1}, 2 = "L"$ SRES1, 2 = "H" $N \ge 3$

FIFO1Without setting of start addressFIFO2With setting of start addressAddress 2

#### 5120×8-BIT LINE MEMORY(FIFO/LIFO)

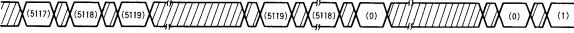

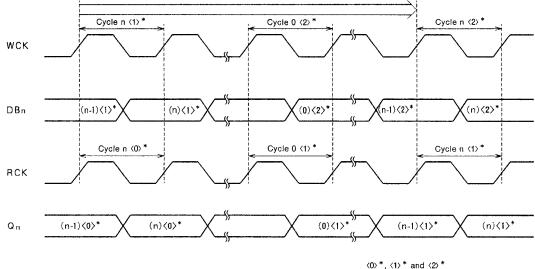

#### • Shortest read of data n" written in cycle n

Cycle n-1 on read side should be started after end of cycle n+1 on write side

When the start of cycle n-1 on read side is earlier than the end of cycle n+1 on write side, output Qn of cycle n becomes invalid. In the figure shown below, the read of cycle n-1 is invalid.

#### • Longest read of data "n" written in cycle n: 1-line delay

Cycle n  $\langle 1 \rangle^*$  on read side should be started when cycle n  $\langle 2 \rangle^*$  on write is started

Output Qn of n cycle <1>\* can be read until the start of reading side n cycle <1>\* and the start of writing side n cycle <2>\* overlap each other.

indicates a line value.