# SIEMENS

### **ICs for Communications**

Memory Time Switch Extended Large MTSXL

PEB 2447 Version 1.2

Data Sheet 03.97

T2447-XV12-D2-7600

| PEB 2447<br>Revision History:                   |       | Current Version: 03.97 (Editorial Update)    |

|-------------------------------------------------|-------|----------------------------------------------|

| Previous Ver                                    | sion: | 01.95                                        |

| PagePage(in previous(in currentVersion)Version) |       | Subjects (major changes since last revision) |

| - 32                                            |       | Register Address Arrangement (new)           |

|                                                 |       |                                              |

|                                                 |       |                                              |

|                                                 |       |                                              |

#### Edition 03.97

This edition was realized using the software system FrameMaker<sup>®</sup>. **Published by Siemens AG.**

Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1997. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

**Components used in life-support devices or systems must be expressly authorized for such purpose!** Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table c                                                                                                                                 | of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                                                             | Overview .<br>Features .<br>Logic Symbol .<br>General Device Overview .<br>Pin Configuration .<br>Pin Definitions and Functions .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| <b>2</b><br>2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4                                            | Functional Description         General Operation         Special Functions         Control Memory Reset         Evaluate Frame Measurement Signal         MTSXL Selftest         Boundary Scan and TAP Controller         Boundary Scan         TAP Controller         Use of Built in Selftest via the Boundary Scan Interface         IDCODE                                                                                                                                                                                                                                                                                           |      |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                                                                      | Operational Description         Initialization Procedure         Operation Mode         Indirect Access Registers         Frame Evaluation         Input Offset and Output Offset         Frame Delay                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14<br>4.15<br>4.16<br>4.17 | Detailed Register Description         Register Address Arrangement         Mode Register (MODR)         Command Register (CMDR)         Status Register (STAR)         Interrupt Status Register (ISTA)         Mask Register (MASK)         Memory Access Address/Code Register High (MACH)         Memory Access Address Register Low (MAAL)         Memory Read Data Register Low (MRDL)         Memory Write Data Register Low (MWDL)         Memory Write Data Register High (MWDH)         Input Clock Shift Register Bank ICSR (15:0)         Output Clock Shift Register Low (FERL)         Frame Evaluation Register Low (FERL) |      |

| 5                                                                                                                                       | Electrical Characteristics         Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 6                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

Type

PEB 2447 H

SIEMENS

## Memory Time Switch Extended Large MTSXL

### Version 1.2

### 1 Overview

### 1.1 Features

- Non blocking time/space switch for 4.096- or 8.192-Mbit/s PCM systems

- Device clock 16.384 MHz

- Switching of up to 2048 incoming PCM channels to up to 2048 outgoing PCM channels

- 32 input and 32 output PCM lines

- Tristate function for further expansion and tandem operation

- µP read access to PCM data

- Programmable clock shift with half clock step resolution for input and output

- Individual line delay measurement for 6 additional inputs

- Individual input offset programmable for 16 PCM inputs

- Boundary scan (fully IEEE1149.1 compatible)

- Built-in selftest (also usable via boundary scan interface)

- 8-bit Intel type demultiplexed μP interface

- All registers accessible by direct addressing

- In-operation adjustment of bit sampling without bit errors

- Low power consumption

- Single 5 V power supply

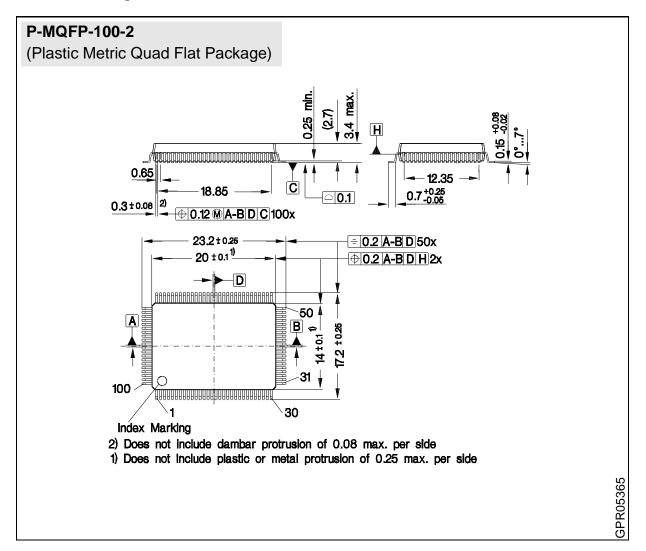

| P-MQFP-100-2 |  |

|--------------|--|

### PEB 2447

**CMOSIC**

Package

P-MQFP-100-2

**Ordering Code**

Q67103-H6594

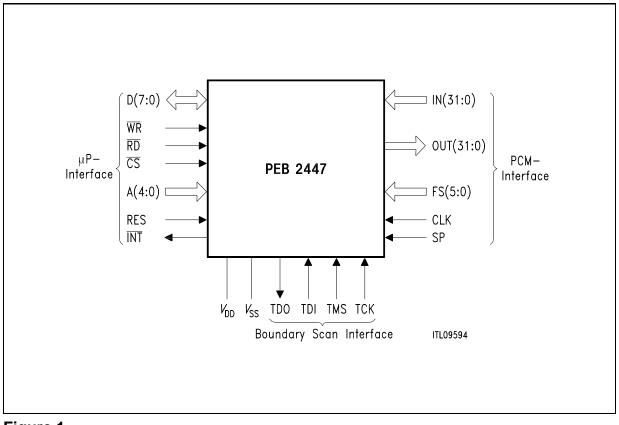

### 1.2 Logic Symbol

### Figure 1 Functional Symbol

### 1.3 General Device Overview

The Siemens Memory Time Switch Extended Large MTSXL (PEB 2447) is a capacity expansion of the MTSL (PEB 2047). It is a monolithic CMOS switching device capable of connecting maximally 2048 PCM input time slots to 2048 output time slots. In order to manage the problem of different line delays, six additional FS inputs can be used as frame measurement inputs and 16 different input offsets of PCM frames are allowed. Thus a frame wander can be compensated by adjusting the input offset during operation. A special circuitry guarantees that no bit error will occur, when reprogramming the input offsets.

The MTSXL on chip connection memory and data memory are accessed via the 8-bit standard  $\mu$ P interface (Intel demultiplexed type).

A built-in selftest mechanism – also activated by the  $\mu\text{P}$  – ensures proper device operation in the system.

The PEB 2447 is fabricated using the advanced CMOS technology from Siemens and is mounted in a P-MQFP-100-2 package. Inputs and outputs are TTL compatible.

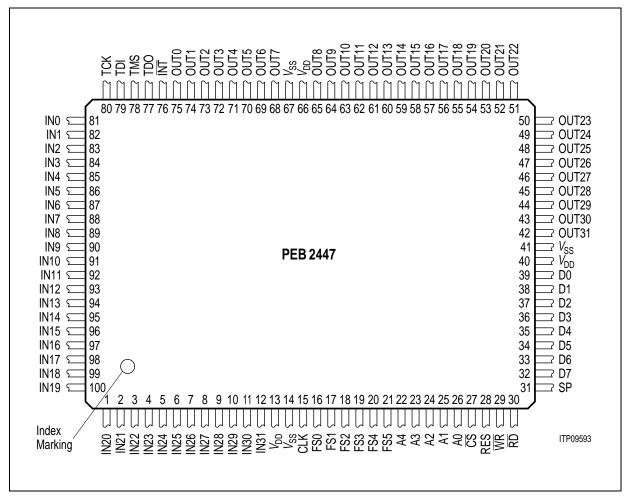

### **1.4 Pin Configuration**

(top view)

### Figure 2

### 1.5 Pin Definitions and Functions

| Pin No.        | Symbol          | Input (I)<br>Output (O)<br>Tristate (T) | Function                   |

|----------------|-----------------|-----------------------------------------|----------------------------|

| 14<br>41<br>67 | V <sub>SS</sub> | 1                                       | Ground (0 V)               |

| 13<br>40<br>66 | V <sub>dd</sub> | 1                                       | Supply Voltage: 5 ∨ ± 5 %. |

### **1.5 Pin Definitions and Functions** (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O)<br>Tristate (T) | Function                                    |

|---------|--------|-----------------------------------------|---------------------------------------------|

| 81      | IN0    | 1                                       | PCM Input Ports: Serial data is received at |

| 82      | IN1    | 1                                       | standard TTL levels.                        |

| 83      | IN2    | 1                                       |                                             |

| 84      | IN3    | 1                                       |                                             |

| 85      | IN4    | 1                                       |                                             |

| 86      | IN5    | 1                                       |                                             |

| 87      | IN6    | 1                                       |                                             |

| 88      | IN7    | 1                                       |                                             |

| 89      | IN8    | 1                                       |                                             |

| 90      | IN9    | 1                                       |                                             |

| 91      | IN10   | 1                                       |                                             |

| 92      | IN11   | 1                                       |                                             |

| 93      | IN12   | 1                                       |                                             |

| 94      | IN13   | 1                                       |                                             |

| 95      | IN14   | 1                                       |                                             |

| 96      | IN15   | 1                                       |                                             |

| 97      | IN16   | 1                                       |                                             |

| 98      | IN17   | 1                                       |                                             |

| 99      | IN18   | 1                                       |                                             |

| 100     | IN19   | 1                                       |                                             |

| 1       | IN20   | 1                                       |                                             |

| 2       | IN21   | 1                                       |                                             |

| 3       | IN22   | 1                                       |                                             |

| 4       | IN23   | 1                                       |                                             |

| 5       | IN24   | 1                                       |                                             |

| 6       | IN25   | 1                                       |                                             |

| 7       | IN26   | 1                                       |                                             |

| 8       | IN27   | 1                                       |                                             |

| 9       | IN28   | 1                                       |                                             |

| 10      | IN29   | 1                                       |                                             |

| 11      | IN30   | 1                                       |                                             |

| 12      | IN31   | I                                       |                                             |

| 15      | CLK    | 1                                       | Clock: 16.384 MHz device clock.             |

### **1.5 Pin Definitions and Functions** (cont'd)

| Pin No.  | Symbol     | Input (I)<br>Output (O)<br>Tristate (T) | Function                                                                                 |

|----------|------------|-----------------------------------------|------------------------------------------------------------------------------------------|

| 16<br>17 | FS0<br>FS1 | 1                                       | Frame Measuring Inputs: These inputs are used as frame evaluation inputs.                |

| 18       | FS2        | 1                                       |                                                                                          |

| 19       | FS3        | 1                                       |                                                                                          |

| 20       | FS4        | 1                                       |                                                                                          |

| 21       | FS5        | 1                                       |                                                                                          |

| 26       | A0         | 1                                       | Address Bus Bit 0 to 4: These inputs interface to                                        |

| 25       | A1         | 1                                       | the systems address bus to select an internal                                            |

| 24       | A2         | 1                                       | register for a read or write access.                                                     |

| 23       | A3         | 1                                       |                                                                                          |

| 22       | A4         | 1                                       |                                                                                          |

| 27       | CS         | I                                       | Chip Select: (low active) A low level selects the MTSXL for a register access operation. |

| 28       | RES        | I                                       | <b>Reset:</b> A high signal on this Input forces the MTSXL into reset state.             |

| 29       | WR         | I                                       | Write: (low active) This signal indicates a write operation.                             |

| 30       | RD         | I                                       | <b>Read:</b> (low active) This signal indicates a read operation.                        |

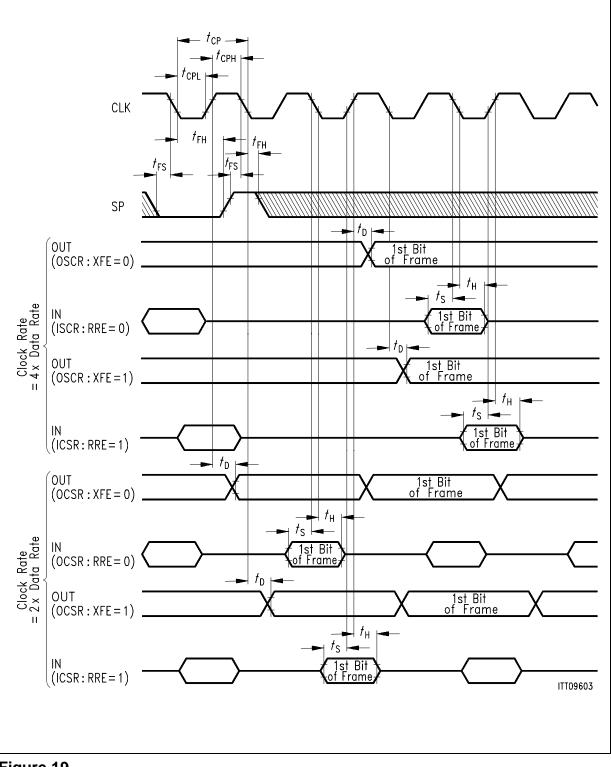

| 31       | SP         | I                                       | <b>Synchronization Pulse:</b> The MTSXL is synchronized to the PCM system via this line. |

| 39       | D0         | I/O/T                                   | <b>Data Bus:</b> These pins transfer data between the $\mu P$                            |

| 38       | D1         | I/O/T                                   | and the MTSXL.                                                                           |

| 37       | D2         | I/O/T                                   |                                                                                          |

| 36       | D3         | I/O/T                                   |                                                                                          |

| 35       | D4         | I/O/T                                   |                                                                                          |

| 34       | D5         | I/O/T                                   |                                                                                          |

| 33       | D6         | I/O/T                                   |                                                                                          |

| 32       | D7         | I/O/T                                   |                                                                                          |

| 1.5 | Pin Definitions and Functions | (cont'd) |

|-----|-------------------------------|----------|

|-----|-------------------------------|----------|

| Pin No. | Symbol | Input (I)<br>Output (O)<br>Tristate (T) | Function                                                                                                                                        |

|---------|--------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 75      | OUT0   | O/T                                     | PCM Output Port: Serial data is sent by these                                                                                                   |

| 74      | OUT1   | O/T                                     | lines. These pins can be tristated.                                                                                                             |

| 73      | OUT2   | O/T                                     |                                                                                                                                                 |

| 72      | OUT3   | O/T                                     |                                                                                                                                                 |

| 71      | OUT4   | O/T                                     |                                                                                                                                                 |

| 70      | OUT5   | O/T                                     |                                                                                                                                                 |

| 69      | OUT6   | O/T                                     |                                                                                                                                                 |

| 68      | OUT7   | O/T                                     |                                                                                                                                                 |

| 65      | OUT8   | O/T                                     |                                                                                                                                                 |

| 64      | OUT9   | O/T                                     |                                                                                                                                                 |

| 63      | OUT10  | O/T                                     |                                                                                                                                                 |

| 62      | OUT11  | O/T                                     |                                                                                                                                                 |

| 61      | OUT12  | O/T                                     |                                                                                                                                                 |

| 60      | OUT13  | O/T                                     |                                                                                                                                                 |

| 59      | OUT14  | O/T                                     |                                                                                                                                                 |

| 58      | OUT15  | O/T                                     |                                                                                                                                                 |

| 57      | OUT16  | O/T                                     |                                                                                                                                                 |

| 56      | OUT17  | O/T                                     |                                                                                                                                                 |

| 55      | OUT18  | O/T                                     |                                                                                                                                                 |

| 54      | OUT19  | O/T                                     |                                                                                                                                                 |

| 53      | OUT20  | O/T                                     |                                                                                                                                                 |

| 52      | OUT21  | O/T                                     |                                                                                                                                                 |

| 51      | OUT22  | O/T                                     |                                                                                                                                                 |

| 50      | OUT23  | O/T                                     |                                                                                                                                                 |

| 49      | OUT24  | O/T                                     |                                                                                                                                                 |

| 48      | OUT25  | O/T                                     |                                                                                                                                                 |

| 47      | OUT26  | O/T                                     |                                                                                                                                                 |

| 46      | OUT27  | O/T                                     |                                                                                                                                                 |

| 45      | OUT28  | O/T                                     |                                                                                                                                                 |

| 44      | OUT29  | O/T                                     |                                                                                                                                                 |

| 43      | OUT30  | O/T                                     |                                                                                                                                                 |

| 42      | OUT31  | O/T                                     |                                                                                                                                                 |

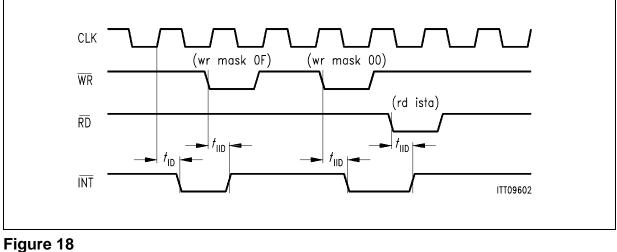

| 76      | INT    | 0                                       | Interrupt Line: Active low.                                                                                                                     |

|         |        | (Open Drain)                            | Reset when reading ISTA                                                                                                                         |

| 77      | TDO    | 0/Т                                     | <b>Test Data Output:</b> In the appropriate TAP controller state test data, an instruction or the selftest result is shifted out via this line. |

### **1.5 Pin Definitions and Functions** (cont'd)

| Pin No. | Symbol | Input (I)<br>Output (O)<br>Tristate (T) | Function                                                                                                                 |

|---------|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

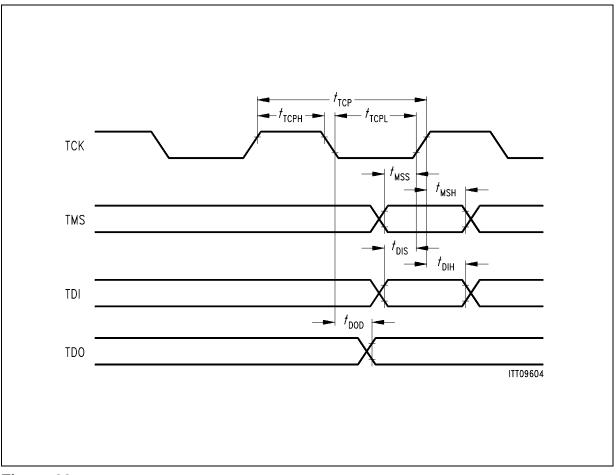

| 78      | TMS    | l<br>(internal<br>pull-up)              | <b>Test Mode Select:</b> 0 -> 1 transitions on this pin are required to step through the TAP controller state machine.   |

| 79      | TDI    | l<br>(internal<br>pull-up)              | <b>Test Data Input:</b> In the appropriate TAP controller state test data or an instruction is shifted in via this line. |

| 80      | ТСК    | I                                       | <b>Test Clock:</b> Single rate test data clock (6.25 MHz)                                                                |

### 2 Functional Description

The MTSXL is a memory time switch device. Operating with a device clock of 16.384 MHz it can connect any of 2048 PCM input channels to any of 2048 output channels.

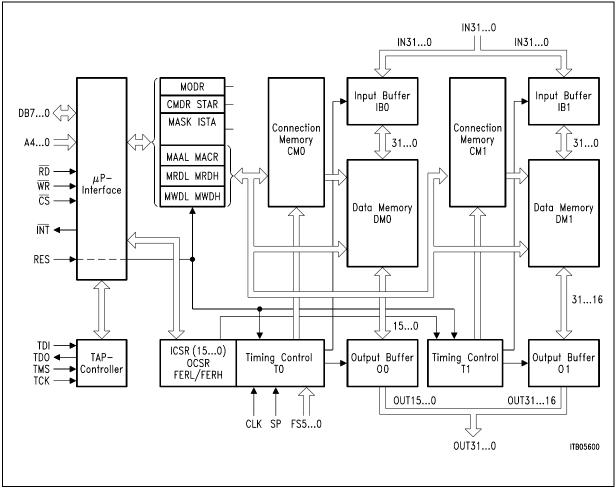

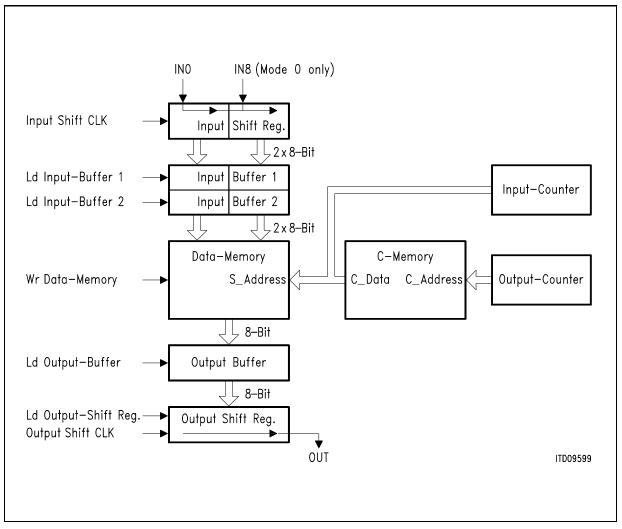

A general block diagram of the MTSXL is shown in **figure 3**.

### 2.1 General Operation

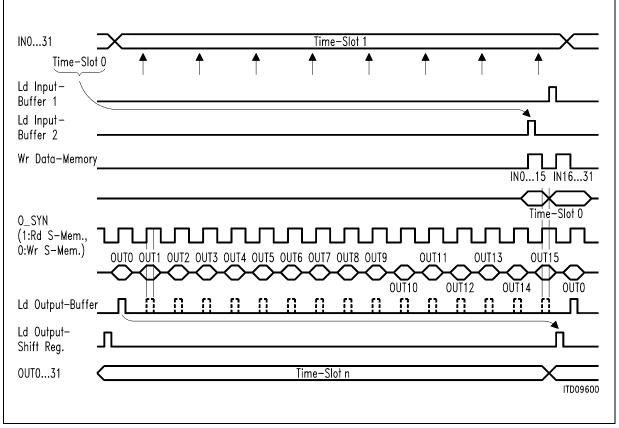

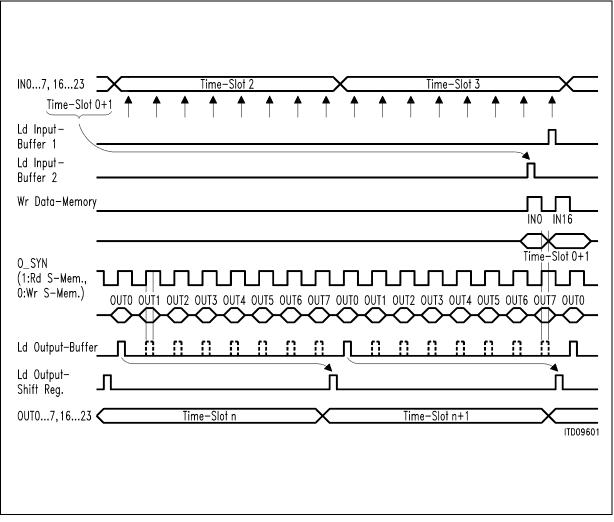

The input information of a complete frame is stored twice in the two on-chip 16-kbit data memories DM 0 and DM 1 (Data Memory 0 and Data Memory 1). The incoming 2048 channels of 8 bits each are written in sequence into fixed positions of DM 0 and DM 1. This is controlled by the input counter in the timing control block with a 8 kHz repetition rate.

For outputting, two connection memories (CM 0 and CM 1) are read in sequence synchronously. Each entry in the connection memory CM 0 / CM 1 points to a location in data memory DM 0 / DM 1. The byte in this data memory location is transferred into the current output time slot. The read access to the CM's is controlled by an output counter. CM 0 supplies the PCM data for outputs OUT0 to OUT15, CM 1 supplies the PCM data for outputs OUT0 to OUT15, CM 1 supplies the PCM data for outputs OUT16 to OUT31.

### Figure 3 Block Diagram of MTSXL

The synchronization of the input and output counters is achieved by a rising edge of the sync pulse SP, which is always sampled with the falling edge of the device clock.

Different modes of operation are configurable at the PCM interfaces (see **table 9**). Furthermore, 16 PCM input lines can be aligned with individual clock shift values to compensate different line delays. If 32 inputs are used, one clock shift value controls two ports at the same time.

Shifting of the output frame is also possible, but all output lines are affected the same way.

The input lines FS0 to FS5 are used as frame measurement inputs. After synchronizing the device by the SP pulse the FS inputs can be evaluated on a per port basis. This evaluation procedure is started by a microprocessor command. As a result the input counter value on the rising edge of the FS signal can be read from an internal register. Thus delay compensation is easily managed by programming appropriate clock shift values and/or a possible software offset.

During operation of the chip a frame length check is also supplied, which controls correct synchronization by the SP pulse and generates an interrupt in case of lost or achieved synchronization.

The unused output ports are tristated by mode selection, whereas unused time slots are tristated by an additional bit in the control memory. By using this tristate capability the MTSXL can be easily expanded to a time switch of any size.

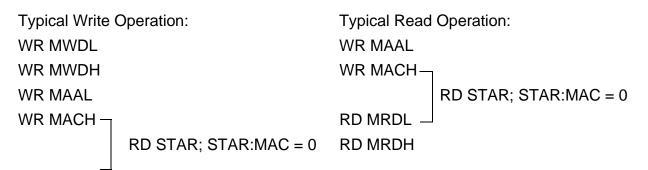

The standard 8-bit  $\mu$ P interface can communicate with Intel demultiplexed microprocessors. It gives access to the internal registers and to the control and data memory. All registers are directly addressable. The memories are accessed by a simple four byte indirect access method.

### 2.2 Special Functions

The activity of all special functions can be read in the status register. Completion of these functions is indicated by interrupts.

### 2.2.1 Control Memory Reset

Initialization of the device after a hardware reset (RES) is easily done with a  $\mu$ P command "control memory reset". After finishing this procedure all control memory channels contain the information "tristated". Apart from this tristate information the contents of the C Memory is undefined.

### 2.2.2 Evaluate Frame Measurement Signal

A command including the address  $(0 \dots 5)$  will be given by the  $\mu$ P. The rising edge of the corresponding frame measurement signal (FS0 … FS5) will be evaluated. The exact timing of the FS edge can then be read from an internal 12-bit register (resolution of a complete 8 kHz frame in half 16 MHz clock periods).

### 2.2.3 MTSXL Selftest

The switching path of the MTSXL including input buffer, data memory, control memory, output buffer and timing control can be tested in the system by a 2-step built-in selftest. Activating this mechanism takes  $2 \times 0.625$  ms (16.384 MHz). Finally the result "selftest ok/selftest not ok" can be read from the internal status register.

After test completion the control memory has also been reset (contains the information tristated).

The selftest can also be started and checked via the boundary scan interface.

Note: For correct execution of the built-in selftest the MTSXL needs a value of ICSR = 00. If MODR:PSB = 0 (e.g. after hardware reset) this value is programmed automatically after start of the selftest procedure. If ICSR does not contain "00" with MODR:PSB = 1 the selftest will fail.

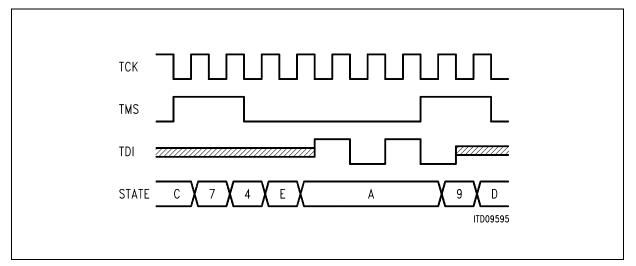

### 2.3 Boundary Scan and TAP Controller

### 2.3.1 Boundary Scan

The MTSXL provides fully IEEE Std. 1149.1 compatible boundary scan support consisting of

- a complete boundary scan

- a test access port controller (TAP controller)

- four dedicated pins (TCK, TMS, TDI, TDO)

- a 32 bit IDCODE register

All pins except power supply and ground are included in the boundary scan. Depending on the pin functionality one, two or three boundary scan cells are provided:

### Table 1

### Boundary Scan Cell Type

| Pin Type | Number of Boundary Scan Cells | Usage                 |

|----------|-------------------------------|-----------------------|

| Input    | 1                             | Input                 |

| Output   | 2                             | Output, enable        |

| I/O      | 3                             | Input, output, enable |

When the TAP controller is in the appropriate mode data is shifted into / out of the boundary scan via the pins TDI / TDO using the 6.25 MHz clock on pin TCK.

The MTSXL pins are included in the boundary scan in the following sequence:

### Table 2Boundary Scan Sequence

| Boundary Scan<br>Number TDI -> | Pin<br>Number | Pin<br>Name | Туре | Number of Scan<br>Cells | Default<br>Value |

|--------------------------------|---------------|-------------|------|-------------------------|------------------|

| 1                              | 81            | IN0         | I    | 1                       | 0                |

| 2                              | 82            | IN1         | I    | 1                       | 0                |

| 3                              | 83            | IN2         | Ι    | 1                       | 1                |

| 4                              | 84            | IN3         | I    | 1                       | 0                |

| 5                              | 85            | IN4         | I    | 1                       | 0                |

| 6                              | 86            | IN5         | I    | 1                       | 0                |

| 7                              | 87            | IN6         | Ι    | 1                       | 0                |

| 8                              | 88            | IN7         | Ι    | 1                       | 0                |

| 9                              | 89            | IN8         | Ι    | 1                       | 0                |

| 10                             | 90            | IN9         | I    | 1                       | 0                |

| 11                             | 91            | IN10        | I    | 1                       | 0                |

| Number TDI ->         Number         Name         Cells         Value           2         92         IN11         1         1         0           3         93         IN12         1         1         0           4         94         IN13         1         1         0           5         95         IN14         1         1         0           5         95         IN14         1         1         0           6         96         IN15         1         1         0           7         97         IN16         1         1         0           8         98         IN17         1         1         1           9         99         IN18         1         1         0           100         IN19         1         1         1         1           11         IN20         1         1         0         1           2         IN21         1         1         0         1           3         IN22         1         1         0         1           5         IN24         1         1         0         1 </th <th colspan="7">Table 2         Boundary Scan Sequence (cont'd)</th> | Table 2         Boundary Scan Sequence (cont'd) |     |      |      |   |   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----|------|------|---|---|--|

| 3       93       IN12       I       1       0         4       94       IN13       I       1       0         5       95       IN14       I       1       0         5       96       IN15       I       1       0         6       96       IN15       I       1       0         7       97       IN16       I       1       0         8       98       IN17       I       1       0         9       99       IN18       I       1       0         0       100       IN19       I       1       0         1       IN20       I       1       0       0         2       IN21       I       1       0       0         3       IN22       I       1       0       0         3       IN22       I       1       0       0         5       IN24       I       1       0       0         6       IN25       I       1       0       0         7       IN26       I       1       0       0         9       IN28                                                                                                                                                                                                    | Boundary Scan<br>Number TDI ->                  |     |      | Туре |   |   |  |

| 4       94       IN13       I       1       0         5       95       IN14       I       1       1         6       96       IN15       I       1       0         7       97       IN16       I       1       0         8       98       IN17       I       1       0         9       99       IN18       I       1       0         0       100       IN19       I       1       0         1       100       IN19       I       1       0         2       IN21       I       1       0       0         3       IN22       I       1       0       0         3       IN22       I       1       0       0         3       IN24       I       1       0       0         5       IN24       I       1       0       0         6       IN25       I       1       0       0         7       IN26       I       1       0       0         9       IN28       I       1       0       0         11       IN3                                                                                                                                                                                                    | 12                                              | 92  | IN11 | 1    | 1 | 0 |  |

| 595 $ N14$ $ $ 111696 $ N15$ $ $ 10797 $ N16$ $ $ 10898 $ N17$ $ $ 11999 $ N18$ $ $ 100100 $ N19$ $ $ 1111 $ N20$ $ $ 1022 $ N21$ $ $ 1033 $ N22$ $ $ 1033 $ N22$ $ $ 1044 $ N23$ $ $ 1055 $ N24$ $ $ 1055 $ N24$ $ $ 107 $ N26$ $ $ 108 $ N27$ $ $ 109 $ N28$ $ $ 109 $ N28$ $ $ 1010 $ N29$ $ $ 1011 $ N30$ $ $ 112 $ 2$ $ N31$ $ $ 1011 $ N31$ $ $ 1012 $ 17$ $ S1 $ $ $ 105 $ 77$ $ S2 $ $ 1$ 06 $ 18$ $ S2 $ $ 1$ 06 $ 18$ $ S2 $ $ 1$ 07 $ 19$ $ S3 $ $ 1$ 108 $ 20$ $ S4 $ $ 1$ 09 $ 21$ $ S5 $ <td>13</td> <td>93</td> <td>IN12</td> <td>1</td> <td>1</td> <td>0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13                                              | 93  | IN12 | 1    | 1 | 0 |  |

| 6         96         IN15         I         1         0           7         97         IN16         I         1         0           8         98         IN17         I         1         1           9         99         IN18         I         1         0           00         100         IN19         I         1         0           11         1         IN20         I         1         0           2         IN21         I         1         0         0           3         IN22         I         1         0         0           3         IN21         I         1         0         0           3         IN22         I         1         0         0           5         IN24         I         1         0         0           5         IN25         I         1         0         0           7         IN26         I         1         0         0           8         IN27         I         1         0         0           99         IN28         I         1         0         0     <                                                                                       | 14                                              | 94  | IN13 | Ι    | 1 | 0 |  |

| 7       97       IN16       I       1       0         8       98       IN17       I       1       1       1         9       99       IN18       I       1       0       0         0       100       IN19       I       1       0       0         1       1       IN20       I       1       0       0         2       2       IN21       I       1       0       0         3       3       IN22       I       1       0       0         4       IN23       I       1       0       0       0         5       5       IN24       I       1       1       0       0         5       5       IN24       I       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       1       1       1       0       0       0       0       1       1       1       1       1       1       1       0       0       1                                                                                                                                                                    | 15                                              | 95  | IN14 | I    | 1 | 1 |  |

| 8         98         IN17         I         1         1           9         99         IN18         I         1         0           0         100         IN19         I         1         1           1         1         IN20         I         1         0           2         2         IN21         I         1         0           3         3         IN22         I         1         0           4         4         IN23         I         1         0           5         5         IN24         I         1         0           6         IN25         I         1         0         0           7         IN26         I         1         0         0           9         IN28         I         1         0         0           11         IN30         I         1         1         1                                                                                                 | 16                                              | 96  | IN15 | I    | 1 | 0 |  |

| 9         99         IN18         I         1         0           00         100         IN19         I         1         1           1         1         IN20         I         1         0           2         2         IN21         I         1         0           3         3         IN22         I         1         0           3         3         IN21         I         1         0           3         3         IN22         I         1         0           3         3         IN22         I         1         0           4         4         IN23         I         1         0           5         5         IN24         I         1         0           5         5         IN25         I         1         0           7         7         IN26         I         1         0           8         IN27         I         1         0         0           9         IN28         I         1         0         1           1         IN30         I         1         1         0                                                                                                  | 17                                              | 97  | IN16 | I    | 1 | 0 |  |

| 0 $100$ $ N19$ $ $ $1$ $1$ $1$ $1$ $1$ $1$ $N20$ $ $ $1$ $1$ $0$ $2$ $2$ $ N21$ $ $ $1$ $1$ $0$ $3$ $3$ $ N22$ $ $ $1$ $0$ $4$ $4$ $ N23$ $ $ $1$ $0$ $5$ $5$ $ N24$ $ $ $1$ $1$ $6$ $6$ $ N25$ $ $ $1$ $0$ $7$ $7$ $ N26$ $ $ $1$ $0$ $7$ $7$ $ N26$ $ $ $1$ $0$ $8$ $8$ $ N27$ $ $ $1$ $0$ $9$ $9$ $ N28$ $ $ $1$ $0$ $0$ $10$ $ N29$ $ $ $1$ $0$ $1$ $11$ $ N30$ $ $ $1$ $1$ $2$ $12$ $ N31 $ $ $ $1$ $1$ $2$ $12$ $ N31 $ $ $ $1$ $0$ $4$ $16$ $FS0$ $ $ $1$ $0$ $4$ $16$ $FS0$ $ $ $1$ $0$ $7$ $19$ $FS3$ $ $ $1$ $0$ $8$ $20$ $FS4$ $ $ $1$ $0$ $9$ $21$ $FS5$ $ $ $1$ $0$ $1$ $1$ $0$ $0$ $22$ $A4$ $ $ $1$ $1$ $0$ $1$ $1$ $0$ $0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18                                              | 98  | IN17 | I    | 1 | 1 |  |

| 11 $IN20$ I1022 $IN21$ I1033 $IN22$ I1044 $IN23$ I1055 $IN24$ I1166 $IN25$ I1077 $IN26$ I1088 $IN27$ I1099 $IN28$ I1010 $IN29$ I101111 $IN30$ I11212 $IN31$ I11315 $CLK$ I10416 $FS0$ I10517 $FS1$ I10618 $FS2$ I10921 $FS5$ I101123 $A3$ I10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                              | 99  | IN18 | I    | 1 | 0 |  |

| 22 $IN21$ I1033 $IN22$ I1044 $IN23$ I1055 $IN24$ I1166 $IN25$ I107 $IN26$ I107 $IN26$ I1088 $IN27$ I1099 $IN28$ I10010 $IN29$ I101111 $IN30$ I11212 $IN31$ I11315 $CLK$ I10416 $FS0$ I10517 $FS1$ I10618 $FS2$ I10719 $FS3$ I10820 $FS4$ I101123 $A3$ I10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20                                              | 100 | IN19 | I    | 1 | 1 |  |

| 33 $IN22$ I1044 $IN23$ I1055 $IN24$ I1166 $IN25$ I1077 $IN26$ I1088 $IN27$ I1099 $IN28$ I10010 $IN29$ I101111 $IN30$ I11212 $IN31$ I11315 $CLK$ I10517 $FS1$ I10618 $FS2$ I10719 $FS3$ I10921 $FS5$ I10123 $A3$ I10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                              | 1   | IN20 | I    | 1 | 0 |  |

| 4 $4$ $IN23$ $I$ $1$ $0$ $5$ $5$ $IN24$ $I$ $1$ $1$ $1$ $6$ $6$ $IN25$ $I$ $1$ $0$ $7$ $7$ $IN26$ $I$ $1$ $0$ $8$ $8$ $IN27$ $I$ $1$ $0$ $9$ $9$ $IN28$ $I$ $1$ $0$ $0$ $10$ $IN29$ $I$ $1$ $0$ $1$ $11$ $IN30$ $I$ $1$ $1$ $2$ $12$ $IN31$ $I$ $1$ $1$ $3$ $15$ $CLK$ $I$ $1$ $0$ $4$ $16$ $FS0$ $I$ $1$ $0$ $5$ $17$ $FS1$ $I$ $1$ $0$ $6$ $18$ $FS2$ $I$ $1$ $0$ $7$ $19$ $FS3$ $I$ $1$ $0$ $9$ $21$ $FS5$ $I$ $1$ $0$ $1$ $23$ $A3$ $I$ $1$ $0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                              | 2   | IN21 | Ι    | 1 | 0 |  |

| 5       5       IN24       I       1       1         6       6       IN25       I       1       0         7       7       IN26       I       1       0         8       IN27       I       1       0         9       9       IN28       I       1       0         9       9       IN28       I       1       0         0       10       IN29       I       1       0         0       10       IN29       I       1       0         11       11       IN30       I       1       1         2       12       IN31       I       1       1         3       15       CLK       I       1       0         4       16       FS0       I       1       0         5       17       FS1       I       1       0         6       18       FS2       I       1       0         7       19       FS3       I       1       0         8       20       FS4       I       1       0         9       21       FS5                                                                                                                                                                                                         | 23                                              | 3   | IN22 | I    | 1 | 0 |  |

| 6       IN25       I       1       0         77       7       IN26       I       1       0         8       IN27       I       1       0         9       9       IN28       I       1       0         9       9       IN28       I       1       0         0       10       IN29       I       1       0         1       11       IN30       I       1       1         2       12       IN31       I       1       1         3       15       CLK       I       1       0         4       16       FS0       I       1       0         5       17       FS1       I       1       0         6       18       FS2       I       1       0         7       19       FS3       I       1       0         8       20       FS4       I       1       0         9       21       FS5       I       1       0         11       23       A3       I       1       0                                                                                                                                                                                                                                               | 24                                              | 4   | IN23 | Ι    | 1 | 0 |  |

| 7 $7$ $1N26$ $1$ $1$ $0$ $8$ $8$ $1N27$ $1$ $1$ $0$ $9$ $9$ $1N28$ $1$ $1$ $0$ $0$ $10$ $1N29$ $1$ $1$ $0$ $11$ $11$ $1N30$ $1$ $1$ $1$ $2$ $12$ $1N31$ $1$ $1$ $1$ $3$ $15$ $CLK$ $1$ $1$ $0$ $4$ $16$ $FS0$ $1$ $1$ $0$ $5$ $17$ $FS1$ $1$ $0$ $6$ $18$ $FS2$ $1$ $1$ $0$ $7$ $19$ $FS3$ $1$ $1$ $0$ $8$ $20$ $FS4$ $1$ $1$ $0$ $9$ $21$ $FS5$ $1$ $1$ $0$ $1$ $23$ $A3$ $1$ $1$ $0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                              | 5   | IN24 | Ι    | 1 | 1 |  |

| 8       IN27       I       1       0         99       9       IN28       I       1       0         00       10       IN29       I       1       0         11       11       IN30       I       1       0         11       11       IN30       I       1       1         12       IN31       I       1       1       1         33       15       CLK       I       1       0         44       16       FS0       I       1       0         55       17       FS1       I       1       0         66       18       FS2       I       1       0         77       19       FS3       I       1       0         8       20       FS4       I       1       0         9       21       FS5       I       1       0         10       23       A3       I       1       0                                                                                                                                                                                                                                                                                                                                        | 26                                              | 6   | IN25 | I    | 1 | 0 |  |

| 99IN28I100010IN29I101111IN30I111212IN31I111315CLKI10416FS0I105517FS1I106618FS2I107719FS3I108820FS4I10921FS5I101123A3I10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                              | 7   | IN26 | I    | 1 | 0 |  |

| 00       10       IN29       I       1       0         11       11       IN30       I       1       1         12       IN31       I       1       1       1         13       15       CLK       I       1       0         14       16       FS0       I       1       0         15       CLK       I       1       0         14       16       FS0       I       1       0         15       17       FS1       I       1       0         16       18       FS2       I       1       0         17       FS3       I       1       0       0         17       FS3       I       1       0       0         17       FS3       I       1       0       0         18       FS2       I       1       0       0         18       FS4       I       1       0       0         19       FS5       I       1       0       0         10       22       A4       I       1       0         11       23       A3                                                                                                                                                                                                    | 28                                              | 8   | IN27 | I    | 1 | 0 |  |

| 111IN30I1112IN31I111315CLKI10416FS0I10517FS1I10618FS2I10719FS3I10820FS4I10921FS5I101123A3I10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29                                              | 9   | IN28 | Ι    | 1 | 0 |  |

| 12       IN31       I       1       1         3       15       CLK       I       1       0         4       16       FS0       I       1       0         5       17       FS1       I       1       0         6       18       FS2       I       1       0         7       19       FS3       I       1       0         8       20       FS4       I       1       0         9       21       FS5       I       1       0         11       23       A3       I       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30                                              | 10  | IN29 | I    | 1 | 0 |  |

| 15CLKI10416FS0I10517FS1I10618FS2I10719FS3I10820FS4I10921FS5I10123A3I10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                                              | 11  | IN30 | I    | 1 | 1 |  |

| 416FS0I10517FS1I10618FS2I10719FS3I10820FS4I10921FS5I10022A4I10123A3I10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32                                              | 12  | IN31 | I    | 1 | 1 |  |

| 17       FS1       I       1       0         6       18       FS2       I       1       0         7       19       FS3       I       1       0         8       20       FS4       I       1       0         9       21       FS5       I       1       0         0       22       A4       I       1       0         1       23       A3       I       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33                                              | 15  | CLK  | I    | 1 | 0 |  |

| 6       18       FS2       I       1       0         77       19       FS3       I       1       0         8       20       FS4       I       1       0         9       21       FS5       I       1       0         0       22       A4       I       1       0         1       23       A3       I       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34                                              | 16  | FS0  | I    | 1 | 0 |  |

| 77       19       FS3       I       1       0         88       20       FS4       I       1       0         99       21       FS5       I       1       0         0       22       A4       I       1       0         1       23       A3       I       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35                                              | 17  | FS1  | I    | 1 | 0 |  |

| 8       20       FS4       I       1       0         9       21       FS5       I       1       0         0       22       A4       I       1       0         1       23       A3       I       1       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36                                              | 18  | FS2  | 1    | 1 | 0 |  |

| 9     21     FS5     I     1     0       0     22     A4     I     1     0       1     23     A3     I     1     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                              | 19  | FS3  | I    | 1 | 0 |  |

| 0     22     A4     I     1     0       1     23     A3     I     1     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38                                              | 20  | FS4  | I    | 1 | 0 |  |

| 1 23 A3 I 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39                                              | 21  | FS5  | I    | 1 | 0 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40                                              | 22  | A4   | 1    | 1 | 0 |  |

| 2 24 A2 I 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41                                              | 23  | A3   | 1    | 1 | 0 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42                                              | 24  | A2   | I    | 1 | 0 |  |

| Boundary Scan | Pin    | Pin   | Туре | Number of Scan | Default |

|---------------|--------|-------|------|----------------|---------|

| Number TDI -> | Number | Name  |      | Cells          | Value   |

| 43            | 25     | A1    | 1    | 1              | 0       |

| 44            | 26     | A0    | 1    | 1              | 0       |

| 45            | 27     | CS    | 1    | 1              | 0       |

| 46            | 28     | RES   | I    | 1              | 0       |

| 47            | 29     | WR    | 1    | 1              | 0       |

| 48            | 30     | RD    | 1    | 1              | 0       |

| 49            | 31     | SP    | 1    | 1              | 0       |

| 50            | 32     | AD7   | 10   | 3              | 000     |

| 51            | 33     | AD6   | IO   | 3              | 000     |

| 52            | 34     | AD5   | IO   | 3              | 000     |

| 53            | 35     | AD4   | IO   | 3              | 000     |

| 54            | 36     | AD3   | IO   | 3              | 000     |

| 55            | 37     | AD2   | IO   | 3              | 000     |

| 56            | 38     | AD1   | IO   | 3              | 000     |

| 57            | 39     | AD0   | IO   | 3              | 000     |

| 58            | 42     | OUT31 | 0    | 2              | 00      |

| 59            | 43     | OUT30 | 0    | 2              | 00      |

| 60            | 44     | OUT29 | 0    | 2              | 00      |

| 61            | 45     | OUT28 | 0    | 2              | 00      |

| 62            | 46     | OUT27 | 0    | 2              | 00      |

| 63            | 47     | OUT26 | 0    | 2              | 00      |

| 64            | 48     | OUT25 | 0    | 2              | 00      |

| 65            | 49     | OUT24 | 0    | 2              | 00      |

| 66            | 50     | OUT23 | 0    | 2              | 00      |

| 67            | 51     | OUT22 | 0    | 2              | 00      |

| 68            | 52     | OUT21 | 0    | 2              | 00      |

| 69            | 53     | OUT20 | 0    | 2              | 00      |

| 70            | 54     | OUT19 | 0    | 2              | 00      |

| 71            | 55     | OUT18 | 0    | 2              | 00      |

| 72            | 56     | OUT17 | 0    | 2              | 00      |

| 73            | 57     | OUT16 | 0    | 2              | 00      |

| Table 2<br>Boundary Scan Sequence (cont'd) |               |             |      |                         |                  |  |  |  |  |  |

|--------------------------------------------|---------------|-------------|------|-------------------------|------------------|--|--|--|--|--|

| Boundary Scan<br>Number TDI ->             | Pin<br>Number | Pin<br>Name | Туре | Number of Scan<br>Cells | Default<br>Value |  |  |  |  |  |

| 74                                         | 58            | OUT15       | 0    | 2                       | 00               |  |  |  |  |  |

| 75                                         | 59            | OUT14       | 0    | 2                       | 00               |  |  |  |  |  |

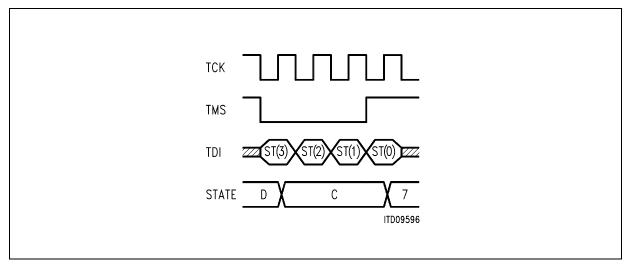

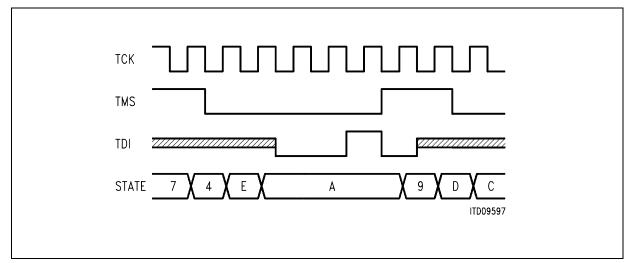

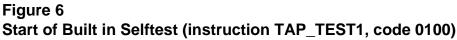

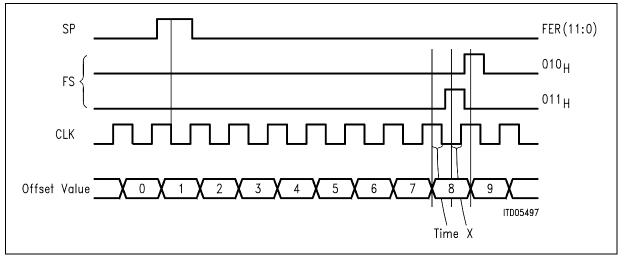

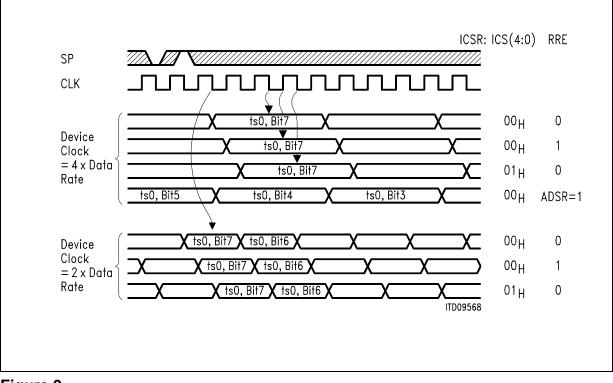

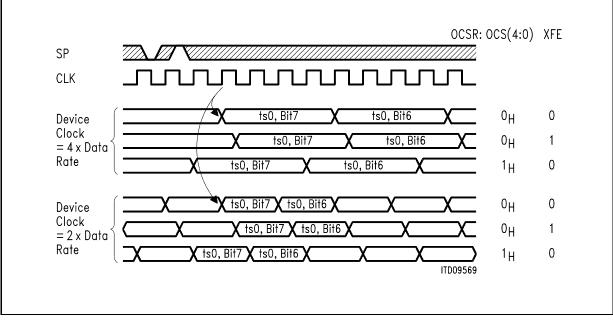

| 76                                         | 60            | OUT13       | 0    | 2                       | 00               |  |  |  |  |  |