## Features

- Smart Card Interface

- Compliance with ISO 7816, EMV2000, GIE-CB, GSM and WHQL Standards Card Clock Stop High or Low for Card Power-down Modes Support Synchronous Cards with C4 and C8 Contacts Card Detection and Automatic de-activation Sequence Programmable Activation Sequence

- Direct Connection to the Smart Card

Logic Level Shifters

Short Circuit Current Limitation (see electrical characteristics)

8kV+ ESD Protection (MIL/STD 883 Class 3)

- Programmable Voltage 5V ±5% at 65 mA (Class A) 3V ±0.2V at 65 mA (Class B) 1.8V ±0.14V at 40 mA

- Low Ripple Noise: < 200 mV

- Versatile Host Interface

- ICAM (Conditional Access) Compatible

- Two Wire Interface (TWI) Link

Programmable Address Allow up to 8 Devices

- Programmable Interrupt Output

- Automatic Level Shifter (1.6V to V<sub>cc</sub>)

- Reset Output Includes

- Power-On Reset (POR)

- Power-Fail Detector (PFD)

- High-efficiency Step-up Converter: 80 to 98% Efficiency

- Extended Voltage Operation: 3V to 5.5V

- Low Power Consumption

- 180 mA Maximum In-rush Current

- 30 µA Typical Power-down Current (without Smart Card)

- 4 to 48 MHz Clock Input, 7 MHz Min for Step-up Converter (for AT83C24)

- 18 to 48MHz Clock input (for AT83C24NDS)

- Industrial Temperature Range: -40 to +85°C

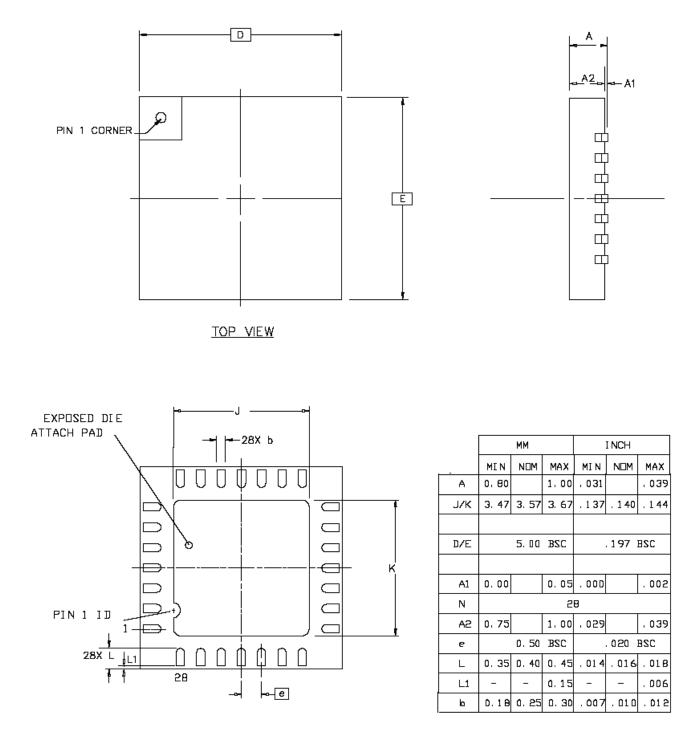

- Packages: SO28 and QFN28

## Description

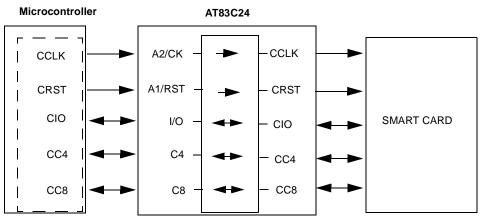

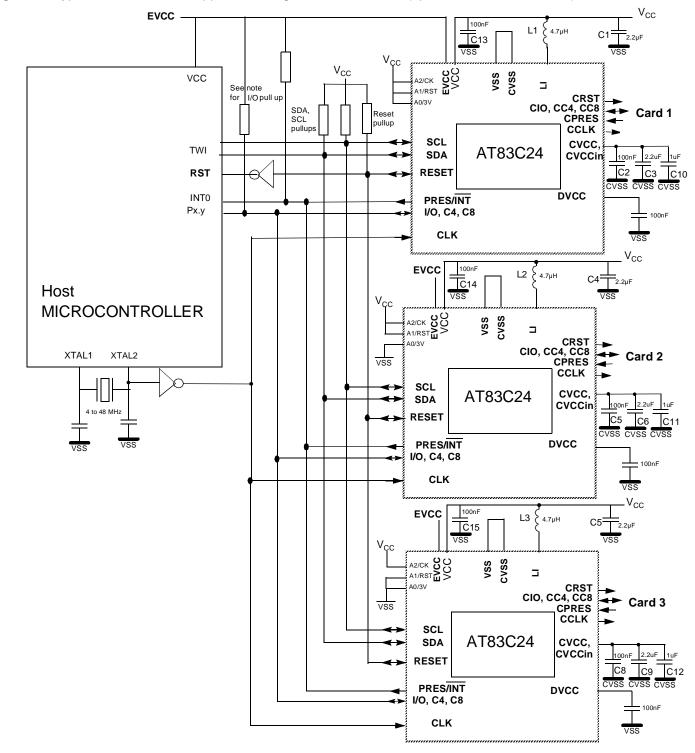

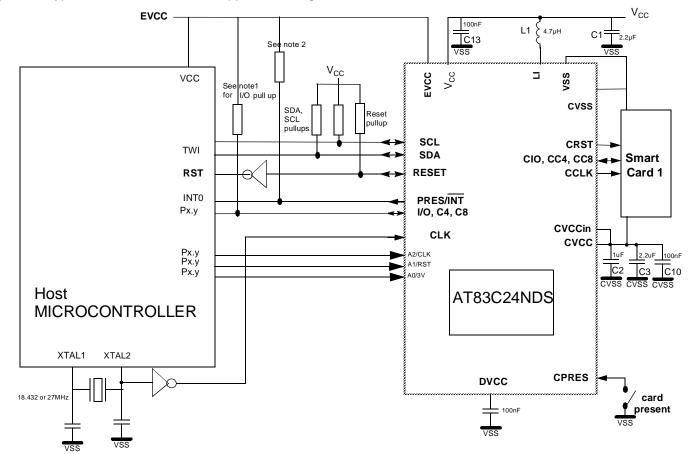

The AT83C24 is a smart card reader interface IC for smart card reader/writer applications such as EFT/POS terminals and set top boxes. It enables the management of any type of smart card from any kind of host. Up to 8 AT83C24 can be connected in parallel using the programmable TWI address.

Its high efficiency DC/DC converter, low quiescent current in standby mode makes it particularly suited to low power and portable applications. The reduced bill of material allows reducing significantly the system cost. A sophisticated protection system guarantees timely and controlled shutdown upon error conditions.

The AT83C24NDS is a dedicated version approved by NDS for use with NDS Video-Guard conditional access software in set-top boxes. All AT83C24 datasheet is applicable to AT83C24NDS. The main differences between AT83C24 and AT83C24NDS are listed below:

- 1/ CLASS A card supplied with CVCC = 4.75 to 5.25V for AT83C24NDS, CLASS A card supplied with CVCC = 4.6 to 5.25V for AT83C24

- 2/ 18MHz minimum on input clock for AT83C24NDS

- 3/ Up to 10µF for capacitor connected on CVCC pin for AT83C24,3.3µF mandatory for AT83C24NDS

Smart Card Reader Interface with Power Management

# AT83C24 AT83C24NDS

4234E-SCR-09/04

## Acronyms

TWI: Two-wire Interface POR: Power On Reset PFD: Power Fail Detect ART: Automatic Reset Transition ATR: Answer To Reset MSB: Most Significant Bit LSB: Least Significant bit SCIB: Smart Card Interface Bus

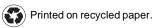

## **Block Diagram**

AT83C24

2

## **Pin Description**

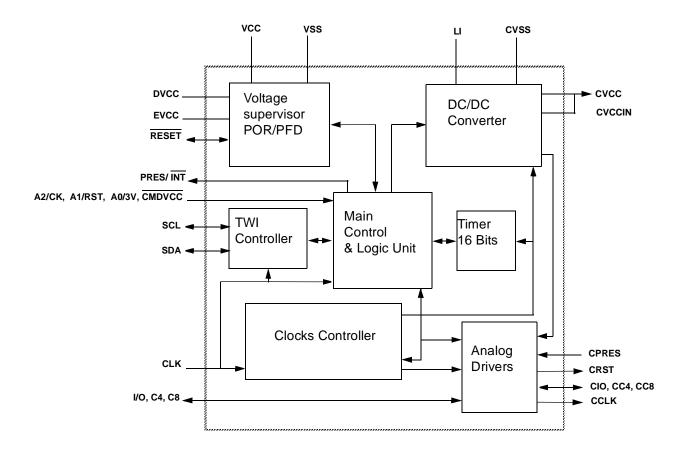

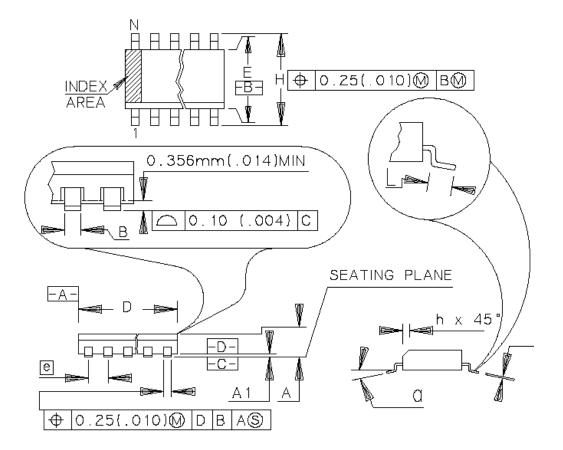

## **Pinouts (Top View)**

Note: 1. NC = Not Connected

2. SOIC and QFN packages are available for AT83C24 and for AT83C24NDS

## Signals

Table 1. Ports Description

| Pad Name                   | Pad Internal<br>Power Supply | ESD<br>Limits | Pad<br>Type           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------|------------------------------|---------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2/CK-<br>A1/RST-<br>A0/3V | EVCC                         | 3 kV          | I                     | Microcontroller Interface Function:<br>TWI bus slave address selection input.<br>A2/CK and A1/RST pins are respectively connected to CCLK and CRST signals in<br>"transparent mode" (see page 18).<br>A0/3V is used for hardware activation to select CVCC voltage (3V or 5V).<br>The slave address of the device is based on the value present on A2, A1, A0 on the<br>rising edge of RESET pin (see Table 2). In fact, the address is taken internally at the 11th<br>CLK rising edge.                                                                                                                                                                                 |

| PRES/INT                   | EVCC                         | 3 kV          | O<br>open-<br>drain   | Microcontroller Interface Function:<br>Depending on IT_SEL value (see CONFIG4 register),<br>PRES/INT outputs card presence status or interruptions (page 9)<br>An internal Pull-up (typ 330kΩ,see Table 18)to EVCC can be activated in the pad if<br>necessary using INT_PULLUP bit (CONFIG4 register).<br>Remark: during power up and before registers configuration, the PRES/INT signal must<br>be ignored.                                                                                                                                                                                                                                                           |

| RESET                      | VCC                          | 3 kV          | I/O<br>open-<br>drain | <ul> <li>Microcontroller Interface Function:</li> <li>Power-on reset</li> <li>A low level on this pin keeps the AT83C24 under reset even if applied on power-on.<br/>It also resets the AT83C24 if applied when the AT83C24 is running (see Power monitoring §).</li> <li>Asserting RESET when the chip is in Shut-down mode returns the chip to normal operation.</li> <li>AT83C24 is driving the Reset pin Low on power-on-reset or if power fail on V<sub>CC</sub> or DVCC (see POWERMON bit in CONFIG4 register), this can be used to reset or interrupt other devices. After reset, AT83C24 needs to be reconfigured before starting a new card session.</li> </ul> |

| R |

|---|

#### Table 1. Ports Description (Continued)

| Pad Name | Pad Internal<br>Power Supply | ESD<br>Limits | Pad<br>Type           | Description                                                                                                                                                                                                                                                                                                                                                           |  |  |

|----------|------------------------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SDA      | VCC                          | 3 kV          | I/O<br>open-<br>drain | Microcontroller Interface Function<br>TWI serial data                                                                                                                                                                                                                                                                                                                 |  |  |

| SCL      | VCC                          | 3 kV          | I/O<br>open-<br>drain | Microcontroller Interface Function<br>TWI serial clock                                                                                                                                                                                                                                                                                                                |  |  |

| I/O      | EVCC                         | 3 kV          | I/O                   | Microcontroller Interface Function<br>Copy of CIO pin and high level reference for EVCC.<br>An external pull up to EVCC is needed on IO pin.<br>I/O is the reference level for EVCC if EVCC is connected to a capacitor.<br>This feature is unused if EVCC is connected to VCC.                                                                                       |  |  |

| C4       | EVCC                         | 3 kV          | I/O<br>(pull-up)      | Microcontroller Interface Function<br>Copy of Card CC4.                                                                                                                                                                                                                                                                                                               |  |  |

| C8       | EVCC                         | 3 kV          | I/O<br>(pull-up)      | Microcontroller Interface Function<br>Copy of Card CC8.                                                                                                                                                                                                                                                                                                               |  |  |

| CLK      | EVCC                         | 3 kV          | I                     | Microcontroller Interface Function<br>Master Clock                                                                                                                                                                                                                                                                                                                    |  |  |

| CIO      | CVCC                         | 8 kV+         | I/O<br>(pull-up)      | Smart card interface function<br>) Card I/O                                                                                                                                                                                                                                                                                                                           |  |  |

| CC4      | CVCC                         | 8 kV+         | I/O<br>(pull-up)      | Smart card interface function<br>Card C4                                                                                                                                                                                                                                                                                                                              |  |  |

| CC8      | CVCC                         | 8 kV+         | I/O<br>(pull-up)      | Smart card interface function<br>Card C8                                                                                                                                                                                                                                                                                                                              |  |  |

| CPRES    | VCC                          | 8 kV+         | l<br>(pull-up)        | Smart card interface function<br>Card presence<br>An internal Pull-up to VCC can be activated in the pad if necessary using PULLUP bit<br>(CONFIG1 register).                                                                                                                                                                                                         |  |  |

| CCLK     | CVCC                         | 8 kV+         | 0                     | Smart card interface function<br>Card clock                                                                                                                                                                                                                                                                                                                           |  |  |

| CRST     | CVCC                         | 8 kV+         | 0                     | Smart card interface function<br>Card reset                                                                                                                                                                                                                                                                                                                           |  |  |

| CMDVCC   | EVCC                         | 3 kV+         | l<br>(pull-up)        | Microcontroller Interface Function:<br>Activation/Shutdown of the smart card Interface.                                                                                                                                                                                                                                                                               |  |  |

| VCC      |                              | 3 kV+         | PWR                   | Supply Voltage $V_{\rm CC}$ is used to power the internal voltage regulators and I/O buffers.                                                                                                                                                                                                                                                                         |  |  |

| LI       |                              | 3 kV+         | PWR                   | DC/DC Input<br>LI <b>must be</b> tied to VCC pin through an external coil (typically 4.7 μH) and provides the<br>current for the charge pump of the DC/DC converter.<br>It may be directly connected to VCC if the step-up converter is not used (see STEPREG<br>bit in CONFIG4 register and see minimum VCC values in Table 20 (class A) and<br>Table 21 (class B)). |  |  |

# AT83C24

4

Table 1. Ports Description (Continued)

| Pad Name | Pad Internal<br>Power Supply | ESD<br>Limits | Pad<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------------------------------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CVCC     |                              | 8 kV+         | PWR         | Card Supply Voltage<br>CVCC is the programmable voltage output for the Card interface.<br>It must be connected to external decoupling capacitors (see page 35 and page 36).                                                                                                                                                                                                                                                                                                                                                                                                       |

| CVCCin   |                              | 8 kV+         | PWR         | Card Supply Voltage<br>This pin must be connected to CVCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DVCC     |                              | 3 kV+         | PWR         | Digital Supply Voltage<br>Is internally generated and used to supply the digital core.<br>This pin has to be connected to an external capacitor of 100 nF and should not be<br>connected to other devices.                                                                                                                                                                                                                                                                                                                                                                        |

| EVCC     |                              | 3 kV+         | PWR         | <ul> <li>Extra Supply Voltage (Microcontroller power supply)</li> <li>EVCC is used to supply the internal level shifters of host interface pins.</li> <li>EVCC voltage can be supplied from the external EVCC pin connected to the host power supply.</li> <li>If EVCC cannot be connected to the host power supply, it must be tied to an external capacitor. EVCC voltage can be generated internally by an automatic follow up of the logic high level on the I/O pin. In this configuration, connect a 100 nF + 100kOhms in parallel between EVCC pin and VSS pin.</li> </ul> |

| CVSS     |                              | 8 kV+         | GND         | DC/DC Ground<br>CVSS is used to sink high shunt currents from the external coil.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSS      |                              |               | GND         | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |                              | Note:         | ESD Te      | st conditions: 3 positive and 3 negative pulses on each pin versus GND. Pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

e: ESD lest conditions: 3 positive and 3 negative pulses on each pin versus GND. Pulses generated according to Mil/STD 883 Class3. Recommended capacitors soldered on CVCC and VCC pins.

## **Operational Modes**

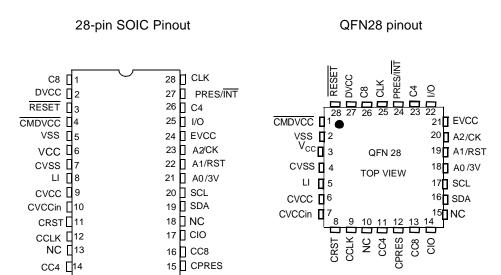

| TWI Bus Control | The Atmel Two-wire Interface (TWI) interconnects components on a unique two-wire bus, made up of one clock line and one data line with speeds of up to 400 Kbits per sec-<br>ond, based on a byte-oriented transfer format. |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                 | The TWI-bus interface can be used:                                                                                                                                                                                          |  |  |  |  |  |

|                 | <ul> <li>To configure the AT83C24</li> </ul>                                                                                                                                                                                |  |  |  |  |  |

|                 | <ul> <li>To select the operating mode of the card: 1.8V, 3V or 5V</li> </ul>                                                                                                                                                |  |  |  |  |  |

|                 | <ul> <li>To configure the automatic activation sequence</li> </ul>                                                                                                                                                          |  |  |  |  |  |

|                 | <ul> <li>To start or stop sessions (activation and de-activation sequences)</li> </ul>                                                                                                                                      |  |  |  |  |  |

|                 | <ul> <li>To initiate a warm reset</li> </ul>                                                                                                                                                                                |  |  |  |  |  |

|                 | <ul> <li>To control the clock to the card in active mode</li> </ul>                                                                                                                                                         |  |  |  |  |  |

|                 | <ul> <li>To control the clock to the card in stand-by mode (stop LOW, stop HIGH or running)</li> </ul>                                                                                                                      |  |  |  |  |  |

|                 | <ul> <li>To enter or leave the card stand-by or power-down modes</li> </ul>                                                                                                                                                 |  |  |  |  |  |

|                 | <ul> <li>To select the interface (connection to the host I/O / C4/ C8)</li> </ul>                                                                                                                                           |  |  |  |  |  |

|                 | <ul> <li>To request the status (card present or not, over-current and out of range<br/>supply voltage occurrence)</li> </ul>                                                                                                |  |  |  |  |  |

|                 | <ul> <li>To drive and monitor the card contacts by software</li> </ul>                                                                                                                                                      |  |  |  |  |  |

|                 | <ul> <li>To accurately measure the ATR delay when automatic activation is used</li> </ul>                                                                                                                                   |  |  |  |  |  |

| TWI Commands    |                                                                                                                                                                                                                             |  |  |  |  |  |

| Frame Structure | The structure of the TWI bus data frames is made of one or a series of write and read commands completed by STOP.                                                                                                           |  |  |  |  |  |

|                 | Write commands to the AT83C24 have the structure:                                                                                                                                                                           |  |  |  |  |  |

|                 | ADDRESS BYTE + COMMAND BYTE + DATA BYTE(S)                                                                                                                                                                                  |  |  |  |  |  |

|                 | Read commands to the AT83C24 have the structure:<br>ADDRESS BYTE + DATA BYTE(S)                                                                                                                                             |  |  |  |  |  |

|                 | The ADDRESS BYTE is sampled on A2/CK, A1/RST, A0/3V after each reset (hard/soft/general call) but A2/CK, A1/RST, A0/3V can be used for transparent mode after the reset.                                                    |  |  |  |  |  |

|                 | Figure 1. Data transfer on TWI bus                                                                                                                                                                                          |  |  |  |  |  |

|                 | acknowledgement                                                                                                                                                                                                             |  |  |  |  |  |

AT83C24

6

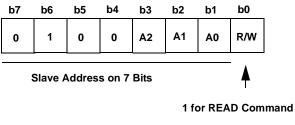

## **Address Byte**

The first byte to send to the device is the address byte. The device controls if the hardware address (A2/CK, A1/RST, A0/3V pins on reset) corresponds to the address given in the address byte (A2, A1, A0 bits).

If the level is not stable on A2/CK pin (or A1/RST pin, or A0/3V pin) at reset, the user has to send the commands to the possible address taken by the device.

If A2/CK to A0/3V are tied to the host microcontroller and their reset values are unknown, a general call on the TWI bus allows to reset all the AT83C24 devices and set their address after A2/CK to A0/3V are fixed.

Figure 2. Address Byte

0 for WRITE Command

Up to 8 devices can be connected on the same TWI bus. Each device is configured with a different combination on A2/CK, A1/RST, A0/3V pins. The corresponding address byte values for read/write operations are listed below.

| A2<br>(A2/CK pin) | A1<br>(A1/RST pin) | A0<br>(A0/3V pin) | Address Byte<br>for<br>Read<br>Command | Address Byte<br>for<br>Write<br>Command |

|-------------------|--------------------|-------------------|----------------------------------------|-----------------------------------------|

| 0                 | 0                  | 0                 | 0x41                                   | 0x40                                    |

| 0                 | 0                  | 1                 | 0x43                                   | 0x42                                    |

| 0                 | 1                  | 0                 | 0x45                                   | 0x44                                    |

| 0                 | 1                  | 1                 | 0x47                                   | 0x46                                    |

| 1                 | 0                  | 0                 | 0x49                                   | 0x48                                    |

| 1                 | 0                  | 1                 | 0x4B                                   | 0x4A                                    |

| 1                 | 1                  | 0                 | 0x4D                                   | 0x4C                                    |

| 1                 | 1                  | 1                 | 0x4F                                   | 0x4E                                    |

Table 2.

Address Byte Values

## Write Commands

#### The write commands are:

1. Reset:

Initializes all the logic and the TWI interface as after a power-up or power-fail reset. If a smart card is active when RESET falls, a deactivation sequence is performed. This is a one-byte command.

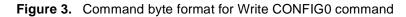

2. Write Config:

Configures the device according to the last six bits in the CONFIG0 register and to the following four bytes in CONFIG1, CONFIG2, CONFIG3 then CONFIG4 registers. This is a five bytes command.

|       |   |   | b2 | <b>N</b> . | b0 |

|-------|---|---|----|------------|----|

| 1 0 X | x | x | x  | x          | х  |

CONFIG0 on 6 Bits

3. Write Timer:

Program the 16-bit automatic reset transition timer with the following two bytes. This is a three bytes command.

4. Write Interface:

Program the interface. This is a one-byte command. The MSB of the command byte is fixed at 0.

5. General Call Reset:

A general call followed by the value 06h has the same effect as a Reset command.

|                          | Address Byte<br>(See Table 2)                       | Command Byte             | Data Byte<br>1 | Data Byte<br>2 | Data Byte<br>3 | Data Byte<br>4 |

|--------------------------|-----------------------------------------------------|--------------------------|----------------|----------------|----------------|----------------|

| 1. Reset                 | 0100 A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> 0 | 1111 1111                |                |                |                |                |

| 2. Write config          | 0100 A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> 0 | (10 + CONFIG0 6<br>bits) | CONFIG1        | CONFIG2        | CONFIG3        | CONFIG4        |

| 3. Write Timer           | 0100 A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> 0 | 1111 1100                | TIMER1         | TIMER0         |                |                |

| 4. Write Interface       | 0100 A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> 0 | (0+INTERFACE 7<br>bits)  |                |                |                |                |

| 5. General Call<br>Reset | 0000 0000                                           | 0000 0110                |                |                |                |                |

Table 3. Write Commands Description

AT83C24

8

## **Read Command**

After the slave address has been configured, the read command allows to read one or several bytes in the following order:

- STATUS, CONFIG0, CONFIG1, CONFIG2, CONFIG3, INTERFACE, TIMER1, TIMER0, CAPTURE1, CAPTURE0

- FFh is completing the transfer if the microcontroller attempts to read beyond the last byte.

- Note: Flags are only reset after the corresponding byte read has been acknowledged by the master.

Table 4. Read Command Description

| Byte Description | Byte Value                                          |

|------------------|-----------------------------------------------------|

| Address byte     | 0100 A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> 1 |

| Data byte 1      | STATUS                                              |

| Data byte 2      | CONFIG0                                             |

| Data byte 3      | CONFIG1                                             |

| Data byte 4      | CONFIG2                                             |

| Data byte 5      | CONFIG3                                             |

| Data byte 6      | CONFIG4                                             |

| Data byte 7      | INTERFACE                                           |

| Data byte 8      | TIMER 1 (MSB)                                       |

| Data byte 9      | TIMER 0 (LSB)                                       |

| Data byte 10     | CAPTURE 1 (MSB)                                     |

| Data byte 11     | CAPTURE 0 (LSB)                                     |

| Data byte 12     | 0xFF                                                |

### Interrupts

The PRES/INT behavior depends on IT\_SEL bit value (see CONFIG4 register).

- If IT\_SEL= 0, the PRES/INT output is High by default (on chip pull up or open drain). PRES/INT is driven Low by any of the following event:

- INSERT bit set in CONFIG0 register (card insertion/extraction or bit set by software )

- VCARD\_INT bit set in STATUS register (the DC/DC output voltage has settled)

- over-current detection on CVCC

- VCARDERR bit set in CONFIG0 register (out of range voltage on CVCC or bit set by software)

- ATRERR bit set in CONFIG0 register (no ATR before the card clock counter overflows or bit set by software). This control of ATR timing is only available if ART bit =1.

If IT\_SEL=0, a read command of STATUS register and of CONFIG0 register will release PRES/INT pin to high level.

Several AT83C24 devices can share the same interrupt and the microcontroller can identify the interrupt sources by polling the status of the AT83C24 devices using TWI commands.

- If IT\_SEL= 1 (mandatory for NDS applications and for software compatibility with existing devices) the PRES/INT output is High to indicate a card is present and none of the following event has occured:

- over-current detection on CVCC

- VCARDERR bit set in CONFIG0 register (out of range voltage on CVCC or bit set by software)

### **Card Presence Detection**

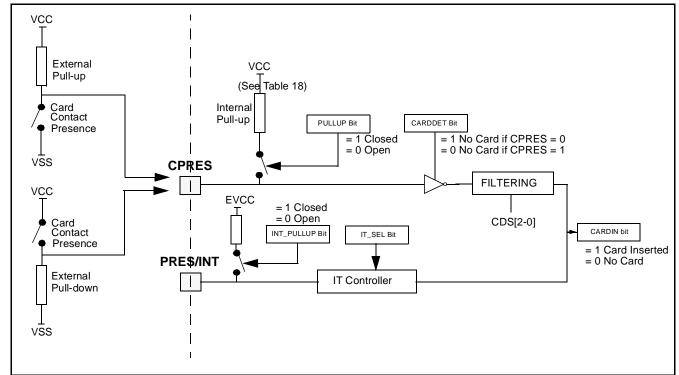

The card presence is provided by the CPRES pin. The polarity of card presence contact is selected with the CARDDET bit (see CONFIG1 register). A programmable filtering is controlled with the CDS[2-0] bits (see CONFIG1 register).

An internal pull-up on the CPRES pin can be disconnected in order to reduce the consumption, an external pull-up must then be connected to VCC. The PULLUP bit (see CONFIG1 register) controls this feature.

The card presence switch is usually connected to Vss (card present if CPRES=1). The CARDDET bit must be set. The internal pull up can be connected.

If the card presence contact is connected to Vcc (card present if CPRES=0), the internal pull-up must be disconnected (see PULLUP bit) and an external pull-down must be connected to the CPRES pin.

An interrupt can be generated if a card is inserted or extracted (see interrupts §).

## 10 **AT83C24**

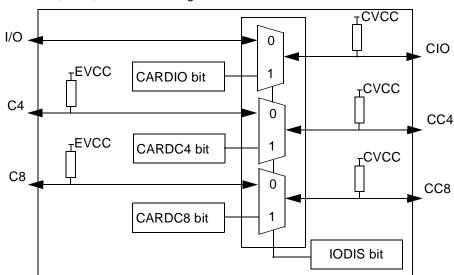

### CIO, CC4, CC8 Controller

The CIO, CC4, CC8 output pins are driven respectively by CARDIO, CARDC4, CARDC8 bits values or by I/O, C4, C8 signal pins. This selection depends of the IODIS bit value. If IODIS is reset, data are bidirectional between respectively I/O, C4, C8 pins and CIO, CC4, CC8 pins.

Figure 5. CIO, CC4, CC8 Block Diagram

IO and CIO pins are linked together through the on chip level shifters if IODIS bit=0 in INTERFACE register. This is done automatically during an hardware activation.

Their iddle level are 1. With IO high, CIO is pulled up.

The same behavior is applicable on C4/ CC4 and C8/ CC8 pins.

The maximum frequency on those lines depends on CLK frequency (3 clock rising edges to transfer). With CLK=27MHz, the maximum frequency on this line is 1.5MHz.

Due to the minimum transfer delay allowed for NDS applications, the CLK minimum frequency is 18MHz.

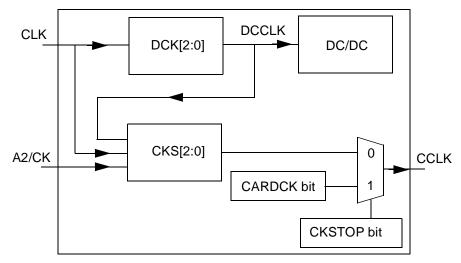

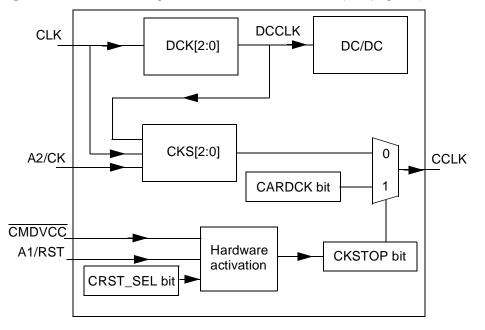

**Clock Controller** The clock controller generates two clocks (as shown in Figure 6 and Figure 7):

- 1. a clock for the CCLK: Four different sources can be used: CLK pin, DCCLK signal, CARDCK bit or A2/CK pin (in transparent mode).

- 2. a clock for DC/DC converter.

Figure 6. Clock Block Diagram with Software Activation (see page 14)

Figure 7. Clock Block Diagram with Hardware Activation (see page 14)

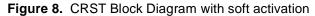

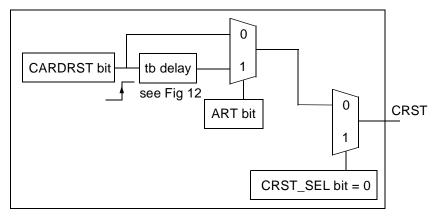

## **CRST Controller**

The CRST output pin is driven by the A1/RST pin signal pin or by the CARDRST bit value. This selection depends of the CRST\_SEL bit value (see CONFIG4 register).

If the CRST pin signal is driven by the CARDRST bit value, two modes are available:

- If the ART bit is reset, CRST pin is driven by CARDRST bit.

- If the ART bit is set, CRST pin is controlled and follows the "Automatic Reset Transition" (page 15).

# 12 **AT83C24**

## **Activation Sequence**

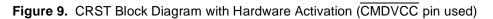

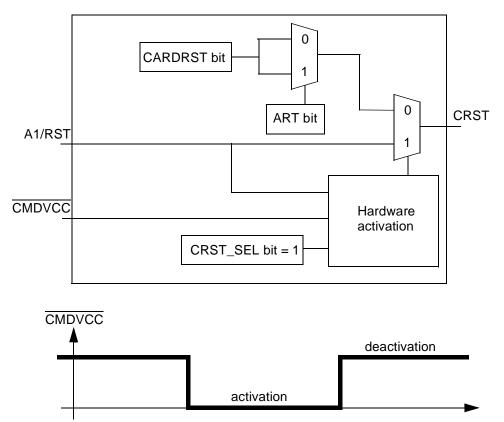

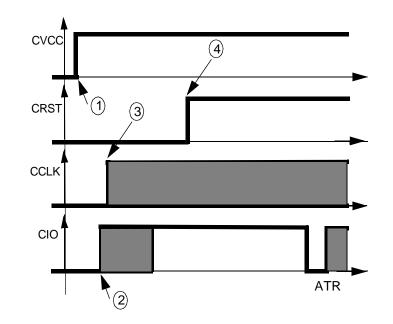

### Hardware Activation (DC/DC started with CMDVCC)

Initial conditions:

CARDDET bit must be configured in accordance to the smart card connector polarity.

IT\_SEL bit, CRST\_SEL bit (see CONFIG4 register) must be set and CARDRST bit (see INTERFACE register) must be cleared. A smart card must be detected to enable to start the DC/DC (CVCC= 3V or 5V).

The hardware activation sequence is started by hardware with  $\overline{CMDVCC}$  pin going high to low. It follows this **automatic** sequence:

- CIO / CC4 / CC8 and IO / C4 / C8 are respectively linked together (IODIS bit is cleared).

- The DC/DC is started and CVCC is set according to the A0/3V pin: 5V (Class A) if A0/3V is High and 3V (Class B) is A0/3V is Low.

- CCLK signal is enabled (CKSTOP bit cleared) when CVCC has settled to the programmed voltage (see Electrical Characteristics) and the level on A1/RST is 0. The CCLK source can be DCCLK signal, CLK signal, A2/CK signals or CARDCK bit (see Figures 5).

- CRST signal is linked with A1/RST pin as soon as A1/RST pin level is 0. A rising edge on A1/RST pin set the CRST pin.

Note: 1. The card must be deactivated to change the voltage.

Figure 10. Activation sequence with CMDVCC

Note: For NDS applications, the host usually starts activation with A1/RST = 0.

14 AT83C24

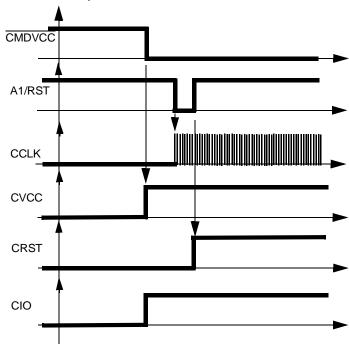

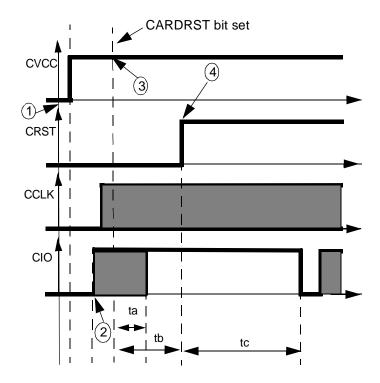

#### Software Activation (DC/DC Started With Writing in VCARD[1:0] bits) and ART bit = 1

Initial conditions: CARDRST bit = 0, CKSTOP bit =1, IODIS bit = 1.

The following sequence can be applied:

- 1. Card Voltage is set by software to the required value (VCARD[1:0] bits in CONFIG0 register). This writing starts the DC/DC.

- Wait the end of the DC/<u>DC</u> init with a polling on VCARDOK bit (STATUS register) or wait for PRES/INT to go Low if enabled (if IT\_SEL bit = 0 in CONFIG4 register). When VCARDOK bit is set (by hardware), CARDIO bit should be set by software.

- 3. CKSTOP, IODIS are programmed by software. CKSTOP bit is reset to have the clock running. IODIS is reset to drive the I/O, C4, C8 pins and the CIO,CC4, CC8 pins according to each other.

- 4. CARDRST bit (see INTERFACE register) is set by software.

Automatic Reset Transition description:

A 16-bit counter starts when CARDRST bit is set. It counts card clock cycles. The CRST signal is set when the counter reaches the TIMER[1-0] value which corresponds to the "tb" time (Figure 11). The counter is reseted when the CRST pin is released and it is stopped at the first start bit of the Answer To Request (ATR) on CIO pin.

The CIO pin is not checked during the first 200 clock cycles (ta on Figure 11). If the ATR arrives before the counter reaches Timer[1-0] value, the activation sequence fails, the CRST signal is not set and the Capture[1-0] register contains the value of the counter at the arrival of the ATR.

If the ATR arrives after the rising edge on CRST pin and before the card clock counter overflows (65535 clock cycles), the activation sequence completes. The Capture[1-0] register contains the value of the counter at the arrival of the ATR (tc time on Figure 11).

Figure 11. Software activation with ART bit = 1

ISO 7816 constraints: ta = 200 card clock cycles

400 card clock cycles< = tb

400 card clock cycles< = tc < = 40000 card clock cycles

Note: Timer[1-0] reset value is 400.

#### Software Activation (DC/DC Started by Writing in VCARD[1:0] bits) and ART bit = 0

The activation sequence is controlled by software using TWI commands, depending on the cards to support. For ISO 7816 cards, the following sequence can be applied:

- 1. Card Voltage is set by software to the required value (VCARD[1:0] bits in CONFIG0 register). This writing starts the DC/DC.

- Wait of the end of the DC/<u>DC</u> init with a polling on VCARDOK bit (STATUS register) or wait for PRES/INT to go Low if enabled (if IT\_SEL bit = 0 in CONFIG4 register). When VCARDOK bit is set (by hardware), CARDIO bit should be set by software.

- 3. CKSTOP, IODIS are programmed by software. CKSTOP bit is reset to have the clock running. IODIS is reset to drive the I/O, C4, C8 pins and the CIO,CC4, CC8 pins according to each other.

- 4. CRST pin is controlled by software using CARDRST bit (see INTERFACE register).

Downloaded from Elcodis.com electronic components distributor

Figure 12. Software activation without automatic control (ART bit = 0)

- Note: It is assumed that initially VCARD[1:0], CARDCK, CARDIO and CARDRST bits are cleared, CKSTOP and IODIS are set (those bits are further explained in the registers description)

- Note: The user should check the AT83C24 status and possibly resume the activation sequence if one TWI transfer is not acknowledged during the activation sequence.

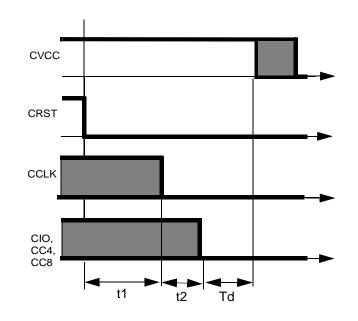

### **Deactivation Sequence**

The card automatic deactivation is triggered when one the following condition occurs:

- ICARDERR bit is set by hardware

- VCARDERR bit is set by hardware (or by software)

- INSERT is set and CARDIN is cleared (card extraction)

- SHUTDOWN is set by software

- CMDVCC goes from Low to High

- Power fail on VCC (see POWERMON bit in CONFIG4 register)

- Reset pin going low

It is a self-timed sequence which cannot be interrupted when started (see Figure 13). Each step is separated by a delay based on Td equal to 8 periods of the DC/DC clock, typically  $2 \,\mu$ s:

- 1. T0: CARDRST is cleared, SHUTDOWN bit set.

- 2. T0 + 5 x Td:CARDCK is cleared, CKSTOP, CARDIO and IODIS are set.

- 3. T0 + 6 x Td: CARDIO is cleared.

- 4. T0 + 7 x Td: VCARD[1-0] = 00.

Figure 13. Deactivation Sequence

- Notes: 1. Setting ICARDERR by software does not trigger a deactivation. VCARDERR can be used to deactivate the card by software.

- 2. t1=5 to 5.5\*Td, and t2=0.5\*Td to Td.

#### **Transparent Mode** If the microcontroller outputs ISO 7816 signals, a transparent mode allows to connect RST/CLK and I/O/C4/C8 signals after an electrical level control. The AT83C24 level shifters adapt the card signals to the smart card voltage selection.

The CRST and CCLK microcontroller signals can be respectively connected to the A1/RST and A2/CK pins.

The CRST\_SEL bit (in CONFIG4 register) selects standard or transparent configuration for the CRST pin. CKS in CONFIG2 allows to select standard or transparent configuration for the CCLK pin. So CCLK and CRST are independent. A2/CK to A0/3V inputs always give the TWI address at reset. The A0/3V pin can be used for TWI addressing and easily connect two AT83C24 devices on the same TWI bus.

#### Figure 14. Transparent Mode Description

18

## Power Modes

Two power-down modes are available to reduce the AT83C24 power consumption (see STUTDOWN bit in CONFIG1 register and LP bits in CONFIG3 register).

To enter in the mode number 4 (see Table 5), the sequence is the following:

- First select the Low-power mode by setting the LP bit

- The activation of the SHUTDOWN bit can then be done.

The AT83C24 exits Power-down if a software/hardware reset is done or if SHUTDOWN bit is cleared. The AT83C24 is then active immediately.

Either a hardware reset or a TWI command clearing the SHUTDOWN bit can cause an exit from Power-down. The internal registers retain their value during the shutdown mode.

In Power-down mode, the device is sleeping and waiting for a wake up condition.

To reduce power consumption, the User should stop the clock on the CLK input after setting the SHUTDOWN bit. The clock can be enabled again just before exiting SHUT-DOWN (at least 10 µs before a START bit on SDA).

Table 5.

Power Modes Description

| Mode<br>Number | Shutdown<br>Bit | LP<br>Bit | STEPREG | VCARD[1:0] | Typical<br>Supply<br>Current | Description                                                                                                      |

|----------------|-----------------|-----------|---------|------------|------------------------------|------------------------------------------------------------------------------------------------------------------|

| 1              | 0               | Х         | 0       | 11         | 160 mA<br>30 mA              | Step up mode: VCC = 3V, CVCC = 5V,<br>lcard = 65mA<br>lcard = 0                                                  |

| 2              | 0               | Х         | 1       | 11         | 70 mA                        | Regulator mode: VCC = 5.25V, CVCC = 5V,<br>Icvcc = 65mA                                                          |

| 3              | 0               | Х         | Х       | 00         | 3 mA                         | DC/DC off, CLK = 10MHz, VCC=3V to 5V                                                                             |

| 4              | 1               | 0         | Х       | 00         | 90 µA                        | The TWI interface of the AT83C24 is active<br>but its analog blocs are switched off to reduce<br>the consumption |

| 5              | 1               | 1         | Х       | 00         | 30 µA                        | Pulsed mode of the internal 3V logic regulator                                                                   |

### **Power Monitoring**

The AT83C24 needs only one power supply to run: VCC.

If the microcontroller outputs signals with a different electrical level, the host positive supply is connected to EVCC.

EVCC and VCC pins can be connected together if they have the same voltage.

• If EVCC and VCC have different electrical levels:

The EVCC pin and RESET pin should be connected with a resistor bridge. RESET pin high level must be higher than VIH (see Table 19). When EVCC drops, RESET pin level drops too. A deactivation sequence starts if a card was active.

Then the AT83C24 resets if RESET pin stays low.

• If EVCC and VCC have the same value, then they should be connected:

The AT83C24 integrates an internal 3V regulator to feed its logic from the VCC supply. The bit powermon allows the user to select if the internal PFD monitors VCC or the internal regulated 3V. If the PFD monitors VCC (POWERMON bit=0), a deactivation is performed if VCC falls below VPFDP (see VPFDP value in the datasheet). Same deactivation is performed if the internal 3V falls below VPFDP and POWER-MON bit = 1.

## Registers

| Table 6. | CONFIG0 | (Config Byte 0 | ) |

|----------|---------|----------------|---|

|----------|---------|----------------|---|

| 7             | 6                   |      | 5                                                                                                                                                                                                                                                                                                                                                                                  | 4                                                                                                                                                                                                                                                                                                                             | 3        | 2        | 1      | 0      |  |  |

|---------------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--------|--------|--|--|

| 1             | 0                   | AT   | RERR                                                                                                                                                                                                                                                                                                                                                                               | INSERT                                                                                                                                                                                                                                                                                                                        | ICARDERR | VCARDERR | VCARD1 | VCARD0 |  |  |

| Bit<br>Number | Bit Mnemo           | onic | Descrip                                                                                                                                                                                                                                                                                                                                                                            | otion                                                                                                                                                                                                                                                                                                                         |          |          |        |        |  |  |

| 7-6           | 1-0                 |      | These b                                                                                                                                                                                                                                                                                                                                                                            | These bits cannot be programmed and are read as 1-0.                                                                                                                                                                                                                                                                          |          |          |        |        |  |  |

| 5             | ATRER               | R    | Answer to Reset Interrupt<br>This bit is set when the card clock counter overflows (no falling edge on CI<br>is received before the overflow of the card clock counter).<br>This bit is cleared by hardware when this register is read. It can be set by<br>software for test purpose. The reset value is 0.                                                                       |                                                                                                                                                                                                                                                                                                                               |          |          |        |        |  |  |

| 4             | INSER               | Т    | Card Insertion Interrupt<br>This bit is set when a card is inserted or extracted: a change in CARDIN<br>filtered according to CDS[2-0]. After power up, if the level on CPRES pi<br>then INSERT bit is set.<br>It can be set by software for test purpose.<br>This bit is cleared by hardware when this register is read. It cannot be cl<br>by software.<br>The reset value is 0. |                                                                                                                                                                                                                                                                                                                               |          |          |        |        |  |  |

| 3             | ICARDE              | RR   | This bit<br>software<br>perform<br>This bit<br>by softw                                                                                                                                                                                                                                                                                                                            | <b>Card Over Current Interrupt</b><br>This bit is set when an over current is detected on CVCC. It can be set by software for test purpose (no card deactivation is performed, no IT is performed).<br>This bit is cleared by hardware when this register is read. It cannot be cleared by software.<br>The reset value is 0. |          |          |        |        |  |  |

| 2             | VCARDE              | RR   | Card Out of Range Voltage Interrupt<br>This bit is set when the output voltage goes out of the voltage range spec<br>by VCARD field. It can be set by software for test purpose and deactivate<br>card.<br>This bit is cleared by hardware when this register is read. It cannot be clear<br>by software.<br>The reset value is 0.                                                 |                                                                                                                                                                                                                                                                                                                               |          |          |        |        |  |  |

| 1-0           | VCARD[ <sup>7</sup> | 1:0] | VCARD<br>VCARD<br>VCARD<br>VCARD<br>VCARD<br>VCARD<br>No card<br>1.8V, 3\<br>changin                                                                                                                                                                                                                                                                                               | · ·                                                                                                                                                                                                                                                                                                                           |          |          |        |        |  |  |

## Table 7. CONFIG 1 (Config Byte 1)

| 7             | 6               | 5                                                                                                                                                                                                                                                                                                                                                                                                  | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                                                                                                                                                     | 2                                                                                     | 1                                                     | 0           |  |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------|-------------|--|--|--|

| X             | ART             | SHUTDOWN                                                                                                                                                                                                                                                                                                                                                                                           | CARDDET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PULLUP                                                                                                                                                | CDS2                                                                                  | CDS1                                                  | CDS0        |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                       |                                                                                       |                                                       |             |  |  |  |

| 7             | х               | This bit shou                                                                                                                                                                                                                                                                                                                                                                                      | ld not be set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                       |                                                                                       |                                                       |             |  |  |  |

| 6             | ART             | Set this bit to<br>Clear this bit<br>in CARDRS1                                                                                                                                                                                                                                                                                                                                                    | Automatic Reset Transition<br>Set this bit to have the CRST pin changed according to activation sequence.<br>Clear this bit to have the CRST pin immediately following the value programme<br>n CARDRST.<br>The reset value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                       |                                                                                       |                                                       |             |  |  |  |

| 5             | SHUTDOWN        | sequence wi<br>Clear this bit                                                                                                                                                                                                                                                                                                                                                                      | Shutdown<br>Set this bit to reduce the power consumption. An automatic de-activation<br>equence will be done.<br>Clear this bit to enable VCARD[1:0] selection.<br>The reset value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                       |                                                                                       |                                                       |             |  |  |  |