MC68HC05CxRG/AD REV 1

## HC05

MC68HC05C4,C8,C9 MC68HC705C8 MC68HC805C4 MC68HCL05C4,C8 MC68HSC05C4,C8

PROGRAMMING REFERENCE GUIDE

The MC68HC05 Family of HCMOS devices covered in this reference guide are as follows:

MC68HC05C4

MC68HC05C8

MC68HC05C9

MC68HC705C8

MC68HC805C4

MC68HCL05C4

MC68HCL05C8

MC68HSC05C4

MC68HSC05C8

**BLOCK DIAGRAMS**

**MEMORY MAPS**

REGISTER/CONTROL BIT ASSIGNMENTS

INSTRUCTIONS ADDRESSING MODES EXECUTION TIMES

**MECHANICAL DATA**

HEX/DEC CONVERSION ASCII CHART

**BLOCK DIAGRAMS**

**MEMORY MAPS**

REGISTER/CONTROL BIT ASSIGNMENTS

INSTRUCTIONS

ADDRESSING MODES

EXECUTION TIMES

**MECHANICAL DATA**

HEX/DEC CONVERSION ASCII CHART

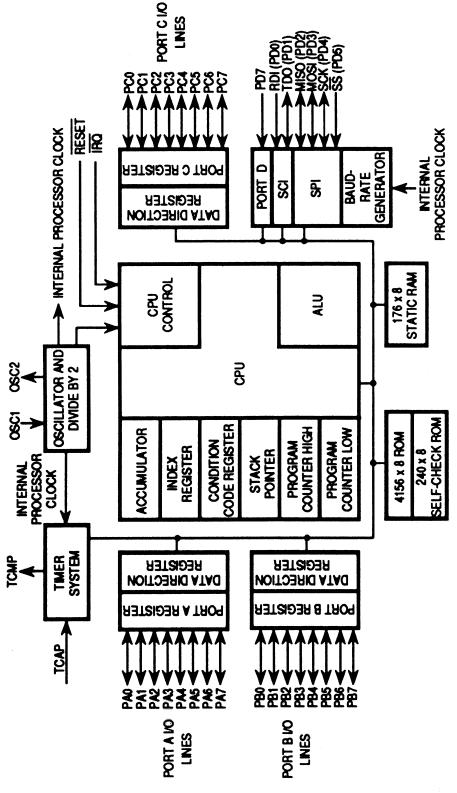

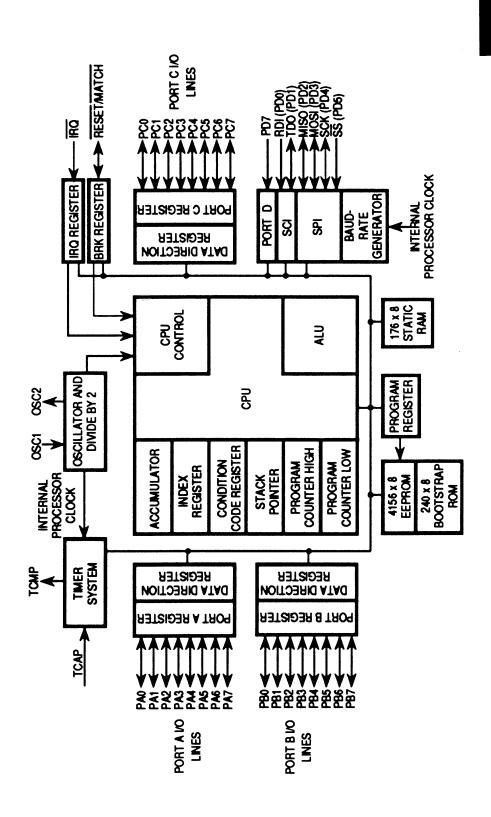

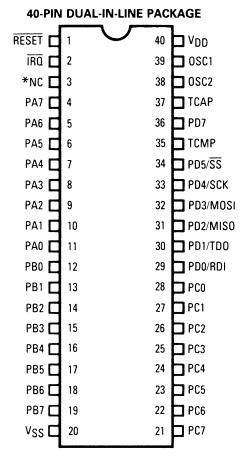

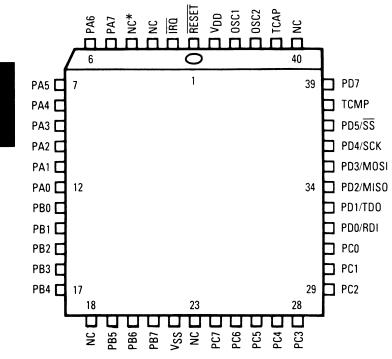

## Freescale Semiconductor, Inc. MC68HC05C4 MC68HCL05C4 MC68HSC05C4 BLOCK DIAGRAM

For More Information On This Product, Go to: www.freescale.com

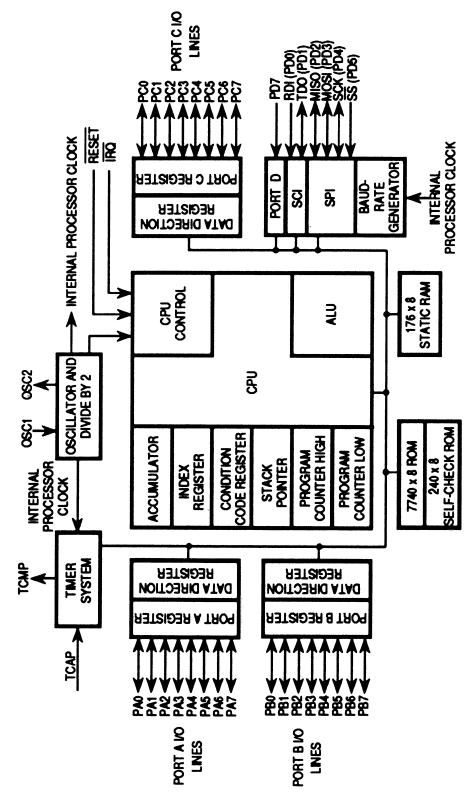

## Freescale Semiconductor, Inc. MC68HC05C8 MC68HCL05C8 MC68HSC05C8 BLOCK DIAGRAM

For More Information On This Product, Go to: www.freescale.com

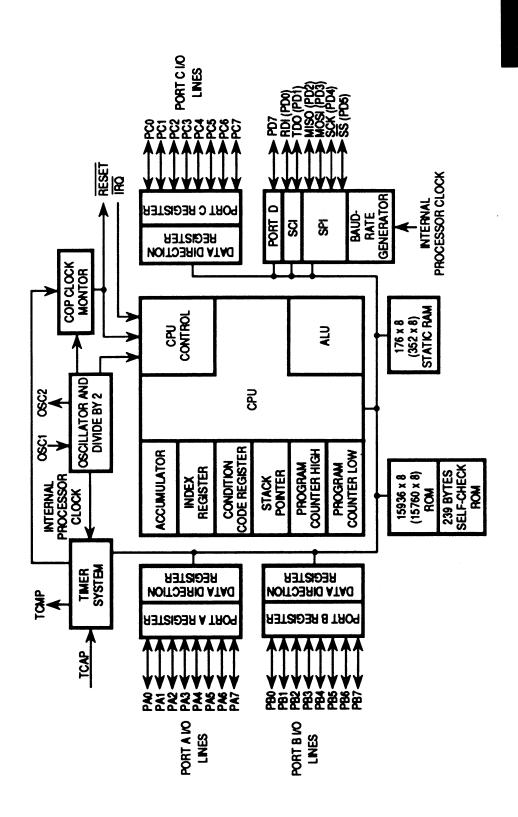

## Freescale Semiconductor, Inc. MC68HC05C9 BLOCK DIAGRAM

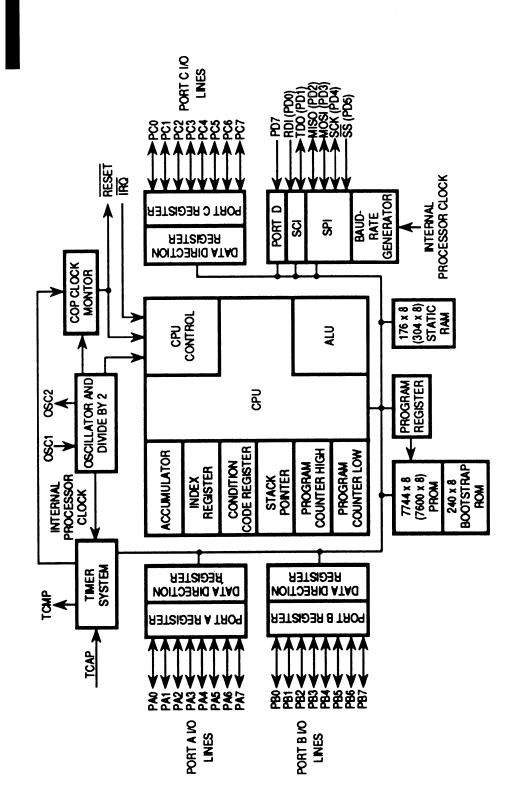

## Freescale Semiconductor, Inc. MC68HC705C8 BLOCK DIAGRAM

## Freescale Semiconductor, Inc. MC68HC805C4 BLOCK DIAGRAM

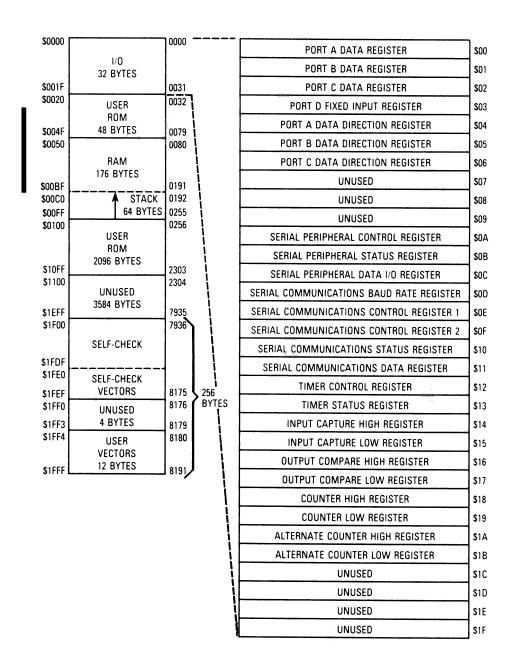

#### Freescale Semiconductor, Inc. MC68HC05C4 MC68HCL05C4 MC68HSC05C4 MEMORY MAP

## Freescale Semiconductor, Inc. MC68HC05C8 MC68HCL05C8 MC68HSC05C8 MEMORY MAP

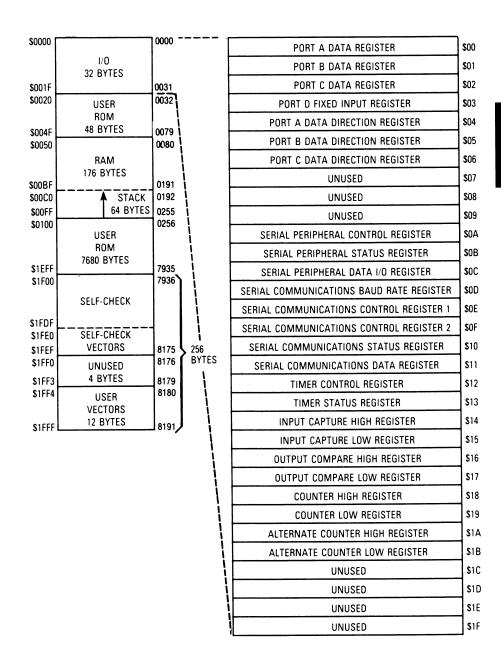

## Freescale Semiconductor, Inc. MC68HC05C9 MEMORY MAP

| \$0000       |                                         | 00000          |     | PORT A DATA REGISTER                     | ] |

|--------------|-----------------------------------------|----------------|-----|------------------------------------------|---|

|              | 1/0<br>32 BYTES                         |                |     | PORT B DATA REGISTER                     | ٦ |

| \$001F       |                                         | 00031          |     | PORT C DATA REGISTER                     | 1 |

| \$0020       | PAGE ZERO                               | 00032          |     | PORT D DATA REGISTER                     | 1 |

| \$004F       | ROM OR RAM<br>48 BYTES                  | 00070          | ı   | PORT A DATA DIRECTION REGISTER           | 1 |

| \$0050       | , , , , , , , , , , , , , , , , , , , , | 00079<br>00080 |     | PORT B DATA DIRECTION REGISTER           | 1 |

|              | RAM                                     |                | 1   | PORT C DATA DIRECTION REGISTER           | 1 |

|              | 176 BYTES                               | 00191          | 1   | PORT D DATA DIRECTION REGISTER           | 1 |

|              | STACK                                   | 00192          | 1   | UNUSED                                   | 1 |

| 1400         | 64 BYTES                                | 100233         | 1   | UNUSED                                   | 1 |

| 50100        | ROM OR RAM                              | 00256          | 1   | SERIAL PERIPHERAL CONTROL REGISTER       | 1 |

| 017F         | 128 BYTES                               | 00383          | 1   | SERIAL PERIPHERAL STATUS REGISTER        | 1 |

| 0180         | MAIN MEMORY ROM                         | 00384          |     | SERIAL PERIPHERAL DATA I/O REGISTER      | 1 |

| 3EFF         | 15744 BYTES                             | 16107          | 1   | SERIAL COMMUNICATIONS BAUD RATE REGISTER | 1 |

| 3F00         | SELF-CHECK ROM                          | 16127<br>16349 | Ì   | SERIAL COMMUNICATIONS CONTROL REGISTER 1 | 1 |

| 3FDE         | 223 BYTES                               | 16571          | Ì   | SERIAL COMMUNICATIONS CONTROL REGISTER 2 | 1 |

| 3FDF<br>3FE0 | OPTION REGISTER                         | 16572<br>16573 | Ì   | SERIAL COMMUNICATIONS STATUS REGISTER    | 1 |

| 31 20        | SELF-CHECK                              | 103/3          | į   | SERIAL COMMUNICATIONS DATA REGISTER      | 1 |

| 3FEF         | VECTORS<br>16 BYTES                     | 16588          | į   | TIMER CONTROL REGISTER                   | 1 |

| 3FF0         | USER                                    | 16589          | į   | TIMER STATUS REGISTER                    | 1 |

|              | VECTORS                                 | İ              | Ì   | INPUT CAPTURE HIGH REGISTER              | 1 |

| 3FFF         | 16 BYTES                                | 16604          | 1   | INPUT CAPTURE LOW REGISTER               | 1 |

|              |                                         |                | 1   | OUTPUT COMPARE HIGH REGISTER             | 1 |

|              |                                         |                | 1   | OUTPUT COMPARE LOW REGISTER              | 1 |

|              |                                         |                | 1   | COUNTER HIGH REGISTER                    | 1 |

|              |                                         |                |     | COUNTER LOW REGISTER -                   | 1 |

|              |                                         |                | . } | ALTERNATE COUNTER HIGH REGISTER          | 1 |

|              |                                         |                | 1   | ALTERNATE COUNTER LOW REGISTER           | 1 |

|              |                                         |                | 1   | UNUSED                                   | 1 |

|              |                                         |                | \   | COP RESET REGISTER                       | 1 |

|              |                                         |                | i i | COP CONTROL REGISTER                     | 1 |

|              |                                         |                | ij  | UNUSED                                   | 1 |

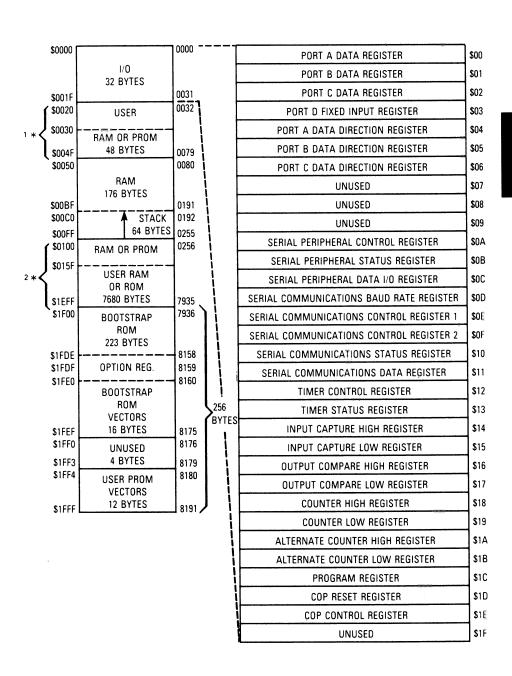

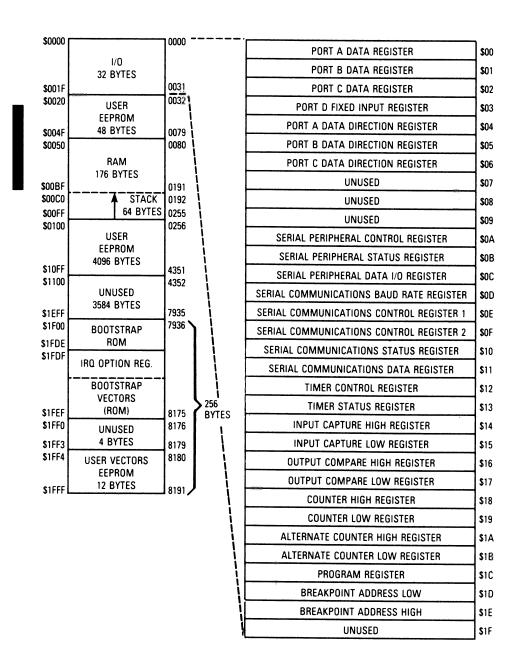

### Freescale Semiconductor, Inc. MC68HC705C8 MEMORY MAP

(Option Register \$1FDF RAM1=0 and RAM0=0) (POR or Master Reset)

\*The nature of this memory block (RAM or PROM) is controlled by bits RAM0 and RAM1 of the Option Register (\$1FDF).

1. RAM0 · 0 — 48 Bytes User PROM

RAM0 · 1 — 32 Bytes RAM with 16 Bytes Unused

2. RAM1 0 — 7680 Bytes User PROM RAM1 1 — 7584 Bytes User PROM and 96 Bytes of RAM

> For More Information On This Product, Go to: www.freescale.com

### Freescale Semiconductor, Inc. MC68HC805C4 MEMORY MAP

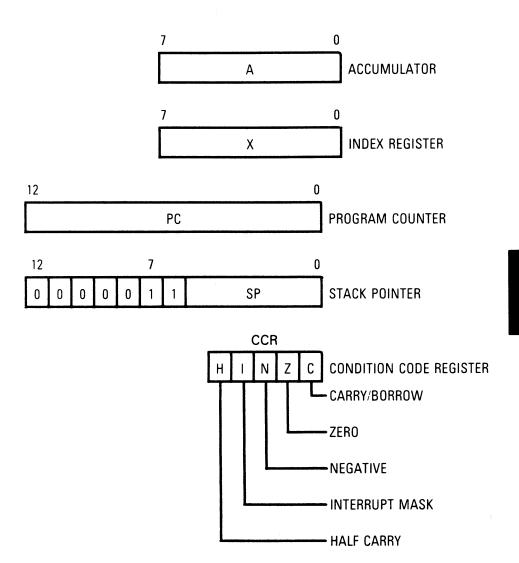

## PROGRAMMING MODEL INTERRUPT STACKING ORDER PROGRAMMING MODEL

#### INTERRUPT STACKING ORDER

NOTE: Since the Stack Pointer decrements during pushes, the PCL is stacked first followed in Philippe Only produce; tack is in the reverse order. Go to: www.freescale.com

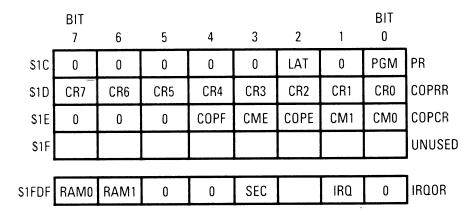

## Freescale Semiconductor, Inc. REGISTER AND CONTROL BIT SUMMARY

|      | BIT<br>7 | 6    | 5     | 4     | 3     | 2     | 1     | BIT<br>0 |                   |

|------|----------|------|-------|-------|-------|-------|-------|----------|-------------------|

| \$00 | PA7      | PA6  | PA5   | PA4   | PA3   | PA2   | PA1   | PA0      | PORTA             |

| \$01 | PB7      | PB6  | PB5   | PB4   | PB3   | PB2   | PB1   | PB0      | PORTB             |

| \$02 | PC7      | PC6  | PC5   | PC4   | PC3   | PC2   | PC1   | PC0      | PORT C            |

| \$03 | PD7/*    |      | PD5/* | PD4/* | PD3/* | PD2/* | PD1/* | PD0/*    | PORTD             |

| \$04 | DDA7     | DDA6 | DDA5  | DDA4  | DDA3  | DDA2  | DDA1  | DDA0     | DDRA              |

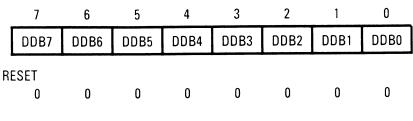

| \$05 | DDB7     | DDB6 | DDB5  | DDB4  | DDB3  | DDB2  | DDB1  | DDB0     | DDRB              |

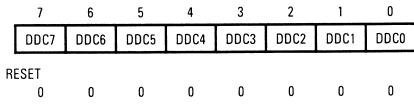

| \$06 | DDC7     | DDC6 | DDC5  | DDC4  | DDC3  | DDC2  | DDC1  | DDC0     | DDRC              |

| \$07 | DDD7     |      | DDD5  | DDD4  | DDD3  | DDD2  | DDD1  | DDD0     | DDRD <sup>†</sup> |

| \$08 |          |      |       |       |       |       |       |          | UNUSED            |

| \$09 |          |      |       |       |       |       |       |          | UNUSED            |

| \$0A | SPIE     | SPE  | DWOM  | MSTR  | CPOL  | СРНА  | SPR1  | SPR0     | SPCR              |

| \$0B | SPIF     | WCOL |       | MODF  |       |       |       |          | SPSR              |

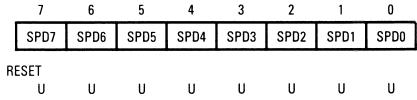

| \$0C | SPD7     | SPD6 | SPD5  | SPD4  | SPD3  | SPD2  | SPD1  | SPD0     | SPDR              |

| \$0D |          |      | SCP1  | SCP0  |       | SCR2  | SCR1  | SCR0     | BAUD              |

| \$0E | R8       | T8   |       | М     | WAKE  |       |       |          | SCCR1             |

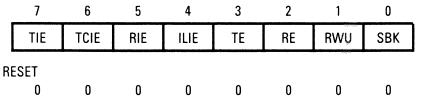

| \$0F | TIE      | TCIE | RIE   | ILIE  | TE    | RE    | RWU   | SBK      | SCCR2             |

| \$10 | TDRE     | TC   | RDRF  | IDLE  | OR    | NF    | FE    |          | SCSR              |

| \$11 | SCD7     | SCD6 | SCD5  | SCD4  | SCD3  | SCD2  | SCD1  | SCD0     | SCDAT             |

| \$12 | ICIE     | OCIE | TOIE  | 0     | 0     | 0     | IEDG  | 0LVL     | TCR               |

| \$13 | ICF      | OCF  | TOF   | 0     | 0     | 0     | 0     | 0        | TSR               |

| \$14 | ICH7     | ICH6 | ICH5  | ICH4  | ICH3  | ICH2  | ICH1  | ICH0     | ICHR              |

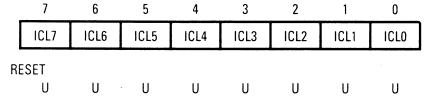

| \$15 | ICL7     | ICL6 | ICL5  | ICL4  | ICL3  | ICL2  | ICL1  | ICLO     | ICLR              |

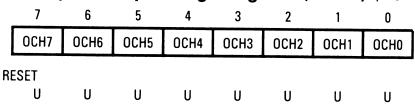

| \$16 | OCH7     | OCH6 | OCH5  | OCH4  | OCH3  | OCH2  | OCH1  | OCH0     | OCHR              |

| \$17 | OCL7     | OCL6 | OCL5  | OCL4  | OCL3  | OCL2  | OCL1  | OCLO     | OCLR              |

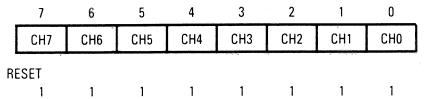

| \$18 | CH7      | CH6  | CH5   | CH4   | CH3   | CH2   | CH1   | CH0      | CHR               |

| \$19 | CL7      | CL6  | CL5   | CL4   | CL3   | CL2   | CL1   | CLO      | CLR               |

| \$1A | ACH7     | ACH6 | ACH5  | ACH4  | ACH3  | ACH2  | ACH1  | ACH0     | ACHR              |

| \$1B | ACL7     | ACL6 | ACL5  | ACL4  | ACL3  | ACL2  | ACL1  | ACL0     | ACLR              |

| \$1C |          |      |       |       |       |       |       |          | UNUSED            |

| \$1D |          |      |       |       |       |       |       |          | UNUSED            |

| \$1E |          |      |       |       |       |       |       |          | UNUSED            |

| \$1F |          |      |       |       |       |       |       |          | UNUSED            |

|      |          |      |       |       |       |       |       |          |                   |

<sup>\*</sup>Denotes fixed input port, see following page.

<sup>†</sup>MC68HC05C9 only For More Information On This Product, Go to: www.freescale.com

## Freescale Semiconductor, Inc. REGISTER AND CONTROL BIT SUMMARY

#### (PORT D FIXED INPUT REGISTER)

|        | BIT  |      |      |      |      |      |      | BIT  |        |

|--------|------|------|------|------|------|------|------|------|--------|

|        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |        |

| \$07   | DDD7 |      | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 |        |

|        |      |      |      |      |      |      |      |      |        |

| \$1D   | CR7  | CR6  | CR5  | CR4  | CR3  | CR2  | CR1  | CR0  | COPRR  |

| \$1E   | R7   | R6   | R5   | COPF | CME  | COPE | CM1  | CM0  | COPCR  |

| \$3FDF | RAM0 | RAM1 |      |      |      |      | IRQ  |      | OPTREG |

#### (MC68HC05C9 ONLY)

#### (MC68HC705C8 ONLY)

|        | BIT<br>7 | 6    | 5     | 4   | 3     | 2    | 1          | BIT<br>0 |        |

|--------|----------|------|-------|-----|-------|------|------------|----------|--------|

| \$1C   | 0        | CPEN | 0     | 0   | ERASE | LATA | LATB       | EEPGM    | PR     |

| \$1D   | Α7       | A6   | A5    | Α4  | A3    | A2   | A1         | A0       | ARL    |

| \$1E   | 0        | 0    | МАТСН | A12 | A11   | A10  | <b>A</b> 9 | A8       | ARH    |

| \$1F   |          |      |       |     |       |      |            |          | UNUSED |

|        |          |      |       |     |       |      | 1          |          | i      |

| \$1FDF | 0        | 0    | 0     | 0   | 0     | 0    | IRQ        | 0        | IRQOR  |

For More Information On This Product, Go to: Www.freescale.com

#### Alternate Counter High Register (ACHR) \$1A

|    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----|------|------|------|------|------|------|------|------|

|    | ACH7 | ACH6 | ACH5 | ACH4 | ACH3 | ACH2 | ACH1 | ACH0 |

| RI | ESET | 1    | 1    | 1    | 4    | 0    |      | 4    |

#### **ACLR**

#### Alternate Counter Low Register (ACLR) \$1B

|    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |   |

|----|------|------|------|------|------|------|------|------|---|

|    | ACL7 | ACL6 | ACL5 | ACL4 | ACL3 | ACL2 | ACL1 | ACL0 |   |

| RI | ESET |      |      |      |      |      |      |      | • |

|    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 1    |   |

#### **ARH**

#### (MC68HC805C4 ONLY)

#### Hardware Breakpoint Register High (ARH) \$1E

|    | 7        | 6 | 5     | 4   | 3   | 2   | 1  | 0  |

|----|----------|---|-------|-----|-----|-----|----|----|

|    | 0 _      | 0 | MATCH | A12 | A11 | A10 | A9 | A8 |

| RE | SET<br>n | n | 0     | 0   | 0   | 0   | 0  | Ω  |

MATCH — An instruction with the same address as that in the breakpoint register was fetched.

1 = Breakpoint enabled

0 = Breakpoint disabled

A12-A8 — Breakpoint address bits A12-A8

#### **ARL**

#### (MC68HC805C4 ONLY)

#### Hardware Breakpoint Register Low (ARL) \$1D

| _  | 7          | 6  | 5  | 4 . | 3  | 2  | 1  | 0  |

|----|------------|----|----|-----|----|----|----|----|

|    | <b>A</b> 7 | A6 | A5 | A4  | А3 | A2 | A1 | A0 |

| RE | SET<br>0   | 0  | 0  | 0   | 0  | 0  | 0  | 0  |

For More Information On This Product, Go to: www.freescale.com

#### Baud Rate Register (BAUD) \$0D

The baud rate register is used to select the SCI transmitter and receiver baud rate. SCP0 and SCP1 prescaler bits are used in conjunction with the SCR2–SCR0 baud rates to provide multiple baud rate combinations for a given crystal frequency. Bits 3, 6, and 7 always read zero.

|    | 7        | 6 | 5    | 4    | 3 | 2    | 1    | 0    |  |

|----|----------|---|------|------|---|------|------|------|--|

|    | _        |   | SCP1 | SCP0 | _ | SCR2 | SCR1 | SCR0 |  |

| RE | SET<br>— |   | 0    | 0    | _ | U    | U    | U    |  |

SCP0 — SCI Prescaler Bit 0 SCP1 — SCI Prescaler Bit 1

Two prescaler bits are used to increase the range of standard baud rates controlled by the SCR2-SCR0 bits. Prescaler internal processor clock division versus bits levels are listed in Table 1.

SCR0 — SCI Baud Rate Bit 0

SCR1 — SCI Baud Rate Bit 1

SCR2 — SCI Baud Rate Bit 2

Three baud rate bits are used to select the baud rates of the SCI transmitter and SCI receiver. Baud rates versus bit levels are listed in Table 2.

Tables 1 and 2 tabulate the divide chain used to obtain the baud rate clock (transmit clock). The actual divider chain is controlled by the combined SCP1–SCP0 and SCR2–SCR0 bits in the baud rate register. All divided frequencies shown in Table 1 represent the final baud rate resulting from the internal processor clock division shown in the divided by column only (prescaler division only). Table 2 lists the prescaler output divided by the action of the SCI select bits (SCR2–SCR0). For example, assume that a 9600 Hz baud rate is required with a 2.4576 MHz external crystal. In this case, the prescaler bits (SCP1–SCP0) could be configured as a divided-by-two. Using the same crystal, the 9600 baud rate can be obained with a prescaler divided-by-one and the SCR2–SCR0 bits configured for a divide-by-eight.

# Table 1. Prescaler Highest Baud Rate Frequency Output

**BAUD**

| SCP Bit | Bit     | Clock*                                  |                                                      |                                                       | Crystal Freq                                       | Crystal Frequency MHz                            |                                                  |                                                |

|---------|---------|-----------------------------------------|------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------------------------------------|

| -       | 0       | Divided By                              | 8.0                                                  | 4.194304                                              | 4.0                                                | 2.4576                                           | 2.0                                              | 1.8432                                         |

| 0 0     | 0 1 0   | - E 4 E                                 | 250.00 kHz<br>83.332 kHz<br>62.500 kHz<br>19.200 kHz | 131.072 kHz<br>43.691 kHz<br>32.768 kHz<br>10.082 kHz | 125.000 kHz<br>41.666 kHz<br>31.250 kHz<br>9600 Hz | 76.80 kHz<br>25.60 kHz<br>19.20 kHz<br>5.907 kHz | 62.60 kHz<br>20.833 kHz<br>15.625 kHz<br>4800 Hz | 57.60 kHz<br>19.20 kHz<br>14.40 kHz<br>4430 Hz |

| Boford  | 4+ 0+ 4 | Boford to the integral seconds of or or | 11-                                                  |                                                       |                                                    |                                                  |                                                  |                                                |

Refers to the internal processor clock.

NOTE: The divided frequencies shown in Table 1 represent baud rates which are the highest transmit baud rate (Tx) that can be obtained by a specific crystal frequency and only using the prescaler division. Lower baud rates may be obtained by providing a further division using the SCI rate select bits as shown below for some representative prescaler outputs.

## Transmit Baud Rate Output for a Given Prescaler Output Table 2.

| Г                                                 | T           |                                                                                                           |

|---------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------|

| ***************************************           | 9600 Hz     | 9600 Hz<br>4800 Hz<br>2400 Hz<br>1200 Hz<br>600 Hz<br>300 Hz<br>150 Hz                                    |

| Rate Output                                       | 19.20 kHz   | 19.20 kHz<br>9600 Hz<br>4800 Hz<br>2400 Hz<br>1200 Hz<br>600 Hz<br>300 Hz<br>150 Hz                       |

| Representative Highest Prescaler Baud Rate Output | 76.80 kHz   | 76.80 kHz<br>38.40 kHz<br>19.20 kHz<br>9600 Hz<br>4800 Hz<br>2400 Hz<br>1200 Hz                           |

| Representativ                                     | 32.768 kHz  | 32.768 kHz<br>16.384 kHz<br>8.192 kHz<br>4.096 kHz<br>2.048 kHz<br>1.024 kHz<br>512 Hz<br>256 Hz          |

|                                                   | 131.072 kHz | 131.072 kHz<br>65.536 kHz<br>32.768 kHz<br>16.384 kHz<br>8.192 kHz<br>4.096 kHz<br>2.048 kHz<br>1.024 kHz |

| Divided                                           | By          | 1<br>2<br>4<br>8<br>16<br>32<br>64<br>128                                                                 |

| its                                               | 0           | 0 - 0 - 0 - 0                                                                                             |

| SCR B                                             | 1           | 0000                                                                                                      |

| SC                                                | 2           | 0000                                                                                                      |

| tio                                               | n Õi        | n This Product,                                                                                           |

NOTE: Table 2 illustrates how the SCI select bits can be used to provide tower transmitter baud rate by further dividing the prescaler output frequency. The five examples are only representative samples. In all cases, the baud rates shown are transmit baud rates (transmit clock) and the receive clock is 16 times higher in frequency than the actual baud rate.

For More Informati Go to: www.freescale.com

**BAUD**

**CHR**

#### Counter High Register (CHR) \$18

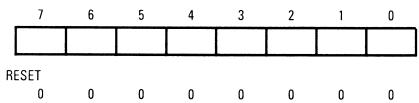

**CLR**

#### Counter Low Register (CLR) \$19

| _  | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |   |

|----|------|-----|-----|-----|-----|-----|-----|-----|---|

|    | CL7  | CL6 | CL5 | CL4 | CL3 | CL2 | CL1 | CLO |   |

| RE | ESET |     |     |     |     |     |     |     | • |

|    | 1    | 1   | 1   | 1   | 1   | 0   | 1   | 1   |   |

#### **COPCR**

#### (MC68HC705C8 ONLY) COP Control Register (COPCR) \$1E

The COPCR shown below is used to control the COP watchdog timer and clock monitor functions.

| 0 0 0 COPF CME COPE | CM1 CM | 10 |

|---------------------|--------|----|

| RESET               | 0 0    |    |

COPF - Computer Operating Properly

1 = COP or clock monitor reset has occurred

0=No COP or clock monitor reset has occurred

CME — Clock Monitor Enable

1 = Clock monitor enabled

0 = Clock monitor disabled

COPE — Computer Operating Properly Enable

1 = COP timeout enabled

0 = COP timeout disabled

CM1 — Computer Operating Properly Mode 1

Used in conjunction with CMO0 to establish the COP timeout period. CM1 can be read and set anytime, but is cleared only by reset. See Table 3.

CM0 — Computer Operating Properly Mode 0

Used in conjunction with CM1 to establish the COP timeout period. CM0 can be read and set anytime, but is cleared only by reset. See Table 3.

Bits 7–5 — Not used\* Always read zero

<sup>\*</sup>In the MC68HC05C9, these bits (R7–R5) are reserved factory test bits.

Table 3. COP Timeout Period

| _ | E/2 <sup>15</sup><br>Divided By | XTAL = 4.0 MHz,<br>E = 2.0 MHz | XTAL = 3.5795 MHz,<br>E = 1.7897 MHz | XTAL = 2.0 MHz, $E = 1.0 MHz$ | XTAL = 1.0 MHz, $E = 0.5 MHz$ |

|---|---------------------------------|--------------------------------|--------------------------------------|-------------------------------|-------------------------------|

| 1 |                                 | 16.38 ms                       | 18.31 ms                             | 32.77 ms                      | 65.54 ms                      |

| 1 | 4                               | 65.54 ms                       | 73.24 ms                             | 131.07 ms                     | 262.14 ms                     |

| 1 | 16                              | 262.95 ms                      | 292.95 ms                            | 524.29 ms                     | 1.048 s                       |

|   | 64                              | 1.048 s                        | 1.172 s                              | 2.097 s                       | 4.194 s                       |

## (MC68HC705C8 AND MC68HC05C9 ONLY)

For More Information On This Product, COPCR Go to: www.freescale.com

#### **COP Reset Register (COPRR) \$1D**

The COPRR shown below is used to control the COP watchdog timer and clock monitor functions.

|       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|-------|---|---|---|---|---|---|---|---------|

|       |   |   |   |   |   | : |   |         |

| RESET |   |   |   |   |   |   |   | <u></u> |

| (     | ) | 0 | 0 | 0 | 0 | 0 | 0 | 0       |

The sequence required to reset the COP timer is as follows: Write \$55 to the COP reset register.

Write \$AA to the COP reset register.

Both write operations must occur in the order listed, but any number of instructions may be executed between the two write operations. The elapsed time between software resets must not be greater than the COP timeout period. Reading the COP reset register does not return valid data and does not affect the watchdog timer.

#### (MC68HC705C8 AND MC68HC05C9 ONLY) COP Reset Register (COPRR) \$1D

The COPRR shown below is used to control the COP watchdog timer and clock monitor functions.

The sequence required to reset the COP time is as follows: Write \$55 to the COP reset register.

Write \$AA to the COP reset register.

Both write operations must occur in the order listed, but any number of instructions may be executed between the two write operations. The elapsed time between software resets must not be greater than the COP timeout period. Reading the COP reset register does not return valid data and does not affect the watchdog timer.

(MC68HC705C8 AND MC68HC05C9 ONLY)

**COPRR**

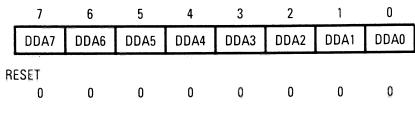

#### Data Direction Register A (DDRA) \$04

DDA7-DDA0 — 0 = Inputs1 = Outputs

#### **DDRB**

#### **Data Direction Register B (DDRB) \$05**

DDB7-DDB0 — 0 = Inputs1 = Outputs

#### **DDRC**

#### **Data Direction Register C (DDRC) \$06**

DDC7-DDC0 — 0 = Inputs1 = Outputs

#### **DDRD**

#### Data Direction Register D (DDRD) \$07

| _  | 7          | 6 | 5    | 4    | 3    | 2    | 1    | 0    |

|----|------------|---|------|------|------|------|------|------|

| I  | DDD7       | _ | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 |

| RE | SET<br>' 0 | 0 | 0    | 0    | 0    | 0    | 0    | 0    |

DDD5-DDD0 —

$$0 = Inputs$$

1 = Outputs

Bits 7,6 — Not used.

#### **ICHR**

#### Input Capture High Register (ICHR) \$14

|    | 7         | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----|-----------|------|------|------|------|------|------|------|

|    | ICH7      | ICH6 | ICH5 | ICH4 | ICH3 | ICH2 | ICH1 | ICH0 |

| RE | ESET<br>U | U    | U    | U    | U    | U    | U    | U    |

#### **ICLR**

#### Input Capture Low Register (ICLR) \$15

#### (MC68HC705C8 ONLY) Option Register (IRQOR) \$1FDF

The option register is used to select the IRQ sensitivity, enable the PROM security, and select the memory configuration.

|    | 7         | 6    | 5 | 4 | 3   | 2 | 1   | 0 |  |

|----|-----------|------|---|---|-----|---|-----|---|--|

|    | RAM0      | RAM1 | 0 | 0 | SEC | _ | IRQ | 0 |  |

| RI | ESET<br>0 | 0    | 0 | 0 | U   | _ | 1   | 0 |  |

RAM0-Random Access Memory Control Bit 0

- 1 = Maps 32 bytes of RAM into page zero starting at address \$0030. Addresses from \$0020 to \$0030 are reserved. This replaces 48 bytes of PROM that were used at these locations. This bit can be read or written at any time, allowing memory configuration to be changed during program execution.

- 0 = Provides 48 bytes of PROM at location \$0030.

- RAM1 Random Access Memory Control Bit 1

- 1 = Maps 96 bytes of RAM into page zero starting at address \$0100. This replaces 96 bytes of PROM that were used at these locations. This bit can be read or written at any time, allowing memory configuration to be changed during program execution.

- 0 = Provides 96 bytes of PROM at location \$0100.

- SEC Security

- 1 = Bootloader disabled, MCU operates only in single-chip mode.

- 0 = Security off, bootloader enabled, expanded mode enabled.

- IRQ-Interrupt Request Bit Sensitivity

- $1 = \overline{IRQ}$  pin is both negative edge- and level-sensitive.

- 0 = IRQ pin is negative edge-sensitive only.

IRQ is set only by reset, but can be cleared by software.

This can only be written once.

Bit 0, 4, 5

Always read zero.

Bit 2

Can be either one or zero.

#### **IRQOR**

#### (MC68HC05C9 ONLY) Option Register (IRQOR) \$3FDF

The option register is used to select the IRQ sensitivity, enable the ROM security, and select the memory configuration.

|    | 7    | 6    | 5 | 4 | 3 | 2 | 1   | 0 |   |

|----|------|------|---|---|---|---|-----|---|---|

|    | RAM0 | RAM1 | 0 | 0 | 0 | 0 | IRQ | 0 | 1 |

| RI | ESET | 0    | 0 | • |   |   | _   | _ | - |

|    | U    | U    | U | U | U | 0 | 1   | 0 |   |

RAM0 - Random Access Memory Control Bit 0

- 1 = Maps 32 bytes of RAM into page zero starting at address \$0020. This replaces 48 bytes of ROM that were used at these locations. This bit can be read or written at any time, allowing memory configuration to be changed during program execution.

- 0 = Provides 48 bytes of ROM at location \$0020.

RAM1 - Random Access Memory Control Bit 1

- 1 = Maps 128 bytes of RAM into page zero starting at address \$0100. This replaces 128 bytes of ROM that were used at these locations. This bit can be read or written at any time, allowing memory configuration to be changed during program execution.

- 0 = Provides 128 bytes of ROM at location \$0100.

- IRQ—Interrupt Request Bit Sensitivity

- $1 = \overline{IRQ}$  pin is both negative edge- and level-sensitive.

- 0 = IRQ pin is negative edge-sensitive only.

IRO is set only by reset, but can be cleared by software.

This can only be written once.

Bit 0, 2, 3, 4, 5

Always read zero.

#### (MC68HC805C4 ONLY) IRQ Option Register (IRQOR) \$1FDF

|    | 7        | 6 | 5 | 4 | 3 | 2 | 1   | 0 |  |

|----|----------|---|---|---|---|---|-----|---|--|

|    | 0        | 0 | 0 | 0 | 0 | 0 | IRQ | 0 |  |

| RE | SET<br>0 | 0 | 0 | 0 | 0 | n | 1   | 0 |  |

Bits 7-2, 0 — Not used

Always read zero.

IRQ — Interrupt Request Bit Sensitivity

$1 = \overline{IRQ}$  pin is both negative edge- and level-sensitive.

$0 = \overline{IRQ}$  pin is negative edge-sensitive only.

IRQ is set only by reset, but can be cleared by software.

#### **OCHR**

#### **Output Compare High Register (OCHR) \$16**

#### **OCLR**

#### **Output Compare Low Register (OCLR) \$17**

|    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----|------|------|------|------|------|------|------|------|

|    | OCL7 | OCL6 | OCL5 | OCL4 | OCL3 | OCL2 | OCL1 | OCL0 |

| RI | ESET |      |      |      |      |      |      |      |

|    | U    | U    | U    | U    | U    | U    | U    | H    |

#### **PORTA**

#### Port A Data Register (PORTA) \$00

|    | 7         | 6   | 5   | 4 4 | 3   | 2   | , <b>1</b> / | 0   |

|----|-----------|-----|-----|-----|-----|-----|--------------|-----|

|    | PA7       | PA6 | PA5 | PA4 | PA3 | PA2 | PA1          | PA0 |

| RE | ESET<br>U | U   | U   | U   | U   | U   | U            | U   |

#### **PORTB**

#### Port B Data Register (PORTB) \$01

|    | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----|-----------|-----|-----|-----|-----|-----|-----|-----|

|    | PB7       | PB6 | PB5 | PB4 | PB3 | PB2 | PB1 | PB0 |

| RI | ESET<br>U | U   | U   | U   | U   | U   | U   | U   |

#### **PORTC**

#### Port C Data Register (PORTC) \$02

|    | 7        | 6   | 5   | 4   | 3   | 2   | 1   | 0 : |

|----|----------|-----|-----|-----|-----|-----|-----|-----|

|    | PC7      | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

| RE | SET<br>U | U   | U   | U   | U   | U   | U   | U   |

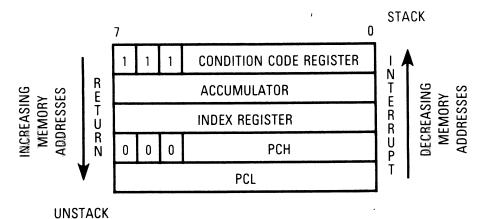

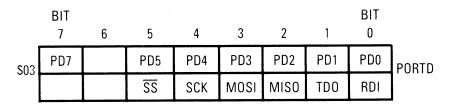

#### **PORTD**

#### Port D Data Register (PORTD) \$03

|    | 7          | 6 | 5                   | 4           | 3            | 2            | 1           | 0           |

|----|------------|---|---------------------|-------------|--------------|--------------|-------------|-------------|

|    | PD7        |   | PD5                 | PD4         | PD3          | PD2          | PD1         | PD0         |

| RE | SET<br>PD7 | 0 | P <u>D5</u> /<br>SS | PD4/<br>SCK | PD3/<br>MOSI | PD2/<br>MISO | PD1/<br>TD0 | PD0/<br>RDI |

|    |            |   | (Port D             | fixed       | input r      | egister      | )           |             |

| RE | SET<br>U   | U | U                   | U           | U            | U            | U           | U           |

#### (MC68HC705C8 ONLY)

#### Program Register (PR) \$1C

The program register (\$1C) is used to perform PROM programming.

| _  | 7        | 6 | 5 | 4 | 3 | 2   | 1 | 0   |

|----|----------|---|---|---|---|-----|---|-----|

| ĺ  | 0        | 0 | 0 | 0 | 0 | LAT | 0 | PGM |

| RE | SET<br>0 | 0 | 0 | 0 | 0 | 0   | 0 | 0   |

LAT — Latch Enable

- 1 = Enables PROM data and address bus latches for programming or erasing on the next byte write cycle.

- 0 = Latch disabled. PROM data and address buses are unlatched for normal CPU operations.

This bit is both readable and writable.

PGM — Program

- 1 = Applies V<sub>PP</sub> power to the PROM for programming.

- $0 = V_{PP}$  power off.

If LAT is cleared, PGM cannot be set.

Bits 1, 7-3 — Not Used

Always read zero.

#### (MC68HC805C4 ONLY)

#### Program Register (PR) \$1C

The program register (\$1C) is used for single-byte EEPROM programming.

|    | 7        | 6    | 5 | 4 | 3     | 2    | 1    | 0     |

|----|----------|------|---|---|-------|------|------|-------|

|    | 0        | CPEN | 0 | 0 | ERASE | LATA | LATB | EEPGM |

| RE | SET<br>0 | 0    | 0 | 0 | 0     | 0    | 0    | 0     |

CPEN — Charge Pump Enable

- 1 = Charge pump enabled

- 0 = Charge pump disabled

ERASE — Erase EEPROM Enable

- 1 = Erase enabled

- 0 = Erase disabled

LATA — Latch A Enable

- 1 = Enables array A data and address bus latches for programming or erasing on the next byte write cycle.

- 0 = Latch disabled

LATB — Latch B Enable

- 1 = Enables array B data and address bus latches for programming or erasing on the next byte write cycle.

- 0 = Latch disabled

Note: If LATA and LATB are cleared, EEPGM cannot be set

For More Information On This Product, Go to: www.freescale.com

PR

EEPGM — Electrically Erase/Program

1 = Applies Vpp power to the EEPROM array for programming or erasing operation.

$0 = V_{PP}$  power off

Bits 4, 5, 7 — Not used

Always read zero.

#### SCCR1

#### Serial Communications Control Reg. 1 (SCCR1) \$0E

The SCCR1 register control bits determine word length and select the wake-up method.

|    | 7    | 6   | 5 | 4 : | 3    | 2 | 1 | 0 |

|----|------|-----|---|-----|------|---|---|---|

|    | R8   | T8  |   | М   | WAKE |   |   |   |

| RI | ESET | I i |   | 11  |      | : |   | 1 |

|    | U    | U   | - | U   | U    | _ |   |   |

R8 — Receive Data Bit 8

R8 bit provides storage location for the ninth bit in the receive data byte (if M = 1).

T8 — Transmit Data Bit 8

T8 bit provides storage location for the ninth bit in the transmit data byte (if M = 1).

M — SCI Character Word Length

1 = One start bit, nine data bits, one stop bit

0 = One start bit, eight data bits, one stop bit

WAKE — Wake-Up Select

Wake bit selects the receiver wake-up method.

1 = Address bit (most significant bit)

0 = Idle line condition

Bits 2–0 and 5 — Not used

Can read either one or zero.

The address bit is dependent on both the wake-bit and the m-bit level. Additionally, the receiver does not use the wake-up feature unless the RWU control bit is SCCR2 is set.

| Wake | М | Receiver Wake-Up                                                                                                                  |

|------|---|-----------------------------------------------------------------------------------------------------------------------------------|

| 0    | X | Detection of an idle line allows the next data byte received to cause the receive data register to fill and produce an RDRF flag. |

| 1    | 0 | Detection of a received one in the eighth data bit allows an RDRF flag and associated error flags.                                |

| 1    | 1 | Detection of a received one in the ninth data bit allows an RDRF flag and associated error flags.                                 |

For More Information On This Product, Go to: www.freescale.com

#### Serial Communications Control Reg. 2 (SCCR2) \$0F

The SCCR2 provides control of individual SCI functions such as interrupts, transmit/receive enabling, receiver wakeup, and break code.

TIE — Transmit Interrupt Enable

1 = SCI interrupt enabled

0 = TDRE interrupt disabled

TCIE — Transmit Complete Interrupt Enable

1 = SCI interrupt enabled

0 = TC interrupt disabled

RIE — Receive Interrupt Enable

1 = SCI interrupt enabled

0 = RDRF and OR interrupts disabled

ILIE — Idle Line Interrupt Enable

1 = SCI interrupt enabled

0 = Idle interrupt disabled

TE-Transmit Enable

- 1 = Transmit shift register output is applied to the TDO line. Depending upon the SCCR1 M bit, a preamble of 10 (M = 0) or 11 (M = 1) consecutive ones is transmitted.

- 0=Transmitter disabled after last byte is loaded in the SCDAT and TDRE is set. After last byte is transmitted, TDO line becomes a high-impedance line.

RE — Receive Enable

- 1 = Receiver shift register input is applied to the RDI line.

- 0 = Receiver disabled and RDRF, IDLE, OR, NF, and FE status bits are inhibited.

RWU — Receiver Wake-Up

- 1 = Places receiver in sleep mode and enables wake-up function.

- 0 = Wake-up function disabled after receiving data word with MSB set (if WAKE = 1). Wake-up function also disabled after receiving 10 (M = 0) or 11 (M = 1) consecutive ones (if WAKE = 0).

SBK — Send Break

- 1 = Transmitter continually sends blocks of zeros (sets of 10 or 11) until cleared. Upon completion of break code, transmitter sends one high bit for recognition of valid start bit.

- 0=Transmitter sends 10 (M=0) or 11 (M=1) zeros then reverts to an idle state or continues sending data. If transmitter is empty and idle, setting and clearing the SBK bit may queue up to two character times of break because the first break transfer immediately to the shift register, and the second is queued into the parallel transmit buffer.

#### **SCDAT**

#### Serial Communications Data Register (SCDAT) \$11

The SCDAT is a read/write register used to receive and transmit SCI data.

|    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----|------|------|------|------|------|------|------|------|

|    | SCD7 | SCD6 | SCD5 | SCD4 | SCD3 | SCD2 | SCD1 | SCD0 |

| RE | SET  |      |      |      |      |      |      |      |

|    | U    | U    | U    | U    | U    | U    | U    | U    |

#### **SCSR**

#### Serial Communications Status Register (SCSR) \$10

The SCSR provides inputs to the SCI interrupt logic circuits. Noise flag and framing error bits are also contained in the SCSR.

|    | 7    | 6   | 5    | 4    | 3  | 2  | 1  | 0 |

|----|------|-----|------|------|----|----|----|---|

|    | TDRE | TC6 | RDRF | IDLE | OR | NF | FE |   |

| RI | ESET |     |      |      |    |    |    |   |

|    | 1    | 1   | 0    | 0    | 0  | 0  | 0  |   |

TDRE — Transmit Data Register (TDR) Empty

- 0 = TDR contents transferred to the transmit data shift register.

- 0 = TDR still contains data. TDRE is cleared by reading the SCSR followed by a write to the TDR.

SCSR For More Information On This Product,

Go to: www.freescale.com

- TC Transmit Complete

- 1 = Indicates end of data frame, preamble, or break condition has occurred.

- 0 = TC bit cleared by reading the SCSR, followed by a write to the TDR.

#### RDRF-Receive Data Register (RDR) Full

- 1 = Receive data shift register contents transferred to the RDR.

- 0 = Receive data shift register transfer did not occur. RDRF is cleared by reading the SCSR, followed by a read of the RDR.

- IDLE Idle Line Detect

- 1 = Indicates receiver has detected an idle line.

- 0=IDLE is cleared by reading the SCSR, followed by a read of the RDR. Once IDLE is cleared, IDLE cannot be set until RDI line becomes active and idle again.

- OR Overrun Error

- 1 = Indicates receive data shift register data is sent to a full RDR (RDRF = 1). Data causing the overrun is lost, and RDR data is not disturbed.

- 0 = OR is cleared by reading the SCSR, followed by a read of the RDR.

- NF Noise Flag

- 1 = Indicates noise is present on the receive bits, including the start and stop bits. NF is not set until RDRF = 1.

- 0 = NF is cleared by reading the SCSR, followed by a read of the RDR.

- FE Framing Error

- 1 = Indicates stop bit not detected in received data character. FE is set the same time RDRF is set. If received byte causes both framing and overrun errors, processor will only recognize the overrun error. Further data transfer into the RDR is inhibited until FE is cleared.

- 0 = FE is cleared by reading the SCSR, followed by a read of the RDR.

- Bit 0 Not used

Can read either one or zero.

#### Serial Peripheral Control Register (SPCR) \$0A

The SPCR provides control of individual SPI functions such as interrupt and system enabling disabling, master slave mode select, and clock polarity phase rate select.

|   | 7    | 6   | 5     | 4    | 3    | 2    | 1    | 0    |   |

|---|------|-----|-------|------|------|------|------|------|---|

|   | SPIE | SPE | DW0M* | MSTR | CPOL | СРНА | SPR1 | SPR0 |   |

| R | FSET |     |       |      |      |      |      |      | • |

RESET

$0 \quad 0 \quad - \quad 0 \quad U \quad U \quad U$

SPIE — Serial Peripheral Interrupt Enable

1 = SPI interrupt enabled

0 = SPI interrupt disabled

SPE — Serial Peripheral System Enable

1 = SPI system on

0 = SPI system off

MSTR — Master Mode Select

1 = Master mode

0 = Slave mode

CPOL — Clock Polarity

Clock polarity bit controls the clock value and is used in conjunction with the clock phase (CPHA) bit.

1 = SCK line idles high

0 = SCK line idles in low state

CPHA — Clock Phase

Clock phase bit along with CPOL controls the clock-data relationship between the master and slave devices. CPOL selects one or two clocking protocols.

$1 = \overline{SS}$  is an output enable control.

0 = Shift clock is the OR or SCK with SS.

When SS is low, first edge of SCK invokes first data sample.

SPR1-SPR0 — SPI Clock Rate Bits

Two clock rate bits are used to select one of four clock rates to be used as SCK in the master mode. In the slave mode, the two clock rate bits have no effect. Clock rate selection is shown in the following table.

| SPR1 | SPR0 | Internal Processor Clock<br>Divided By |

|------|------|----------------------------------------|

| 0    | 0    | 2                                      |

| 0    | 1    | 4                                      |

| 1    | 0    | 16                                     |

| 1    | 1    | 32                                     |

Bit 5 — Not used\*

Can read either one or zero.

(\*MC68HC05C9 only, bit 5 (DWOM) is the wire-OR mode bit.)

- 1 = Disables active pullup devices on Port D, causing outputs to be open drain.

- 0 = Open-drain disabled.

**SPCR**

For More Information On This Product, Go to: www.freescale.com

# Serial Peripheral Data I/O Register (SPDR) \$0C

The SPDR is read/write register used to receive and transmit SPI data.

A write to the SPDR places data directly into the shift register for transmission. Only a write to this register will initiate transmission/reception of another byte and will only occur in the master device. On completion of byte transmission, the SPIF status bit is set in both master and slave devices.

A read to the SPDR causes the buffer to be read. The first SPIF status bit must be cleared by the time a second data transfer from the shift register to the read buffer begins, or an overrun condition will exist. In overrun cases, the byte causing the overrun is lost.

# **SPSR**

# Serial Peripheral Status Register (SPSR) \$0B

The SPSR contains three status bits.

| _  | 7        | 6    | 5 | 4    | 3 | 2 | 1 | 0 |

|----|----------|------|---|------|---|---|---|---|

|    | SPIF     | WCOL | _ | MODF | _ |   | _ |   |

| RE | SET<br>n | Λ    |   | 0    |   |   |   |   |

SPIF — Serial Peripheral Data Transfer Flag

1 = Indicates data transfer completed between processor and external device.

(If SPIF = 1 and SPIE = 1, SPI interrupt is enabled.)

0 = Clearing is accomplished by reading SPSR, followed by SPDR access.

WCOL — Write Collision

- 1 = Indicates an attempt is made to write to SPDR while data transfer is in processor.

- 0 = Clearing is accomplished by reading SPSR, followed by SPDR access.

MODF — Mode Fault Flag

- 1 = Indicates multi-master system control conflict.

- 0 = Clearing is accomplished by reading SPSR, followed by a write to the SPCR.

Bits 3-0 and 5 — Not used

Can read either zero or one.

# **Timer Control Register (TCR) \$12**

The TCR is a read/write register containing five control bits. Three bits control interrupts associated with the timer status register flags ICF, OCF, and TOF.

|    | 7         | 6    | 5    | 4 | 3 | 2 | 1    | 0    | _ |

|----|-----------|------|------|---|---|---|------|------|---|

|    | ICIE      | OCIE | TOIE | 0 | 0 | 0 | IEDG | OLVL | 1 |

| RE | ESET<br>0 | 0    | 0    |   | 0 | 0 | IJ   | 0    |   |

ICIE — Input Capture Interrupt Enable

1 = Interrupt enabled

0 = Interrupt disabled

OCIE — Output Compare Interrupt Enable

1 = Interrupt enabled

0 = Interrupt disabled

TOIE — Timer Overflow Interrupt Enable

1 = Interrupt enabled

0 = Interrupt disabled

IEDG — Input Edge

Value of input edge determines which level transition on TCAP pin will trigger free-running counter transfer to the input capture register.

1 = Positive edge

0 = Negative edge

OLVL — Output Level

Value of output level is clocked into output level register by the next successful output compare and will appear on the TCMP pin.

1 = High output

0 = Low output

Bits 2, 3, and 4 — Not used

Always read zero.

# Timer Status Register (TSR) \$13

The TSR is a read-only register containing three status flag bits.

| _  | 7   | 6   | 5   | 4 | 3 | 2 | 1 | 0 |   |

|----|-----|-----|-----|---|---|---|---|---|---|

|    | ICF | OCF | TOF | 0 | 0 | 0 | 0 | 0 |   |

| RE | SET | 11  | 11  | Λ | Ω | 0 | n | n | - |

ICF — Input Capture Flag

- 1 = Flag set when selected polarity edge is sensed by input capture edge detector.

- 0 = Flag cleared when TSR and input capture low register (\$15) are accessed.

- OCF Output Compare Flag

- 1 = Flag set when output compare register contents match the free-running counter contents.

- 0 = Flag cleared when TSR and output compare low register (\$17) are accessed.

- TOF Timer Overflow Flag

- 1 = Flag set when free-running counter transition from \$FFFF to \$0000 occurs.

- 0 = Flag cleared when TSR and counter low register (\$19) are accessed.

Bits 4–0 — Not used Always read zero.

# Freescale Semiconductor, Inc. ADDRESSING MODES

# **IMMEDIATE (IMM)**

The effective address (EA) of an immediate mode instruction is the location following the opcode. This mode is used to fetch a value which is known at the time the program is written, and which is not changed during program execution.

#### DIRECT (DIR)

The EA of a direct mode instruction is the contents of the byte following the opcode. This mode is used to fetch a value from any one of the first 256 memory locations with a two-byte instruction.

## **EXTENDED (EXT)**

The EA of an extended mode instruction is the contents of the next two bytes following the opcode. This mode is used to fetch a value from any location in the MC146805G2 memory location, I/O, RAM, and ROM, with a three-byte instruction.

#### INDEXED (IX, IX1, IX2)

The EA of an indexed mode instruction is determined by the contents of the X-register being added to an offset. The offset can be either zero, 8-bit, or 16-bit. For zero offset (IX), the X-register is the EA. For 8-bit offset (IX1), the result of the X-register contents added to the byte following the opcode is the EA. For 16-bit offset (IX2), the result of the X-register contents added to the concatenated contents of the two bytes following the opcode is the EA.

#### **RELATIVE (REL)**

The EA of a relative mode instruction depends upon whether or not the branch is taken. If a branch is taken, EA is formed by adding the byte following the opcode to the value of the program counter, and the program counter is loaded with the EA. If no branch is required, EA is equal to the contents of the program counter.

#### BIT SET/CLEAR (BSC)

The EA of a Bit Set/Clear mode instruction is contained in the byte following the opcode. The actual bit which is to be set or cleared is contained in the lower four bits (nibble) of the opcode.

#### BIT TEST AND BRANCH (BTB)

This addressing mode combines direct, relative and bit addressing. The EA of this instruction is the contents of the byte following the opcode (direct mode), if no branch is taken. If a branch is taken, the EA becomes the result of the second byte following the opcode being added to the value of the program counter (similar to relative mode). The actual bit which is to be tested is contained in the lower four bits (nibble) of the opcode.

#### INHERENT (INH)

This addressing mode has no EA since all information necessary to carry out the instruction is contained in the opcode.

For More Information On This Product, Go to: www.freescale.com

# MERACOS INSTRUCTION SET.

The following table is an alphabetical listing of the instructions available to the M68HC05 MCU user. In listing all the factors necessary to program, the table uses the following symbols:

# **Condition Code Symblols**

| Н | <ul><li>Half Carry (Bit 4)</li></ul>       | <b>±</b> | <ul> <li>Test and Set if True,</li> </ul>   |

|---|--------------------------------------------|----------|---------------------------------------------|

| l | <ul> <li>Interrupt Mask (Bit 3)</li> </ul> | •        | (Cleared otherwise)                         |

| Ν | <ul><li>Negate (Sign Bit 2)</li></ul>      |          | <ul> <li>Not Affected</li> </ul>            |

| Z | — Zero (Bit 1)                             | ?        | <ul> <li>Load CC Reg. from Stack</li> </ul> |

| С | — Carry/Borrow (Bit 0)                     | 0        | — Cleared                                   |

|   |                                            | 1        | — Set                                       |

# **Boolean Operators**

| ( ) | — Contents of (i.e.) (M) = | +        | — (inclusive) OR                 |

|-----|----------------------------|----------|----------------------------------|

|     | means the contents         | $\oplus$ | — EXCLUSIVE OR                   |

|     | of memory location         |          | — NOT                            |

|     | M                          | _        | <ul><li>negation</li></ul>       |

| •   | — is loaded with, 'gets'   |          | (twos complement)                |

| •   | — AND                      | ×        | <ul><li>multiplication</li></ul> |

# **MPU Registers**

| Α    | <ul><li>Accumulator</li></ul>           | PC  | <ul> <li>Program Counter</li> </ul>  |

|------|-----------------------------------------|-----|--------------------------------------|

| ACCA | <ul><li>Accumulator</li></ul>           | PCH | <ul><li>PC High Byte</li></ul>       |

| CC   | <ul> <li>Condition Code Reg.</li> </ul> | PCL | — PC Low Byte                        |

| Χ    | <ul><li>Index Register</li></ul>        | SP  | <ul><li>Stack Pointer</li></ul>      |

| M    | <ul> <li>Any memory location</li> </ul> | REL | <ul> <li>Relative Address</li> </ul> |

|      | (one byte)                              |     |                                      |

| <b>Addressing Modes</b> | (Abbreviation) | Opera | nds |

|-------------------------|----------------|-------|-----|

| Inherent                | INH            | none  |     |

| Immediate               | IMM            | ii    |     |

| Direct (for bit         | DIR            | dd    |     |

| test instructions)      |                | dd    | rr  |

| Extended                | EXT            | hh    | H   |

| Indexed 0 Offset        | IX             | none  |     |

| Indexed 1-Byte          | IX1            | ff    |     |

| Indexed 2-Byte          | IX2            | ee    | ff  |

| Relative                | REL            | rr    |     |

# INSTRUCTIONS, ADDRESSING MODES, AND EXECUTION TIMES

|                              |            | reescale Se                           | miconducto                                         | or, inc.                               |

|------------------------------|------------|---------------------------------------|----------------------------------------------------|----------------------------------------|

| 6                            | ပ          | <b>+</b>                              | 40                                                 |                                        |

| Cod                          | 7          | 44                                    | 44                                                 | **                                     |

| tion                         | Z          | 40                                    | <b>4</b> •                                         | <b>4+</b>                              |

| Condition Code               | _          |                                       |                                                    |                                        |

|                              | I          | 40                                    | <b>++</b>                                          |                                        |

| Bytes Cycles                 |            | 2 4 4 3 4 8 4 8 4 8                   | 2 8 4 5 4 8                                        | 7 6 4 6 4 6                            |

| Bytes                        |            | 2<br>2<br>3<br>3<br>1                 | 2 3 3 2 7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1      | 123327                                 |

| ing<br>at)                   | and        | #                                     | <b>=</b> #                                         | = #                                    |

| e Cod<br>Jecima              | Operand    | ii<br>dd<br>hh<br>ee<br>ff            | ii<br>dd<br>hh<br>ee                               | ii<br>dd<br>hh<br>ee                   |

| Machine Coding (hexadecimal) | Opcode     | A9<br>B9<br>C9<br>D9<br>E9            | AB<br>BB<br>CB<br>DB<br>EB                         | A4<br>B4<br>C4<br>D4<br>E4             |

| Addressing<br>Mode for       | Operand    | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX | IMM<br>DIR<br>EXT<br>IX2<br>IX1                    | IMIM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX |

| Boolean                      | Expression | ACCA ♦ ACCA + M + C                   | ACCA ♠ ACCA + M                                    | ACCA ♦ ACCA • M                        |

| Operation                    |            | Add with Carry                        | Add                                                | Logical AND                            |

| Source                       | LOUIII(S)  | (obt) Fér More Inform Go to: w        | (ldo)<br>OO<br>ation On This Pi<br>ww.freescale.co | (Job) ON<br>Coduct,                    |

| Free                              | scale Sen                                                                      | niq                   | onductor, Inc.                                                  | 1                   |                 |

|-----------------------------------|--------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------|---------------------|-----------------|

| ♦♦                                | <b>4+</b>                                                                      | -                     |                                                                 |                     |                 |

| 44                                | <b>♦</b>                                                                       | -1                    |                                                                 | - 1                 | 1               |

| <b>4+</b>                         | <b>4+</b>                                                                      | 1                     |                                                                 |                     |                 |

|                                   |                                                                                |                       |                                                                 | ١                   |                 |

| 1                                 |                                                                                | -                     | 1                                                               | -                   | -               |

| വയനാവ                             | വയനാവ                                                                          | က                     | 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                         | 3                   | 3               |

| 22-                               | 2-1-2-                                                                         | 2                     | 0000000                                                         | 2                   | 2               |

| dd<br>ff                          | dd<br>ff                                                                       | rr                    | p p p p p p p p                                                 | rr                  | rr              |

| 38<br>48<br>58<br>68<br>78        | 37<br>47<br>57<br>67                                                           | 24                    | 11<br>13<br>15<br>19<br>10<br>11                                | 25                  | 27              |

| DIR<br>INH(A)<br>IX1<br>IX        | DIR<br>INH(A)<br>INH(X)<br>IX1                                                 | REL                   | DIR(b0) DIR(b1) DIR(b2) DIR(b3) DIR(b4) DIR(b5) DIR(b6) DIR(b6) | REL                 | REL             |

| C b7 b0                           | D 09 C9                                                                        | ) C == 0              | Mn <b>♦</b> 0                                                   | ? C=1               | ? Z=1           |

| Arithmetic Shift Left             | Arithmetic Shift Right                                                         | Branch if Carry Clear | Clear Bit n in Memory                                           | Branch if Carry Set | Branch if Equal |

| ASL (opr) ASLA ASLX ASLX SL (opr) | Apply SR (opr)  Apply SRA  Boto  Apply SRA  Company SR (opr)  Company SR (opr) | Signal (rel)          | CTR u' (obr) This Product, eescale.com                          | BCS (rel)           | BEQ (rel)       |

|                              |             |                            | re                       | es               | ca                       | le_                       | Se                       | mic                    | on          | dı                                      | JC           | to | r,                | Inc                     |                          |

|------------------------------|-------------|----------------------------|--------------------------|------------------|--------------------------|---------------------------|--------------------------|------------------------|-------------|-----------------------------------------|--------------|----|-------------------|-------------------------|--------------------------|

| ge                           | ပ           | <u> </u>                   | <u> </u>                 | <u> </u>         | -                        | <u> </u>                  | 1                        |                        | ·           |                                         |              |    |                   |                         |                          |

| ပိ                           | <b>Z</b>    |                            |                          | -                | -                        | -                         | <br>                     | **                     |             |                                         | <del>.</del> |    |                   |                         | <u> </u>                 |

| Condition Code               | Z           |                            | <u> </u>                 |                  |                          |                           |                          | **                     |             |                                         |              | ,  |                   |                         | -                        |

| Con                          | _           |                            | -                        |                  |                          | 1                         |                          | <u> </u>               | ····        |                                         |              |    |                   | -                       | 1                        |

| Si                           | I           | -                          | 1                        | 1                | 1                        |                           |                          |                        | <del></del> |                                         |              |    | l                 | - 1                     |                          |

| Bytes Cycles                 |             | 3                          | 3                        | 3                | 3                        | 3                         | 3                        | 2                      | . 4         | 2                                       | 4            | က  | 3                 | 3                       | က                        |

| Bytes                        |             | 7                          | 2                        | 7                | 2                        | 7                         | 2                        | 2                      | ۸ W         | က                                       | 2            | _  | 2                 | 2                       | 2                        |

| Machine Coding (hexadecimal) | Operand     | rr                         | rr                       | ונ               | rr                       | rr                        | rr                       | ::                     | =<br>Ph     | ee ff                                   | ff           |    | rr                | rr                      | ٦                        |

| Machin<br>(hexad             | Opcode      | 28                         | 29                       | 22               | 24                       | 2F                        | 2E                       | A5<br>B5               | 3 2         | 02                                      | E5           | F5 | 25                | 23                      | 2C                       |

| Addressing<br>Mode for       | Operand     | REL                        | REL                      | REL              | REL                      | REL                       | REL                      | MMI                    | EXT         | IX2                                     | ×            | ×  | REL               | REL                     | REL                      |

| Boolean                      | LAPIESSIOII | 0=H ≥                      | ? H=1                    | (C + Z) = 0      | ) C=0                    | ? <u>IRO</u> Pin=1        | ? <u>IRO</u> Pin=0       | ACCA ● M               |             | *************************************** |              |    | ? C=1             | ? (C + X) = 1           | 7 1=0                    |

| Operation                    |             | Branch if Half Carry Clear | Branch if Half Carry Set | Branch if Higher | Branch if Higher or Same | Branch if IRO Pin is High | Branch if IRO Pin is Low | Bit Test Memory with A |             |                                         |              |    | Branch if Lower   | Branch if Lower or Same | Branch if I Bit is Clear |

| Source<br>Form(s)            | (6)11101    | BHCC (rel)                 | <b>罗</b> HCS (rel)       | ₽HI (rel)        | <b>9.</b> BHS (rel)      | <b>引起</b> H (rel)         | <b>事</b> L (rel)         | atton                  | On          | Th                                      | nis          | Pr | <b>P</b> LO (rel) | SLS (rel)               | BMC (rel)                |

|                 | Freescale Semicon      |                     |                |               |                          |         |         |         |         |         |                      | dų      | ct           | OI                     | ۴,       | ln      | C.      |         |            |         |         |

|-----------------|------------------------|---------------------|----------------|---------------|--------------------------|---------|---------|---------|---------|---------|----------------------|---------|--------------|------------------------|----------|---------|---------|---------|------------|---------|---------|

|                 | 1                      | 1                   |                |               | 40                       |         |         |         |         |         |                      |         |              | **                     |          |         |         |         |            |         |         |

|                 |                        | 1                   |                |               | 1                        |         |         |         |         |         |                      |         | 1            | 1                      |          |         |         |         |            |         |         |

|                 |                        | 1                   | 1              | ١             | I                        |         |         |         |         |         |                      |         | 1            | i                      |          |         |         |         |            |         |         |

| 1               |                        | 1                   |                | 1             |                          |         |         |         |         |         |                      |         |              | 1                      | *        |         |         |         |            |         |         |

|                 |                        |                     | 1              | 1             | ١                        |         |         |         |         |         |                      |         |              | 1                      |          |         |         |         |            |         |         |

| 3               | 3                      | 3                   | 3              | 3             | 5                        | 2       | വ       | D       | വ       | വ       | വ                    | വ       | က            | 2                      | 2        | ည       | വ       | വ       | 2          | വ       | 2       |

| 2               | 2                      | 2                   | 2              | 2             | က                        | က       | က       | က       | က       | 3       | က                    | 3       | 2            | က                      | က        | က       | က       | က       | က          | က       | က       |

|                 |                        |                     |                |               | ٤                        | ٢       | ٢       | ٤       | ı       | ı       | ٢                    | rr      |              | ۲                      | ٤        | ٦       | ٤       | ٢       | ٤          | ۲       | ٢       |

| rr              | ב                      | ٤                   | ٦              | ٦             | pp                       | рp      | pp      | pp      | рp      | рр      | pp                   | pp      | ۲            | рp                     | pp       | рр      | pp      | рp      | P          | рp      | рp      |

| 2B              | 2D                     | 56                  | 2A             | 20            | 01                       | 03      | 02      | 07      | 60      | 0B      | <u>0</u>             | 0F      | 21           | 00                     | 05       | 04      | 90      | 80      | 0 <b>A</b> | ၁       | 0E      |

| REL             | REL                    | REL                 | REL            | REL           | DIR(b0)                  | DIR(b1) | DIR(b2) | DIR(b3) | DIR(b4) | DIR(b5) | DIR(b6)              | DIR(b7) | REL          | DIR(b0)                | DIR(b1)  | DIR(b2) | DIR(b3) | DIR(b4) | DIR(b5)    | DIR(b6) | DIR(b7) |

| ? N = 1         | 7  = 1                 | 3 Z = 0             | 0=N ¿          | 7 1=1         | ? Bit n of M = 0         |         |         |         |         |         |                      |         | ? 1=0        | ? Bit n of M = 1       |          |         |         |         |            |         |         |

| Branch if Minus | Branch if I Bit is Set | Branch if Not Equal | Branch if Plus | Branch Always | Branch if Bit n of M = 0 |         |         |         |         |         |                      |         | Branch Never | Branch if Bit n of M=1 |          |         |         |         |            |         |         |

| BMI (rel)       | BMS (rel)              | BNE (rel)           | BPL (rel)      | &RA (rel)     | RCLR n, (opr)            | (re)    | In      | for     | ma<br>w | atio    | on<br><del>,fr</del> | On      | EN (rel)     | BRSET n, (opr)         | ro (Lel) | du      | ct,     |         |            |         |         |

|                              |            |                     | re      | <b>e</b> | SC             | a            | le      | S       | er      | nie                  | <b>CO</b>                              | n                          | dų            | ct               | or,              | _In           | C.     |               |           |               |

|------------------------------|------------|---------------------|---------|----------|----------------|--------------|---------|---------|---------|----------------------|----------------------------------------|----------------------------|---------------|------------------|------------------|---------------|--------|---------------|-----------|---------------|

| le                           | ၁          | -                   |         |          |                |              |         |         |         |                      |                                        |                            |               | 0                | - 1              |               |        |               |           |               |

| Coc                          | 2          |                     |         |          | <del>, ,</del> | <del>,</del> |         |         |         |                      |                                        |                            |               | -                | 1                | -             |        |               |           |               |

| ition                        | Z          | 1                   |         |          |                |              |         |         |         |                      |                                        |                            |               | -1               | 1                | 0             |        |               |           |               |

| Condition Code               | _          | ١                   |         |          |                |              |         |         |         |                      |                                        |                            |               | 1                | 0                | 1             |        | :             |           |               |

|                              | I          |                     |         |          |                |              |         |         |         |                      |                                        |                            |               | 1                | 1                |               |        |               |           |               |

| Bytes Cycles                 |            | 9                   | 2       | 2        | വ              | 2            | 2       | 2       | 2       | 9                    |                                        |                            |               | 2                | 2                | 2             | က      | က             | ဖ         | വ             |

| Bytes                        |            | 2                   | 2       | 2        | 2              | 2            | 2       | 2       | 2       | 2                    |                                        |                            |               | 1                | 1                | 2             | -      | <b>,</b>      | 7         | _             |

| Machine Coding (hexadecimal) | Operand    | pp                  | pp      | pp       | pp             | pp           | pp      | pp      | pp      | ιι                   |                                        |                            |               |                  |                  | pp            |        |               | <b>#</b>  |               |

| Machin<br>(hexac             | Opcode     | 10                  | 12      | 14       | 16             | 18           | 1       | 7       | 1E      | AD                   |                                        |                            |               | 86               | 9A               | 3F            | 4F     | 5F            | 9F        | 7F            |

| Addressing<br>Mode for       | Operand    | DIR(b0)             | DIR(b1) | DIR(b2)  | DIR(b3)        | DIR(b4)      | DIR(b5) | DIR(b6) | DIR(b7) | REL                  |                                        |                            |               | INH              | HNI              | DIR           | NH(A)  | NH(X)         | ×         | ×             |

| Boolean                      | Expression | Mn <b>4</b> 1       |         |          |                |              |         |         |         | PC <b>♦</b> PC+0002  | (SP) <b>♦</b> PCL; SP <b>♦</b> SP−0001 | (SP) ♦ PCH; SP ♦ SP – 0001 | PC ← PC + Rel | C bit <b>♦</b> 0 | l bit <b>♦</b> 0 | M <b>♦</b> 00 | A ♠ 00 | 00 <b>→</b> × | M ◆ 00    | 00 <b>♥</b> W |

| Operation                    |            | Set Bit n in Memory |         |          |                |              |         |         |         | Branch to Subroutine |                                        |                            |               | Clear C Bit      | Clear I Bit      | Clear         |        |               |           |               |

| Source                       | rorm(s)    | BSET n, (opr)       | F       | or l     | Мо             | re<br>G      | Ini     | ior     | ma      | est (ref)            | n O                                    | )n ˈ                       | Thi           | s s              | igo.             | PLR (opr)     | CLRA   | CLRX          | CLR (opr) | CLR (opr)     |