MC68HC705C4A MC68HSC705C4A

Technical Data

# M68HC05 Microcontrollers

MC68HC705C4A/D Rev. 3, 5/2002

WWW.MOTOROLA.COM/SEMICONDUCTORS

# MC68HC705C4A MC68HSC705C4A

### **Technical Data**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.motorola.com/semiconductors/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

Motorola and the Stylized M Logo are registered trademarks of Motorola, Inc. digital dna is a trademark of Motorola, Inc.

© Motorola, Inc., 2002

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

**Technical Data**

MOTOROLA 3

# **Technical Data**

# **Revision History**

| Date      | Revision<br>Level | Description                      | Page<br>Number(s) |

|-----------|-------------------|----------------------------------|-------------------|

| May, 2002 | 3.0               | Corrected World Wide Web address | N/A               |

**Technical Data**

# **List of Sections**

| Section 1. General Description2                      |

|------------------------------------------------------|

| Section 2. Memory35                                  |

| Section 3. Central Processor Unit (CPU)43            |

| Section 4. Interrupts                                |

| Section 5. Resets63                                  |

| Section 6. Low-Power Modes67                         |

| Section 7. Parallel Input/Output (I/O)73             |

| Section 8. Capture/Compare Timer                     |

| Section 9. EPROM/OTPROM (PROM)99                     |

| Section 10. Serial Communications Interface (SCI)115 |

| Section 11. Serial Peripheral Interface (SPI)133     |

| Section 12. Instruction Set147                       |

| Section 13. Electrical Specifications165             |

| Section 14. Mechanical Specifications                |

| Section 15. Ordering Information189                  |

| Appendix A. MC68HSC705C4A193                         |

| Index                                                |

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

# List of Sections

# **Table of Contents**

### **Section 1. General Description**

| 1.1    | Contents                             |

|--------|--------------------------------------|

| 1.2    | Introduction21                       |

| 1.3    | Features                             |

| 1.4    | Programmable Options23               |

| 1.5    | Block Diagram24                      |

| 1.6    | Pin Assignments                      |

| 1.7    | Pin Functions                        |

| 1.7.1  | $V_{DD}$ and $V_{SS}$                |

| 1.7.2  | OSC1 and OSC2                        |

| 1.7.3  | External Reset Pin (RESET)           |

| 1.7.4  | External Interrupt Request Pin (IRQ) |

| 1.7.5  | Input Capture Pin (TCAP)32           |

| 1.7.6  | Output Compare Pin (TCMP)33          |

| 1.7.7  | Port A I/O Pins (PA7–PA0)33          |

| 1.7.8  | Port B I/O Pins (PB7–PB0)33          |

| 1.7.9  | Port C I/O Pins (PC7–PC0)            |

| 1.7.10 | Port D I/O Pins (PD7 and PD5–PD0)33  |

|        | Section 2. Memory                    |

| 2.1    | Contents                             |

| 2.2    | Introduction35                       |

| 2.3    | Memory Map                           |

| 2.4    | Input/Output (I/O)                   |

| 2.5    | RAM36                                |

|        |                                      |

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

# **Table of Contents**

| 2.6                                                       | EPROM/OTPROM (PROM)                                                                                                                                   | 37                   |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2.7                                                       | Bootloader ROM                                                                                                                                        | 37                   |

|                                                           | Section 3. Central Processor Unit (CPU)                                                                                                               |                      |

| 3.1                                                       | Contents                                                                                                                                              | 43                   |

| 3.2                                                       | Introduction                                                                                                                                          | 43                   |

| 3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5          | CPU Registers  Accumulator  Index Register  Stack Pointer  Program Counter  Condition Code Register                                                   | 45<br>45<br>46       |

| 3.4                                                       | Arithmetic/Logic Unit (ALU)                                                                                                                           | 49                   |

|                                                           | Section 4. Interrupts                                                                                                                                 |                      |

| 4.1                                                       | Contents                                                                                                                                              | 51                   |

| 4.2                                                       | Introduction                                                                                                                                          | 51                   |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6 | Interrupt Sources  Software Interrupt.  External Interrupt (IRQ)  Port B Interrupts  Capture/Compare Timer Interrupts  SCI Interrupts  SPI Interrupts | 52<br>53<br>55<br>56 |

| 4.4                                                       | Interrupt Processing                                                                                                                                  | 60                   |

|                                                           | Section 5. Resets                                                                                                                                     |                      |

| 5.1                                                       | Contents                                                                                                                                              | 63                   |

| 5.2                                                       | Introduction                                                                                                                                          | 63                   |

**Technical Data**

| 5.3                            | Reset Sources                                                  | 63                   |

|--------------------------------|----------------------------------------------------------------|----------------------|

| 5.3.1                          | Power-On Reset (POR)                                           | 64                   |

| 5.3.2                          | External Reset                                                 | 64                   |

| 5.3.3                          | Computer Operating Properly (COP) Watchdog Reset               | 64                   |

|                                | Section 6. Low-Power Modes                                     |                      |

| 6.1                            | Contents                                                       | 67                   |

| 6.2                            | Introduction                                                   | 67                   |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3 | Stop Mode                                                      | 69<br>69             |

| 6.4                            | Wait Mode                                                      | 70                   |

| 6.5                            | Data-Retention Mode                                            | 72                   |

|                                | Section 7. Parallel Input/Output (I/O)                         |                      |

| 7.1                            | Contents                                                       | 73                   |

| 7.2                            | Introduction                                                   | 73                   |

| 7.3<br>7.3.1<br>7.3.2<br>7.3.3 | Port A                                                         | 74<br>75             |

|                                | Port B                                                         | 77                   |

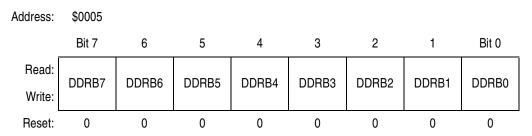

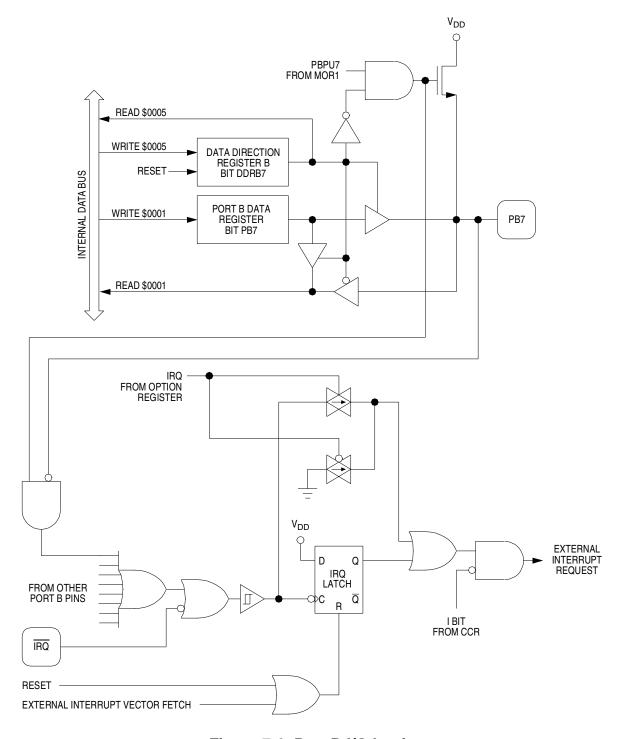

| 7.4.2<br>7.4.3                 | Port B Data Register  Data Direction Register B.  Port B Logic | 78                   |

|                                | Data Direction Register B                                      | 78<br>79<br>81<br>81 |

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

8.1

# **Section 8. Capture/Compare Timer**

| 8                          | .2                                                   | Introduction85                                                                                                                                                      |

|----------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                          | .3<br>.3.1<br>.3.2                                   | Timer Operation                                                                                                                                                     |

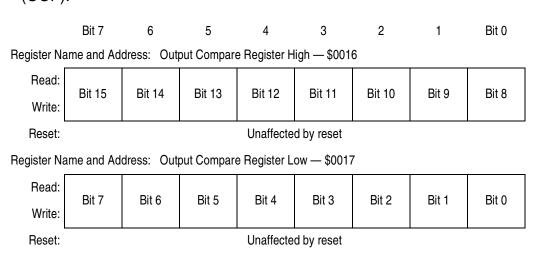

| 8<br>8<br>8<br>8<br>8      | .4.1<br>.4.2<br>.4.3<br>.4.4<br>.4.5<br>.4.6         | Timer I/O Registers90Timer Control Register90Timer Status Register92Timer Registers93Alternate Timer Registers94Input Capture Registers95Output Compare Registers96 |

|                            |                                                      | Section 9. EPROM/OTPROM (PROM)                                                                                                                                      |

| 9                          | .1                                                   | Contents                                                                                                                                                            |

| 9                          | .2                                                   | Introduction                                                                                                                                                        |

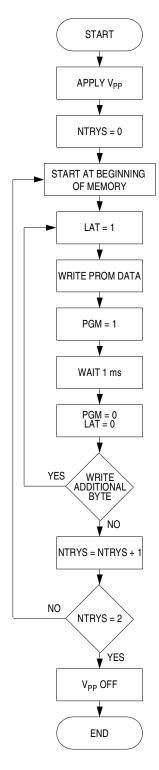

| 9                          | .3<br>.3.1<br>.3.2                                   | EPROM/OTPROM (PROM) Programming                                                                                                                                     |

| 9<br>9<br>9<br>9<br>9<br>9 | .4.1<br>.4.2<br>.4.3<br>.4.4<br>.4.5<br>.4.6<br>.4.7 | PROM Programming Routines                                                                                                                                           |

| 9                          | .5<br>.5.1<br>.5.2<br>.5.3                           | Control Registers112Option Register112Mask Option Register 1113Mask Option Register 2114                                                                            |

| 9                          | .6                                                   | EPROM Erasing                                                                                                                                                       |

| Technical Data             |                                                      | MC68HC705C4A • MC68HSC705C4A — Rev. 3.0                                                                                                                             |

| Section 10. Serial Communications Interface (SCI)                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.1 Contents                                                                                                                                                                                                                                                                                                          |

| 10.2 Introduction                                                                                                                                                                                                                                                                                                      |

| 10.3 Features                                                                                                                                                                                                                                                                                                          |

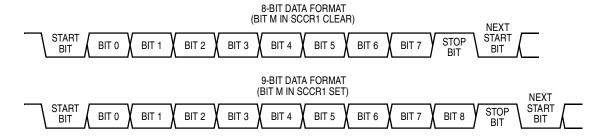

| 10.4 SCI Data Format116                                                                                                                                                                                                                                                                                                |

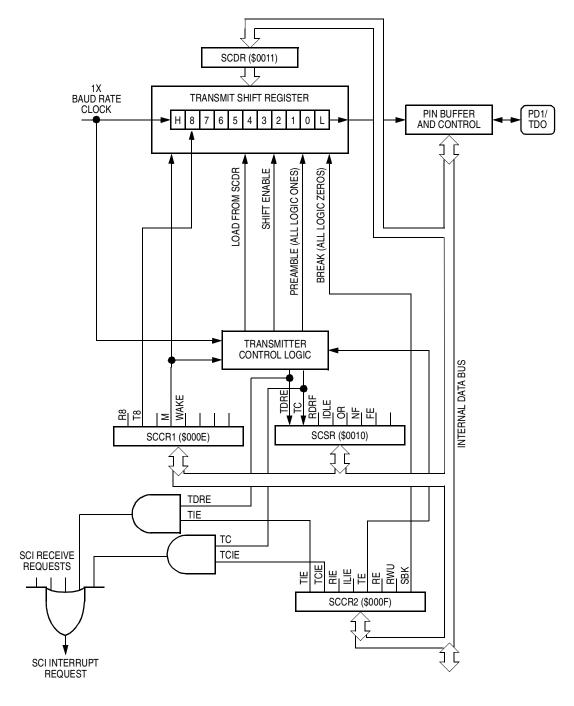

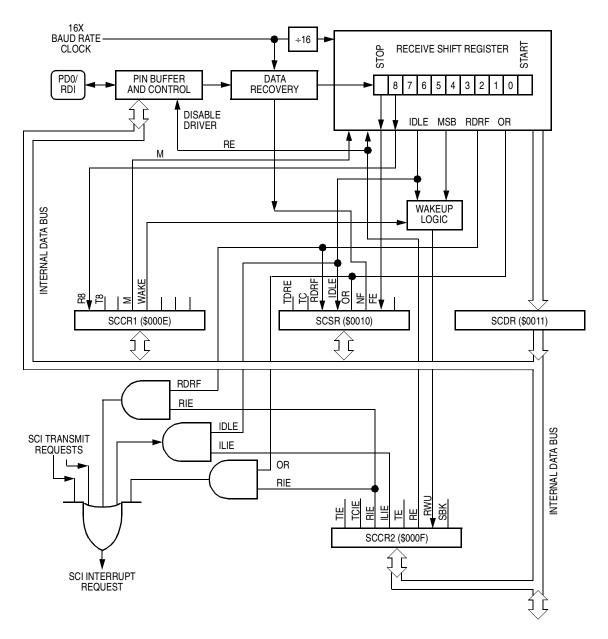

| 10.5       SCI Operation       .117         10.5.1       Transmitter       .117         10.5.2       Receiver       .120                                                                                                                                                                                               |

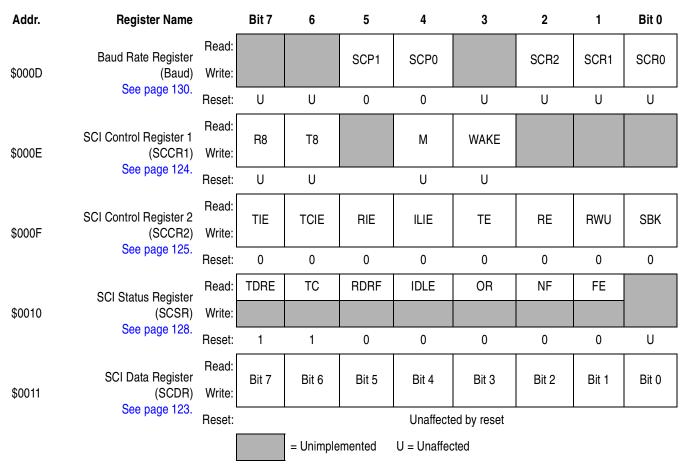

| 10.6       SCI I/O Registers       123         10.6.1       SCI Data Register (SCDR)       123         10.6.2       SCI Control Register 1       124         10.6.3       SCI Control Register 2       125         10.6.4       SCI Status Register       127         10.6.5       Baud Rate Register (Baud)       130 |

| Section 11. Serial Peripheral Interface (SPI)                                                                                                                                                                                                                                                                          |

| 11.1 Contents                                                                                                                                                                                                                                                                                                          |

| 11.2 Introduction                                                                                                                                                                                                                                                                                                      |

| 11.3 Features                                                                                                                                                                                                                                                                                                          |

| 11.4 Operation                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                        |

| 11.5 Multiple-SPI Systems                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                        |

| 11.5 Multiple-SPI Systems                                                                                                                                                                                                                                                                                              |

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

# **Table of Contents**

|                | 11.9.1 SPI Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43                                                             |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|                | 11.9.2 SPI Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |

|                | 11.9.3 SPI Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                             |

|                | Section 12. Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |

|                | 12.1 Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                             |

|                | 12.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48                                                             |

|                | 12.3       Addressing Modes       1         12.3.1       Inherent       1         12.3.2       Immediate       1         12.3.3       Direct       1         12.3.4       Extended       1         12.3.5       Indexed, No Offset       1         12.3.6       Indexed, 8-Bit Offset       1         12.3.7       Indexed, 16-Bit Offset       1         12.3.8       Relative       1         12.4.1       Register/Memory Instructions       1         12.4.2       Read-Modify-Write Instructions       1         12.4.3       Jump/Branch Instructions       1         12.4.4       Bit Manipulation Instructions       1         12.4.5       Control Instructions       1 | 49<br>49<br>49<br>50<br>50<br>51<br>51<br>52<br>53<br>54<br>56 |

|                | 12.5 Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

|                | 12.6 Opcode Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                |

|                | Section 13. Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                |

|                | 13.1 Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                             |

|                | 13.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65                                                             |

|                | 13.3 Maximum Ratings1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                             |

|                | 13.4 Operating Temperature Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67                                                             |

|                | 13.5 Thermal Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67                                                             |

| Technical Data | MC68HC705C4A • MC68HSC705C4A — Rev.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.0                                                            |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                |

| 13.6  | Power Considerations                                | 38 |

|-------|-----------------------------------------------------|----|

| 13.7  | 5.0-Volt DC Electrical Characteristics16            | 39 |

| 13.8  | 3.3-Volt DC Electrical Characteristics              | 70 |

| 13.9  | 5.0-Volt Control Timing17                           | 75 |

| 13.10 | 3.3-Volt Control Timing17                           | 76 |

| 13.11 | 5.0-Volt Serial Peripheral Interface (SPI) Timing   | 79 |

| 13.12 | 3.3-Volt Serial Peripheral Interface (SPI) Timing   | 31 |

|       | Section 14. Mechanical Specifications               |    |

| 14.1  | Contents                                            | 35 |

| 14.2  | Introduction                                        | 35 |

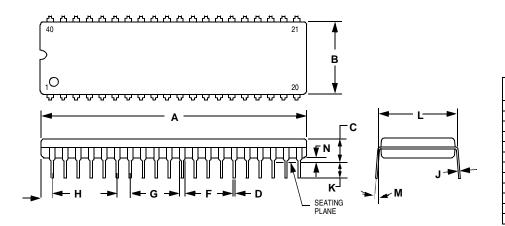

| 14.3  | 40-Pin Plastic Dual In-Line Package (PDIP)18        | 36 |

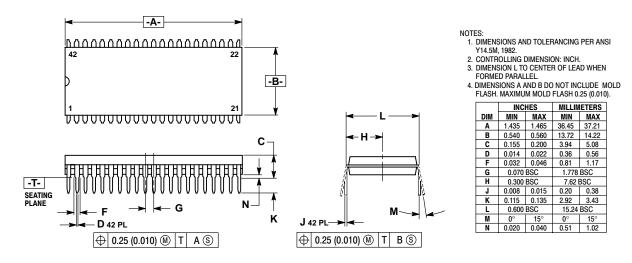

| 14.4  | 42-Pin Shrink Dual In-Line Package (SDIP)18         | 36 |

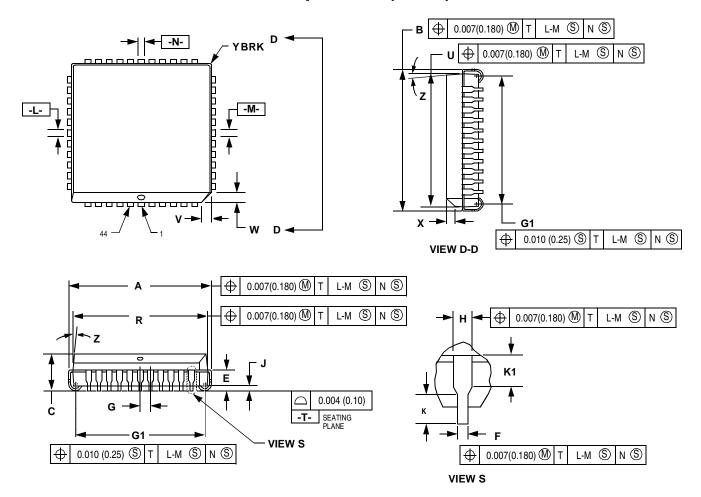

| 14.5  | 44-Lead Plastic-Leaded Chip Carrier (PLCC)18        | 37 |

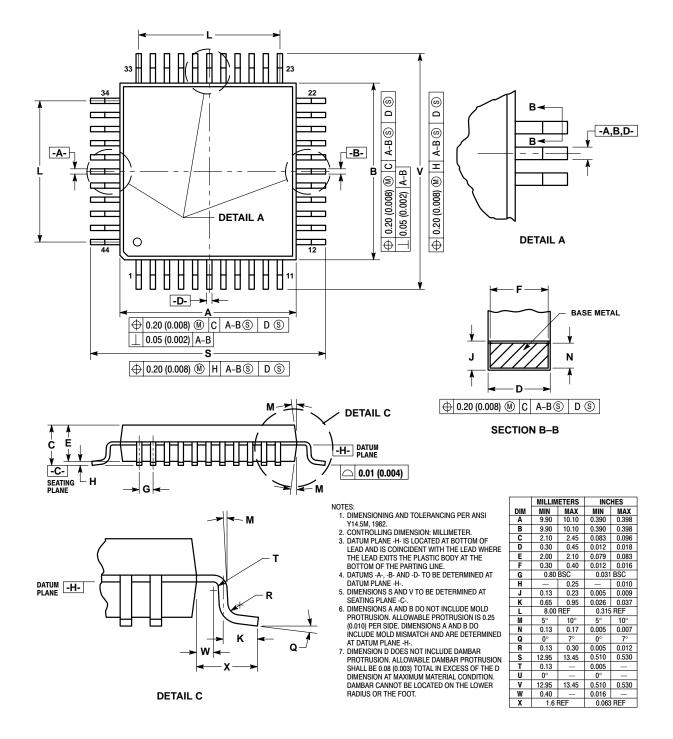

| 14.6  | 44-Pin Quad Flat Pack (QFP)18                       | 38 |

|       | Section 15. Ordering Information                    |    |

| 15.1  | Contents                                            | 39 |

| 15.2  | Introduction18                                      | 39 |

| 15.3  | MCU Order Numbers                                   | 39 |

|       | Appendix A. MC68HSC705C4A                           |    |

| A.1   | Contents                                            | 91 |

| A.2   | Introduction19                                      | 91 |

| A.3   | 5.0-Volt High-Speed DC Electrical Characteristics19 | 92 |

| A.4   | 3.3-Volt High-Speed DC Electrical Characteristics19 | 93 |

| A.5   | 5.0-Volt High-Speed Control Timing19                | 94 |

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

# **Table of Contents**

|            | Index                                 |

|------------|---------------------------------------|

|            | Index                                 |

| A.9        | Ordering Information199               |

| <b>A.8</b> | 3.3-Volt High-Speed SPI Timing197     |

| A.7        | 5.0-Volt High-Speed SPI Timing195     |

| A.6        | 3.3-Volt High-Speed Control Timing194 |

**Technical Data**

# **List of Figures**

| Title                                        | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Option Register (Option)                     | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Block Diagram                                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 40-Pin PDIP Pin Assignments                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

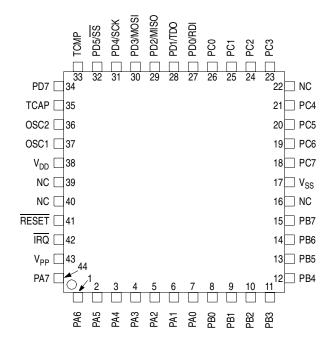

| 44-Lead PLCC Pin Assignments                 | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 44-Pin QFP Pin Assignments                   | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

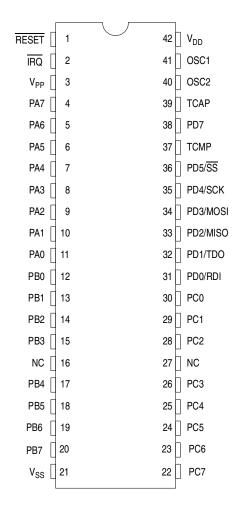

| 42-Pin SDIP Pin Assignments                  | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Bypassing Layout Recommendation              | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Crystal Connections                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2-Pin Ceramic Resonator                      | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3-Pin Ceramic Resonator Connections          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| External Clock                               | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Memory Map                                   | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| I/O Register Summary                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Programming Model                            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Accumulator (A)                              | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Index Register (X)                           | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Stack Pointer (SP)                           | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Program Counter (PC)                         | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Condition Code Register (CCR)                | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

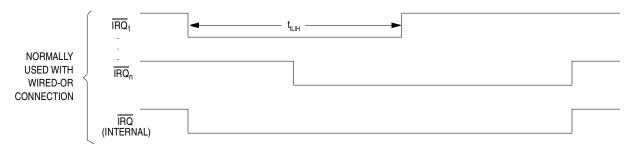

| External Interrupt Internal Function Diagram | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

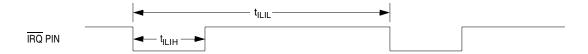

| External Interrupt Timing                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port B I/O Logic                             | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

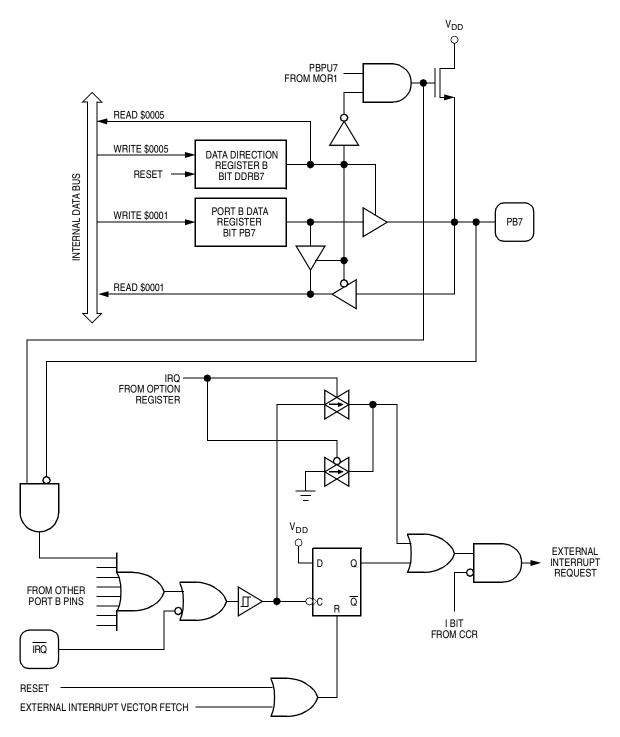

| Interrupt Stacking Order                     | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

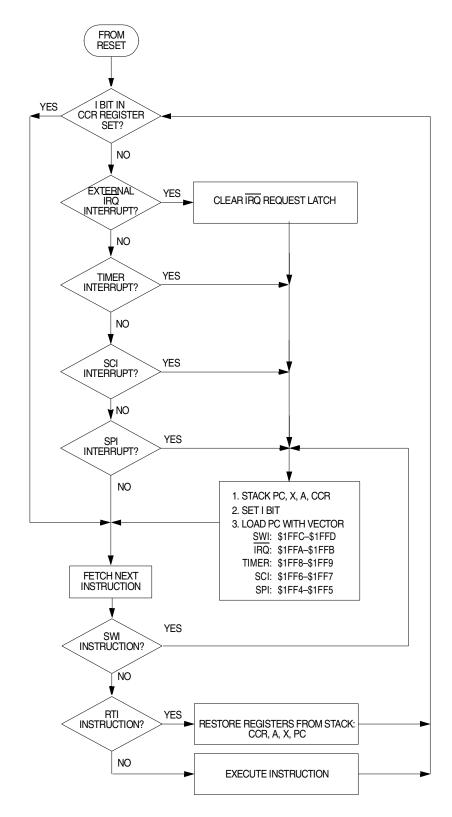

| Reset and Interrupt Processing Flowchart     | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

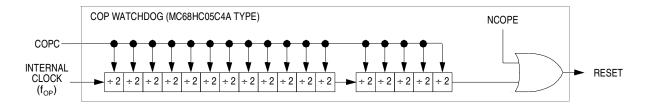

| COP Watchdog Diagram                         | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                              | Option Register (Option) Block Diagram 40-Pin PDIP Pin Assignments 44-Lead PLCC Pin Assignments 44-Pin QFP Pin Assignments 42-Pin SDIP Pin Assignments Bypassing Layout Recommendation Crystal Connections 2-Pin Ceramic Resonator 3-Pin Ceramic Resonator Connections External Clock  Memory Map I/O Register Summary  Programming Model Accumulator (A) Index Register (X) Stack Pointer (SP) Program Counter (PC) Condition Code Register (CCR)  External Interrupt Internal Function Diagram External Interrupt Timing Port B I/O Logic Interrupt Stacking Order Reset and Interrupt Processing Flowchart  COP Watchdog Diagram |

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

# List of Figures

| Figure | Title                                     | Page |

|--------|-------------------------------------------|------|

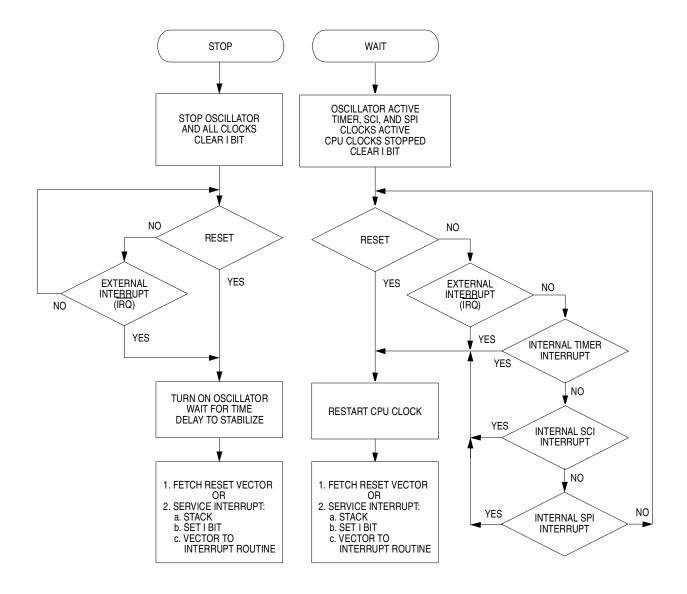

| 6-1    | Stop/Wait Mode Function Flowchart         | 68   |

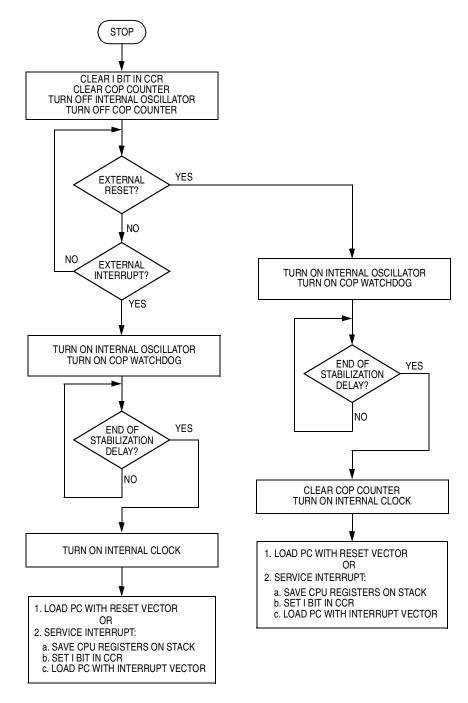

| 6-2    | COP Watchdog in Stop Mode Flowchart       |      |

|        | (NCOPE = 1)                               | 71   |

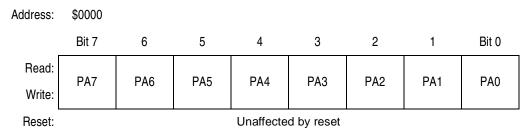

| 7-1    | Port A Data Register (PORTA)              | 74   |

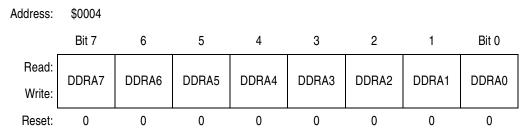

| 7-2    | Data Direction Register A (DDRA)          | 75   |

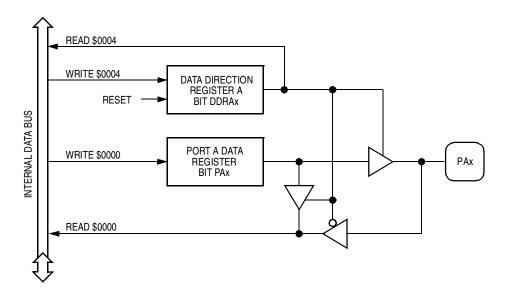

| 7-3    | Port A I/O Logic                          |      |

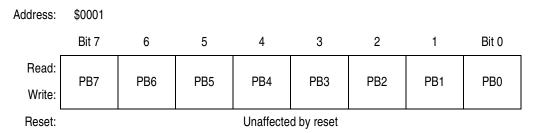

| 7-4    | Port B Data Register (PORTB)              | 77   |

| 7-5    | Data Direction Register B (DDRB)          | 78   |

| 7-6    | Port B I/O Logic                          | 79   |

| 7-7    | Port C Data Register (PORTC)              | 81   |

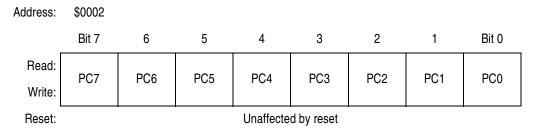

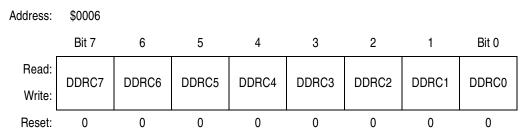

| 7-8    | Data Direction Register C (DDRC)          | 82   |

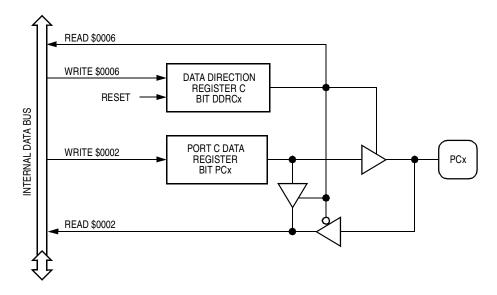

| 7-9    | Port C I/O Logic                          | 83   |

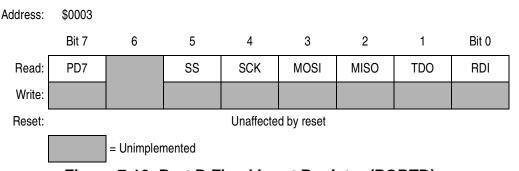

| 7-10   | Port D Fixed Input Register (PORTD)       | 84   |

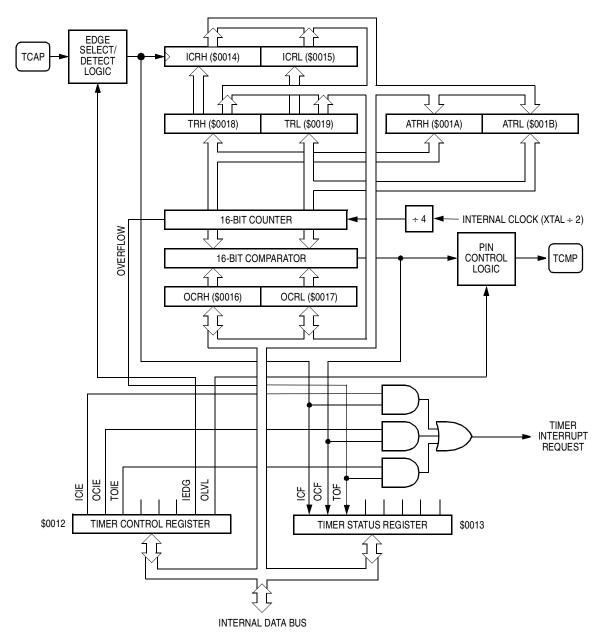

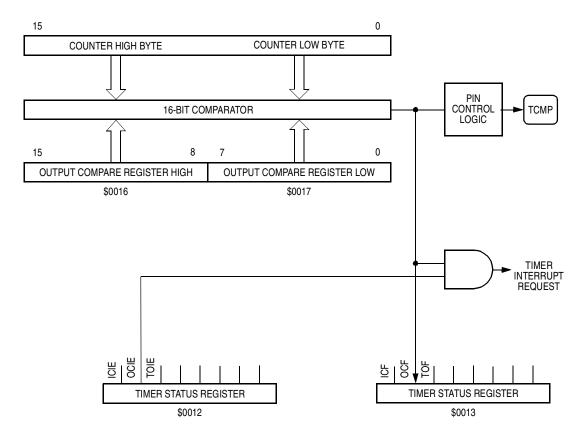

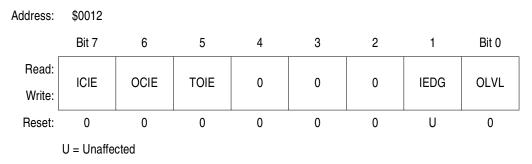

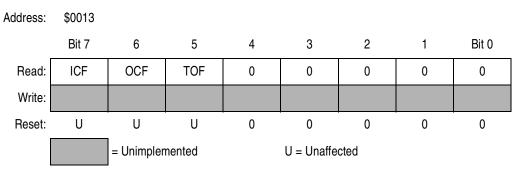

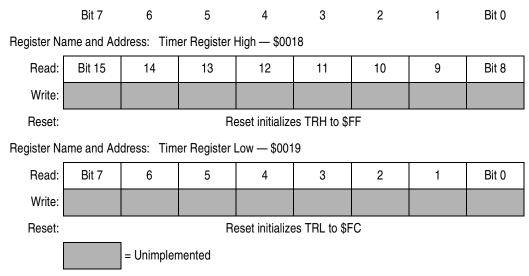

| 8-1    | Timer Block Diagram                       | 86   |

| 8-2    | Timer I/O Register Summary                |      |

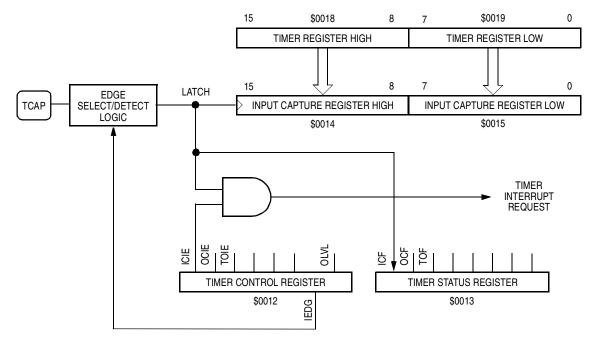

| 8-3    | Input Capture Operation                   | 88   |

| 8-4    | Output Compare Operation                  | 89   |

| 8-5    | Timer Control Register (TCR)              | 90   |

| 8-6    | Timer Status Register (TSR)               | 92   |

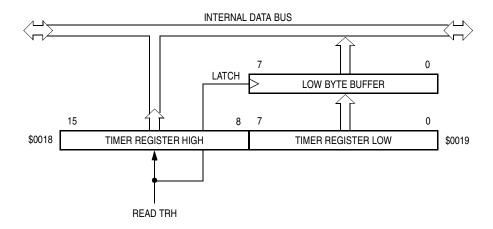

| 8-7    | Timer Registers (TRH and TRL)             | 93   |

| 8-8    | Timer Register Reads                      |      |

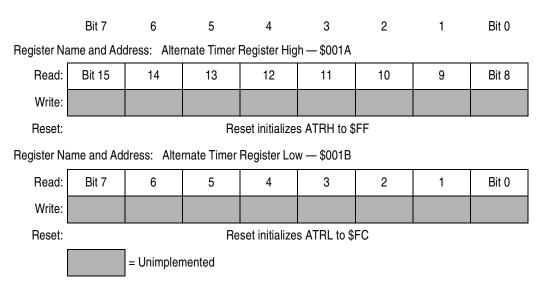

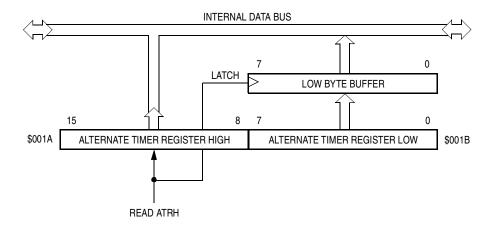

| 8-9    | Alternate Timer Registers (ATRH and ATRL) |      |

| 8-10   | Alternate Timer Register Reads            |      |

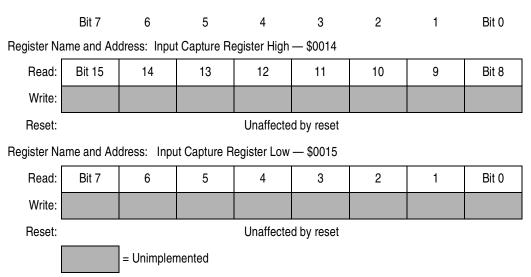

| 8-11   | Input Capture Registers (ICRH and ICRL)   |      |

| 8-12   | Output Compare Registers (OCRH and OCRL)  | 96   |

| 9-1    | EPROM/OTPROM Programming Flowchart        | .101 |

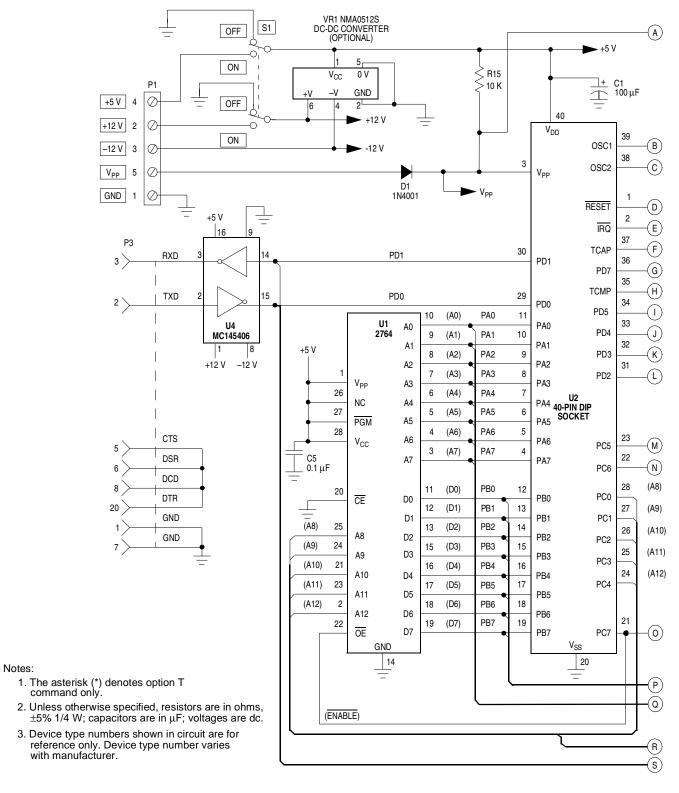

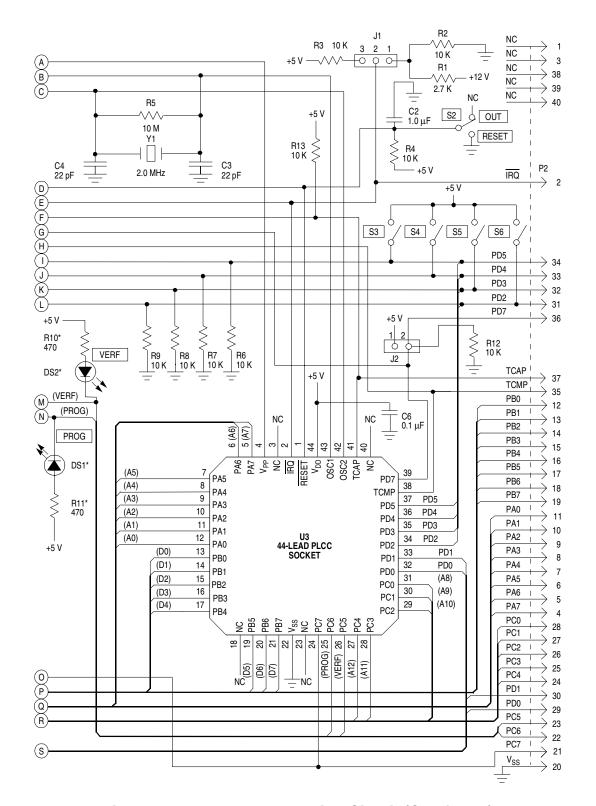

| 9-2    | PROM Programming Circuit                  | .102 |

| 9-3    | Program Register (PROG)                   | .105 |

| 9-4    | Option Register (Option)                  |      |

| 9-5    | Mask Option Register 1 (MOR1)             | .113 |

| 9-6    | Mask Option Register 2 (MOR2)             | .114 |

**Technical Data**

${\sf MC68HC705C4A \bullet MC68HSC705C4A -- Rev.~3.0}$

| Figure | Title                                            | Page  |

|--------|--------------------------------------------------|-------|

| 10-1   | SCI Data Format                                  | .116  |

| 10-2   | SCI Transmitter                                  | .118  |

| 10-3   | SCI Transmitter I/O Register Summary             | .119  |

| 10-4   | SCI Receiver                                     | .121  |

| 10-5   | SCI Data Register (SCDR)                         | .123  |

| 10-6   | SCI Control Register 1 (SCCR1)                   | .124  |

| 10-7   | SCI Control Register 2 (SCCR2)                   | .125  |

| 10-8   | SCI Status Register (SCSR)                       | .128  |

| 10-9   | Baud Rate Register (Baud)                        | .130  |

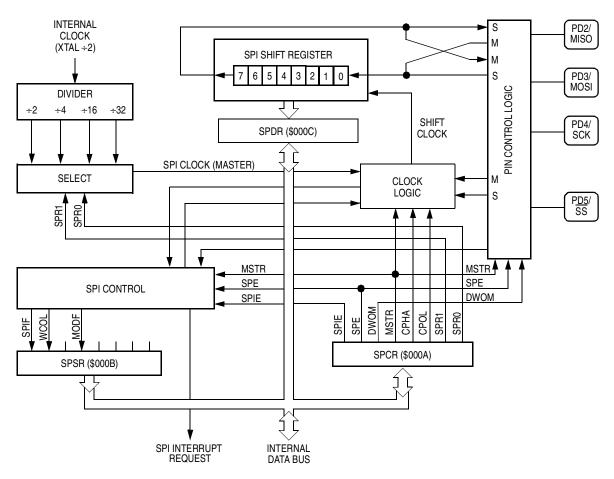

| 11-1   | SPI Block Diagram                                | .135  |

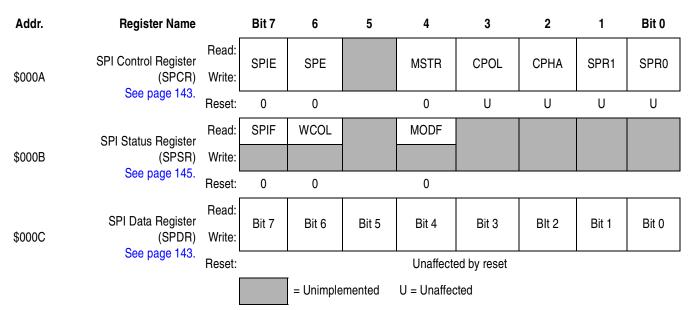

| 11-2   | SPI I/O Register Summary                         | .136  |

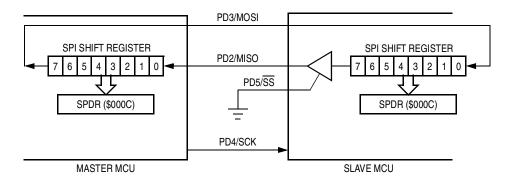

| 11-3   | Master/Slave Connections                         | .137  |

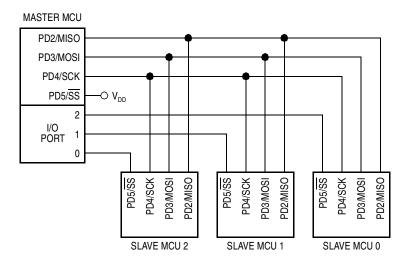

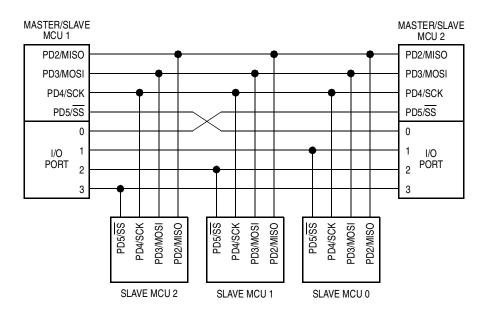

| 11-4   | One Master and Three Slaves Block Diagram        | .139  |

| 11-5   | Two Master/Slaves and Three Slaves Block Diagram | .140  |

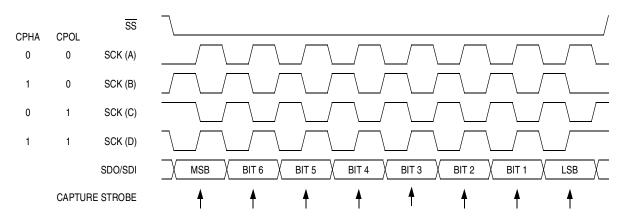

| 11-6   | SPI Clock/Data Timing                            | .140  |

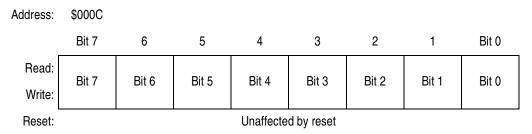

| 11-7   | SPI Data Register (SPDR)                         | .143  |

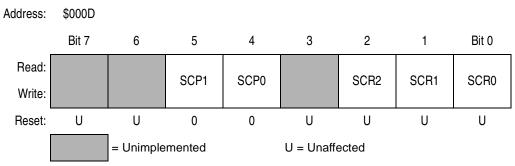

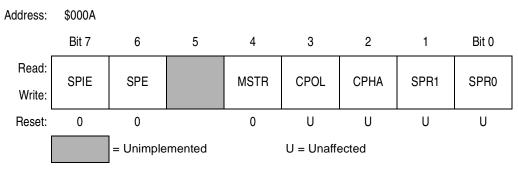

| 11-8   | SPI Control Register (SPCR)                      | .143  |

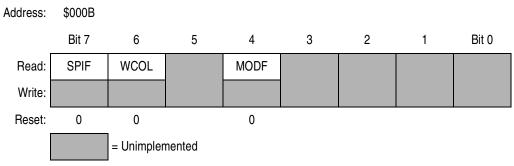

| 11-9   | SPI Status Register (SPSR)                       | .145  |

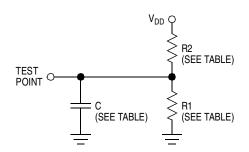

| 13-1   | Equivalent Test Load                             | .167  |

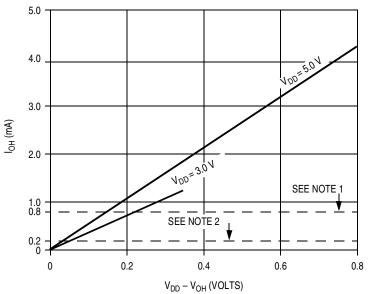

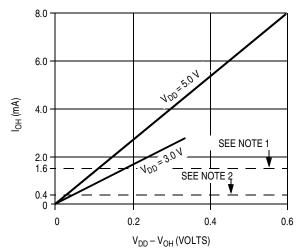

| 13-2   | Typical Voltage Compared to Current              | .171  |

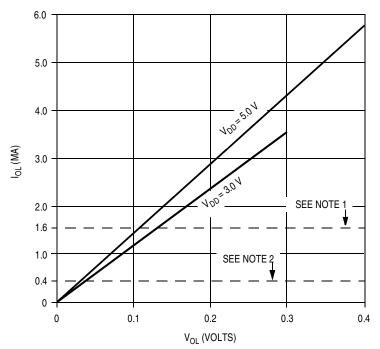

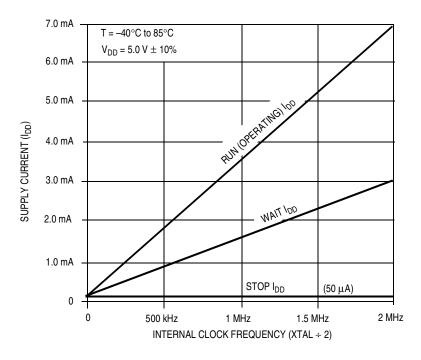

| 13-3   | Typical Current versus Internal                  |       |

|        | Frequency for Run and Wait Modes                 | .173  |

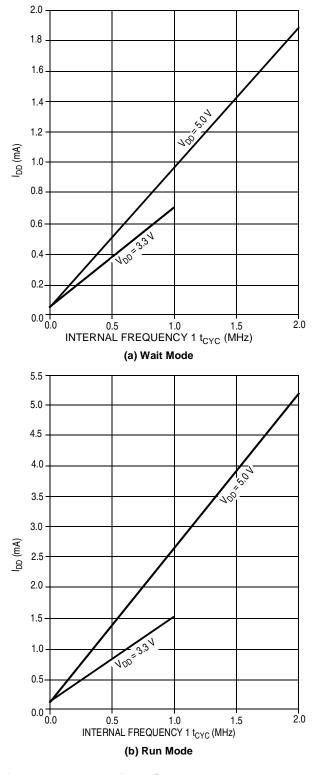

| 13-4   | Total Current Drain versus Frequency             |       |

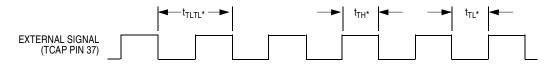

| 13-5   | Timer Relationships                              |       |

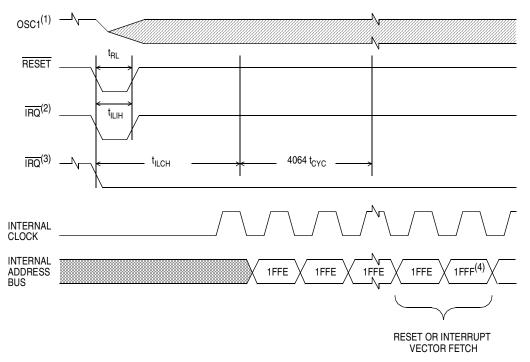

| 13-6   | Stop Recovery Timing Diagram                     | .177  |

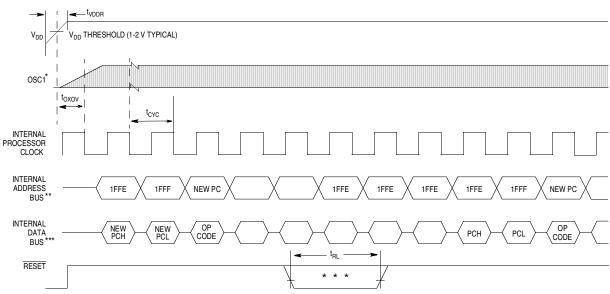

| 13-7   | Power-On Reset and External Reset Timing Diagram | .178  |

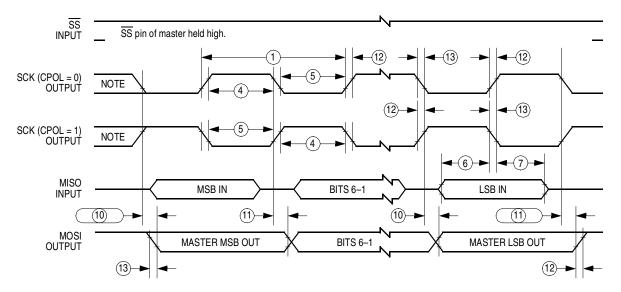

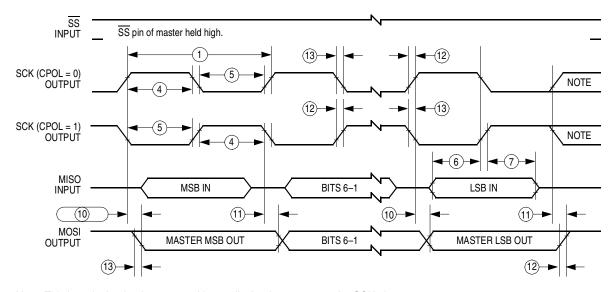

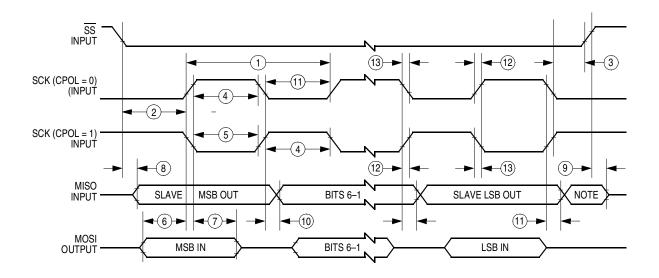

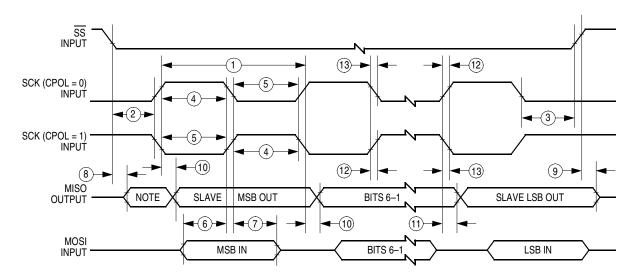

| 13-8   | SPI Master Timing                                | .183  |

| 13-9   | SPI Slave Timing                                 | .184  |

| 14-1   | MC68HC705C4AP Package Dimensions                 | 400   |

| 44.0   | (Case #711)                                      | . 186 |

| 14-2   | MC68HC705C4AB Package Dimensions                 | 400   |

|        | (Case #858)                                      | .186  |

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

# List of Figures

| Figure | Title                             | Page |

|--------|-----------------------------------|------|

| 14-3   | MC68HC705C4AFN Package Dimensions |      |

|        | (Case #777)                       | 187  |

| 14-4   | MC68HC705C4AFB Package Dimensions |      |

|        | (Case #824E)                      | 188  |

# **List of Tables**

| Table      | Title                                  | Page |

|------------|----------------------------------------|------|

| 4-1        | Reset/Interrupt Vector Addresses       | 60   |

| 7-1<br>7-2 | Port A Pin Functions                   |      |

| 7-3        | Port C Pin Functions                   |      |

| 9-1        | MC68HC05PGMR PCB Reference Designators |      |

| 9-2        | PROM Programming Routines              | 104  |

| 10-1       | Baud Rate Generator Clock Prescaling   |      |

| 10-2       | Baud Rate Selection                    |      |

| 10-3       | Baud Rate Selection Examples           | 132  |

| 11-1       | SPI Clock Rate Selection               | 144  |

| 12-1       | Register/Memory Instructions           |      |

| 12-2       | Read-Modify-Write Instructions         |      |

| 12-3       | Jump and Branch Instructions           |      |

| 12-4       | Bit Manipulation Instructions          |      |

| 12-5       | Control Instructions                   |      |

| 12-6       | Instruction Set Summary                |      |

| 12-7       | Opcode Map                             | 164  |

| 15-1       | MC68HC705C4A Order Numbers             | 189  |

| Δ-1        | MC68HSC705C4A Order Numbers            | 199  |

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

# List of Tables

# **Section 1. General Description**

### 1.1 Contents

| 1.2     | Introduction                         |

|---------|--------------------------------------|

| 1.3     | Features                             |

| 1.4     | Programmable Options23               |

| 1.5     | Block Diagram24                      |

| 1.6     | Pin Assignments24                    |

| 1.7     | Pin Functions                        |

| 1.7.1   | V <sub>DD</sub> and V <sub>SS</sub>  |

| 1.7.2   | OSC1 and OSC2                        |

| 1.7.2.  | 1 Crystal Resonator30                |

| 1.7.2.  |                                      |

| 1.7.2.3 | 3 External Clock Signal              |

| 1.7.3   | External Reset Pin (RESET)32         |

| 1.7.4   | External Interrupt Request Pin (IRQ) |

| 1.7.5   | Input Capture Pin (TCAP)32           |

| 1.7.6   | Output Compare Pin (TCMP)33          |

| 1.7.7   | Port A I/O Pins (PA7–PA0)            |

| 1.7.8   | Port B I/O Pins (PB7–PB0)            |

| 1.7.9   | Port C I/O Pins (PC7–PC0)            |

| 1.7.10  |                                      |

### 1.2 Introduction

The MC68HC705C4A is a member of the low-cost, high-performance M68HC05 Family of 8-bit microcontroller units (MCUs). The M68HC05 Family is based on the customer-specified integrated circuit (CSIC) design strategy. All MCUs in the family use the M68HC05 central

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

processor unit (CPU) and are available with a variety of subsystems, memory sizes and types, and package types.

The MC68HC705C4A is similar to the MC68HC705C8A. The major differences are that the MC68HC705C4A has less RAM and ROM, no selectable memory configurations, no clock monitor reset function, and only one computer operating properly (COP) watchdog timer. The MC68HSC705C4A, introduced in **Appendix A. MC68HSC705C4A**, is an enhanced, high-speed version of the MC68HC705C4A.

#### 1.3 Features

#### Features of the MC68HC705C4A include:

- M68HC05 central processor unit (CPU)

- On-chip oscillator with crystal/ceramic resonator

- Memory-mapped input/output (I/O)

- Computer operating properly (COP) watchdog timer

- · Selectable port B external interrupt capability

- High current drive on pin C7 (PC7)

- 24 bidirectional I/O lines and 7 input-only lines

- Serial communications interface (SCI) system

- Serial peripheral interface (SPI) system

- Bootstrap capability

- Power-saving stop, wait, and data-retention modes

- Single 3.0-volt to 5.5-volt supply (2-volt data-retention mode)

- Fully static operation

- Software-programmable external interrupt sensitivity

#### NOTE:

A line over a signal name indicates an active low signal. For example, RESET is active high and RESET is active low. Any reference to voltage, current, or frequency specified in the following sections will refer to the nominal values. The exact values and their tolerance or limits are specified in **Section 13. Electrical Specifications**.

Technical Data

### 1.4 Programmable Options

These options are programmable in the mask option registers:

- Enabling of port B pullup devices (see 9.5.2 Mask Option Register 1)

- Enabling of non-programmable COP watchdog (see 9.5.3 Mask Option Register 2)

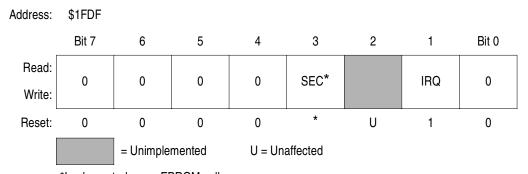

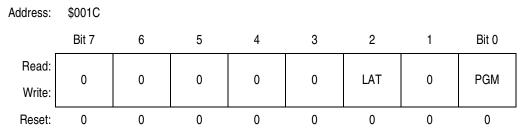

These options are programmable in the option register (shown in **Figure 1-1**):

- PROM security<sup>(1)</sup>

- External interrupt sensitivity

\*Implemented as an EPROM cell

Figure 1-1. Option Register (Option)

SEC — Security Bit

This bit is implemented as an EPROM cell and is not affected by reset.

- 1 = Bootloader disabled; MCU operates only in single-chip mode.

- 0 = Security off; bootloader can be enabled.

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

<sup>1.</sup> No security feature is absolutely secure. However, Motorola's strategy is to make reading or copying the PROM difficult for unauthorized users.

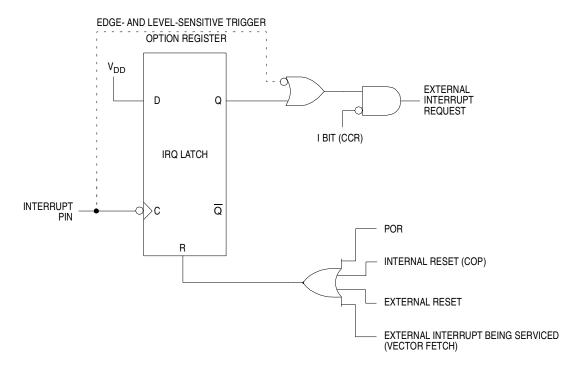

IRQ — Interrupt Request Pin Sensitivity Bit

IRQ is set only by reset, but can be cleared by software. This bit can be written only once.

- 1 = IRQ pin is both negative edge- and level-sensitive.

- $0 = \overline{IRQ}$  pin is negative edge-sensitive only.

Bits 7-4 and 0 — Not used; always read 0

Bit 2 — Unaffected by reset; reads either 1 or 0

### 1.5 Block Diagram

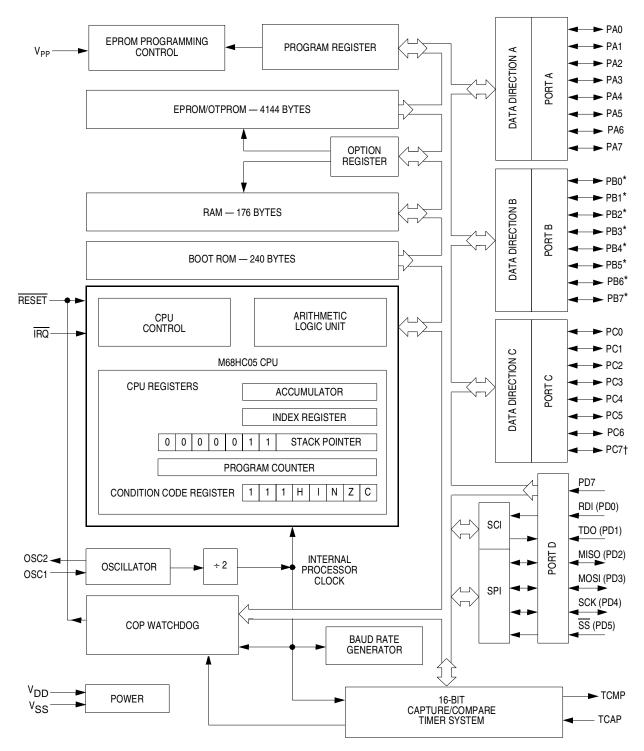

Figure 1-2 shows the structure of the MC68HC705C4A.

### 1.6 Pin Assignments

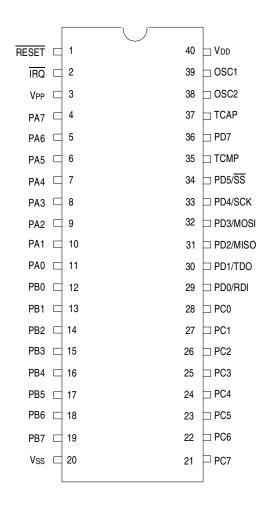

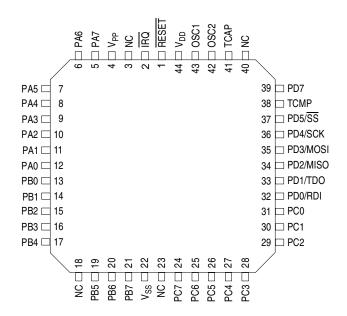

The MC68HC705C4A is available in four packages:

- 40-pin plastic dual in-line package (PDIP)

- 44-lead plastic-leaded chip carrier (PLCC)

- 44-pin quad flat pack (QFP)

- 42-pin shrink dual in-line package (SDIP)

The pin assignments for these packages are shown in **Figure 1-3**, **Figure 1-4**, **Figure 1-5**, and **Figure 1-6**.

<sup>\*</sup> Port B pins also function as external interrupts.

Figure 1-2. Block Diagram

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

<sup>†</sup> PC7 has a high current sink and source capability.

Figure 1-3. 40-Pin PDIP Pin Assignments

Technical Data

26

Figure 1-4. 44-Lead PLCC Pin Assignments

Figure 1-5. 44-Pin QFP Pin Assignments

Figure 1-6. 42-Pin SDIP Pin Assignments

28

#### 1.7 Pin Functions

The following paragraphs describe the MC68HC705C4A signals.

### 1.7.1 $V_{DD}$ and $V_{SS}$

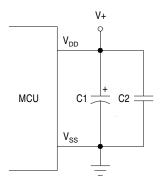

$V_{\text{DD}}$  and  $V_{\text{SS}}$  are the power supply and ground pins. The MCU operates from a single power supply.

Very fast signal transitions occur on the MCU pins, placing high short-duration current demands on the power supply. To prevent noise problems, take special care to provide good power supply bypassing at the MCU. Place bypass capacitors as close to the MCU as possible, as shown in **Figure 1-7**.

Figure 1-7. Bypassing Layout Recommendation

#### 1.7.2 OSC1 and OSC2

The OSC1 and OSC2 pins are the control connections for the 2-pin on-chip oscillator. The oscillator can be driven by:

- Crystal resonator

- Ceramic resonator

- External clock signal

**NOTE:** The frequency of the internal oscillator is  $f_{OSC}$ . The MCU divides the internal oscillator output by two to produce the internal clock with a

frequency of f<sub>OP</sub>.

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

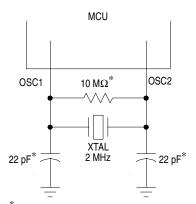

#### 1.7.2.1 Crystal Resonator

The circuit in **Figure 1-8** shows a crystal oscillator circuit for an AT-cut, parallel resonant crystal. Follow the crystal supplier's recommendations, because the crystal parameters determine the external component values required to provide reliable startup and maximum stability. The load capacitance values used in the oscillator circuit design should account for all stray layout capacitances. To minimize output distortion, mount the crystal and capacitors as close as possible to the pins.

<sup>\*</sup>Starting value only. Follow crystal supplier's recommendations regarding component values that will provide reliable startup and maximum stability.

Figure 1-8. Crystal Connections

**NOTE:** Use an AT-cut crystal and not a strip or tuning fork crystal. The MCU might overdrive or have the incorrect characteristic impedance for a strip or tuning fork crystal.

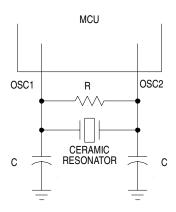

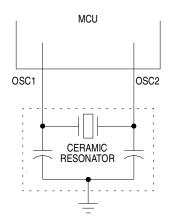

#### 1.7.2.2 Ceramic Resonator

To reduce cost, use a ceramic resonator instead of a crystal. Use the circuit shown in **Figure 1-9** for a 2-pin ceramic resonator or the circuit shown in **Figure 1-10** for a 3-pin ceramic resonator, and follow the resonator manufacturer's recommendations.

The external component values required for maximum stability and reliable starting depend upon the resonator parameters. The load capacitance values used in the oscillator circuit design should include all

**Technical Data**

stray layout capacitances. To minimize output distortion, mount the resonator and capacitors as close as possible to the pins.

Figure 1-9. 2-Pin Ceramic Resonator

**NOTE:** The bus frequency  $(f_{OP})$  is one-half the external or crystal frequency  $(f_{OSC})$ , while the processor clock cycle  $(t_{CYC})$  is two times the  $f_{OSC}$  period.

Figure 1-10. 3-Pin Ceramic Resonator Connections

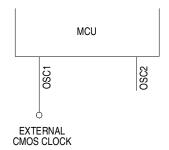

#### 1.7.2.3 External Clock Signal

An external clock from another CMOS-compatible device can drive the OSC1 input, with the OSC2 pin unconnected, as Figure 1-11 shows.

Figure 1-11. External Clock

**NOTE:** The bus frequency  $(f_{OP})$  is one-half the external frequency  $(f_{OSC})$  while the processor clock cycle is two times the  $f_{OSC}$  period.

### 1.7.3 External Reset Pin (RESET)

A logic 0 on the RESET pin forces the MCU to a known startup state. The RESET pin contains an internal Schmitt trigger as part of its input to improve noise immunity. See **Section 5. Resets**.

### 1.7.4 External Interrupt Request Pin (IRQ)

The IRQ pin is an asynchronous external interrupt pin. The IRQ pin contains an internal Schmitt trigger as part of its input to improve noise immunity. See **4.3.2 External Interrupt (IRQ)**.

### 1.7.5 Input Capture Pin (TCAP)

The TCAP pin is the input capture pin for the on-chip capture/compare timer. The TCAP pin contains an internal Schmitt trigger as part of its input to improve noise immunity. See **Section 8. Capture/Compare Timer**.

Technical Data

#### 1.7.6 Output Compare Pin (TCMP)

The TCMP pin is the output compare pin for the on-chip capture/compare timer. See **Section 8. Capture/Compare Timer**.

#### 1.7.7 Port A I/O Pins (PA7-PA0)

These eight I/O lines comprise port A, a general-purpose, bidirectional I/O port. The pins are programmable as either inputs or outputs under software control of the data direction registers. See **7.3 Port A**.

#### 1.7.8 Port B I/O Pins (PB7-PB0)

These eight I/O pins comprise port B, a general-purpose, bidirectional I/O port. The pins are programmable as either inputs or outputs under software control of the data direction registers. Port B pins also can be configured to function as external interrupts. See **7.4 Port B**.

### 1.7.9 Port C I/O Pins (PC7-PC0)

These eight I/O pins comprise port C, a general-purpose, bidirectional I/O port. The pins are programmable as either inputs or outputs under software control of the data direction registers. PC7 has a high current sink and source capability See **7.5 Port C**.

### 1.7.10 Port D I/O Pins (PD7 and PD5-PD0)

These seven lines comprise port D, a fixed input port. All special functions that are enabled (SPI and SCI) affect this port. See **7.6 Port D**.

**NOTE:** Connecting the  $V_{PP}$  pin (programming voltage) to  $V_{SS}$  (ground) could result in damage to the MCU.

34

### Section 2. Memory

### 2.1 Contents

| 2.2 | Introduction        | . 35 |

|-----|---------------------|------|

| 2.3 | Memory Map          | . 35 |

| 2.4 | Input/Output (I/O)  | . 36 |

| 2.5 | RAM                 | .36  |

| 2.6 | EPROM/OTPROM (PROM) | .37  |

| 2.7 | Bootloader ROM      | .37  |

#### 2.2 Introduction

This section describes the organization of the on-chip memory.

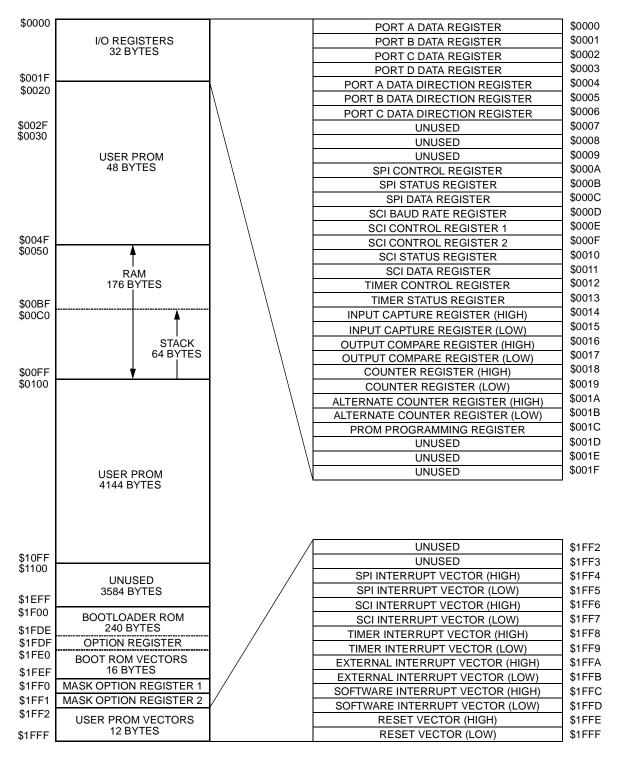

### 2.3 Memory Map

The central processor unit (CPU) can address eight Kbytes of memory and input/output (I/O) registers. The program counter typically advances one address at a time through memory, reading the program instructions and data. The programmable read-only memory (PROM) portion of memory — either one-time programmable read-only memory (OTPROM) or erasable programmable read-only memory (EPROM) — holds the program instructions, fixed data, user-defined vectors, and interrupt service routines. The RAM portion of memory holds variable data.

I/O registers are memory-mapped so that the CPU can access their locations in the same way that it accesses all other memory locations. The shared stack area is used during processing of an interrupt or

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

subroutine call to save the CPU state. The stack pointer decrements during pushes and increments during pulls.

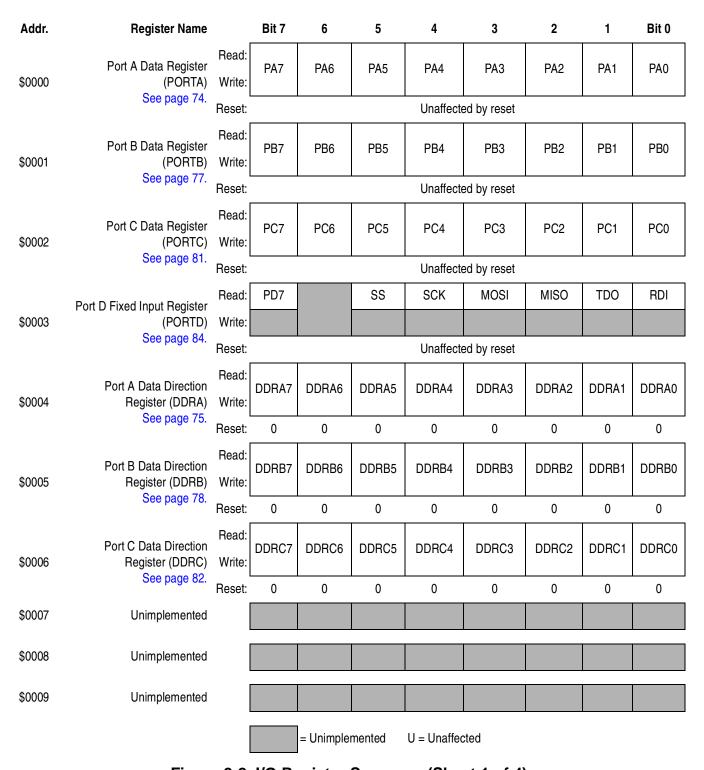

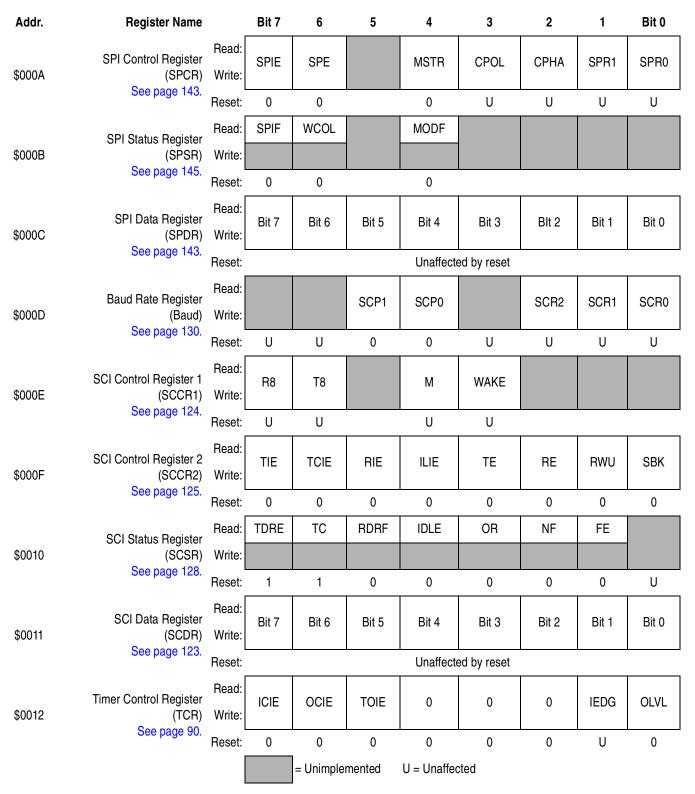

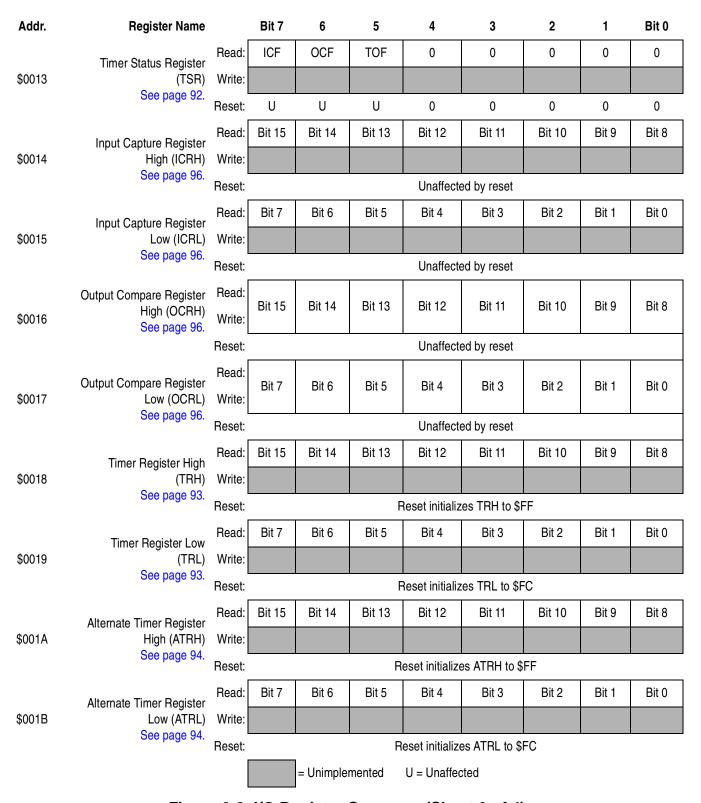

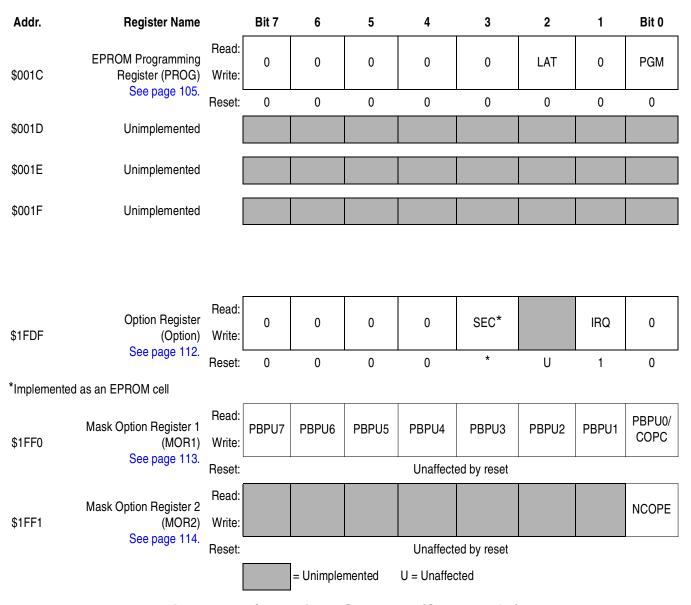

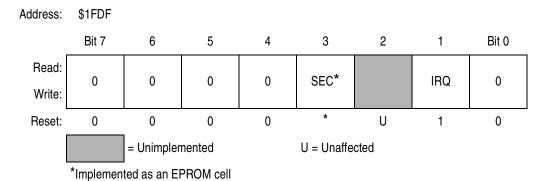

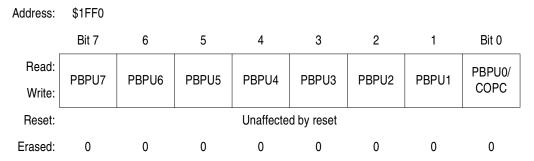

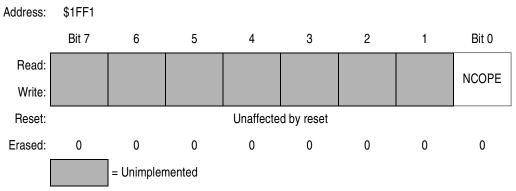

**Figure 2-1** is a memory map of the MCU. Addresses \$0000–\$001F, shown in **Figure 2-2**, contain most of the control, status, and data registers. Additional I/O registers have these addresses:

- \$1FDF, option register

- \$1FF0, mask option register 1 (MOR1)

- \$1FF1, mask option register 2 (MOR2)

### 2.4 Input/Output (I/O)

The first 32 addresses of memory space, from \$0000 to \$001F, are the I/O section. These are the addresses of the I/O control registers, status registers, and data registers. See **Figure 2-2** for more information.

#### 2.5 **RAM**

The 176 addresses from \$0050–\$00FF are RAM locations. The CPU uses the top 64 RAM addresses, \$00C0–00FF, as the stack. Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers. During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements when the CPU stores a byte on the stack and increments when the CPU retrieves a byte from the stack.

NOTE:

Be careful when using nested subroutines or multiple interrupt levels. The CPU can overwrite data in the stack RAM during a subroutine or during the interrupt stacking operation.

## 2.6 EPROM/OTPROM (PROM)

An MCU with a quartz window has a maximum of 4144 bytes of EPROM. The quartz window allows the EPROM erasure with ultraviolet light. In an MCU without a quartz window, the EPROM cannot be erased and serves a maximum 4144 bytes of OTPROM. See **Section 9**. **EPROM/OTPROM (PROM)**.

#### 2.7 Bootloader ROM

The 240 bytes at addresses \$1F00—\$1FEF are reserved ROM addresses that contain the instructions for the bootloader functions. See **Section 9. EPROM/OTPROM (PROM)**.

Figure 2-1. Memory Map

**Technical Data**

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

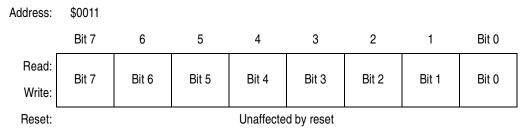

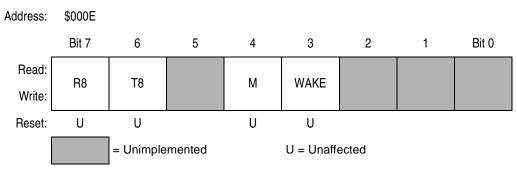

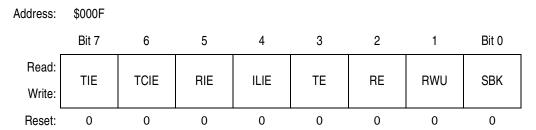

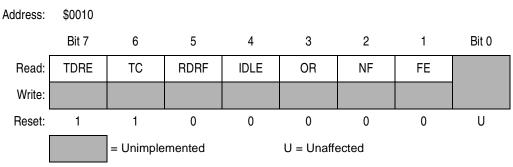

Figure 2-2. I/O Register Summary (Sheet 1 of 4)

Figure 2-2. I/O Register Summary (Sheet 2 of 4)

Technical Data MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

Figure 2-2. I/O Register Summary (Sheet 3 of 4)

MC68HC705C4A • MC68HSC705C4A — Rev. 3.0

Figure 2-2. I/O Register Summary (Sheet 4 of 4)

# **Section 3. Central Processor Unit (CPU)**

## 3.1 Contents

| 3.2   | Introduction                | 3 |

|-------|-----------------------------|---|

| 3.3   | CPU Registers               | 4 |

| 3.3.1 | Accumulator4                | 5 |

| 3.3.2 | Index Register              | 5 |

| 3.3.3 | Stack Pointer               | 3 |

| 3.3.4 | Program Counter             | 7 |

| 3.3.5 | Condition Code Register     | 3 |

| 3.4   | Arithmetic/Logic Unit (ALU) | 9 |

## 3.2 Introduction

This section describes the central processor unit (CPU) registers.

## 3.3 CPU Registers

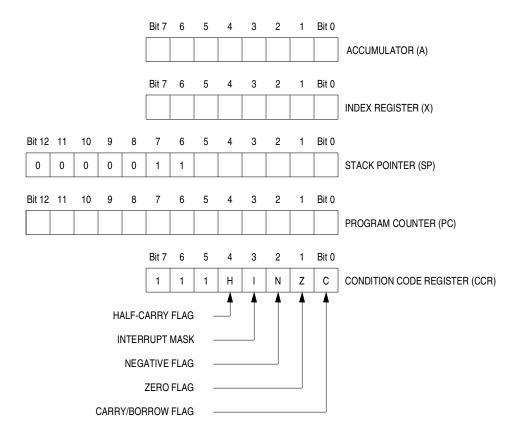

Figure 3-1 shows the five CPU registers:

- Accumulator (A)

- Index register (X)

- Stack pointer (SP)

- Program counter (PC)

- Condition code register (CCR)

These are hard-wired registers within the CPU and are not part of the memory map.

Figure 3-1. Programming Model

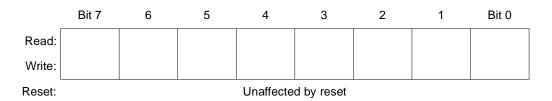

#### 3.3.1 Accumulator

The accumulator (A) shown in **Figure 3-2** is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and results of arithmetic and non-arithmetic operations.

Figure 3-2. Accumulator (A)

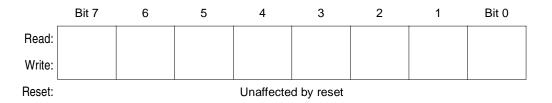

## 3.3.2 Index Register

In the indexed addressing modes, the CPU uses the byte in the index register (X) to determine the conditional address of the operand (Figure 3-3). For more information on indexed addressing, see 12.3.5 Indexed, No Offset, 12.3.6 Indexed, 8-Bit Offset, and 12.3.7 Indexed, 16-Bit Offset.

Figure 3-3. Index Register (X)

The 8-bit index register also can serve as a temporary data storage location.

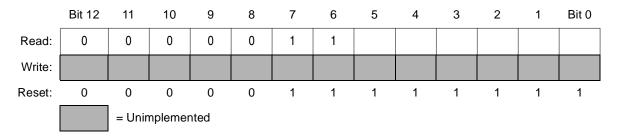

#### 3.3.3 Stack Pointer

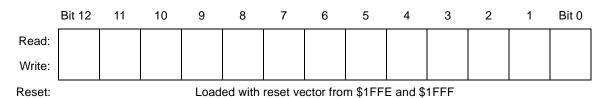

The stack pointer (SP) shown in **Figure 3-4** is a 13-bit register that contains the address of the next free location on the stack. During a reset or after the reset stack pointer (RSP) instruction, the stack pointer initializes to \$00FF. The address in the stack pointer decrements as data is pushed onto the stack and increments as data is pulled from the stack.

Figure 3-4. Stack Pointer (SP)

The seven most significant bits of the stack pointer are fixed permanently at 0000011, so the stack pointer produces addresses from \$00C0 to \$00FF. If subroutines and interrupts use more than 64 stack locations, the stack pointer wraps around to address \$00FF and begins writing over the previously stored data. A subroutine uses two stack locations. An interrupt uses five locations.

#### 3.3.4 Program Counter

The program counter (PC) shown in **Figure 3-5** is a 13-bit register that contains the address of the next instruction or operand to be fetched.

Normally, the address in the program counter automatically increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

Figure 3-5. Program Counter (PC)

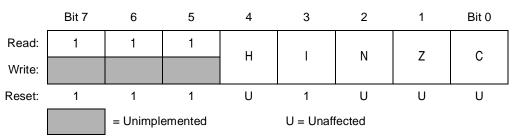

#### 3.3.5 Condition Code Register

The condition code register (CCR) shown in **Figure 3-6** is an 8-bit register whose three most significant bits are permanently fixed at 111. The condition code register contains the interrupt mask and four bits that indicate the results of prior instructions. Functions of the condition code register are described here.

Figure 3-6. Condition Code Register (CCR)

#### H — Half-Carry Bit (H)

The CPU sets the half-carry flag when a carry occurs between bits 3 and 4 of the accumulator during an add without carry (ADD) or add with carry (ADC) operation. The half-carry bit is required for binary-coded decimal (BCD) arithmetic operations. Reset has no affect on the half-carry flag.

#### I — Interrupt Mask

Setting the interrupt mask (I) disables interrupts. If an interrupt request occurs while the interrupt mask is a logic 0, the CPU saves the CPU registers on the stack, sets the interrupt mask, and then fetches the interrupt vector. If an interrupt request occurs while the interrupt mask is set, the interrupt request is latched. The CPU processes the latched interrupt as soon as the interrupt mask is cleared again.

A return from interrupt (RTI) instruction pulls the CPU registers from the stack, restoring the interrupt mask to its cleared state. After a reset, the interrupt mask is set and can be cleared only by a clear interrupt mask bit (CLI), STOP, or WAIT instruction.

#### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logical operation, or data manipulation produces a negative result (bit 7 in the results is a logic 1). Reset has no effect on the negative flag.

#### Z — Zero Flag