# TP3040, TP3040A PCM Monolithic Filter

## **General Description**

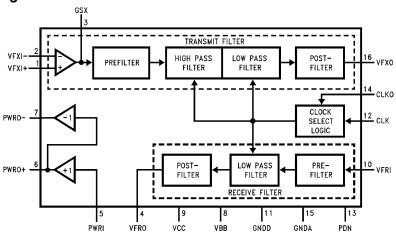

The TP3040/TP3040A filter is a monolithic circuit containing both transmit and receive filters specifically designed for PCM CODEC filtering applications in 8 kHz sampled systems.

The filter is manufactured using microCMOS technology and switched capacitor integrators are used to simulate classical LC ladder filters which exhibit low component sensitivity.

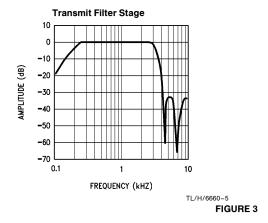

#### TRANSMIT FILTER STAGE

The transmit filter is a fifth order elliptic low pass filter in series with a fourth order Chebyshev high pass filter. It provides a flat response in the passband and rejection of signals below 200 Hz and above 3.4 kHz.

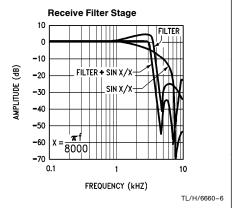

#### RECEIVE FILTER STAGE

The receive filter is a fifth order elliptic low pass filter designed to reconstruct the voice signal from the decoded/demultiplexed signal which, as a result of the sampling process, is a stair-step signal having the inherent sin x/x frequency response. The receive filter approximates the function required to compensate for the degraded frequency response and restore the flat passband response.

### **Features**

- Designed for D3/D4 and CCITT applications

- $\blacksquare$  +5V, -5V power supplies

- Low power consumption:

- 45 mW (0 dBm0 into 600 $\Omega$ )

- 30 mW (power amps disabled)

- Power down mode: 0.5 mW

- 20 dB gain adjust range

- No external anti-aliasing components

- Sin x/x correction in receive filter

- 50/60 Hz rejection in transmit filter

- TTL and CMOS compatible logic

- All inputs protected against static discharge due to handling

## **Block Diagram**

FIGURE 1

TL/H/6660-1

© 1995 National Semiconductor Corporation TL/H/6

RRD-B30M115/Printed in U. S. A.

## **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$\begin{array}{ccc} \text{Supply Voltages} & \pm 7\text{V} \\ \text{Power Dissipation} & 1 \text{ W/Package} \\ \text{Input Voltage} & \pm 7\text{V} \end{array}$

Voltage at Any Input

or Output  $V_{CC} + 0.3V$  to  $V_{BBV} - 0.3V$

$\begin{array}{lll} \mbox{Output Short-Circuit Duration} & \mbox{Continuous} \\ \mbox{Operating Temperature Range} & -25^{\circ}\mbox{C to } +125^{\circ}\mbox{C} \\ \mbox{Storage Temperature} & -65^{\circ}\mbox{C to } +150^{\circ}\mbox{C} \\ \mbox{Lead Temperature (Soldering, 10 seconds)} & 300^{\circ}\mbox{C} \end{array}$

ESD Rating to be determined

**DC Electrical Characteristics** Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{CC} = +5.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ ;  $T_A = 0^{\circ}C$  to  $70^{\circ}C$  by correlation with 100% electrical testing at  $T_A = 25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization. Typicals specified at  $V_{CC} = +5.0V$ ,  $V_{BB} = -5.0V$ ,  $T_A = 25^{\circ}C$ . Clock frequency is 2.048 MHz. Digital interface voltages measured with respect to digital ground, GNDD. Analog voltages measured with respect to analog ground, GNDA.

| Symbol             | Parameter                                                    | Conditions                                                                                                               | Min                  | Тур    | Max                   | Units     |

|--------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|--------|-----------------------|-----------|

| POWER DISSIPATION  |                                                              |                                                                                                                          |                      |        |                       |           |

| I <sub>CC0</sub>   | V <sub>CC</sub> Standby Current                              | $V_{\rm CC}=5.25$ V, $V_{\rm BB}=-5.25$ V, CLK0 and PWRI = $-5.25$ V (Note 6) All other pins at GND (0V) TP3040, TP3040A | 50                   |        | 100                   | μΑ        |

| I <sub>BB0</sub>   | V <sub>BB</sub> Standby Current                              | $V_{\rm CC}=5.25$ V, $V_{\rm BB}=-5.25$ V, CLK0 and PWRI = $-5.25$ V (Note 6) All other pins at GND (0V) TP3040, TP3040A |                      | 50 100 |                       | μΑ        |

| I <sub>CC1</sub>   | V <sub>CC</sub> Operating Current                            | PWRI = V <sub>BB</sub> , Power Amp Inactive                                                                              |                      | 3.0    | 4.0                   | mA        |

| I <sub>BB1</sub>   | V <sub>BB</sub> Operating Current                            | PWRI = V <sub>BB</sub> , Power Amp Inactive                                                                              |                      | 3.0    | 4.0                   | mA        |

| I <sub>CC2</sub>   | V <sub>CC</sub> Operating Current                            | (Note 1)                                                                                                                 |                      | 4.6    | 6.4                   | mA        |

| I <sub>BB2</sub>   | V <sub>BB</sub> Operating Current                            | (Note 1)                                                                                                                 |                      | 4.6    | 6.4                   | mA        |

| DIGITAL            | INTERFACE                                                    |                                                                                                                          |                      |        |                       |           |

| I <sub>INC</sub>   | Input Current, CLK                                           | $V_{BB} \le V_{IN} \le V_{CC}$                                                                                           | -10                  |        | 10                    | μΑ        |

| I <sub>INP</sub>   | Input Current, PDN                                           | $V_{BB} \le V_{IN} \le V_{CC}$                                                                                           | -100                 |        |                       | μΑ        |

| I <sub>IN0</sub>   | Input Current, CLK0                                          | $V_{BB} \le V_{IN} \le V_{CC} - 0.5V$                                                                                    | -10                  |        | -0.1                  | μΑ        |

| $V_{IL}$           | Input Low Voltage, CLK, PDN                                  |                                                                                                                          | 0                    |        | 0.8                   | V         |

| $V_{IH}$           | Input High Voltage, CLK, PDN                                 |                                                                                                                          | 2.2                  |        | V <sub>CC</sub>       | V         |

| $V_{IL0}$          | Input Low Voltage, CLK0                                      |                                                                                                                          | V <sub>BB</sub>      |        | V <sub>BB</sub> + 0.5 | V         |

| V <sub>IIO</sub>   | Input Intermediate Voltage, CLK0                             |                                                                                                                          | -0.8                 |        | 0.8                   | V         |

| V <sub>IH0</sub>   | Input High Voltage, CLK0                                     |                                                                                                                          | V <sub>CC</sub> -0.5 |        | V <sub>CC</sub>       | V         |

| TRANSM             | IT INPUT OP AMP                                              |                                                                                                                          |                      |        |                       |           |

| $IB_xI$            | Input Leakage Current, VF <sub>x</sub> I                     | $-3.2V \leq V_{IN} \leq +3.2V$                                                                                           | -100                 |        | 100                   | nA        |

| RI <sub>x</sub> I  | Input Resistance, VF <sub>x</sub> I                          | $V_{BB} \le VF_xI \le V_{CC}$                                                                                            | 10                   |        |                       | $M\Omega$ |

| VOS <sub>x</sub> I | Input Offset Voltage, VF <sub>x</sub> I                      | $-2.5V \le V_{IN} \le +2.5V$                                                                                             | -20                  |        | 20                    | mV        |

| V <sub>CM</sub>    | Common-Mode Range, VF <sub>x</sub> I                         |                                                                                                                          | - 2.5                |        | 2.5                   | V         |

| CMRR               | Common-Mode Rejection Ratio                                  | $-2.5V \leq V_{IN} \leq 2.5V$                                                                                            | 60                   |        |                       | dB        |

| PSRR               | Power Supply Rejection of V <sub>CC</sub> or V <sub>BB</sub> |                                                                                                                          | 60                   |        |                       | dB        |

| R <sub>OL</sub>    | Open Loop Output Resistance, GS <sub>x</sub>                 |                                                                                                                          |                      | 1      |                       | kΩ        |

| $R_{L}$            | Minimum Load Resistance, GS <sub>x</sub>                     |                                                                                                                          | 10                   |        |                       | kΩ        |

| $C_L$              | Maximum Load Capacitance, GS <sub>x</sub>                    |                                                                                                                          |                      |        | 100                   | pF        |

| VO <sub>x</sub> I  | Output Voltage Swing, GS <sub>x</sub>                        | R <sub>L</sub> ≥ 10k                                                                                                     | ± 2.5                |        |                       | V         |

| A <sub>VOL</sub>   | Open Loop Voltage Gain, GS <sub>x</sub>                      | R <sub>L</sub> ≥ 10k                                                                                                     | 5,000                |        |                       | V/V       |

| F <sub>c</sub>     | Open Loop Unity Gain Bandwidth, GS <sub>x</sub>              |                                                                                                                          |                      | 2      |                       | MHz       |

## **AC Electrical Characteristics**

Unless otherwise specified,  $T_A = 25^{\circ}C$ . All parameters are specified for a signal level of 0 dBm0 at 1 kHz. The 0 dBm0 level is assumed to be 1.54 Vrms measured at the output of the transmit or receive filter. Limits printed in **BOLD** characters are guaranteed for  $V_{CC} = +5.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ ;  $T_A = 0^{\circ}C$  to 70°C by correlation with 100% electrical testing at  $T_A = 25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization. Typicals specified at  $V_{CC} = +5.0V$ ,  $V_{BB} = -5.0V$ ,  $T_{A} = 25^{\circ}C$ .

| Symbol                                                                                                                                              | Parameter                                                                 | Conditions                                                                                                                                            | Min                                                     | Тур        | Max                                                                           | Units                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------|-------------------------------------------------------------------------------|----------------------------------------------|

| TRANSMIT FILTER (Transmit filter input op amp set to the non-inverting unity gain mode, with VF <sub>x</sub> I = 1.09 Vrms unless otherwise noted.) |                                                                           |                                                                                                                                                       |                                                         |            |                                                                               |                                              |

| RL <sub>x</sub>                                                                                                                                     | Minimum Load Resistance, VF <sub>x</sub> O                                | -2.5V < V <sub>OUT</sub> < 2.5V<br>-3.2V < V <sub>OUT</sub> < 3.2V                                                                                    | 3<br>10                                                 |            |                                                                               | kΩ<br>kΩ                                     |

| CL <sub>x</sub>                                                                                                                                     | Load Capacitance, VF <sub>x</sub> O                                       |                                                                                                                                                       |                                                         |            | 100                                                                           | pF                                           |

| RO <sub>x</sub>                                                                                                                                     | Output Resistance, VF <sub>x</sub> O                                      |                                                                                                                                                       |                                                         | 1          | 3                                                                             | Ω                                            |

| PSRR1                                                                                                                                               | V <sub>CC</sub> Power Supply Rejection, VF <sub>x</sub> O                 | $f=1 \text{ kHz}, VF_XI+=0 \text{ Vrms}$                                                                                                              | 30                                                      |            |                                                                               | dB                                           |

| PSRR2                                                                                                                                               | V <sub>BB</sub> Power Supply Rejection, VF <sub>x</sub> O                 | Same as Above                                                                                                                                         | 35                                                      |            |                                                                               | dB                                           |

| GA <sub>x</sub>                                                                                                                                     | Absolute Gain                                                             | f = 1 kHz (TP3040A)<br>f = 1 kHz (TP3040)                                                                                                             | 2.9<br>2.875                                            | 3.0<br>3.0 | 3.1<br>3.125                                                                  | d<br>d<br>d                                  |

| GR <sub>x</sub>                                                                                                                                     | Gain Relative to GA <sub>x</sub>                                          | Below 50 Hz 50 Hz 60 Hz 200 Hz (TP3040A) 200 Hz (TP3040) 300 Hz to 3 kHz (TP3040A) 300 Hz to 3 kHz (TP3040) 3.3 kHz 3.4 kHz 4.0 kHz 4.6 kHz and Above | - 1.5<br>- 1.5<br>- 0.125<br>- 0.15<br>- 0.35<br>- 0.70 | -41<br>-35 | -35<br>-35<br>-30<br>0<br>0.05<br>0.125<br>0.15<br>0.03<br>-0.1<br>-14<br>-32 | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| $DA_{x}$                                                                                                                                            | Absolute Delay at 1 kHz                                                   |                                                                                                                                                       |                                                         |            | 250                                                                           | μs                                           |

| DD <sub>x</sub>                                                                                                                                     | Differential Envelope Delay from 1 kHz to 2.6 kHz                         |                                                                                                                                                       |                                                         |            | 60                                                                            | μs                                           |

| DP <sub>x</sub> 1                                                                                                                                   | Single Frequency Distortion<br>Products                                   |                                                                                                                                                       |                                                         |            | <b>-48</b>                                                                    | dB                                           |

| DP <sub>x</sub> 2                                                                                                                                   | Distortion at Maximum Signal<br>Level                                     | 0.16 Vrms, 1 kHz Signal Applied to VF <sub>x</sub> I+, Gain=20 dB, R <sub>L</sub> =10k                                                                |                                                         |            | -45                                                                           | dB                                           |

| NC <sub>x</sub> 1                                                                                                                                   | Total C Message Noise at VF <sub>x</sub> O                                | TP3040, TP3040A                                                                                                                                       |                                                         | 2          | 5                                                                             | dBrnc0                                       |

| NC <sub>x</sub> 2                                                                                                                                   | Total C Message Noise at VF <sub>x</sub> O                                | Gain Setting Op Amp at 20 dB,<br>Non-Inverting (Note 3)<br>T <sub>A</sub> = 0°C to 70°C<br>TP3040, TP3040A                                            |                                                         | 3          | 6                                                                             | dBrnc0                                       |

| GA <sub>x</sub> T                                                                                                                                   | Temperature Coefficient of 1 kHz Gain                                     |                                                                                                                                                       |                                                         | 0.0004     |                                                                               | dB/°C                                        |

| GA <sub>x</sub> S                                                                                                                                   | Supply Voltage Coefficient of 1 kHz Gain                                  | $V_{CC} = 5.0V \pm 5\%$<br>$V_{BB} = -5.0V \pm 5\%$                                                                                                   |                                                         | 0.01       |                                                                               | dB/V                                         |

| CT <sub>RX</sub>                                                                                                                                    | Crosstalk, Receive to Transmit 20 log VF <sub>x</sub> O/VF <sub>R</sub> O | Receive Filter Output = 2.2 Vrms $VF_XI + = 0$ Vrms, f = 0.2 kHz to 3.4 kHz Measure $VF_XO$                                                           |                                                         |            | <b>-70</b>                                                                    | dB                                           |

| GR <sub>x</sub> L                                                                                                                                   | Gaintracking Relative to GA <sub>x</sub>                                  | Output Level = +3 dBm0<br>+2 dBm0 to -40 dBm0<br>-40 dBm0 to -55 dBm0                                                                                 | -0.1<br>-0.05<br>-0.1                                   |            | 0.1<br>0.05<br>0.1                                                            | dB<br>dB<br>dB                               |

## **AC Electrical Characteristics** (Continued)

Unless otherwise specified,  $T_A = 25^{\circ}C$ . All parameters are specified for a signal level of 0 dBm0 at 1 kHz. The 0 dBm0 level is assumed to be 1.54 Vrms measured at the output of the transmit or receive filter. Limits printed in **BOLD** characters are guaranteed for  $V_{CC} = +5.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ ;  $T_A = 0^{\circ}C$  to  $70^{\circ}C$  by correlation with 100% electrical testing at  $T_A = 25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization. Typicals specified at  $V_{CC} = +5.0V$ ,  $V_{BB} = -5.0V$ ,  $T_A = 25^{\circ}C$ .

| Symbol                                                                                                                               | Parameter                                                                 | Conditions                                                                                                                                      | Min                              | Тур    | Max                                                  | Units                            |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------|------------------------------------------------------|----------------------------------|

| RECEIVE FILTER (Unless otherwise noted, the receive filter is preceded by a sin x/x filter with an input signal level of 1.54 Vrms.) |                                                                           |                                                                                                                                                 |                                  |        |                                                      |                                  |

| IB <sub>R</sub>                                                                                                                      | Input Leakage Current, VF <sub>R</sub> I                                  | -3.2V≤V <sub>IN</sub> ≤3.2V                                                                                                                     | -100                             |        | 100                                                  | nA                               |

| RIR                                                                                                                                  | Input Resistance, VF <sub>R</sub> I                                       |                                                                                                                                                 | 10                               |        |                                                      | МΩ                               |

| ROR                                                                                                                                  | Output Resistance, VF <sub>R</sub> O                                      |                                                                                                                                                 |                                  | 1      | 3                                                    | Ω                                |

| CLR                                                                                                                                  | Load Capacitance, VF <sub>R</sub> O                                       |                                                                                                                                                 |                                  |        | 100                                                  | pF                               |

| RLR                                                                                                                                  | Load Resistance, VF <sub>R</sub> O                                        |                                                                                                                                                 | 10                               |        |                                                      | kΩ                               |

| PSRR3                                                                                                                                | Power Supply Rejection of $V_{CC}$ or $V_{BB}$ , $V_{FR}$ O               | VF <sub>R</sub> I Connected to GNDA<br>f=1 kHz                                                                                                  | 35                               |        |                                                      | dB                               |

| VOSRO                                                                                                                                | Output DC Offset, VF <sub>R</sub> O                                       | VF <sub>R</sub> I Connected to GNDA                                                                                                             | -200                             |        | 200                                                  | mV                               |

| GAR                                                                                                                                  | Absolute Gain                                                             | f=1 kHz (TP3040A)<br>f=1 kHz (TP3040)                                                                                                           | −0.1<br>−0.125                   | 0<br>0 | 0.1<br>0.125                                         | dB<br>dB                         |

| GR <sub>R</sub>                                                                                                                      | Gain Relative to Gain at 1 kHz                                            | Below 300 Hz<br>300 Hz to 3.0 kHz (TP3040A)<br>300 Hz to 3.0 kHz (TP3040)<br>3.3 kHz<br>3.4 kHz<br>4.0 kHz<br>4.6 kHz and Above                 | -0.125<br>-0.15<br>-0.35<br>-0.7 |        | 0.125<br>0.125<br>0.15<br>0.03<br>-0.1<br>-14<br>-32 | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| DA <sub>R</sub>                                                                                                                      | Absolute Delay at 1 kHz                                                   |                                                                                                                                                 |                                  |        | 140                                                  | μs                               |

| DD <sub>R</sub>                                                                                                                      | Differential Envelope Delay 1 kHz<br>to 2.6 kHz                           |                                                                                                                                                 |                                  |        | 100                                                  | μs                               |

| DP <sub>R</sub> 1                                                                                                                    | Single Frequency Distortion<br>Products                                   | f=1 kHz                                                                                                                                         |                                  |        | <b>-48</b>                                           | dB                               |

| DP <sub>R</sub> 2                                                                                                                    | Distortion at Maximum Signal<br>Level                                     | 2.2 Vrms Input to Sin x/x Filter,<br>f=1 kHz, R <sub>L</sub> =10k                                                                               |                                  |        | -45                                                  | dB                               |

| NCR                                                                                                                                  | Total C-Message Noise at VF <sub>R</sub> O                                | TP3040, TP3040A                                                                                                                                 |                                  | 3      | 5                                                    | dBrnc0                           |

| GA <sub>R</sub> T                                                                                                                    | Temperature Coefficient of 1 kHz<br>Gain                                  |                                                                                                                                                 |                                  | 0.0004 |                                                      | dB/°C                            |

| GA <sub>R</sub> S                                                                                                                    | Supply Voltage Coefficient of 1 kHz Gain                                  |                                                                                                                                                 |                                  | 0.01   |                                                      | dB/V                             |

| CT <sub>XR</sub>                                                                                                                     | Crosstalk, Transmit to Receive 20 log VF <sub>R</sub> O VF <sub>x</sub> O | $\label{eq:TransmitFilter Output} Transmit Filter Output = 2.2 \ Vrms \\ VF_RI = 0 \ Vrms, \ f = 0.3 \ kHz \ to \ 3.4 \ kHz \\ Measure \ VF_RO$ |                                  |        | <b>-70</b>                                           | dB                               |

| GR <sub>R</sub> L                                                                                                                    | Gaintracking Relative to GA <sub>R</sub>                                  | Output Level = +3 dBm0<br>+2 dBm0 to -40 dBm0<br>-40 dBm0 to -55 dBm0<br>(Note 5)                                                               | -0.1<br>-0.05<br>-0.1            |        | 0.1<br>0.05<br>0.1                                   | dB<br>dB<br>dB                   |

### **AC Electrical Characteristics** (Continued)

Unless otherwise specified,  $T_A = 25^{\circ}$ C. All parameters are specified for a signal level of 0 dBm0 at 1 kHz. The 0 dBm0 level is assumed to be 1.54 Vrms measured at the output of the transmit or receive filter. Limits printed in BOLD characters are guaranteed for  $V_{CC} = +5.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ ;  $V_{AB} = -5.0V \pm 5\%$ ;  $V_{AB$ specified at  $V_{CC} = +5.0V$ ,  $V_{BB} = -5.0V$ ,  $T_A = 25$ °C.

| Symbol                                 | Parameter                                                              | Conditions                                                                                                                                                                                                          | Min                  | Тур     | Max                | Units      |

|----------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|--------------------|------------|

| RECEIVE OUTPUT POWER AMPLIFIER         |                                                                        |                                                                                                                                                                                                                     |                      |         |                    |            |

| IBP                                    | Input Leakage Current, PWRI                                            | $-3.2V \le V_{IN} \le 3.2V$                                                                                                                                                                                         | 0.1                  |         | 3                  | μΑ         |

| RIP                                    | Input Resistance, PWRI                                                 |                                                                                                                                                                                                                     | 10                   |         |                    | $M\Omega$  |

| ROP1                                   | Output Resistance, PWRO+, PWRO-                                        | Amplifiers Active                                                                                                                                                                                                   |                      | 1       |                    | Ω          |

| CLP                                    | Load Capacitance, PWRO+, PWRO-                                         |                                                                                                                                                                                                                     |                      |         | 500                | pF         |

| GA <sub>p</sub> +<br>GA <sub>p</sub> - | Gain, PWRI to PWRO + Gain, PWRI to PWRO -                              | $R_L = 600\Omega$ Connected Between PWRO+ and PWRO-, Input Level = 0 dBm0 (Note 4)                                                                                                                                  |                      | 1<br>-1 |                    | V/V<br>V/V |

| GR <sub>p</sub> L                      | Gaintracking Relative to 0 dBm0 Output Level, Including Receive Filter | $ \begin{array}{c} \text{V=}2.05\text{Vrms},\text{R}_{\text{L}}\!=\!600\Omega}\\ \text{V=}1.75\text{Vrms},\text{R}_{\text{L}}\!=\!300\Omega} \end{array} \text{(Notes 4, 5)} $                                      | - <b>0.1</b><br>-0.1 |         | <b>0.1</b> 0.1     | dB<br>dB   |

| S/D <sub>p</sub>                       | Signal/Distortion                                                      | $\begin{array}{c} \text{V=}\text{2.05 Vrms, R}_{\text{L}}\!=\!600\Omega \\ \text{V=}\text{1.75 Vrms, R}_{\text{L}}\!=\!300\Omega \end{array}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |                      |         | - <b>45</b><br>-45 | dB<br>dB   |

| VOSP                                   | Output DC Offset, PWRO+, PWRO-                                         | PWRI Connected to GNDA                                                                                                                                                                                              | -50                  |         | 50                 | mV         |

| PSRR5                                  | Power Supply Rejection of V <sub>CC</sub> or V <sub>BB</sub>           | PWRI Connected to GNDA                                                                                                                                                                                              | 45                   |         |                    | dB         |

Note 1: Maximum power consumption will depend on the load impedance connected to the power amplifier. This specification listed assumes 0 dBm is delivered to  $600\Omega$  connected from PWRO+ to PWRO-

$\textbf{Note 2:} \ \ \text{Voltage input to receive filter at 0V, VF}_{R}O \ \ \text{connected to PWRI, } \ 600\Omega \ \ \text{from PWRO+ to PWRO-}. \ \ \text{Output measured from PWRO+ to PWRO-}.$

Note 3: The 0 dBm0 level for the filter is assumed to be 1.54 Vrms measured at the output of the XMT or RCV filter.

Note 4: The 0 dBm0 level for the power amplifiers is load dependent. For R<sub>I</sub> = 600 $\Omega$  to GNDA, the 0 dBm0 level is 1.43 Vrms measured at the amplifier output. For  $R_L = 300\Omega$  the 0 dBm0 level is 1.22 Vrms.

Note 5: VFRO connected to PWRI, input signal applied to VFRI.

Note 6: Previous revisions of the datasheet did not clearly indicate this specification requires power amps in powerdown (PWRI = -5.25V).

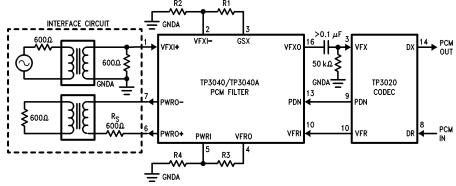

## **Typical Application**

TL/H/6660-2

Note 1: Transmit voltage gain  $=\frac{R1+R2}{R2} \times \sqrt{2}$  (The filter itself introduces a 3 dB gain), (R1 +R2  $\geq$ 10k)

Note 2: Receive gain =

$$\frac{R4}{R3 + R4}$$

(R3 +R4≥10k)

Note: In the configuration shown, the receive filter power amplifiers will drive a  $600\Omega$  T to R termination to a maximum signal level of 8.5 dBm. An alternative arrangement, using a transformer winding ratio equivalent to 1.414:1 and  $300\Omega$  resistor,  $R_S$ , will provide a maximum signal level of 10.1 dBm across a  $600\Omega$ termination impedance.

FIGURE 2

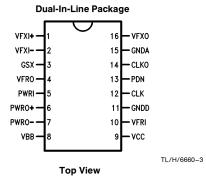

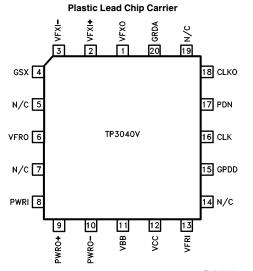

# **Connection Diagrams**

Order Number TP3040J or TP3040AJ See NS Package J16A or TP3040N or TP3040AN See NS Package N16A

TL/H/6660-4

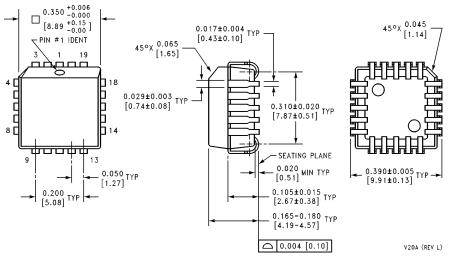

Order Number TP3040V or TP3040AV See NS Package V20A

## **Description of Pin Functions**

| Symbol            | Function                                                                                                   | Symbol            | Function                                                                                                                            |                  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|

| $VF_xI +$         | The non-inverting input to the transmit filter stage.                                                      | GNDD              | Digital ground input pin. All digital signals are referenced to this pin.                                                           |                  |  |  |  |

| $VF_xI-$          | The inverting input to the transmit filter stage.                                                          | CLK               | Master input clock. Input frequency can be s                                                                                        |                  |  |  |  |

| $GS_x$            | The output used for gain adjustments of the                                                                | PDN               | lected as 2.048 MHz, 1.544 MHz or 1.536 MHz.                                                                                        |                  |  |  |  |

|                   | transmit filter.                                                                                           |                   | The input pin used to power down the TP3040/                                                                                        |                  |  |  |  |

| VF <sub>R</sub> O | The low power receive filter output. This pin can directly drive the receive port of an electronic hybrid. |                   | TP3040A during idle periods. Logic 1 ( $V_{\rm CC}$ ) input voltage causes a power down condition. An internal pull-up is provided. |                  |  |  |  |

| PWRI              | The input to the receive filter differential power amplifier.                                              | CLK0              | This input pin selects internal counters in accordance with the CLK input clock frequency:                                          |                  |  |  |  |

| PWRO+             | The non-inverting output of the receive filter pow-                                                        |                   | CLK                                                                                                                                 | Connect CLK0 to: |  |  |  |

|                   | er amplifier. This output can directly interface                                                           |                   | 2048 kHz                                                                                                                            | $V_{CC}$         |  |  |  |

|                   | conventional transformer hybrids.                                                                          |                   | 1544 kHz                                                                                                                            | GNDD             |  |  |  |

| PWRO-             | The inverting output of the receive filter power                                                           |                   | 1536 kHz                                                                                                                            | $V_{BB}$         |  |  |  |

|                   | amplifier. This output can be used with PWRO+                                                              |                   | An internal pull-up is provided.                                                                                                    |                  |  |  |  |

|                   | to differentially drive a transformer hybrid.                                                              | GNDA              | Analog ground input pin. All analog signals                                                                                         |                  |  |  |  |

| $V_{BB}$          | The negative power supply pin. Recommended input is $-5$ V.                                                |                   | referenced to this pin. Not internally connected to GNDD.                                                                           |                  |  |  |  |

| V <sub>CC</sub>   | The positive power supply pin. The recommended input is 5V.                                                | VF <sub>x</sub> O | The output of the transmit filter stage.                                                                                            |                  |  |  |  |

| $VF_RI$           | The input pin for the receive filter stage.                                                                |                   |                                                                                                                                     |                  |  |  |  |

|                   |                                                                                                            |                   |                                                                                                                                     |                  |  |  |  |

## **Functional Description**

The TP3040/TP3040A monolithic filter contains four main sections; Transmit Filter, Receive Filter, Receive Filter Power Amplifier, and Frequency Divider/Select Logic (*Figure 1*). A brief description of the circuit operation for each section is provided below.

#### TRANSMIT FILTER

The input stage of the transmit filter is a CMOS operational amplifier which provides an input resistance of greater than 10 M $\Omega$ , a voltage gain of greater than 5,000, low power consumption (less than 3 mW), high power supply rejection, and is capable of driving a 10 k $\Omega$  load in parallel with up to 25 pF. The inputs and output of the amplifier are accessible for added flexibility. Non-inverting mode, inverting mode, or differential amplifier mode operation can be implemented with external resistors. It can also be connected to provide a gain of up to 20 dB without degrading the overall filter performance.

The input stage is followed by a prefilter which is a two-pole RC active low pass filter designed to attenuate high frequency noise before the input signal enters the switched-capacitor high pass and low pass filters.

A high pass filter is provided to reject 200 Hz or lower noise which may exist in the signal path. The low pass portion of the switched-capacitor filter provides stopband attenuation which exceeds the D3 and D4 specifications as well as the CCITT G712 recommendations (Figure 3).

The output stage of the transmit filter, the postfilter, is also a two-pole RC active low pass filter which attenuates clock frequency noise by at least 40 dB. The output of the transmit filter is capable of driving a  $\pm 3.2 V$  peak to peak signal into a 10  $k\Omega$  load in parallel with up to 25 pF.

#### **RECEIVE FILTER**

The input stage of the receive filter is a prefilter which is similar to the transmit prefilter. The prefilter attenuates high frequency noise that may be present on the receive input signal. A switched capacitor low pass filter follows the prefilter to provide the necessary passband flatness, stopband rejection and sin x/x gain correction. A postfilter which is similar to the transmit postfilter follows the low pass stage. It attenuates clock frequency noise and provides a low output impedance capable of directly driving an electronic subscriber-line-interface circuit (Figure 3).

### RECEIVE FILTER POWER AMPLIFIERS

Two power amplifiers are also provided to interface to transformer coupled line circuits. These two amplifiers are driven by the output of the receive postfilter through gain setting resistors, R3, R4 (*Figure 2*). The power amplifiers can be deactivated, when not required, by connecting the power amplifier input (pin 5) to the negative power supply VBB. This reduces the total filter power consumption by approximately 10 mW–20 mW depending on output signal amplitude

#### POWER DOWN CONTROL

A power down mode is also provided. A logic 1 power down command applied on the PDN pin (pin 13) will reduce the total filter power consumption to less than 1 mW. Connect PDN to GNDD for normal operation.

#### FREQUENCY DIVIDER AND SELECT LOGIC CIRCUIT

This circuit divides the external clock frequency down to the switching frequency of the low pass and high pass switched capacitor filters. The divider also contains a TTL-CMOS interface circuit which converts the external TTL clock level to the CMOS logic level required for the divider logic. This interface circuit can also be directly driven by CMOS logic. A frequency select circuit is provided to allow the filter to operate with 2.048 MHz, 1.544 MHz or 1.536 MHz clock frequencies. By connecting the frequency select pin CLKO (pin 14) to V<sub>CC</sub>, a 2.048 MHz clock input frequency is selected. Digital ground selects 1.544 MHz and V<sub>BB</sub> selects 1.536 MHz.

## **Applications Information**

#### **GAIN ADJUST**

Figure 2 shows the signal path interconnections between the TP3040/TP3040A and the TP3020 signal-channel CO-DEC. The transmit RC coupling components have been chosen both for minimum passband droop and to present the correct impedance to the CODEC during sampling.

Optimum noise and distortion performance will be obtained from the TP3040/TP3040A filter when operated with system peak overload voltages of  $\pm 2.5 V$  to  $\pm 3.2 V$  at VF $_{\chi}O$  and VF $_{R}O$ . When interfacing to a PCM CODEC with a peak overload voltage outside this range, further gain or attenuation may be required.

#### **BOARD LAYOUT**

Care must be taken in PCB layout to minimize power supply and ground noise. Analog ground (GNDA) of each filter should be connected to digital ground (GNDD) at a single point, which should be bypassed to both power supplies. Further power supply decoupling adjacent to each filter and CODEC is recommended. Ground loops should be avoided, both between GNDA and GNDD and between the GNDA traces of adjacent filters and CODECs.

# **Typical Performance Characteristics**

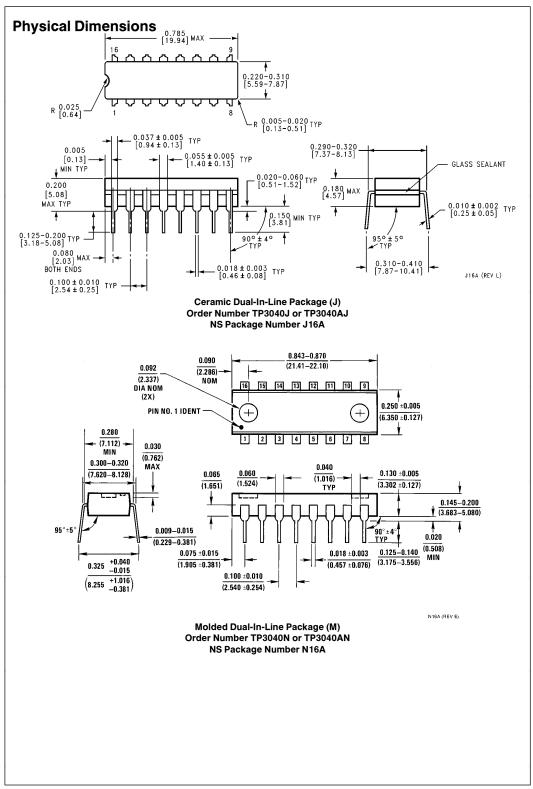

# Physical Dimensions (Continued)

Lit. # 113919

20-Lead Plastic Chip Carrier Order Number TP3040V or TP3040AV NS Package Number V20A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86

Email: cnjwge@tevm2.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85

English Tel: (+49) 0-180-532 78 32

Français Tel: (+49) 0-180-532 93 58

Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9860 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications