#

# PALC22V10D

# Flash Erasable, Reprogrammable CMOS PAL® Device

#### Features

- Advanced second-generation PAL architecture

- Low power

- 90 mA max. commercial (10 ns)

- -130 mA max. commercial (7.5 ns)

- CMOS Flash EPROM technology for electrical erasability and reprogrammability

- Variable product terms

- -2 x(8 through 16) product terms

- User-programmable macrocell

- -Output polarity control

- Individually selectable for registered or combinatorial operation

- Up to 22 input terms and 10 outputs

- DIP, LCC, and PLCC available

- -7.5 ns commercial version

- 5 ns t<sub>CO</sub>

- 5 ns t<sub>S</sub>

- 7.5 ns t<sub>PD</sub>

- 133-MHz state machine

- 10 ns military and industrial versions

6 ns t<sub>CO</sub>

- 6 ns t<sub>S</sub>

- 10 ns t<sub>PD</sub>

- 110-MHz state machine

- 15-ns commercial and military versions

- 25-ns commercial and military versions

- High reliability

- Proven Flash EPROM technology

#### 100% programming and functional testing

#### **Functional Description**

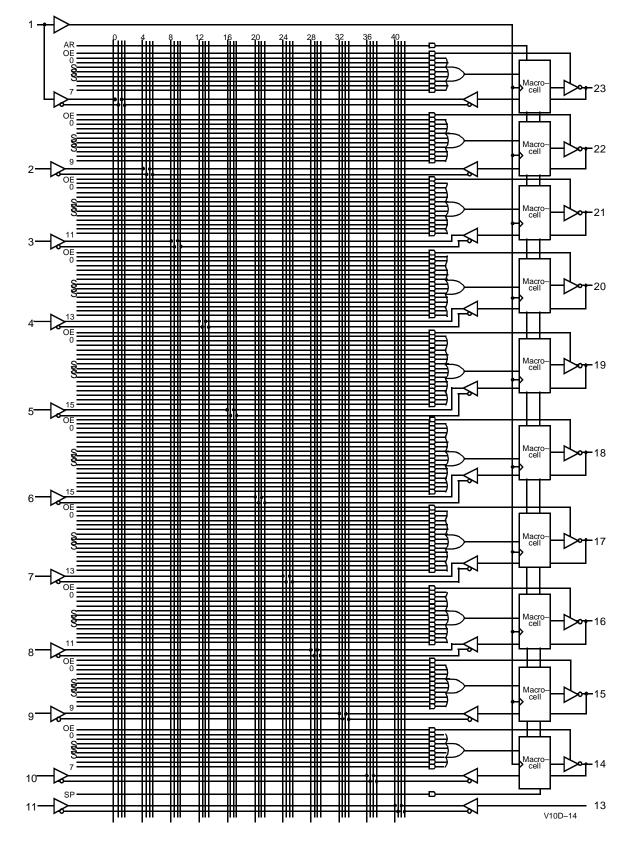

The Cypress PALC22V10D is a CMOS Flash Erasable second-generation programmable array logic device. It is implemented with the familiar sum-of-products (AND-OR) logic structure and the programmable macrocell.

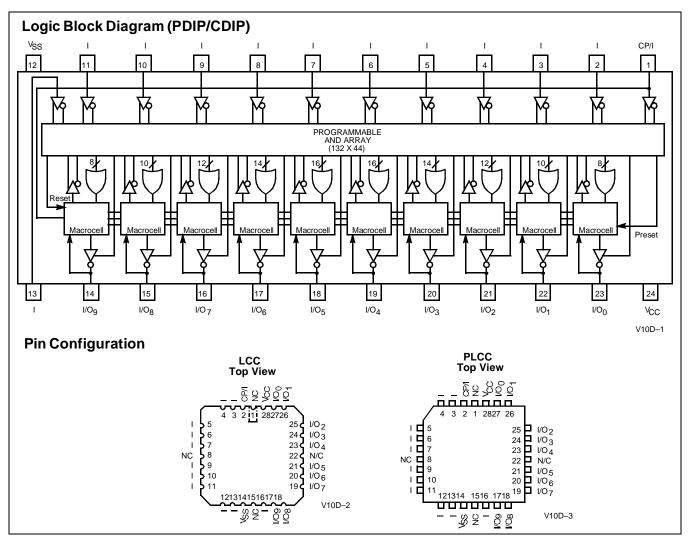

The PALC22V10D is executed in a 24-pin 300-mil molded DIP, a 300-mil cerDIP, a 28-lead square ceramic leadless chip carrier, a 28-lead square plastic leaded chip carrier, and provides up to 22 inputs and 10 outputs. The 22V10D can be electrically erased and reprogrammed. The programmable macrocell provides the capability of defining the architecture of each output individually. Each of the 10 potential outputs may be specified as "registered" or "combinatorial." Polarity of each output may also be individually selected, allowing complete flexibility of output configuration. Further configurability is provided through "array" configurable "output enable" for each potential output. This feature allows the 10 outputs to be reconfigured as inputs on an individual basis, or alternately used as a combination I/O controlled by the programmable array.

PALC22V10D features a variable product term architecture. There are 5 pairs of product term sums beginning at 8 product terms per output and incrementing by 2 to 16 product terms per output. By providing this variable structure, the PAL C 22V10D is optimized to the configurations found in a majority of applications without creating devices that burden the product term structures with unusable product terms and lower performance.

Additional features of the Cypress PALC22V10D include a synchronous preset and an asynchronous reset product term. These product terms are common to all macrocells, eliminating the need to dedicate standard product terms for initialization functions. The device automatically resets upon power-up.

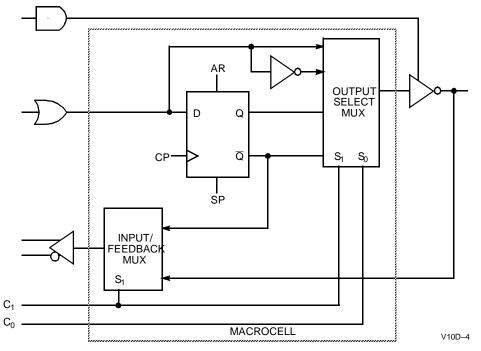

The PALC22V10D, featuring programmable macrocells and variable product terms, provides a device with the flexibility to implement logic functions in the 500- to 800-gate-array complexity. Since each of the 10 output pins may be individually configured as inputs on a temporary or permanent basis, functions requiring up to 21 inputs and only a single output and down to 12 inputs and 10 outputs are possible. The 10 potential outputs are enabled using product terms. Any output pin may be permanently selected as an output or arbitrarily enabled as an output and an input through the selective use of individual product terms associated with each output. Each of these outputs is achieved through an individual programmable macrocell. These macrocells are programmable to provide a combinatorial or registered inverting or non-inverting output. In a registered mode of operation, the output of the register is fed back into the array, providing current status information to the array. This information is available for establishing the next result in applications such as control state machines. In a combinatorial configuration, the combinatorial output or, if the output is disabled, the signal present on the I/O pin is made available to the array. The flexibility provided by both programmable product term control of the outputs and variable product terms allows a significant gain in functional density through the use of programmable logic.

Along with this increase in functional density, the Cypress PALC22V10D provides lower-power operation through the use of CMOS technology, and increased testability with Flash reprogrammability.

PAL is a registered trademark of Advanced Micro Devices

#### **Configuration Table**

| Registered/Combinatorial                    |   |                        |  |  |  |

|---------------------------------------------|---|------------------------|--|--|--|

| C <sub>1</sub> C <sub>0</sub> Configuration |   |                        |  |  |  |

| 0                                           | 0 | Registered/Active LOW  |  |  |  |

| 0                                           | 1 | Registered/Active HIGH |  |  |  |

#### **Configuration Table**

|                                             | Registered/Combinatorial |                           |  |  |  |

|---------------------------------------------|--------------------------|---------------------------|--|--|--|

| C <sub>1</sub> C <sub>0</sub> Configuration |                          |                           |  |  |  |

| 1                                           | 0                        | Combinatorial/Active LOW  |  |  |  |

| 1                                           | 1                        | Combinatorial/Active HIGH |  |  |  |

# Macrocell

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                                   | –65°C to +150°C |

|-------------------------------------------------------|-----------------|

| Ambient Temperature with<br>Power Applied             | –55°C to +125°C |

| Supply Voltage to Ground Potential (Pin 24 to Pin 12) | –0.5V to +7.0V  |

| DC Voltage Applied to Outputs<br>in High Z State      | –0.5V to +7.0V  |

| DC Input Voltage                                      | 0.5V to +7.0V   |

| Output Current into Outputs (LOW)                     | 16 mA           |

| DC Programming Voltage                                | 12.5V           |

Latch-Up Current.....>200 mA Static Discharge Voltage (per MIL-STD-883, Method 3015) .....>2001V

#### **Operating Range**

| Range                   | Ambient<br>Temperature | V <sub>CC</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +75°C           | 5V ±5%          |

| Military <sup>[1]</sup> | –55°C to +125°C        | 5V ±10%         |

| Industrial              | –40°C to +85°C         | 5V ±10%         |

Note:

1.  $T_A$  is the "instant on" case temperature.

# Electrical Characteristics Over the Operating Range<sup>[2]</sup>

| Parameter           | Description                  | 1                                              | Min.                                                               | Max.                             | Unit |     |    |

|---------------------|------------------------------|------------------------------------------------|--------------------------------------------------------------------|----------------------------------|------|-----|----|

| V <sub>OH</sub>     | Output HIGH Voltage          | V <sub>CC</sub> = Min.,                        | I <sub>OH</sub> = -3.2 mA                                          | Com'l                            | 2.4  |     | V  |

|                     |                              | $V_{IN} = V_{IH} \text{ or } V_{IL}$           | I <sub>OH</sub> = -2 mA                                            | Mil/Ind                          |      |     |    |

| V <sub>OL</sub>     | Output LOW Voltage           | V <sub>CC</sub> = Min.,                        | I <sub>OL</sub> = 16 mA                                            | Com'l                            |      | 0.5 | V  |

|                     |                              | $V_{IN} = V_{IH} \text{ or } V_{IL}$           | I <sub>OL</sub> = 12 mA                                            | Mil/Ind                          |      |     |    |

| V <sub>IH</sub>     | Input HIGH Level             | Guaranteed Input L                             | ogical HIGH Volta                                                  | ge for All Inputs <sup>[3]</sup> | 2.0  |     | V  |

| V <sub>IL</sub> [2] | Input LOW Level              | Guaranteed Input Lo                            | Guaranteed Input Logical LOW Voltage for All Inputs <sup>[3]</sup> |                                  |      |     | V  |

| I <sub>IX</sub>     | Input Leakage Current        | $V_{SS} \leq V_{IN} \leq V_{CC}, V_{CC}$       | $V_{SS} \le V_{IN} \le V_{CC}, V_{CC} = Max.$                      |                                  |      | 10  | μΑ |

| I <sub>OZ</sub>     | Output Leakage Current       | $V_{CC} = Max., V_{SS} \le V_{OUT} \le V_{CC}$ |                                                                    |                                  | -40  | 40  | μΑ |

| I <sub>SC</sub>     | Output Short Circuit Current | V <sub>CC</sub> = Max., V <sub>OUT</sub> =     | = 0.5V <sup>[5,6]</sup>                                            |                                  | -30  | -90 | mA |

#### Electrical Characteristics Over the Operating Range<sup>[2]</sup>

| Parameter            | Description                        | Т                                                                                                             | Min.          | Max.    | Unit |     |    |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------|---------|------|-----|----|

| I <sub>CC1</sub>     | Standby Power Supply               | V <sub>CC</sub> = Max.,                                                                                       | 10, 15, 25 ns | Com'l   |      | 90  | mA |

|                      | Current                            | Outputs Open in<br>Unprogrammed De-                                                                           | 7.5 ns        | Com'l   |      | 130 | mA |

|                      |                                    |                                                                                                               | 15, 25 ns     | Mil/Ind |      | 120 | mA |

|                      | vice                               | 10 ns                                                                                                         | Mil/Ind       |         | 120  | mA  |    |

| I <sub>CC2</sub> [6] | Operating Power Supply             |                                                                                                               | 10, 15, 25 ns | Com'l   |      | 110 | mA |

|                      | Current                            | V <sub>CC</sub> = Max., V <sub>IL</sub> =<br>0V, V <sub>IH</sub> = 3V,<br>Output Open, De-<br>vice Programmed | 7.5 ns        | Com'l   |      | 140 | mA |

|                      |                                    |                                                                                                               | 15, 25 ns     | Mil/Ind |      | 130 | mA |

| as a 1<br>f = 25     | as a 10-Bit Counter,<br>f = 25 MHz | 10 ns                                                                                                         | Mil/Ind       |         | 130  | mA  |    |

Notes:

2

See the last page of this specification for Group A subgroup testing information. These are absolute values with respect to device ground. All overshoots due to system or tester noise are included.  $V_{IL}$  (Min.) is equal to -3.0V for pulse durations less than 20 ns. 3. 4.

Not more than one output should be tested at a time. Duration of the short circuit should not be more than one second. V<sub>OUT</sub> = 0.5V has been chosen to avoid test problems 5. caused by tester ground degradation. Tested initially and after any design or process changes that may affect these parameters.

6.

# Capacitance<sup>[6]</sup>

| Parameter        | Description        | Test Conditions                     | Min. | Max. | Unit |

|------------------|--------------------|-------------------------------------|------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 2.0V @ f = 1 MHz  |      | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 2.0V @ f = 1 MHz |      | 10   | pF   |

#### Endurance Characteristics<sup>[6]</sup>

| Parameter | Description                  | Test Conditions               | Min. | Max. | Unit   |

|-----------|------------------------------|-------------------------------|------|------|--------|

| Ν         | Minimum Reprogramming Cycles | Normal Programming Conditions | 100  |      | Cycles |

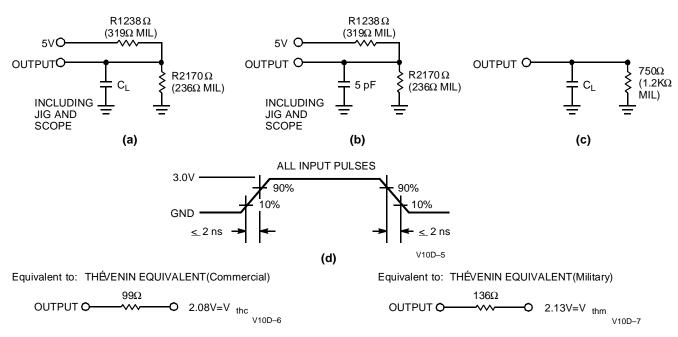

#### **AC Test Loads and Waveforms**

| Load Speed            | CL    | Package                  |

|-----------------------|-------|--------------------------|

| 7.5, 10, 15, 25<br>ns | 50 pF | PDIP, CDIP,<br>PLCC, LCC |

| Parameter            | V <sub>X</sub>   | Output Waveform Measurement Level                              |  |  |  |  |  |

|----------------------|------------------|----------------------------------------------------------------|--|--|--|--|--|

| t <sub>ER (-</sub> ) | 1.5V             | V <sub>OH</sub> 0.5V                                           |  |  |  |  |  |

| t <sub>ER (+)</sub>  | 2.6V             | V <sub>OL</sub> 0.5V V <sub>X</sub>                            |  |  |  |  |  |

| t <sub>EA (+)</sub>  | 0V               | V <sub>X</sub> <u>1.5V</u> V <sub>OH</sub> V <sub>10D-10</sub> |  |  |  |  |  |

| t <sub>EA (-</sub> ) | V <sub>thc</sub> | V <sub>X</sub> 0.5V VOL V10D-11                                |  |  |  |  |  |

(e) Test Waveforms

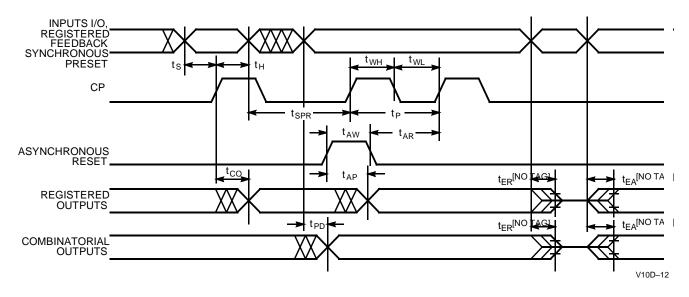

## Commercial Switching Characteristics PALC22V10D<sup>[2, 7]</sup>

|                   |                                                                                                  | 22V <sup>-</sup> | 10D-7 | 22V1 | 0D-10 | 22V1 | 0D-15 | 22V1 | 0D-25 |      |

|-------------------|--------------------------------------------------------------------------------------------------|------------------|-------|------|-------|------|-------|------|-------|------|

| Parameter         | Description                                                                                      | Min.             | Max.  | Min. | Max.  | Min. | Max.  | Min. | Max.  | Unit |

| t <sub>PD</sub>   | Input to Output<br>Propagation Delay <sup>[8, 9]</sup>                                           | 3                | 7.5   | 3    | 10    | 3    | 15    | 3    | 25    | ns   |

| t <sub>EA</sub>   | Input to Output Enable Delay <sup>[10]</sup>                                                     |                  | 8     |      | 10    |      | 15    |      | 25    | ns   |

| t <sub>ER</sub>   | Input to Output Disable Delay <sup>[11]</sup>                                                    |                  | 8     |      | 10    |      | 15    |      | 25    | ns   |

| t <sub>CO</sub>   | Clock to Output Delay <sup>[8, 9]</sup>                                                          | 2                | 5     | 2    | 7     | 2    | 8     | 2    | 15    | ns   |

| t <sub>S1</sub>   | Input or Feedback Set-Up Time                                                                    | 5                |       | 6    |       | 10   |       | 15   |       | ns   |

| t <sub>S2</sub>   | Synchronous Preset Set-Up Time                                                                   | 6                |       | 7    |       | 10   |       | 15   |       | ns   |

| t <sub>H</sub>    | Input Hold Time                                                                                  | 0                |       | 0    |       | 0    |       | 0    |       | ns   |

| t <sub>P</sub>    | External Clock Period (t <sub>CO</sub> + t <sub>S</sub> )                                        | 10               |       | 12   |       | 20   |       | 30   |       | ns   |

| t <sub>WH</sub>   | Clock Width HIGH <sup>[6]</sup>                                                                  | 3                |       | 3    |       | 6    |       | 13   |       | ns   |

| t <sub>WL</sub>   | Clock Width LOW <sup>[6]</sup>                                                                   | 3                |       | 3    |       | 6    |       | 13   |       | ns   |

| f <sub>MAX1</sub> | External Maximum Frequency $(1/(t_{CO} + t_S))^{[12]}$                                           | 100              |       | 76.9 |       | 55.5 |       | 33.3 |       | MHz  |

| f <sub>MAX2</sub> | Data Path Maximum Frequency $(1/(t_{WH} + t_{WL}))^{[6, 13]}$                                    | 166              |       | 142  |       | 83.3 |       | 35.7 |       | MHz  |

| f <sub>MAX3</sub> | Internal Feedback Maximum<br>Frequency (1/(t <sub>CF</sub> + t <sub>S</sub> )) <sup>[6,14]</sup> | 133              |       | 111  |       | 68.9 |       | 38.5 |       | MHz  |

| t <sub>CF</sub>   | Register Clock to<br>Feedback Input <sup>[6, 15]</sup>                                           |                  | 2.5   |      | 3     |      | 4.5   |      | 13    | ns   |

| t <sub>AW</sub>   | Asynchronous Reset Width                                                                         | 8                |       | 10   |       | 15   |       | 25   |       | ns   |

| t <sub>AR</sub>   | Asynchronous Reset Recovery<br>Time                                                              | 5                |       | 6    |       | 10   |       | 25   |       | ns   |

| t <sub>AP</sub>   | Asynchronous Reset to<br>Registered Output Delay                                                 |                  | 12    |      | 13    |      | 20    |      | 25    | ns   |

| t <sub>SPR</sub>  | Synchronous Preset Recovery<br>Time                                                              | 6                |       | 8    |       | 10   |       | 15   |       | ns   |

| t <sub>PR</sub>   | Power-Up Reset Time <sup>[6,16]</sup>                                                            | 1                |       | 1    |       | 1    |       | 1    |       | μs   |

Notes:

7. Part (a) of AC Test Loads and Waveforms is used for all parameters except t<sub>ER</sub> and t<sub>EA(+)</sub>. Part (b) of AC Test Loads and Waveforms is used for t<sub>ER</sub>. Part (c) of AC Test

8.

Loads and Waveforms is used for  $t_{EA(+)}$ . Min. times are tested initially and after any design or process changes that may affect these parameters. This specification is guaranteed for all device outputs changing state in a given access cycle. The test load of part (a) of AC Test Loads and Waveforms is used for measuring  $t_{EA(+)}$ . The test load of part (c) of AC Test Loads and Waveforms is used for measuring  $t_{EA(+)}$ . The test load of part (c) of AC Test Loads and Waveforms is used for measuring to the test waveforms and measurement reference levels. 10.

This parameter is measured as the time after output disable input that the previous output data state remains stable on the output. This delay is measured to the point at which a previous HIGH level has fallen to 0.5 volts below  $V_{OH}$  min. or a previous LOW level has risen to 0.5 volts above  $V_{OL}$  max. Please see part (e) of AC 11. Test Loads and Waveforms for enable and disable test waveforms and measurement reference levels.

This specification indicates the guaranteed maximum frequency at which a state machine configuration with external feedback can operate. This specification indicates the guaranteed maximum frequency at which the device can operate in data path mode. This specification indicates the guaranteed maximum frequency at which a state machine configuration with internal only feedback can operate. This specification indicates the guaranteed maximum frequency at which a state machine configuration with internal only feedback can operate. This specification indicates the guaranteed maximum frequency at which a state machine configuration with internal only feedback can operate. This parameter is calculated from the clock period at  $f_{MAX}$  internal ( $1/f_{MAX3}$ ) as measured (see Note above) minus t<sub>3</sub>. 12.

13.

14.

15.

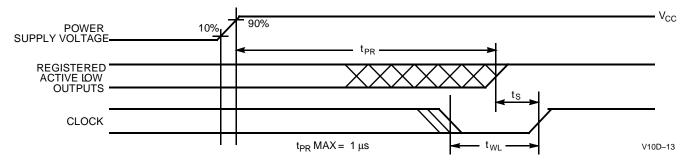

The registers in the PALC22V10D have been designed with the capability to reset during system power-up. Following power-up, all registers will be reset to a logic LOW state. The output state will depend on the polarity of the output buffer. This feature is useful in establishing state machine initialization. To insure proper operation, the rise in V<sub>CC</sub> must be monotonic and the timing constraints depicted in Power-Up Reset Waveform must be satisfied. 16.

# Military and Industrial Switching Characteristics PALC22V10D<sup>[2,7]</sup>

|                   |                                                                                                  | 22V1 | 0D-10 | 22V1 | 22V10D-15 |      | 22V10D-25 |      |

|-------------------|--------------------------------------------------------------------------------------------------|------|-------|------|-----------|------|-----------|------|

| Parameter         | Description                                                                                      | Min. | Max.  | Min. | Max.      | Min. | Max.      | Unit |

| t <sub>PD</sub>   | Input to Output<br>Propagation Delay <sup>[8, 9]</sup>                                           | 3    | 10    | 3    | 15        | 3    | 25        | ns   |

| t <sub>EA</sub>   | Input to Output Enable Delay <sup>[10]</sup>                                                     |      | 10    |      | 15        |      | 25        | ns   |

| t <sub>ER</sub>   | Input to Output Disable Delay <sup>[11]</sup>                                                    |      | 10    |      | 15        |      | 25        | ns   |

| t <sub>CO</sub>   | Clock to Output Delay <sup>[8, 9]</sup>                                                          | 2    | 7     | 2    | 8         | 2    | 15        | ns   |

| t <sub>S1</sub>   | Input or Feedback Set-Up Time                                                                    | 6    |       | 10   |           | 18   |           | ns   |

| t <sub>S2</sub>   | Synchronous Preset Set-Up Time                                                                   | 7    |       | 10   |           | 18   |           | ns   |

| t <sub>H</sub>    | Input Hold Time                                                                                  | 0    |       | 0    |           | 0    |           | ns   |

| t <sub>P</sub>    | External Clock Period (t <sub>CO</sub> + t <sub>S</sub> )                                        | 12   |       | 20   |           | 33   |           | ns   |

| t <sub>WH</sub>   | Clock Width HIGH <sup>[6]</sup>                                                                  | 3    |       | 6    |           | 14   |           | ns   |

| t <sub>WL</sub>   | Clock Width LOW <sup>[6]</sup>                                                                   | 3    |       | 6    |           | 14   |           | ns   |

| f <sub>MAX1</sub> | External Maximum Frequency $(1/(t_{CO} + t_S))^{[12]}$                                           | 76.9 |       | 50.0 |           | 30.3 |           | MHz  |

| f <sub>MAX2</sub> | Data Path Maximum Frequency (1/(t <sub>WH</sub> + t <sub>WL</sub> )) <sup>[6, 13]</sup>          | 142  |       | 83.3 |           | 35.7 |           | MHz  |

| f <sub>MAX3</sub> | Internal Feedback Maximum<br>Frequency (1/(t <sub>CF</sub> + t <sub>S</sub> )) <sup>[6,14]</sup> | 111  |       | 68.9 |           | 32.2 |           | MHz  |

| t <sub>CF</sub>   | Register Clock to<br>Feedback Input <sup>[6,15]</sup>                                            |      | 3     |      | 4.5       |      | 13        | ns   |

| t <sub>AW</sub>   | Asynchronous Reset Width                                                                         | 10   |       | 15   |           | 25   |           | ns   |

| t <sub>AR</sub>   | Asynchronous Reset<br>Recovery Time                                                              | 6    |       | 12   |           | 25   |           | ns   |

| t <sub>AP</sub>   | Asynchronous Reset to<br>Registered Output Delay                                                 |      | 12    |      | 20        |      | 25        | ns   |

| t <sub>SPR</sub>  | Synchronous Preset<br>Recovery Time                                                              | 8    |       | 20   |           | 25   |           | ns   |

| t <sub>PR</sub>   | Power-Up Reset Time <sup>[6, 16]</sup>                                                           | 1    |       | 1    |           | 1    |           | μs   |

# **Switching Waveform**

# Power-Up Reset Waveform<sup>[16]</sup>

# Functional Logic Diagram for PALC22V10D

# **Ordering Information**

| I <sub>CC</sub><br>(mA) | t <sub>PD</sub><br>(ns) | t <sub>S</sub><br>(ns) | t <sub>CO</sub><br>(ns) | Ordering Code    | Package<br>Name | Package Type                        | Operating<br>Range |

|-------------------------|-------------------------|------------------------|-------------------------|------------------|-----------------|-------------------------------------|--------------------|

| 130                     | 7.5                     | 5                      | 5                       | PALC22V10D-7JC   | J64             | 28-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALC22V10D-7PC   | P13             | 24-Lead (300-Mil) Molded DIP        |                    |

| 90                      | 10                      | 6                      | 7                       | PALC22V10D-10JC  | J64             | 28-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALC22V10D-10PC  | P13             | 24-Lead (300-Mil) Molded DIP        | 7                  |

| 150                     | 10                      | 6                      | 7                       | PALC22V10D-10JI  | J64             | 28-Lead Plastic Leaded Chip Carrier | Industrial         |

|                         |                         |                        |                         | PALC22V10D-10PI  | P13             | 24-Lead (300-Mil) Molded DIP        |                    |

| 150                     | 10                      | 6                      | 7                       | PALC22V10D-10DMB | D14             | 24-Lead (300-Mil) CerDIP            | Military           |

|                         |                         |                        |                         | PALC22V10D-10KMB | K73             | 24-Lead Rectangular Cerpack         |                    |

|                         |                         |                        |                         | PALC22V10D-10LMB | L64             | 28-Square Leadless Chip Carrier     |                    |

| 90                      | 15                      | 7.5                    | 10                      | PALC22V10D-15JC  | J64             | 28-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALC22V10D-15PC  | P13             | 24-Lead (300-Mil) Molded DIP        |                    |

| 120                     | 15                      | 7.5                    | 10                      | PALC22V10D-15JI  | J64             | 28-Lead Plastic Leaded Chip Carrier | Industrial         |

|                         |                         |                        |                         | PALC22V10D-15PI  | P13             | 24-Lead (300-Mil) Molded DIP        |                    |

| 120                     | 15                      | 7.5                    | 10                      | PALC22V10D-15DMB | D14             | 24-Lead (300-Mil) CerDIP            | Military           |

|                         |                         |                        |                         | PALC22V10D-15KMB | K73             | 24-Lead Rectangular Cerpack         |                    |

|                         |                         |                        |                         | PALC22V10D-15LMB | L64             | 28-Square Leadless Chip Carrier     |                    |

| 90                      | 25                      | 15                     | 15                      | PALC22V10D-25JC  | J64             | 28-Lead Plastic Leaded Chip Carrier | Commercial         |

|                         |                         |                        |                         | PALC22V10D-25PC  | P13             | 24-Lead (300-Mil) Molded DIP        |                    |

| 120                     | 25                      | 15                     | 15                      | PALC22V10D-25JI  | J64             | 28-Lead Plastic Leaded Chip Carrier | Industrial         |

|                         |                         |                        |                         | PALC22V10D-25PI  | P13             | 24-Lead (300-Mil) Molded DIP        |                    |

| 120                     | 25                      | 15                     | 15                      | PALC22V10D-25DMB | D14             | 24-Lead (300-Mil) CerDIP            | Military           |

|                         |                         |                        |                         | PALC22V10D-25KMB | K73             | 24-Lead Rectangular Cerpack         |                    |

|                         |                         |                        |                         | PALC22V10D-25LMB | L64             | 28-Square Leadless Chip Carrier     |                    |

\_\_\_\_\_

## MILITARY SPECIFICATIONS Group A Subgroup Testing

### **DC Characteristics**

| Parameter       | Subgroups |

|-----------------|-----------|

| V <sub>OH</sub> | 1, 2, 3   |

| V <sub>OL</sub> | 1, 2, 3   |

| V <sub>IH</sub> | 1, 2, 3   |

| V <sub>IL</sub> | 1, 2, 3   |

| I <sub>IX</sub> | 1, 2, 3   |

| I <sub>OZ</sub> | 1, 2, 3   |

| I <sub>CC</sub> | 1, 2, 3   |

# **Switching Characteristics**

| Parameter       | Subgroups |

|-----------------|-----------|

| t <sub>PD</sub> | 9, 10, 11 |

| t <sub>CO</sub> | 9, 10, 11 |

| t <sub>S</sub>  | 9, 10, 11 |

| t <sub>H</sub>  | 9, 10, 11 |

Document #: 38-00185-H

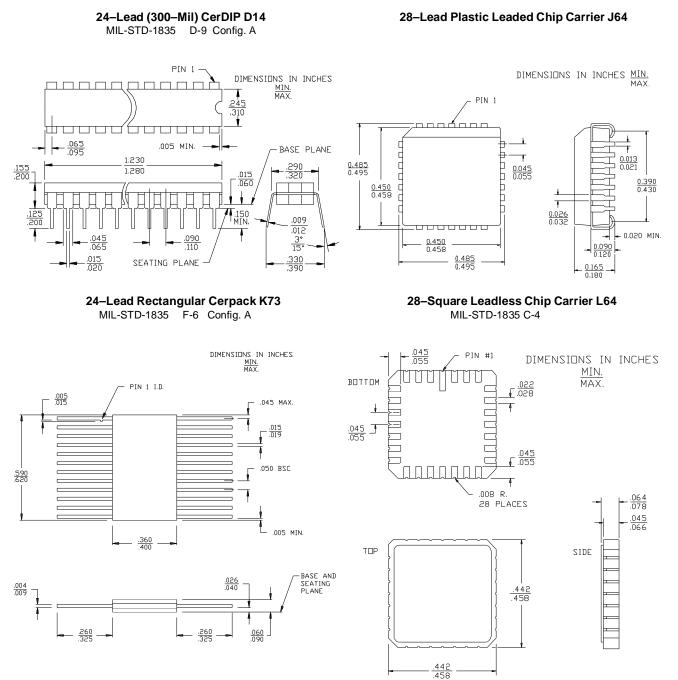

#### **Package Diagrams**

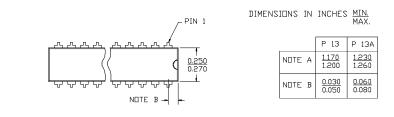

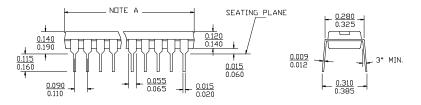

#### Package Diagrams (continued)

#### 24-Lead (300-Mil) Molded DIP P13/P13A

© Cypress Semiconductor Corporation, 1995. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of charges.