DP83932C-20/25/33 MHz SONIC Systems-Oriented Network Interface Controlle

# DP83932C-20/25/33 MHz SONIC<sup>™</sup> Systems-Oriented Network Interface Controller

## **General Description**

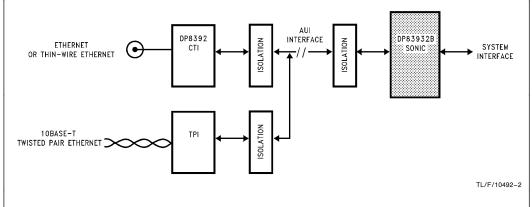

The SONIC (Systems-Oriented Network Interface Controller) is a second-generation Ethernet Controller designed to meet the demands of today's high-speed 32- and 16-bit systems. Its system interface operates with a high speed DMA that typically consumes less than 3% of the bus bandwidth (25 MHz bus clock). Selectable bus modes provide both big and little endian byte ordering and a clean interface to standard microprocessors. The linked-list buffer management system of SONIC offers maximum flexibility in a variety of environments from PC-oriented adapters to high-speed motherboard designs. Furthermore, the SONIC integrates a fully-compatible IEEE 802.3 Encoder/Decoder (ENDEC) allowing for a simple 2-chip solution for Ethernet when the SONIC is paired with the DP8392 Coaxial Transceiver Interface or a 10BASE-T transceiver.

For increased performance, the SONIC implements a unique buffer management scheme to efficiently process, receive and transmit packets in system memory. No intermediate packet copy is necessary. The receive buffer management uses three areas in memory for (1) allocating additional resources, (2) indicating status information, and (3) buffering packet data. During reception, the SONIC stores packets in the buffer area, then indicates receive status and control information in the descriptor area. The system allocates more memory resources to the SONIC by adding descriptors to the memory resource area. The transmit buffer

management uses two areas in memory: one for indicating status and control information and the other for fetching packet data. The system can create a transmit queue allowing multiple packets to be transmitted from a single transmit command. The packet data can reside on any arbitrary byte boundary and can exist in several non-contiguous locations.

### **Features**

- 32-bit non-multiplexed address and data bus

- High-speed, interruptible DMA

- Linked-list buffer management maximizes flexibility

- Two independent 32-byte transmit and receive FIFOs

- Bus compatibility for all standard microprocessors

- Supports big and little endian formats

- Integrated IEEE 802.3 ENDEC

- Complete address filtering for up to 16 physical and/or multicast addresses

- 32-bit general-purpose timer

- Full-duplex loopback diagnostics

- Fabricated in low-power CMOS

- 132 PQFP package

- Full network management facilities support the 802.3 layer management standard

- Integrated support for bridge and repeater applications

# **System Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation. SONICTM is a trademark of National Semiconductor Corporation.

© 1995 National Semiconductor Corporation TL/F/1

RRD-B30M105/Printed in U. S. A

## **Table of Contents**

#### 1.0 FUNCTIONAL DESCRIPTION

- 1.1 IEEE 802.3 ENDEC Unit

- 1.1.1 ENDEC Operation

- 1.1.2 Selecting an External ENDEC

- 1.2 MAC Unit

- 1.2.1 MAC Receive Section

- 1.2.2 MAC Transmit Section

- 1.3 Data Width and Byte Ordering

- 1.4 FIFO and Control Logic

- 1.4.1 Receive FIFO

- 1.4.2 Transmit FIFO

- 1.5 Status and Configuration Registers

- 1.6 Bus Interface

- 1.7 Loopback and Diagnostics

- 1.7.1 Loopback Procedure

- 1.8 Network Management Functions

## 2.0 TRANSMIT/RECEIVE IEEE 802.3 FRAME FORMAT

- 2.1 Preamble and Start Of Frame Delimiter (SFD)

- 2.2 Destination Address

- 2.3 Source Address

- 2.4 Length/Type Field

- 2.5 Data Field

- 2.6 FCS Field

- 2.7 MAC (Media Access Control) Conformance

## 3.0 BUFFER MANAGEMENT

- 3.1 Buffer Management Overview

- 3.2 Descriptor Areas

- 3.2.1 Naming Convention for Descriptors

- 3.2.2 Abbreviations

- 3.2.3 Buffer Management Base Addresses

- 3.3 Descriptor Data Alignment

- 3.4 Receive Buffer Management

- 3.4.1 Receive Resource Area (RRA)

- 3.4.2 Receive Buffer Area (RBA)

- 3.4.3 Receive Descriptor Area (RDA)

- 3.4.4 Receive Buffer Management Initialization

- 3.4.5 Beginning of Reception

- 3.4.6 End of Packet Processing

- 3.4.7 Overflow Conditions

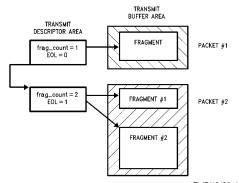

- 3.5 Transmit Buffer Management

- 3.5.1 Transmit Descriptor Area (TDA)

- 3.5.2 Transmit Buffer Area (TBA)

- 3.5.3 Preparing to Transmit

- 3.5.4 Dynamically Adding TDA Descriptors

#### 4.0 SONIC REGISTERS

- 4.1 The CAM Unit

- 4.1.1 The Load CAM Command

- 4.2 Status/Control Registers

- 4.3 Register Description

- 4.3.1 Command Register

- 4.3.2 Data Configuration Register

- 4.3.3 Receive Control Register

- 4.3.4 Transmit Control Register

- 4.3.5 Interrupt Mask Register

- 4.3.6 Interrupt Status Register

- 4.3.7 Data Configuration Register 2

- 4.3.8 Transmit Registers

- 4.3.9 Receive Registers

- 4.3.10 CAM Registers

- 4.3.11 Tally Counters

- 4.3.12 General Purpose Timer

- 4.3.13 Silicon Revision Register

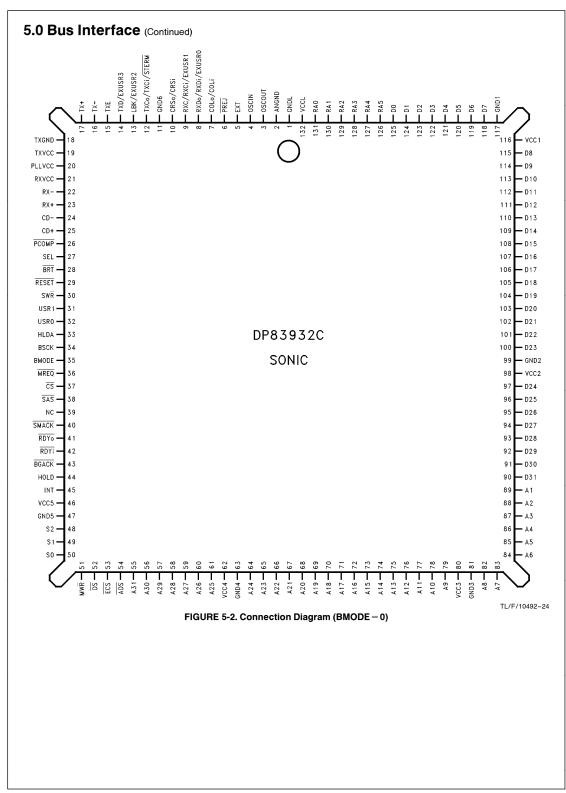

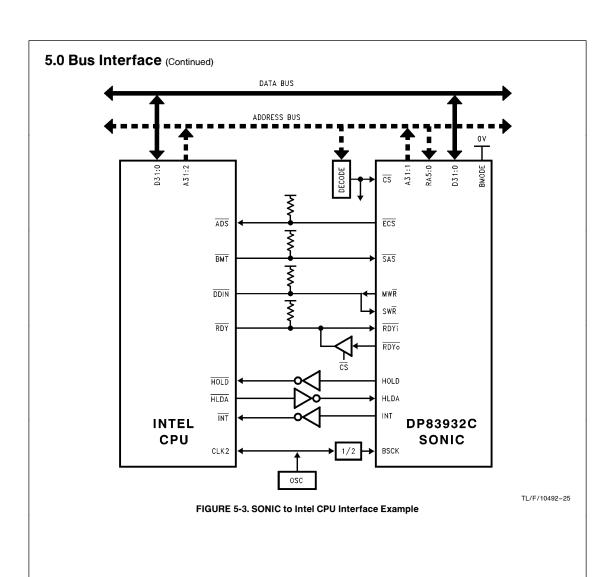

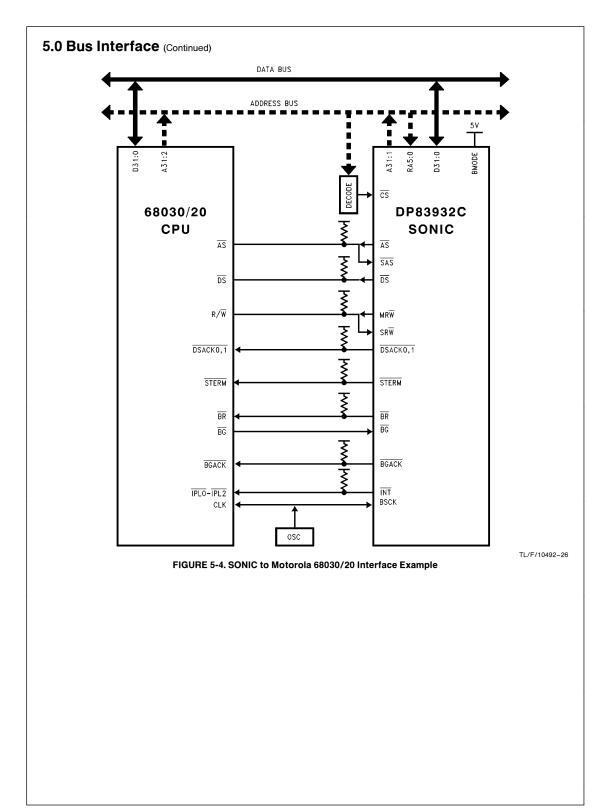

## **5.0 BUS INTERFACE**

- 5.1 Pin Configurations

- 5.2 Pin Description

- 5.3 System Configuration

- 5.4 Bus Operations

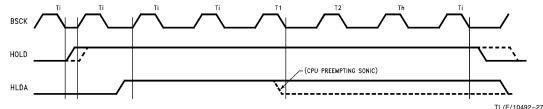

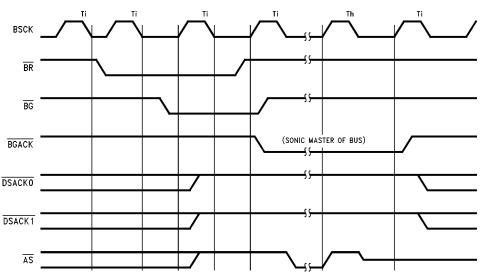

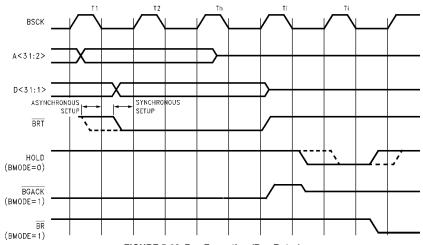

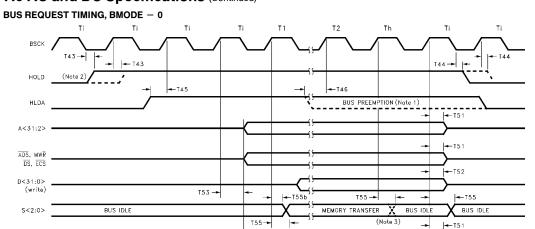

- 5.4.1 Acquiring the Bus

- 5.4.2 Block Transfers

- 5.4.3 Bus Status

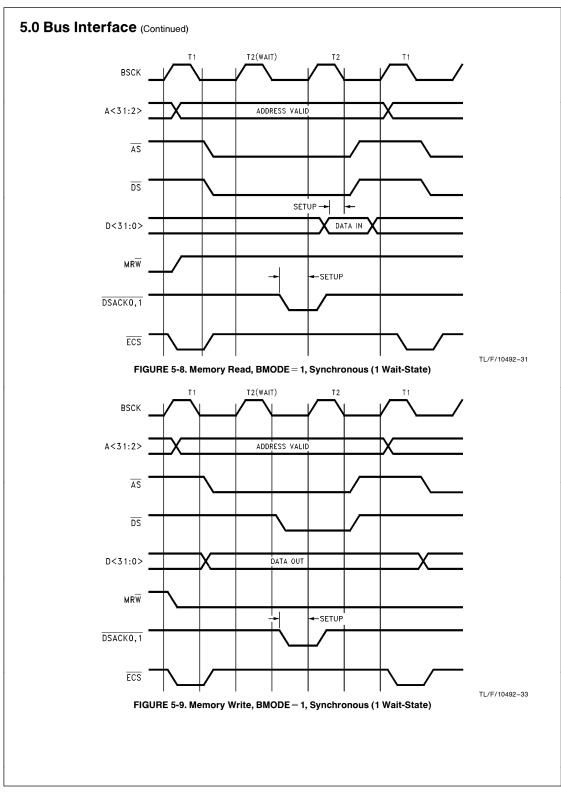

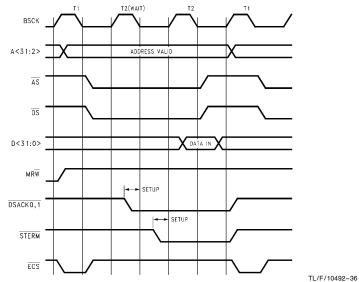

- 5.4.4 Bus Mode Compatibility

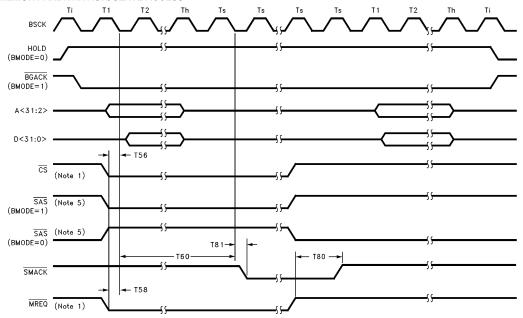

- 5.4.5 Master Mode Bus Cycles

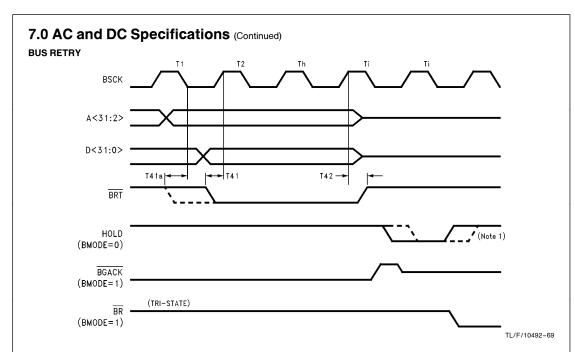

- 5.4.6 Bus Exceptions (Bus Retry)

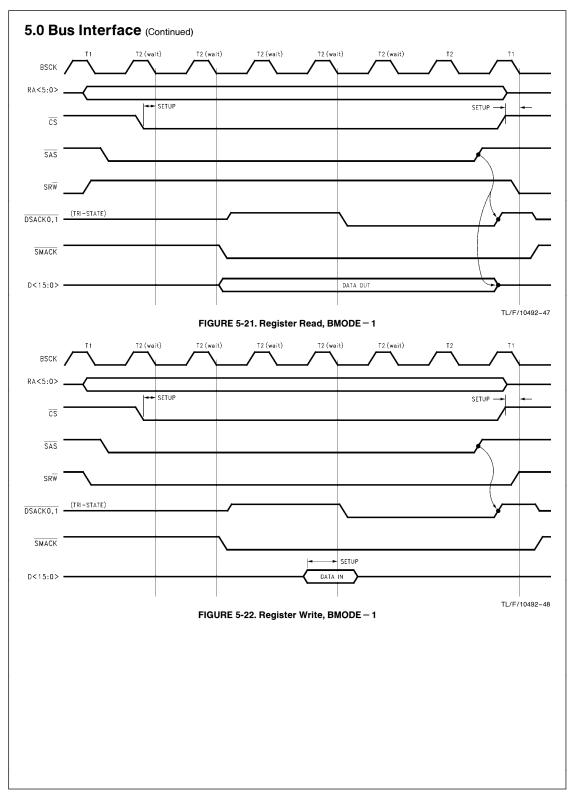

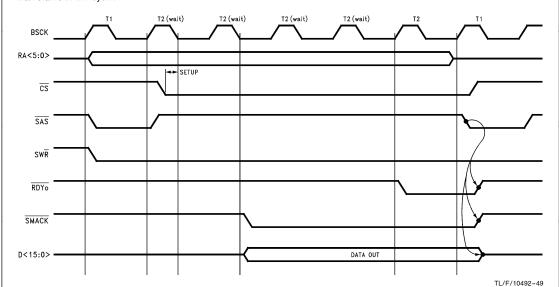

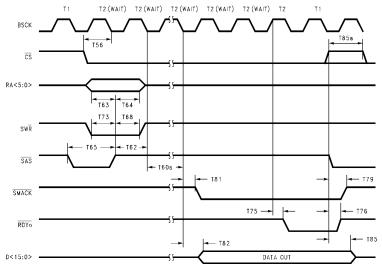

- 5.4.7 Slave Mode Bus Cycle

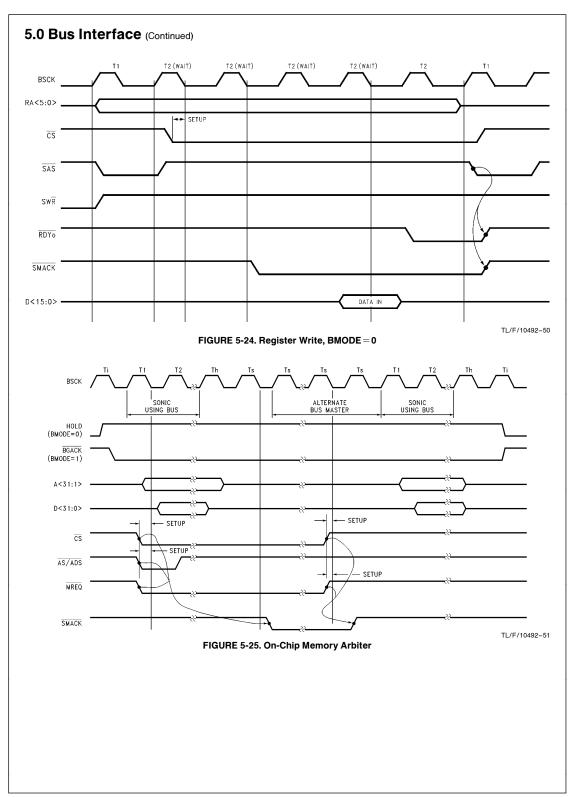

- 5.4.8 On-Chip Memory Arbiter

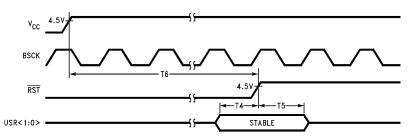

- 5.4.9 Chip Reset

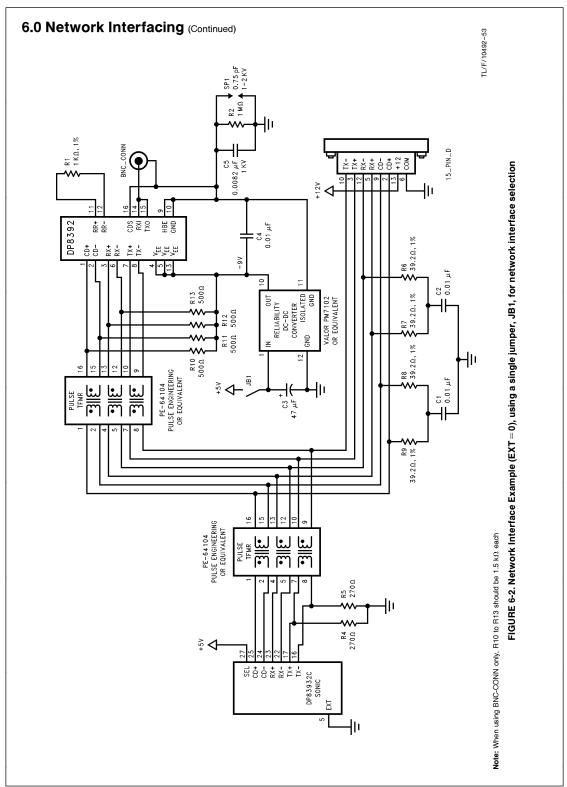

## 6.0 NETWORK INTERFACING

- 6.1 Manchester Encoder and Differential Driver

- 6.1.1 Manchester Decoder

- 6.1.2 Collision Translator

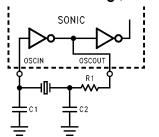

- 6.1.3 Oscillator Inputs

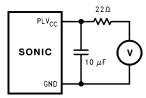

- 6.1.4 Power Supply Considerations

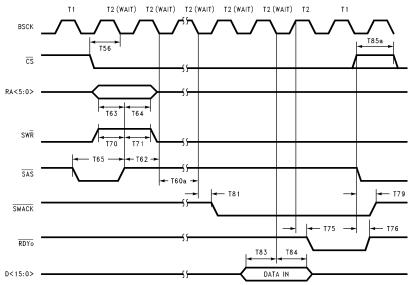

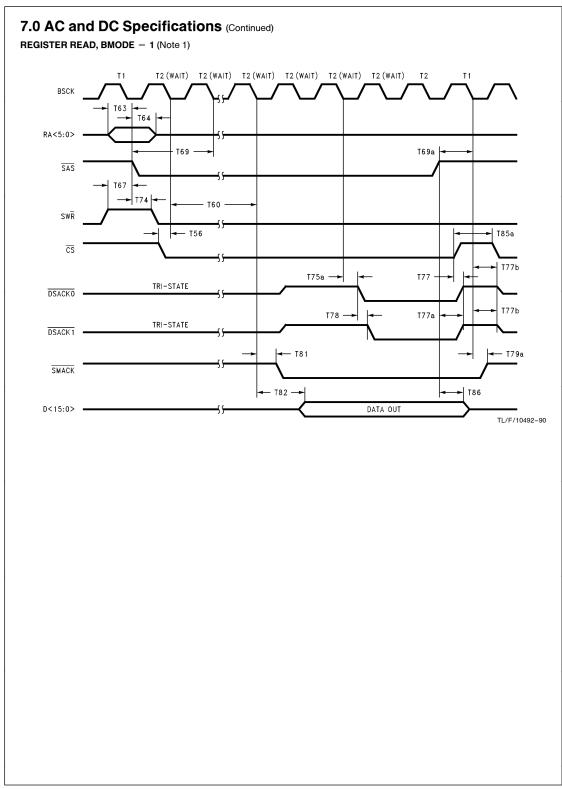

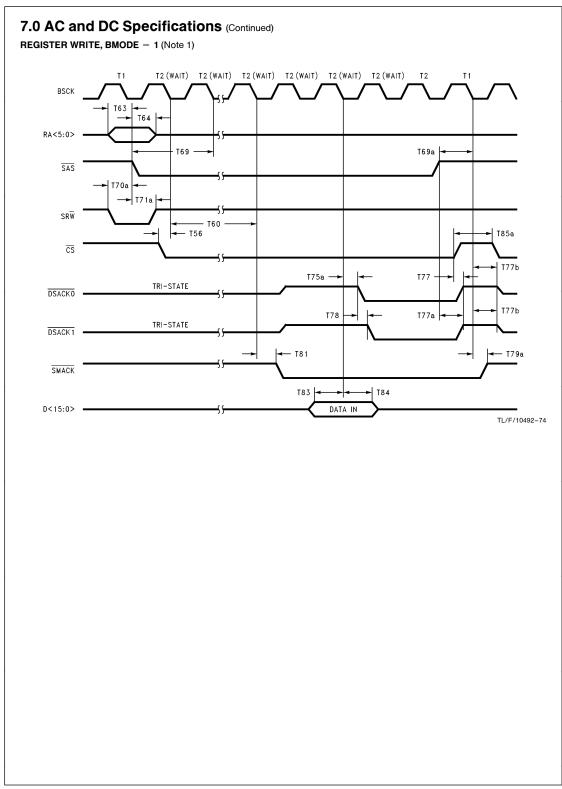

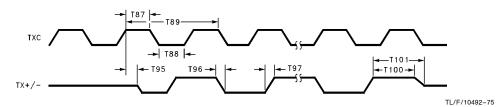

## 7.0 AC AND DC SPECIFICATIONS

**8.0 AC TIMING TEST CONDITIONS**

## 1.0 Functional Description

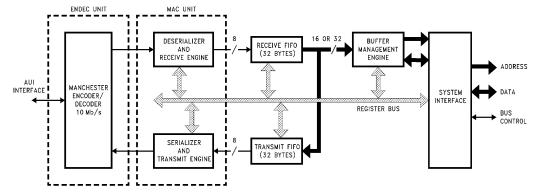

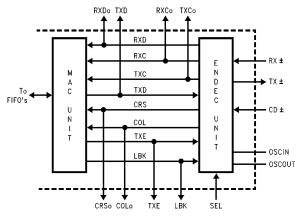

The SONIC (Figure 1-1) consists of an encoder/decoder (ENDEC) unit, media access control (MAC) unit, separate receive and transmit FIFOs, a system buffer management engine, and a user programmable system bus interface unit on a single chip. SONIC is highly pipelined providing maximum system level performance. This section provides a functional overview of SONIC.

## 1.1 IEEE 802.3 ENDEC UNIT

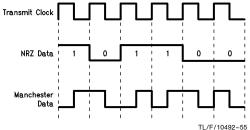

The ENDEC (Encoder/Decoder) unit is the interface between the Ethernet transceiver and the MAC unit. It provides the Manchester data encoding and decoding functions for IEEE 802.3 Ethernet/Thin-Ethernet type local area networks. The ENDEC operations of SONIC are identical to the DP83910A CMOS Serial Network Interface device. During transmission, the ENDEC unit combines non-return-zero (NRZ) data from the MAC section and clock pulses into Manchester data and sends the converted data differentially to the transceiver. Conversely, during reception, an analog PLL decodes the Manchester data to NRZ format and receive clock. The ENDEC unit is a functionally complete Manchester encoder/decoder incorporating a balanced driver and receiver, on-board crystal oscillator, collision signal translator, and a diagnostic loopback. The features include:

- Compatible with Ethernet I and II, IEEE 802.3 10base5 and 10base2

- 10Mb/s Manchester encoding/decoding with receive clock recovery

- · Requires no precision components

- · Loopback capability for diagnostics

- Externally selectable half or full step modes of operation at transmit output

- Squelch circuitry at the receive and collision inputs reject noise

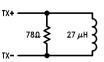

- Connects to the transceiver (AUI) cable via external pulse transformer

#### 1.1.1 ENDEC Operation

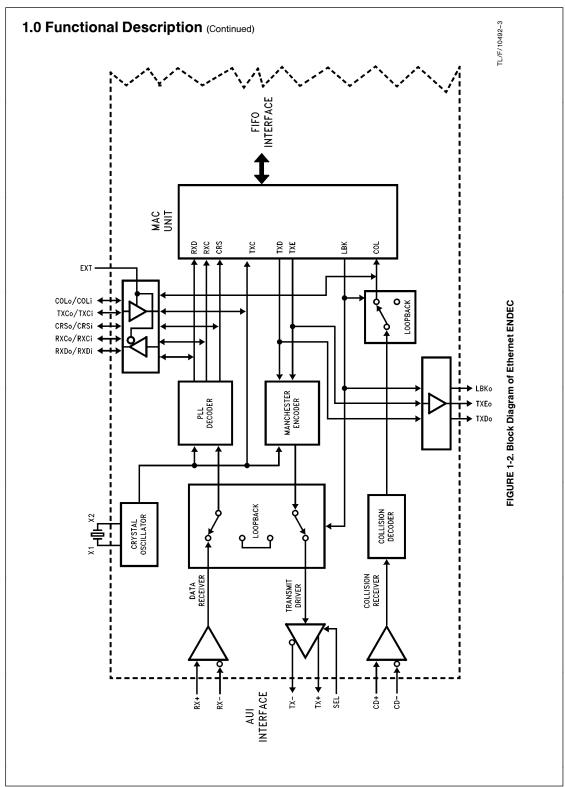

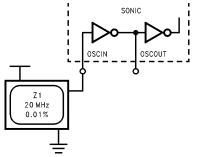

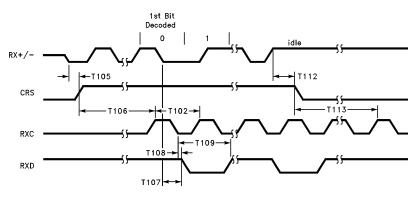

The primary function of the ENDEC unit (Figure 1-2) is to perform the encoding and decoding necessary for compatibility between the differential pair Manchester encoded data of the transceiver and the Non-Return-to-Zero (NRZ) serial data of the MAC unit data line. In addition to encoding and decoding the data stream, the ENDEC also supplies all the necessary special signals (e.g., collision detect, carrier sense, and clocks) to the MAC unit. The signals provided to the MAC unit from the on-chip ENDEC are also provided as outputs to the user.

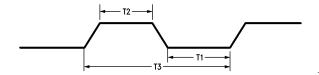

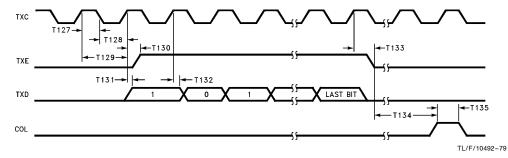

Manchester Encoder and Differential Output Driver: During transmission to the network, the ENDEC unit translates the NRZ serial data from the MAC unit into differential pair Manchester encoded data on the Coaxial Transceiver Interface (e.g., National's DP8392) transmit pair. To perform this operation the NRZ bit stream from the MAC unit is passed through the Manchester encoder block of the ENDEC unit. Once the bit stream is encoded, it is transmitted out differentially to the transmit differential pair through the transmit driver.

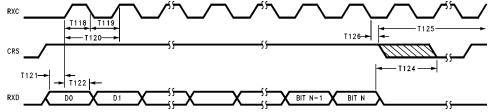

Manchester Decoder: During reception from the network, the differential receive data from the transceiver (e.g., the DP8392) is converted from Manchester encoded data into NRZ serial data and a receive clock, which are sent to the receive data and clock inputs of the MAC unit. To perform this operation the signal, once received by the differential receiver, is passed to the phase locked loop (PLL) decoder block. The PLL decodes the data and generates a data receive clock and a NRZ serial data stream to the MAC unit.

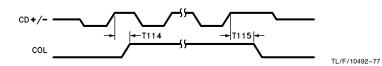

Special Signals: In addition to performing the Manchester encoding and decoding function, the ENDEC unit provides control and clocking signals to the MAC unit. The ENDEC sends a carrier sense (CRS) signal that indicates to the MAC unit that data is present from the network on the ENDEC's receive differential pair. The MAC unit is also provided with a collision detection signal (COL) that informs the MAC unit that a collision is taking place somewhere on

FIGURE 1-1. SONIC Block Diagram

TL/F/10492-1

the network. The ENDEC section detects this when its collision receiver detects a 10 MHz signal on the differential collision input pair. The ENDEC also provides both the receive and transmit clocks to the MAC unit. The transmit clock is one half of the oscillator input. The receive clock is extracted from the input data by the PLL.

Oscillator: The oscillator generates the 10 MHz transmit clock signal for network timing. The oscillator is controlled by a parallel resonant crystal or by an external clock (see Section 6.1.3). The 20 MHz output of the oscillator is divided by 2 to generate the 10 MHz transmit clock (TXC) for the MAC section. The oscillator provides an internal clock signal for the encoding and decoding circuits.

Loopback Functions: The SONIC provides three loopback modes. These modes allow loopback testing at the MAC, ENDEC and external transceiver level (see Section 1.7 for details). It is important to note that when the SONIC is transmitting, the transmitted packet will always be looped back by the external transceiver. The SONIC takes advantage of this to monitor the transmitted packet. See the explanation of the Receive State Machine in Section 1.2.1 for more information about monitoring transmitted packets.

## 1.1.2 Selecting An External ENDEC

An option is provided on SONIC to disable the on-chip ENDEC unit and use an external ENDEC. The internal IEEE 802.3 ENDEC can be bypassed by connecting the EXT pin to  $V_{\rm CC}$  (EXT = 1). In this mode the MAC signals are redirected, allowing an external ENDEC to be used. See Section 5.2 for the alternate pin definitions.

#### 1.2 MAC UNIT

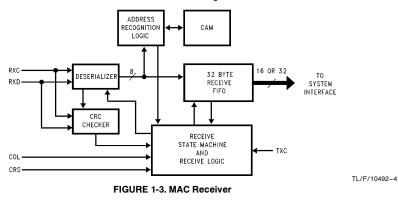

The MAC (Media Access Control) unit performs the media access control functions for transmitting and receiving packets over Ethernet. During transmission, the MAC unit frames information from the transmit FIFO and supplies serialized data to the ENDEC unit. During reception, the incoming information from the ENDEC unit is deserialized, the frame checked for valid reception, and the data is transferred to the receive FIFO. Control and status registers on the SONIC govern the operation of the MAC unit.

## 1.2.1 MAC Receive Section

The receive section (Figure 1-3) controls the MAC receive operations during reception, loopback, and transmission. During reception, the deserializer goes active after detecting the one byte SFD (Start of Frame Delimiter) pattern (Section 2.1) consisting of a "10101011" sequence. It then frames the incoming bits into octet boundaries and transfers the

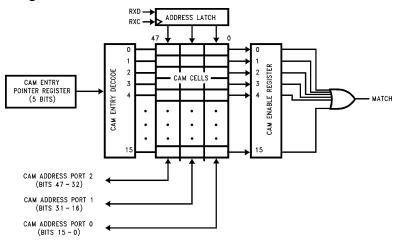

data to the 32-byte receive FIFO. Concurrently the address comparator compares the Destination Address Field to the addresses stored in the chip's CAM address registers (Content Addressable Memory cells). If a match occurs, the descrializer passes the remainder of the packet to the receive FIFO. The packet is decapsulated when the carrier sense input pin (CRS) goes inactive. At the end of reception the receive section checks the following:

- Frame alignment errors

- CRC errors

- Length errors (runt packets)

The appropriate status is indicated in the Receive Control register (Section 4.3.3). In loopback operations, the receive section operates the same as during normal reception.

During transmission, the receive section remains active to allow monitoring of the self-received packet. The CRC checker operates as normal, and the Source Address field is compared with the CAM address entries. Status of the CRC check and the source address comparison is indicated by the PMB bit in the Transmit Control register (Section 4.3.4). No data is written to the receive FIFO during transmit operations.

The receive section consists of the following blocks detailed below.

Receive State Machine (RSM): The RSM insures the proper sequencing for normal reception and self-reception during transmission. When the network is inactive, the RSM remains in an idle state continually monitoring for network activity. If the network becomes active, the RSM allows the deserializer to write data into the receive FIFO. During this state, the following conditions may prevent the complete reception of the packet.

- FIFO Overrun—The receive FIFO has been completely filled before the SONIC could buffer the data to memory.

- CAM Address Mismatch—The packet is rejected because of a mismatch between the destination address of the packet and the address in the CAM.

- Memory Resource Error—There are no more resources (buffers) available for buffering the incoming packets.

- Collision or Other Error—A collision occured on the network or some other error, such as a CRC error, occurred (this is true if the SONIC has been told to reject packets on a collision, or reject packets with errors).

If these conditions do not occur, the RSM processes the packet indicating the appropriate status in the Receive Control register.

During transmission of a packet from the SONIC, the external transceiver will always loop the packet back to the SONIC. The SONIC will use this to monitor the packet as it is being transmitted. The CRC and source address of the looped back packet are checked with the CRC and source address that were transmitted. If they do not match, an error bit is set in the status of the transmitted packet (see Packet Monitored Bad, PMB, in the Transmit Control Register, Section 4.3.4). Data is not written to the receive FIFO during this monitoring process unless Transceiver Loopback mode has been selected (see Section 1.7).

Receive Logic: The receive logic contains the command, control, and status registers that govern the operations of the receive section. It generates the control signals for writing data to the receive FIFO, processes error signals obtained from the CRC checker and the descrializer, activates the "packet reject" signal to the RSM for rejecting packets, and posts the applicable status in the Receive Control register

**Deserializer:** This section deserializes the serial input data stream and furnishes a byte clock for the address comparator and receive logic. It also synchronizes the CRC checker to begin operation (after SFD is detected), and checks for proper frame alignment with respect to CRS going inactive at the end of reception.

Address Comparator: The address comparator latches the Destination Address (during reception or loopback) or Source Address (during transmission) and determines whether the address matches one of the entries in the CAM (Content Addressable Memory).

**CRC Checker:** The CRC checker calculates the 4-byte Frame Check Sequence (FCS) field from the incoming data stream and compares it with the last 4-bytes of the received packet. The CRC checker is active for both normal reception and self-reception during transmission.

Content Addressable Memory (CAM): The CAM contains 16 user programmable entries and 1 pre-programmed Broadcast address entry for complete filtering of received packets. The CAM can be loaded with any combination of Physical and Multicast Addresses (Section 2.2). See Section 4.1 for the procedure on loading the CAM registers.

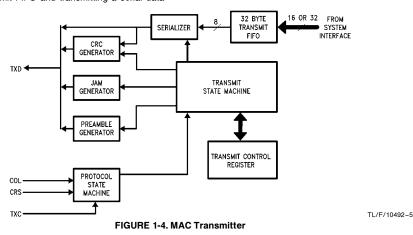

## 1.2.2 MAC Transmit Section

The transmit section (Figure 1-4) is responsible for reading data from the transmit FIFO and transmitting a serial data

stream onto the network in conformance with the IEEE 802.3 CSMA/CD standard. The Transmit Section consists of the following blocks.

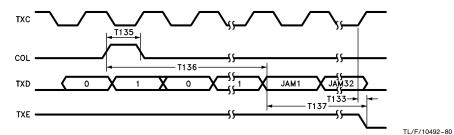

Transmit State Machine (TSM): The TSM controls the functions of the serializer, preamble generator, and JAM generator. It determines the proper sequence of events that the transmitter follows under various network conditions. If no collision occurs, the transmitter prefixes a 7 byte preamble and 1 byte Start of Frame Delimiter (SFD) consisting of a "10101011" sequence at the beginning of each packet, then sends the serialized data. At the end of the packet, an optional 4-byte CRC pattern is appended. If a collision occurs, the transmitter switches from transmitting data to sending a 4-byte Jam pattern to notify all nodes that a collision has occurred. Should the collision occur during the preamble, the transmitter waits for it to complete before jamming. After the transmission has completed, the transmitter writes status in the Transmit Control register (Section 4.3.4).

Protocol State Machine: The protocol state machine assures that the SONIC obeys the CSMA/CD protocol. Before transmitting, this state machine monitors the carrier sense and collision signals for network activity. If another node(s) is currently transmitting, the SONIC defers until the network is quiet, then transmits after its Interframe Gap Timer (9.6  $\mu$ s) has expired. The Interframe Gap time is divided into two portions. During the first 6.4  $\mu$ s, network activity restarts the Interframe Gap timer. Beyond this time, however, network activity is ignored and the state machine waits the remaining 3.2  $\mu s$  before transmitting. If the SONIC experiences a collision during a transmission, the SONIC switches from transmitting data to a 4-byte JAM pattern (4 bytes of all 1's), before ceasing to transmit. The SONIC then waits a random number of slot times (51.2  $\mu$ s) determined by the Truncated Binary Exponential Backoff Algorithm before reattempting another transmission. In this algorithm, the number of slot times to delay before the nth retransmission is chosen to be a random integer r in the range of:

$$0 \le r \le 2^k$$

where  $k = min(n,10)$

If a collision occurs on the 16th transmit attempt, the SONIC aborts transmitting the packet and reports an "Excessive Collisions" error in the Transmit Control register.

Serializer: After data has been written into the 32-byte transmit FIFO, the serializer reads byte wide data from the FIFO and sends a NRZ data stream to the Manchester encoder. The rate at which data is transmitted is determined by the transmit clock (TXC). The serialized data is transmitted after the SFD.

Preamble Generator: The preamble generator prefixes a 7 byte alternating "1,0" pattern and a 1 byte "10101011" SFD pattern at the beginning of each packet. This allows receiving nodes to synchronize to the incoming data. The preamble is always transmitted in its entirety even in the event of a collision. This assures that the minimum collision fragment is 96 bits (64 bits of normal preamble, and 4 bytes, or rather 32 bits, of the JAM pattern).

CRC Generator: The CRC generator calculates the 4-byte FCS field from the transmitted serial data stream. If enabled, the 4-byte FCS field is appended to the end of the transmitted packet (Section 2.6).

For bridging or switched ethernet applications the CRC Generator can be inhibited by setting bit 13 in the Transmit Control Register (Section 4.3.4). This feature is used when an ethernet segment has already received a packet with a CRC appended and needs to forward it to another ethernet

Jam Generator: The Jam generator produces a 4-byte pattern of all 1's to assure that all nodes on the network sense the collision. When a collision occurs, the SONIC stops transmitting data and enables the Jam generator. If a collision occurs during the preamble, the SONIC finishes transmitting the preamble before enabling the Jam generator (see Preamble Generator above).

#### 1.3 DATA WIDTH AND BYTE ORDERING

The SONIC can be programmed to operate with either 32-bit or 16-bit wide memory. The data width is configured during initialization by programming the DW bit in the Data Configuration Register (DCR, Section 4.3.2). If the 16-bit data path is selected, data is driven on pins D15-D0. The SONIC also provides both Little Endian and Big Endian byte-ordering capability for compatibility with National/Intel or Motorola microprocessors respectively by selecting the proper level on the BMODE pin. The byte ordering is depicted below.

Little Endian mode (National/Intel, BMODE = 0): The byte orientation for received and transmitted data in the Receive Buffer Area (RBA) and Transmit Buffer Area (TBA) of system memory is as follows:

#### 16-Bit Word

| 15   | 8 | 7  | 0     |

|------|---|----|-------|

| Byte | 1 | By | /te 0 |

| MSB  | 3 | L  | .SB   |

## 32-Bit Long Word

| 31     | 24 | 23     | 16 | 15     | 8 | 7      | 0  |

|--------|----|--------|----|--------|---|--------|----|

| Byte 3 |    | Byte 2 |    | Byte 1 |   | Byte 0 |    |

| MSB    |    |        |    |        |   | 1.     | SB |

Big Endian mode (Motorola, BMODE = 1): The byte orientation for received and transmitted data in the RBA and TBA is as follows:

#### 16-Bit Word

| 15   | 8      | 7   | 0    |  |

|------|--------|-----|------|--|

| Byte | Byte 0 |     | te 1 |  |

| LSB  |        | MSB |      |  |

#### 32-Bit Long Word

| 31     | 24 | 23     | 16 | 15     | 8 | 7      | 0   |

|--------|----|--------|----|--------|---|--------|-----|

| Byte 0 |    | Byte 1 |    | Byte 2 |   | Byte 3 |     |

| LSB    |    |        |    |        |   | M      | ISB |

TL/F/10492-6

FIGURE 1-5. Receive FIFO

#### 1.4 FIFO AND CONTROL LOGIC

The SONIC incorporates two independent 32-byte FIFOs for transferring data to/from the system interface and from/ to the network. The FIFOs, providing temporary storage of data, free the host system from the real-time demands on the network

The way in which the FIFOS are emptied and filled is controlled by the FIFO threshold values and the Block Mode Select bits (BMS, Section 4.3.2). The threshold values determine how full or empty the FIFOs can be before the SONIC will request the bus to get more data from memory or buffer more data to memory. When block mode is set, the number of bytes transferred is set by the threshold value. For example, if the threshold for the receive FIFO is 4 words, then the SONIC will always transfer 4 words from the receive FIFO to memory. If empty/fill mode is set, however, the number of bytes transferred is the number required to fill the transmit FIFO or empty the receive FIFO. More specific information about how the threshold affects reception and transmission of packets is discussed in Sections 1.4.1 and 1.4.2 below.

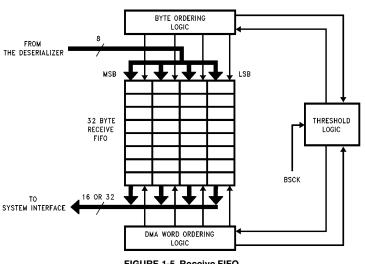

#### 1.4.1 Receive FIFO

To accommodate the different transfer rates, the receive FIFO (Figure 1-5) serves as a buffer between the 8-bit network (deserializer) interface and the 16/32-bit system interface. The FIFO is arranged as a 4-byte wide by 8 deep memory array (8 long words, or 32 bytes) controlled by three sections of logic. During reception, the Byte Ordering logic directs the byte stream from the deserializer into the FIFO using one of four write pointers. Depending on the selected byte-ordering mode, data is written either least significant byte first or most significant byte first to accommodate little or big endian byte-ordering formats respectively.

As data enters the FIFO, the Threshold Logic monitors the number of bytes written in from the deserializer. The programmable threshold (RFT1,0 in the Data Configuration Register) determines the number of words (or long words) written into the FIFO from the MAC unit before a DMA request for system memory occurs. When the threshold is reached, the Threshold Logic enables the Buffer Management Engine to read a programmed number of 16- or 32-bit words (depending upon the selected data width) from the FIFO and transfers them to the system interface (the system memory) using DMA. The threshold is reached when the number of bytes in the receive FIFO is greater than the value of the threshold. For example, if the threshold is 4 words (8 bytes), then the Threshold Logic will not cause the Buffer Management Engine to write to memory until there are more than 8 bytes in the FIFO.

The Buffer Management Engine reads either the upper or lower half (16 bits) of the FIFO in 16-bit mode or reads the complete long word (32 bits) in 32-bit mode. If, after the transfer is complete, the number of bytes in the FIFO is less then the threshold, then the SONIC is done. This is always the case when the SONIC is in empty/fill mode. If, however, for some reason (e.g. latency on the bus) the number of bytes in the FIFO is still greater than the threshold value, the Threshold Logic will cause the Buffer Management Engine to do a DMA request to write to memory again. This later case is usually only possible when the SONIC is in block mode.

When in block mode, each time the SONIC requests the bus, only a number of bytes equal to the threshold value will be transferred. The Threshold Logic continues to monitor

the number of bytes written in from the deserializer and enables the Buffer Management Engine every time the threshold has been reached. This process continues until the end of the packet.

Once the end of the packet has been reached, the serializer will fill out the last word (16-bit mode) or long word (32-bit mode) if the last byte did not end on a word or long word boundary respectively. The fill byte will be 0FFh. Immediately after the last byte (or fill byte) in the FIFO, the received packets status will be written into the FIFO. The entire packet, including any fill bytes and the received packet status will be buffered to memory. When a packet is buffered to memory by the Buffer Management Engine, it is always taken from the FIFO in words or long words and buffered to memory on word (16-bit mode) or long word (32-bit mode) boundaries. Data from a packet cannot be buffered on odd byte boundaries for 16-bit mode, and odd word boundaries for 32-bit mode (see Section 3.3). For more information on the receive packet buffering process, see Section 3.4.

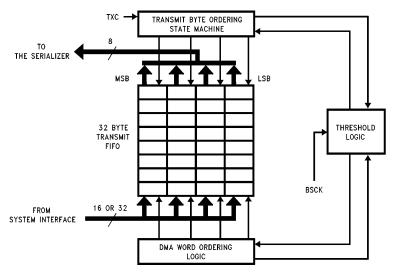

#### 1.4.2 Transmit FIFO

Similar to the Receive FIFO, the Transmit FIFO (Figure 1-6) serves as a buffer between the 16/32-bit system interface and the network (serializer) interface. The Transmit FIFO is also arranged as a 4 byte by 8 deep memory array (8 long words or 32 bytes) controlled by three sections of logic. Before transmission can begin, the Buffer Management Engine fetches a programmed number of 16- or 32-bit words from memory and transfers them to the FIFO. The Buffer Management Engine writes either the upper or lower half (16 bits) into the FIFO for 16-bit mode or writes the complete long word (32 bits) during 32-bit mode.

The Threshold logic monitors the number of bytes as they are written into the FIFO. When the threshold has been reached, the Transmit Byte Ordering state machine begins reading bytes from the FIFO to produce a continuous byte stream for the serializer. The threshold is met when the number of bytes in the FIFO is greater than the value of the threshold. For example, if the transmit threshold is 4 words (8 bytes), the Transmit Byte Ordering state machine will not begin reading bytes from the FIFO until there are 9 or more bytes in the buffer. The Buffer Management Engine continues replenishing the FIFO until the end of the packet. It does this by making multiple DMA requests to the system interface. Whenever the number of bytes in the FIFO is equal to or less than the threshold value, the Buffer Management Engine will do a DMA request. If block mode is set, then after each request has been granted by the system. the Buffer Management Engine will transfer a number of bytes equal to the threshold value into the FIFO. If empty/fill mode is set, the FIFO will be completely filled in one DMA request.

Since data may be organized in big or little endian byte ordering format, the Transmit Byte Ordering state machine uses one of four read pointers to locate the proper byte within the 4 byte wide FIFO. It also determines the valid number of bytes in the FIFO, For packets which begin or end at odd bytes in the FIFO, the Buffer Management Engine writes extraneous bytes into the FIFO. The Transmit Byte Ordering state machine detects these bytes and only transfers the valid bytes to the serializer. The Buffer Management Engine can read data from memory on any byte boundary (see Section 3.3). See Section 3.5 for more information on transmit buffering.

FIGURE 1-6. Transmit FIFO

TL/F/10492-7

#### 1.5 STATUS AND CONFIGURATION REGISTERS

The SONIC contains a set of status/control registers for conveying status and control information to/from the host system. The SONIC uses these registers for loading commands generated from the system, indicating transmit and receive status, buffering data to/from memory, and providing interrupt control. Each register is 16 bits in length. See Section 4.0 for a description of the registers.

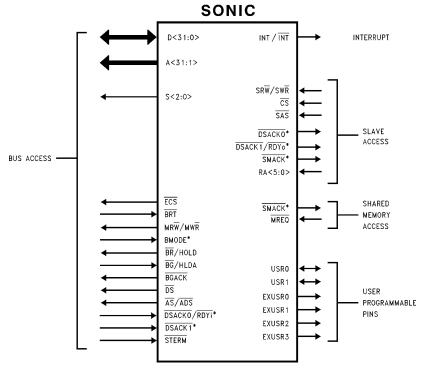

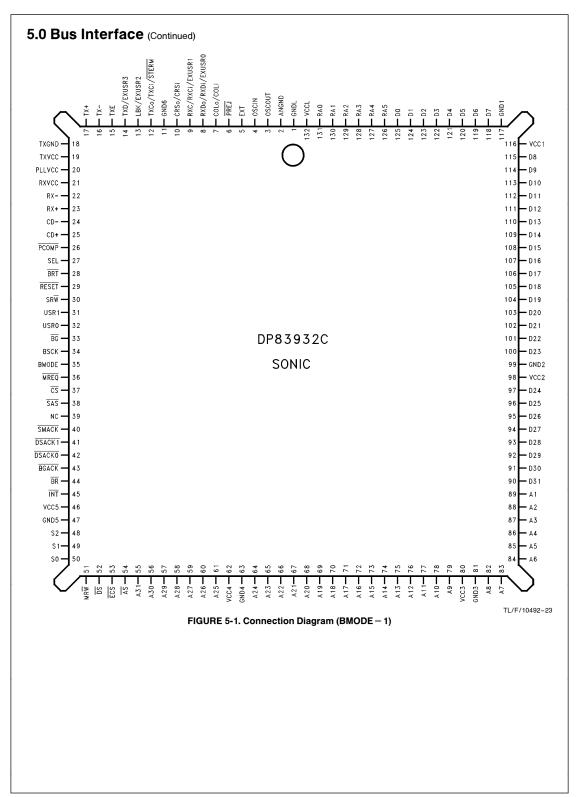

#### 1.6 BUS INTERFACE

The system interface (Figure 1-7) consists of the pins necessary for interfacing to a variety of buses. It includes the I/O drivers for the data and address lines, bus access control for standard microprocessors, ready logic for synchronous or asynchronous systems, slave access control, interrupt control, and shared-memory access control. The functional signal groups are shown in Figure 1-7. See Section 5.0 for a complete description of the SONIC bus interface.

### 1.7 LOOPBACK AND DIAGNOSTICS

The SONIC furnishes three loopback modes for self-testing from the controller interface to the transceiver interface. The loopback function is provided to allow self-testing of the chip's internal transmit and receive operations. During loopback, transmitted packets are routed back to the receive section of the SONIC where they are filtered by the address recognition logic and buffered to memory if accepted. Transmit and receive status and interrupts remain active during loopback. This means that when using loopback, it is as if the packet was transmitted and received by two separate chips that are connected to the same bus and memory.

MAC Loopback: Transmitted data is looped back at the MAC. Data is not sent from the MAC to either the internal ENDEC or an external ENDEC (the external ENDEC interface pins will not be driven), hence, data is not transmitted from the chip. Even though the ENDEC is not used in MAC loopback, the ENDEC clock (an oscillator or crystal for the

internal ENDEC or TXC for an external ENDEC) must be driven. Network activity, such as a collision, does not affect MAC loopback. CSMA/CD MAC protocol is not completely followed in MAC loopback.

**ENDEC Loopback:** Transmitted data is looped back at the ENDEC. If the internal ENDEC is used, data is switched from the transmit section of the ENDEC to the receive section (*Figure 1-2*). Data is not transmitted from the chip and the collision lines, CD±, are ignored, hence, network activity does not affect ENDEC loopback. The LBK signal from the MAC tells the internal ENDEC to go into loopback mode. If an external ENDEC is used, it should operate in loopback mode when the LBK signal is asserted. CSMA/CD MAC protocol is followed even though data is not transmitted from the chip.

**Transceiver Loopback:** Transmitted data is looped back at the external transceiver (which is always the case regardless of the SONIC's loopback mode). CSMA/CD MAC protocol is followed since data will be transmitted from the chip. This means that transceiver loopback is affected by network activity. In normal operations, the SONIC only monitors the packet that is looped back by the transceiver, but does not fill the receive FIFO and buffer the packet.

## 1.7.1 Loopback Procedure

The following procedure describes the loopback operation.

- Initialize the Transmit and Receive Area as described in Sections 3.4 and 3.5.

- Load one of the CAM address registers (see Section 4.1), with the Destination Address of the packet if you are verifying the SONIC's address recognition capability.

- Load one of the CAM address registers with the Source Address of the packet if it is different than the Destination Address to avoid getting a Packet Monitored Bad (PMB) error in the Transmit status (see Section 4.3.4).

- 4. Program the Receive Control register with the desired receive filter and the loopback mode (LB1, LB0).

- 5. Issue the transmit command (TXP) and enable the receiver (RXEN) in the Command register.

The SONIC completes the loopback operation after the packet has been completely received (or rejected if there is an address mismatch). The Transmit Control and Receive Control registers treat the loopback packet as in normal operation and indicate status accordingly. Interrupts are also generated if enabled in the Interrupt Mask register.

Note: For MAC Loopback, only one packet may be queued for proper operation. This restriction occurs because the transmit MAC section, which does not generate an Interframe Gap time (IFG) between transmitted packets, does not allow the receive MAC section to update receive status. There are no restrictions for the other loopback modes.

#### 1.8 NETWORK MANAGEMENT FUNCTIONS

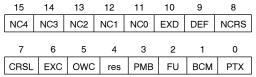

The SONIC fully supports the Layer Management IEEE 802.3 standard to allow a node to monitor the overall performance of the network. These statistics are available on a per packet basis at the end of reception or transmission. In addition, the SONIC provides three tally counters to tabulate CRC errors, Frame Alignment errors, and missed packets. Table 1-1 shows the statistics indicated by the SONIC.

TL/F/10492-8

\*Note: DSACK0,1 are used for both Bus and Slave Access Control and are bidirectional. SMACK is used for both Slave access and shared memory access. The BMODE pin selects between National/Intel or Motorola type buses.

FIGURE 1-7. SONIC Bus Interface Signals

**TABLE 1-1. Network Management Statistics**

| Statistic                                    | Register Used | Bits Used  |

|----------------------------------------------|---------------|------------|

| Frames Transmitted OK                        | TCR (Note)    | PTX        |

| Single Collision Frames                      | (Note)        | NC0-NC4    |

| Multiple Collision Frames                    | (Note)        | NC0-NC4    |

| Collision Frames                             | (Note)        | NC0-NC4    |

| Frames with Deferred Transmissions           | TCR (Note)    | DEF        |

| Late Collisions                              | TCR (Note)    | OWC        |

| Excessive Collisions                         | TCR (Note)    | EXC        |

| Excessive Deferral                           | TCR (Note)    | EXD        |

| Internal MAC Transmit Error                  | TCR (Note)    | BCM, FU    |

| Frames Received OK                           | RCR (Note)    | PRX        |

| Multicast Frames Received OK                 | RCR (Note)    | MC         |

| Broadcast Frames Received OK                 | RCR (Note)    | BC         |

| Frame Check Sequence Errors                  | CRCT<br>RCR   | All<br>CRC |

| Alignment Errors                             | FAET<br>RCR   | All<br>FAE |

| Frame Lost Due to Internal MAC Receive Error | MPT<br>ISR    | All<br>RFO |

**Note:** The number of collisions and the contents of the Transmit Control register are posted in the TXpkt.status field (see Section 3.5.1.2). The contents of the Receive Control register are posted in the RXpkt.status field (see Section 3.4.3).

## 2.0 Transmit/Receive IEEE 802.3 Frame Format

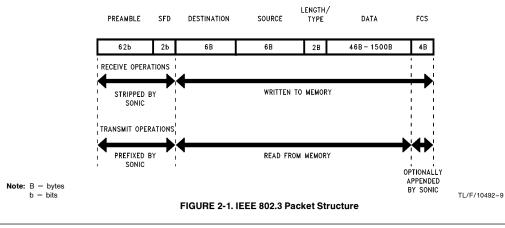

A standard IEEE 802.3 packet (Figure 2-1) consists of the following fields: preamble, Start of Frame Delimiter (SFD), destination address, source address, length, data and Frame Check Sequence (FCS). The typical format is shown in Figure 2-1. The packets are Manchester encoded and decoded by the ENDEC unit and transferred serially to/from the MAC unit using NRZ data with a clock. All fields are of fixed length except for the data field. The SONIC generates and appends the preamble, SFD and FCS field during transmission. The Preamble and SFD fields are stripped during reception. (The CRC is passed through to buffer memory during reception.)

# 2.1 PREAMBLE AND START OF FRAME DELIMITER (SFD)

The Manchester encoded alternating 1,0 preamble field is used by the ENDEC to acquire bit synchronization with an incoming packet. When transmitted, each packet contains 62 bits of an alternating 1,0 preamble. Some of this preamble may be lost as the packet travels through the network. Byte alignment is performed when the Start of Frame Delimiter (SFD) pattern, consisting of two consecutive 1's, is detected.

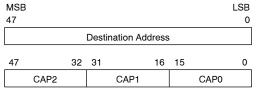

## 2.2 DESTINATION ADDRESS

The destination address indicates the destination of the packet on the network and is used to filter unwanted pack-

## 2.0 Transmit/Receive IEEE 802.3 Frame Format (Continued)

ets from reaching a node. There are three types of address formats supported by the SONIC: Physical, Multicast, and Broadcast.

Physical Address: The physical address is a unique address that corresponds only to a single node. All physical addresses have the LSB of the first byte of the address set to "0". These addresses are compared to the internally stored CAM (Content Addressable Memory) address entries. All bits in the destination address must match an entry in the CAM in order for the SONIC to accept the packet.

Multicast Address: Multicast addresses, which have the LSB of the first byte of the address set to "1", are treated similarly as Physical addresses, i.e., they must match an entry in the CAM. This allows perfect filtering of Multicast packets and eliminates the need for a hashing algorithm for mapping Multicast packets.

**Broadcast Address:** If the address consists of all 1's, it is a Broadcast address, indicating that the packet is intended for all nodes.

The SONIC also provides a promiscuous mode which allows reception of all physical address packets. Physical, Multicast, Broadcast, and promiscuous address modes can be selected via the Receive Control register.

#### 2.3 SOURCE ADDRESS

The source address is the physical address of the sending node. Source addresses cannot be multicast or broadcast addresses. This field must be passed to the SONIC's transmit buffer from the system software. During transmission, the SONIC compares the Source address with its internal CAM address entries before monitoring the CRC of the self-received packet. If the source address of the packet transmitted does not match a value in the CAM, the packet monitored bad flag (PMB) will be set in the transmit status field of the transmit descriptor (see Sections 3.5.1.2 and 4.3.4). The SONIC does not provide Source Address insertion. However, a transmit descriptor fragment, containing only the Source Address, may be created for each packet. (See Section 3.5.1.)

## 2.4 LENGTH/TYPE FIELD

For IEEE 802.3 type packets, this field indicates the number of bytes that are contained in the data field of the packet. For Ethernet I and II networks, this field indicates the type of packet. The SONIC does not operate on this field.

## 2.5 DATA FIELD

The data field has a variable octet length ranging from 46 to 1500 bytes as defined by the Ethernet specification. Messages longer than 1500 bytes need to be broken into multiple packets for IEEE 802.3 networks. Data fields shorter than 46 bytes require appending a pad to bring the complete frame length to 64 bytes. If the data field is padded, the number of valid bytes are indicated in the length field. The SONIC does not append pad bytes for short packets during transmission, nor check for oversize packets during reception. However, the user's driver software can easily append the pad by lengthening the TXpkt.pkt\_size field and TXpkt.frag\_size field(s) to at least 64 bytes (see Section 3.5.1). While the Ethernet specification defines the maximum number of bytes in the data field the SONIC can transmit and receive packets up to 64k bytes in length.

### 2.6 FCS FIELD

The Frame Check Sequence (FCS) is a 32-bit CRC field calculated and appended to a packet during transmission to allow detection of error-free packets. During reception, an error-free packet results in a specific pattern in the CRC

generator. The AUTODIN II  $(X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X^1 + 1)$  polynomial is used for the CRC calculations. The SONIC may optionally append the CRC sequence during transmission, and checks the CRC both during normal reception and self-reception during a transmission (see Section 1.2.1).

#### 2.7 MAC (MEDIA ACCESS CONTROL) CONFORMANCE

The SONIC is designed to be compliant to the IEEE 802.3 MAC Conformance specification. The SONIC implements most MAC functions in silicon and provides hooks for the user software to handle the remaining functions. The MAC Conformance specifications are summarized in Table 2-1.

**TABLE 2-1. MAC Conformance Specifications**

| Conformance                          |       | X 2 X X |       |

|--------------------------------------|-------|---------|-------|

| Conformance<br>Test Name             | SONIC |         | Notes |

| Minimum Frame Size                   | Х     |         |       |

| Maximum Frame Size                   | Х     | Х       | 1     |

| Address Generation                   | Х     | Х       | 2     |

| Address Recognition                  | Х     |         |       |

| Pad Length Generation                | Х     | Х       | 3     |

| Start Of Frame Delimiter             | Х     |         |       |

| Length Field                         | Х     |         |       |

| Preamble Generation                  | Х     |         |       |

| Order of Bit Transmission            | Х     |         |       |

| Inconsistent Frame Length            | Х     | Х       | 1     |

| Non-Integral Octet Count             | Х     |         |       |

| Incorrect Frame Check<br>Sequence    | Х     |         |       |

| Frame Assembly                       | Х     |         |       |

| FCS Generation and Insertion         | Х     |         |       |

| Carrier Deference                    | Х     |         |       |

| Interframe Spacing                   | Х     |         |       |

| Collision Detection                  | Х     |         |       |

| Collision Handling                   | Х     |         |       |

| Collision Backoff and Retransmission | х     |         |       |

| FCS Validation                       | Х     |         |       |

| Frame Disassembly                    | Х     |         |       |

| Back-to-Back Frames                  | Х     |         |       |

| Flow Control                         | Х     |         |       |

| Attempt Limit                        | Х     |         |       |

| Jam Size (after SFD)                 | Х     |         |       |

| Jam Size (in Preamble)               | Х     |         |       |

**Note 1:** The SONIC provides the byte count of the entire packet in the RXpkt.byte\_count (see Section 3.4.3). The user's driver software may perform further filtering of the packet based upon the byte count.

Note 2: The SONIC does not provide Source Address insertion; however, a transmit descriptor fragment, containing only the Source Address, may be created for each packet. See Section 3.5.1.

Note 3: The SONIC does not provide Pad generation; however, the user's driver software can easily append the Pad by lengthening the TXpkt\_pkt\_ size field and TXpkt.frag\_size field(s) to at least 64 bytes. See Section 3.5.1.

## 3.0 Buffer Management

# 3.1 BUFFER MANAGEMENT OVERVIEW

The SONIC's buffer management scheme is based on separate buffers and descriptors (Figures 3-2 and 3-11). Packets that are received or transmitted are placed in buffers called the Receive Buffer Area (RBA) and the Transmit Buffer Area (TBA). The system keeps track of packets in these buffers using the information in the Receive Descriptor Area (RDA) and the Transmit Descriptor Area (TDA). A single (TDA) points to a single TBA, but multiple RDAs can point to a single RBA (one RDA per packet in the buffer). The Receive Resource Area (RRA), which is another form of descriptor, is used to keep track of the actual buffer.

When packets are transmitted, the system sets up the packets in one or more TBAs with a TDA pointing to each TBA. There can only be one packet per TBA/TDA pair. A single TBA, however, may be made up of several fragments of data dispersed in memory. There is one TDA pointing to each TBA which specifies information about the buffer's size, location in memory, number of fragments and status after transmission. The TDAs are linked together in a linked list. The system causes the SONIC to transmit the packets by passing the first TDA to the SONIC and issuing the transmit command.

Before a packet can be received, an RDA and RBA must be set up by the system. RDA's are made up as a linked list similar to TDAs. An RDA is not linked to a particular RBA, though. Instead, an RDA is linked specifically to a packet after it has been buffered into an RBA. More than one packet can be buffered into the same RBA, but each packet gets its own RDA. A received packet can not be scattered into fragments. The system only needs to tell the SONIC where the first RDA and where the RBAs are. Since an RDA never specifically points to an RBA, the RRA is used to keep track of the RBAs. The RRA is a circular queue of pointers and buffer sizes (not a linked list). When the SONIC receives a packet, it is buffered into a RBA with a corresponding and unique RDA that is written to so that it points to and describes the new packet. If the RBA does not have enough space to buffer the next packet, a new RBA is obtained from the RRA.

## 3.2 DESCRIPTOR AREAS

Descriptors are the basis of the buffer management scheme used by the SONIC. A RDA points to a received packet within a RBA, RRA points to a RBA and a TDA points to a TBA which contains a packet to be transmitted. The conventions and registers used to describe these descriptors are discussed in the next three sections.

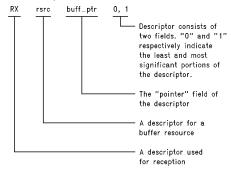

### 3.2.1 Naming Convention for Descriptors

The fields which make up the descriptors are named in a consistent manner to assist in remembering the usage of each descriptor. Each descriptor name consists of three components in the following format.

### [RX/TX][descriptor name].[field]

The first two capital letters indicate whether the descriptor is used for transmission (TX) or reception (RX), and is then followed by the descriptor name having one of two names.

rsrc = Resource descriptor

pkt = Packet descriptor

The last component consists of a field name to distinguish it from the other fields of a descriptor. The field name is separated from the descriptor name by a period ("."). An example of a descriptor is shown below.

TL/F/10492-86

#### 3.2.2 Abbreviations

The abbreviations in Table 3.1 are used to describe the SONIC registers and data structures in memory. The "0" and "1" in the abbreviations indicate the least and most significant portions of the registers or descriptors. Table 3-1 lists the naming convention abbreviations for descriptors.

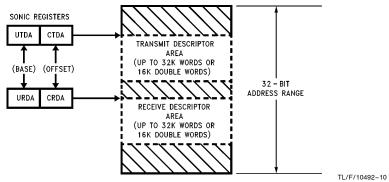

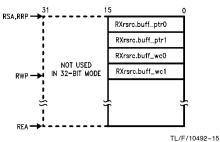

#### 3.2.3 Buffer Management Base Addresses

The SONIC uses three areas in memory to store descriptor information: the Transmit Descriptor Area (TDA), Receive Descriptor Area (RDA), and the Receive Resource Area (RRA). The SONIC accesses these areas by concatenating a 16-bit base address register with a 16-bit offset register. The base address register supplies a fixed upper 16 bits of address and the offset registers provide the lower 16 bits of address. The base address registers are the Upper Transmit Descriptor Address (UTDA), Upper Receive Descriptor Address (URDA), and the Upper Receive Resource Address (URRA) registers. The corresponding offset registers are shown below.

| Upper Address Registers | Offset Registers   |

|-------------------------|--------------------|

| URRA                    | RSA, REA, RWP, RRP |

| URDA                    | CRDA               |

| UTDA                    | CTDA               |

See Table 3-1 for definition of register mnemonics.

Figure 3-1 shows an example of the Transmit Descriptor Area and the Receive Descriptor Area being located by the UTDA and URDA registers. The descriptor areas, RDA, TDA, and RRA are allowed to have the same base address. i.e., URRA = URDA = UTDA. Care, however, must be taken to prevent these areas from overwriting each other.

**TABLE 3-1. Descriptor Abbreviations**

| TRANSMIT AN | TRANSMIT AND RECEIVE AREAS                      |  |  |  |  |

|-------------|-------------------------------------------------|--|--|--|--|

| RRA         | Receive Resource Area                           |  |  |  |  |

| RDA         | Receive Descriptor Area                         |  |  |  |  |

| RBA         | Receive Buffer Area                             |  |  |  |  |

| TDA         | Transmit Descriptor Area                        |  |  |  |  |

| TBA         | Transmit Buffer Area                            |  |  |  |  |

| BUFFER MAN  | AGEMENT REGISTERS                               |  |  |  |  |

| RSA         | Resource Start Area Register                    |  |  |  |  |

| REA         | Resource End Area Register                      |  |  |  |  |

| RRP         | Resource Read Pointer Register                  |  |  |  |  |

| RWP         | Resource Write Pointer Register                 |  |  |  |  |

| CRDA        | Current Receive Descriptor<br>Address Register  |  |  |  |  |

| CRBA0,1     | Current Receive Buffer Address<br>Register      |  |  |  |  |

| TCBA0,1     | Temporary Current Buffer Address<br>Register    |  |  |  |  |

| RBWC0,1     | Remaining Buffer Word Count<br>Register         |  |  |  |  |

| TRBWC0,1    | Temporary Remaining Buffer Word Count Register  |  |  |  |  |

| EOBC        | End of Buffer Count Register                    |  |  |  |  |

| TPS         | Transmit Packet Size Register                   |  |  |  |  |

| TSA0,1      | Transmit Start Address Register                 |  |  |  |  |

| CTDA        | Current Transmit Descriptor<br>Address Register |  |  |  |  |

| BUFFER MANAGEMENT REGISTERS (Continued) |                                               |  |  |  |  |  |

|-----------------------------------------|-----------------------------------------------|--|--|--|--|--|

| TFC                                     | Transmit Fragment Count Register              |  |  |  |  |  |

| TFS                                     | Transmit Fragment Size Register               |  |  |  |  |  |

| UTDA                                    | Upper Transmit Descriptor<br>Address Register |  |  |  |  |  |

| URRA                                    | Upper Receive Resource Address<br>Register    |  |  |  |  |  |

| URDA                                    | Upper Receive Descriptor Address<br>Register  |  |  |  |  |  |

| TRANSMIT AND RE                         | CEIVE DESCRIPTORS                             |  |  |  |  |  |

| RXrsrc.buffptr0,1                       | Buffer Pointer Field in the RRA               |  |  |  |  |  |

| RXrsrc.buff_wc0,1                       | Buffer Word Count Fields in the RRA           |  |  |  |  |  |

| RXpkt.status                            | Receive Status Field in the RDA               |  |  |  |  |  |

| RXpkt.bytecount                         | Packet Byte Count Field in the RDA            |  |  |  |  |  |

| RXpkt.buffptr0,1                        | Buffer Pointer Fields in the RDA              |  |  |  |  |  |

| RXpkt.link                              | Receive Descriptor Link Field in RDA          |  |  |  |  |  |

| RXpkt.in_use                            | "In Use" Field in RDA                         |  |  |  |  |  |

| TXpkt.fragcount                         | Fragment Count Field in TDA                   |  |  |  |  |  |

| TXpkt.pkt_size                          | Packet Size Field in TDA                      |  |  |  |  |  |

| TXpkt.pkt_ptr0,1                        | Packet Pointer Fields in TDA                  |  |  |  |  |  |

| TXpkt.frag_size                         | Fragment Size Field in TDA                    |  |  |  |  |  |

| TXpkt.link                              | Transmit Descriptor Link Field in TDA         |  |  |  |  |  |

FIGURE 3-1. Transmit and Receive Descriptor Pointers

14

## 3.3 DESCRIPTOR DATA ALIGNMENT

All fields used by descriptors (RXpkt.xxx, RXrsrc.xxx, and TXpkt.xxx) are word quantities (16-bit) and must be aligned to word boundaries (A0=0) for 16-bit memory and to long word boundaries (A1,A0=0,0) for 32-bit memory. The Receive Buffer Area (RBA) must also be aligned to a word boundary in 16-bit mode and a long word boundary in 32-bit mode. The fragments in the Transmit Buffer Area (TBA), however, may be aligned on any arbitrary byte boundary.

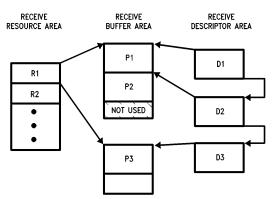

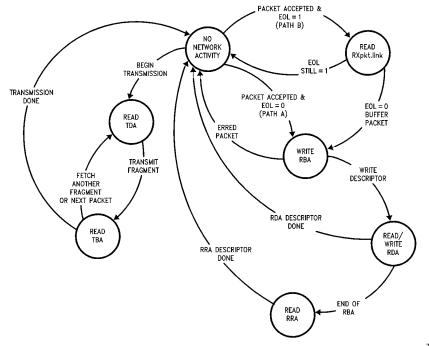

#### 3.4 RECEIVE BUFFER MANAGEMENT

The Receive Buffer Management operates on three areas in memory into which data, status, and control information are written during reception (Figure 3-2). These three areas must be initialized (Section 3.4.4) before enabling the receiver (setting the RXEN bit in the Command register). The receive resource area (RRA) contains descriptors that locate receive buffer areas in system memory. These descriptors are denoted by R1, R2, etc. in Figure 3-2. Packets (denoted by P1, P2, etc.) can then be buffered into the corresponding RBAs. Depending on the size of each buffer area and the size of the packet(s), multiple or single packets are buffered into each RBA. The receive descriptor area (RDA) contains status and control information for each packet (D1, D2, etc. in Figure 3-2) corresponding to each received packet (D1 goes with P1, D2 with P2, etc.).

When a packet arrives, the address recognition logic checks the address for a Physical, Multicast, or Broadcast match and if the packet is accepted, the SONIC buffers the packet contiguously into the selected Receive Buffer Area (RBA). Because of the previous end-of-packet processing, the SONIC assures that the complete packet is written into a single contiguous block. When the packet ends, the SONIC writes the receive status, byte count, and location of the packet into the Receive Descriptor Area (RDA). The SONIC then updates its pointers to locate the next available descriptor and checks the remaining words available in the RBA. If sufficient space remains, the SONIC buffers the next packet immediately after the previous packet. If the current buffer is out of space the SONIC fetches a Resource descriptor from the Receive Resource Area (RRA) acquiring an additional buffer that has been previously allocated by the system.

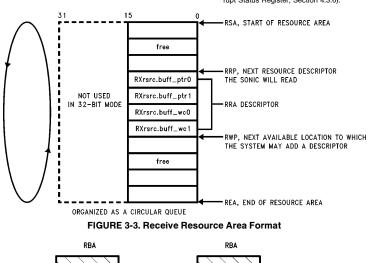

## 3.4.1 Receive Resource Area (RRA)

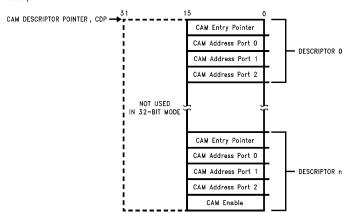

As buffer memory is consumed by the SONIC for storing data, the Receive Resource Area (RRA) provides a mechanism that allows the system to allocate additional buffer space for the SONIC. The system loads this area with resource descriptors that the SONIC, in turn, reads as its current buffer space is used up. Each resource descriptor consists of a 32-bit buffer pointer locating the starting point of the RBA and a 32-bit Word Count that indicates the size of the buffer in words (2 bytes per word). The buffer pointer and word count are contiguously located using the format shown in Figure 3-3 with each component composed of 16-bit fields. The SONIC stores this information internally and concatenates the corresponding fields to create 32-bit long words for the buffer pointer and word count. Note that in 32-bit mode the upper word (D<31:16>) is not used by the SONIC. This area may be used for other purposes since the SONIC never writes into the RRA.

The SONIC organizes the RRA as a circular queue for efficient processing of descriptors. Four registers define the RRA. The first two, the Resource Start Area (RSA) and the Resource End Area (REA) registers, determine the starting and ending locations of the RRA, and the other two registers update the RRA. The system adds descriptors at the address specified by the Resource Write Pointer (RWP), and the SONIC reads the next descriptor designated by the Resource Read Pointer (RRP). The RRP is advanced 4 words in 16-bit mode (4 long words in 32-bit mode) after the SONIC finishes reading the RRA and automatically wraps around to the beginning of the RRA once the end has been reached. When a descriptor in the RRA is read, the RXrsc.buff\_pt0,1 is loaded into the CRBA0,1 registers and the RXrsc.buff\_wc0,1 is loaded into the RBWC0,1 registers

The alignment of the RRA is confined to either word or long word boundaries, depending upon the data width mode. In 16-bit mode, the RRA must be aligned to a word boundary (A0 is always zero) and in 32-bit mode, the RRA is aligned to a long word boundary (A0 and A1 are always zero).

FIGURE 3-2. Overview of Receive Buffer Management

TL/F/10492-11

## 3.4.2 Receive Buffer Area (RBA)

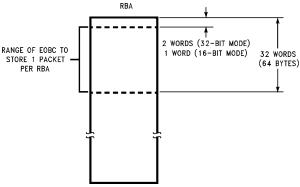

The SONIC stores the actual data of a received packet in the RBA. The RBAs are designated by the resource descriptors in the RRA as described above. The RXrsrc.buff\_ wc0,1 fields of the RRA indicate the length of the RBA. When the SONIC gets a RBA from the RRA, the RXrsrc.buff\_wc0,1 values are loaded into the Remaining Buffer Word Count registers (RBWC0,1). These registers keep track of how much space (in words) is left in the buffer. When a packet is buffered in a RBA, it is buffered contiguously (the SONIC will not scatter a packet into multiple buffers or fragments). Therefore, if there is not enough space left in a RBA after buffering a packet to buffer at least one more maximum sized packet (the maximum legal sized packet expected to be received from the network), a new buffer must be acquired. The End of Buffer Count (EOBC) register is used to tell the SONIC the maximum packet size that the SONIC will need to buffer.

### 3.4.2.1 End of Buffer Count (EOBC)

The EOBC is a boundary in the RBA based from the bottom of the buffer. The value written into the EOBC is the maximum expected size (in words) of the network packet that the SONIC will have to buffer. This word count creates a line in the RBA that, when crossed, causes the SONIC to fetch a new RBA resource from the RRA.

Note: The EOBC is a word count, not a byte count. Also, the value programmed into EOBC must be a double word (32-bit) quantity when the SONIC is in 32-bit mode (e.g. in 32-bit mode, EOBC should be set to 758 words, not 759 words even though the maximum size of an IEEE 802.3 packet is 759 words).

### 3.4.2.2 Buffering the Last Packet in an RBA

At the start of reception, the SONIC stores the packet beginning at the Current Receive Buffer Address (CRBA0.1) and continues until the reception is complete. Concurrent with reception, the SONIC decrements the Remaining Buffer Word Count (RBWC0,1) by one in 16-bit mode or by two in 32-bit mode. At the end of reception, if the packet has crossed the EOBC boundary, the SONIC knows that the next packet might not fit in the RBA. This check is done by comparing the RBWC0,1 registers with the EOBC. If RBWC0,1 is less than the EOBC (the last packet buffered has crossed the EOBC boundary), the SONIC fetches the next resource descriptor in the RRA. If RBWC0,1 is greater than or equal to the EOBC (the EOBC boundary has not been crossed) the next packet reception continues at the present location pointed to by CRBA0,1 in the same RBA. Figure 3-4 illustrates the SONIC's actions for (1) RBWC0,1 ≥ EOBC and (2) RBWC0,1 < EOBC. See Section 3.4.4.4 for specific information about setting the EOBC.

Note: It is important that the EOBC boundary be "crossed." In other words, case #1 in Figure 3-4 must exist before case #2 exists. If case #2 occurs without case #1 having occurred first, the test for RBWC0,1 < EOBC will not work properly and the SONIC will not fetch a new buffer. The result of this will be a buffer overflow (RBAE in the Interrupt Status Register, Section 4.3.6).

TL/F/10492-12

RBA

RBA

RBA

PACKET #1

PACKET #1

PACKET #2

EOBC

Case #1

(RBWC0,1  $\geq$  EOBC)

Case #2

(RBWC0,1  $\leq$  EOBC)

Case #1: SONIC buffers next packet in same RBA

Case #2: SONIC detects an exhausted RBA and will buffer the next packet in another RBA.

FIGURE 3-4. Receive Buffer Area

#### 3.4.3 Receive Descriptor Area (RDA)

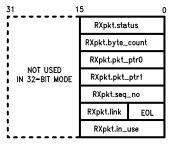

After the SONIC buffers a packet to memory, it writes 6 words of status and control information into the RDA, reads the link field to the next receive descriptor, and writes to the in-use field of the current descriptor. In 32-bit mode, the upper word, D<31:16>, is not used. This unused area in memory should not be used for other purposes, since the SONIC may still write into these locations. Each receive descriptor consists of the following sections (*Figure 3-5*).

TL/F/10492-14

FIGURE 3-5. Receive Descriptor Format

**receive status:** indicates status of the received packet. The SONIC writes the Receive Control register into this field. *Figure 3-6* shows the receive status format. This field is loaded from the contents of the Receive Control register. Note that ERR, RNT, BRD, PRO, and AMC are configuration bits and are programmed during initialization. See Section 4.3.3 for the description of the Receive Control register.

|     |      |     |     | 11   |      |     |     |

|-----|------|-----|-----|------|------|-----|-----|

| ERR | RNT  | BRD | PRO | AMC  | LB1  | LB0 | MC  |

| 7   | 6    | 5   | 4   | 3    | 2    | 1   | 0   |

| вс  | LPKT | CRS | COL | CRCR | FAER | LBK | PRX |

FIGURE 3-6. Receive Status Format

**byte count:** gives the length of the complete packet from the start of Destination Address to the end of FCS.

packet pointer: a 32-bit pointer that locates the packet in the RBA. The SONIC writes the contents of the CRBA0,1 registers into this field.

sequence numbers: this field displays the contents of two 8-bit counters (modulo 256) that sequence the RBAs used and the packets buffered. These counters assist the system in determining when an RBA has been completely processed. The sequence numbers allow the system to tally the packets that have been processed within a particular RBA. There are two sequence numbers that describe a packet: the RBA Sequence Number and the Packet Sequence Number. When a packet is buffered to memory, the SONIC maintains a single RBA Sequence Number for all packets in an RBA and sequences the Packet Number for succeeding packets in the RBA. When the SONIC uses the next RBA, it increments the RBA Sequence Number and clears the Packet Sequence Number. The RBA's sequence counter is not incremented when the read RRA command is issued in the Command register. The format of the Receive Sequence Numbers are shown in Figure 3-7. These counters are reset during hardware reset or by writing zero to them.

| 15             | 8                   | 7       | 0          |

|----------------|---------------------|---------|------------|

| RBA Sequence N | RBA Sequence Number |         | nce Number |

| (Modulo 256    | 3)                  | (Modulo | 256)       |

FIGURE 3-7. Receive Sequence Number Format

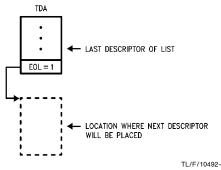

**receive link field:** a 15-bit pointer (A15-A1) that locates the next receive descriptor. The LSB of this field is the End Of List (EOL) bit, and indicates the last descriptor in the list. (Initialized by the system.)

in use field: this field provides a handshake between the system and the SONIC to indicate the ownership of the descriptor. When the system avails a descriptor to the SONIC, it writes a non-zero value into this field. The SONIC, in turn, sets this field to all "0's" when it has finished processing the descriptor. (That is, when the CRDA register has advanced to the next receive descriptor.) Generally, the SONIC releases control after writing the status and control information into the RDA. If, however, the SONIC has reached the last descriptor in the list, it maintains ownership of the descriptor until the system has appended additional descriptors to the list. The SONIC then relinquishes control after receiving the next packet. (See Section 3.4.6.1 for details on when the SONIC writes to this field). The receive packet descriptor format is shown in Figure 3-5.

#### 3.4.4 Receive Buffer Management Initialization

The Receive Resource, Descriptor, and Buffer areas (RRA, RDA, RBA) in memory and the appropriate SONIC registers must be properly initialized before the SONIC begins buffering packets. This section describes the initialization process.

## 3.4.4.1 Initializing The Descriptor Page

All descriptor areas (RRA, RDA, and TDA) used by the SONIC reside within areas up to 32k (word) or 16k (long word) pages. This page may be placed anywhere within the 32-bit address range by loading the upper 16 address lines into the UTDA, URDA, and URRA registers.

## 3.4.4.2 Initializing The RRA

The initialization of the RRA consists of loading the four SONIC RRA registers and writing the resource descriptor information to memory.

The RRA registers are loaded with the following values.

Resource Start Area (RSA) register: The RSA is loaded with the lower 16-bit address of the beginning of the RRA.

**Resource End Area (REA) register:** The REA is loaded with the lower 16-bit address of the end of the RRA. The end of the RRA is defined as the address of the last RXrsrc.ptr0 field in the RRA plus 4 words in 16-bit mode or 4 long words in 32-bit mode (*Figure 3-3*).

**Resource Read Pointer (RRP) register:** The RRP is loaded with the lower 16-bit address of the first resource descriptor the SONIC reads.

Resource Write Pointer (RWP) register: The RWP is loaded with the lower 16-bit address of the next vacant location where a resource descriptor will be placed by the system.

Note: The RWP register must only point to either (1) the RXrsrc.ptr0 field of one of the RRA Descriptors, (2) the memory address that the RSA points to (the start of the RRA), or (3) the memory address that the REA points to (the end of the RRA). When the RWP = RRP comparison is made, it is performed after the complete RRA descriptor has been read and not during the fetch. Failure to set the RWP to any of the above values prevents the RWP = RRP comparison from ever becoming true.

All RRA registers are concatenated with the URRA register for generating the full 32-bit address.

The resource descriptors that the system writes to the RRA consists of four fields: (1) RXrsrc.buff\_ptr0, (2) RXrsrc.buff\_ptr1, (3) RXrsrc.buff\_wc0, and (4) RXrsrc.buff\_wc1. The fields must be contiguous (they cannot straddle the end points) and are written in the order shown in *Figure 3-8*. The "0" and "1" in the descriptors denote the least and most significant portions for the Buffer Pointer and Word Count. The first two fields supply the 32-bit starting location of the Receive Buffer Area (RBA), and the second two define the number of 16-bit words that the RBA occupies.

Note that two restrictions apply to the Buffer Pointer and Word Count. First, in 32-bit mode, since the SONIC always writes long words, an even count must be written to RXrsrc.buff\_wc0. Second, the Buffer Pointer must either be pointing to a word boundary in 16-bit mode (A0=0) or a long word boundary in 32-bit mode (A0,A1=0,0). Note also that the descriptors must be properly aligned in the RRA as discussed in Section 3.3.

FIGURE 3-8. RRA Initialization

After configuring the RRA, the RRA Read command (setting RRRA bit in the Command register) may be given. This command causes the SONIC to read the RRA descriptor in a single block operation, and load the following registers (see Section 4.2 for register mnemonics):

CRBA0 register ← RXrsrc.buff\_ptr0

CRBA1 register ← RXrsrc.buff\_ptr1

RBWC0 register ← RXrsrc.buff\_wc0

RBWC1 register ← RXrsrc.buff\_wc1

When the command has completed, the RRRA bit in the Command register is reset to "0". Generally this command is only issued during initialization. At all other times, the RRA is automatically read as the SONIC finishes using an RBA.

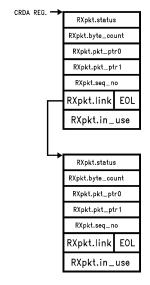

## 3.4.4.3 Initializing The RDA

To accept multiple packets from the network, the receive packet descriptors must be linked together via the RXpkt.link fields. Each link field must be written with a 15-bit (A15-A1) pointer to locate the beginning of the next descriptor in the list. The LSB of the RXpkt.link field is the End of List (EOL) bit and is used to indicate the end of the descriptor list. EOL = 1 for the last descriptor and EOL = 0 for the first or middle descriptors. The RXpkt.in\_use field indicates whether the descriptor is owned by the SONIC. The system writes a non-zero value to this field when the descriptor is available, and the SONIC writes all "0's" when it finishes using the descriptor. At startup, the Current Receive Descriptor Address (CRDA) register must be loaded with the address of the first RXpkt.status field in order for

the SONIC to begin receive processing at the first descriptor. An example of two descriptors linked together is shown in Figure 3-9. The fields initialized by the system are displayed in **bold type**. The other fields are written by the SONIC after a packet is accepted. The RXpktin\_use field is first written by the system, and then by the SONIC. Note that the descriptors must be aligned properly as discussed in Section 3.3. Also note that the URDA register is concatenated with the CRDA register to generate the full 32-bit address.

TL/F/10492-16

FIGURE 3-9. RDA Initialization Example

### 3.4.4.4 Initializing the Lower Boundary of the RBA

A "false bottom" is set in the RBA by loading the End Of Buffer Count (EOBC) register with a value equal to the maximum size packet in words (16 bits) that may be received. This creates a lower boundary in the RBA. Whenever the Remaining Buffer Word Count (RBWC0,1) registers decrement below the EOBC register, the SONIC buffers the next packet into another RBA. This also guarantees that a packet is always contiguously buffered into a single Receive Buffer Area (RBA). The SONIC does not buffer a packet into multiple RBAs. Note that in 32-bit mode, the SONIC holds the LSB always low so that it properly compares with the RBWC0,1 registers.

After a hardware reset, the EOBC reset, the EOBC register is automatically initialized to 2F8h (760 words or 1520 bytes). For 32-bit applications this is the suggested value for EOBC. EOBC defaults to 760 words (1520 bytes) instead of 759 words (1518 bytes) because 1518 is not a double word (32-bit) boundary (see Section 3.4.2.1). If the SONIC is used in 16-bit mode, then EOBC should be set to 759 words (1518 bytes) because 1518 is a word (16-bit) boundary.

Sometimes it may be desired to buffer a single packet per RBA. When doing this, it is important to set EOBC and the buffer size correctly. The suggested practice is to set EOBC to a value that is at least 4 bytes, in 32-bit mode, or 2 bytes, in 16-bit mode, less than the buffer size. An example of this for 32-bit mode is to set EOBC to 760 words (1520 bytes)

and the buffer size to 762 words (1524 bytes). A similar example for 16-bit mode would be EOBC =759 words (1518 bytes) and the buffer size set to 760 words (1520 bytes). The buffer can be any size, but as long as the EOBC is 2 words, for 32-bit mode, or 1 word, for 16-bit mode, less than the buffer size, only one packet will be buffered in that  $\rm RBA$

Note 1: It is possible to filter out most oversized packets by setting the buffer size to 760 words (1520 bytes) in 32-bit mode or 759 words (1518 bytes) in 16-bit mode. EOBC would be set to 758 words (1516 bytes) for both cases. With this configuration, any packet over 1520 bytes, in 32-bit mode, or 1518 bytes, in 16-bit mode, will not be completely buffered because the packet will overflow the buffer. When a packet overflow occurs, a Receive Buffer Area Exceeded interrupt (RBAE in the Interrupt Status Register, Section 4.3.6) will occur.

Note 2: When buffering one packet per buffer, it is suggested that the values in Note 1 above be used. Since the minimum legal sized Ethernet packet is 64 bytes, however, it is possible to set EOBC as much as 64 bytes less than the buffer size and still end up with one packet per buffer. Figure 3-10 shows this "range."

### 3.4.5 Beginning Of Reception

At the beginning of reception, the SONIC checks its internally stored EOL bit from the previous RXpkt.link field for a "1". If the SONIC finds EOL=1, it recognizes that after the previous reception, there were no more remaining receive packet descriptors. It re-reads the same RXpkt.link field to check if the system has updated this field since the last reception. If the SONIC still finds EOL=1, reception ceases. (See Section 3.5 for adding descriptors to the list.) Otherwise, the SONIC begins storing the packet in the RBA starting at the Current Receive Buffer Address (CRBA0,1) registers and continues until the packet has completed. Concurrent with the packet reception, the Remaining Buffer Word Count (RBWC0,1) registers are decremented after each word is written to memory. This register determines the remaining words in the RBA at the end of reception.

## 3.4.6 End Of Packet Processing

At the end of a reception, the SONIC enters its end of packet processing sequence to determine whether to accept or reject the packet based on receive errors and packet size. At the end of reception the SONIC enters one of the following two sequences:

- Successful reception sequence

- Buffer recovery for runt packets or packets with errors

#### 3.4.6.1 Successful Reception

If the SONIC accepts the packet, it first writes 5 words of descriptor information in the RDA beginning at the address pointed to by the Current Receive Descriptor Address (CRDA) register. It then reads the RXpkt.link field to advance the CRDA register to the next receive descriptor. The SONIC also checks the EOL bit for a "1" in this field. If EOL=1, no more descriptors are available for the SONIC. The SONIC recovers the address of the current RXpkt.link field (from a temporary register) and generates a "Receive Descriptors Exhausted" indication in the Interrupt Status register. (See Section 3.4.7 on how to add descriptors.) The SONIC maintains ownership of the descriptor by not writing to the RXpkt.in\_use field. Otherwise, if EOL=0, the SONIC advances the CRDA register to the next descriptor and resets the RXpkt.in\_use field to all "0's".

The SONIC accesses the complete 7 word RDA descriptor in a single block operation.

The SONIC also checks if there is remaining space in the RBA. The SONIC compares the Remaining Buffer Word Count (RBWC0,1) registers with the static End Of Buffer Count (EOBC). If the RBWC is less than the EOBC, a maximum sized packet will no longer fit in the remaining space in the RBA; hence, the SONIC fetches a resource descriptor from the RRA and loads its registers with the pointer and word count of the next available RBA.

# 3.4.6.2 Buffer Recovery For Runt Packets Or Packets With Errors

If a runt packet (less than 64 bytes) or packet with errors arrives and the Receive Control register has been configured to not accept these packets, the SONIC recovers its pointers back to the original positions. The CRBA0,1 registers are not advanced and the RBWC0,1 registers are not decremented. The SONIC recovers its pointers by maintaining a copy of the buffer address in the Temporary Receive Buffer Address registers (TRBA0,1). The SONIC recovers the value in the RBWC0,1 registers from the Temporary Buffer Word Count registers (TBWC0,1).

## 3.4.7 Overflow Conditions

When an overflow condition occurs, the SONIC halts its DMA operations to prevent writing into unauthorized memory. The SONIC uses the Interrupt Status register (ISR) to indicate three possible overflow conditions that can occur

TL/F/10492-17

Range of EOBC = (RXrsrc.wc0,1 - 2 to RXrsrc.wc0,1 - 32)

FIGURE 3-10. Setting EOBC for Single Packet RBA

when its receive resources have been exhausted. The system should respond by replenishing the resources that have been exhausted. These overflow conditions (Descriptor Resources Exhausted, Buffer Resources Exhausted, and RBA Limit Exceeded) are indicated in the Interrupt Status register and are detailed as follows:

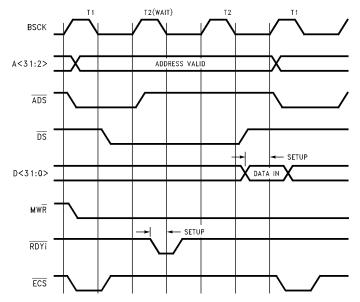

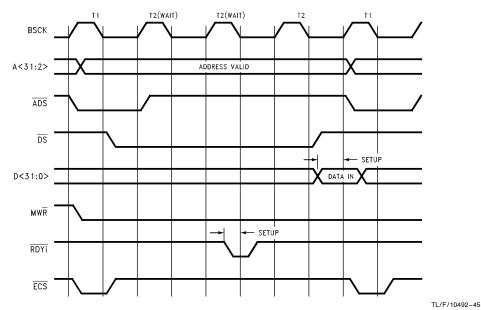

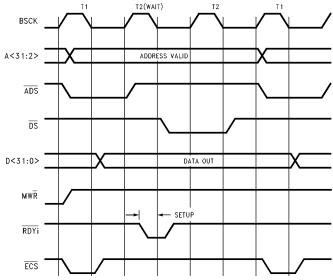

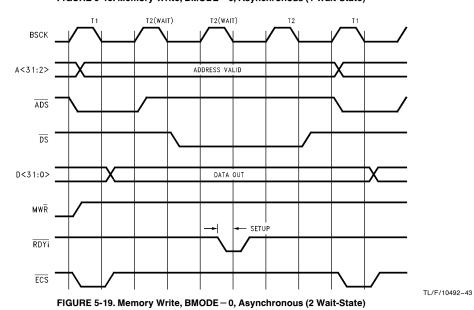

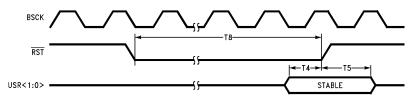

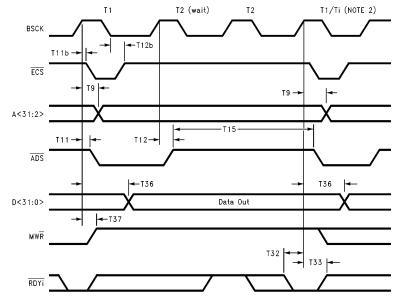

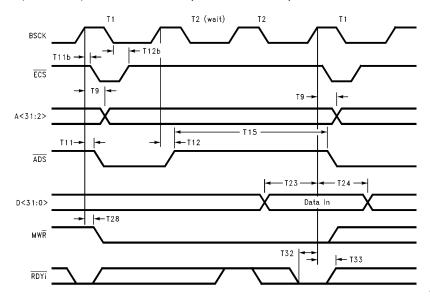

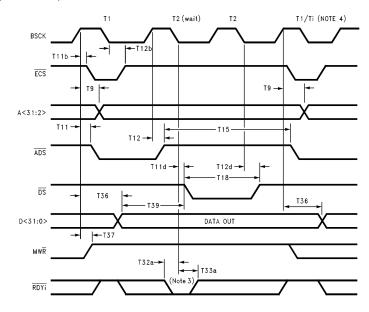

**Descriptor Resources Exhausted:** This occurs when the SONIC has reached the last receive descriptor in the list, meaning that the SONIC has detected EOL=1. The system must supply additional descriptors for continued reception. The system can do this in one of two ways: 1) appending descriptors to the existing list, or 2) creating a separate list.