## Linear Power PSoC™ Devices

## 1.0 Features

### 1.1 Key Features

- Extended Operating Voltage of 2.5V to 36V

- 2 HV Linear Opamp Control Loops for Driving Power PFETs

- 2 HV Analog Sense Inputs

- 4KB of Flash

- 256 Bytes of SRAM

### 1.2 Improved Features

- Very Low Current Mode for 100 nA Sleep (Deep Sleep)

- Analog Absolute Accuracy (0.75%)

- · Additional Flexibility for Sleep Modes

- 2 Comparators with DAC References

- 6- to 12-Bit ADC (20 Ksps at 8 Bits)

- Configurable Analog Mux, 10:1 or 5:2 Differential

- Configurable Digital Blocks

- 8- to 16-Bit Timers and Counters

- -Connectable to All GPIO Pins

- Digital Blocks can Drive Outputs to 36V

- Complex Peripherals by Combining Blocks

### 1.3 Applications

- Battery Chargers (Linear or Fly Back)

- White LED Drivers

- Temperature Sensor (Thermistor, Thermocouple)

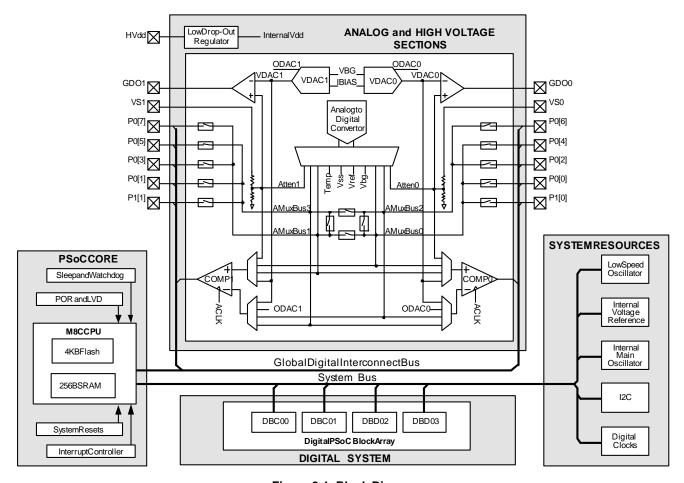

## 2.0 Block Diagram

Figure 2-1. Block Diagram

198 Champion Court

San Jose, CA 95134 • 408.943.2600 Revised November 17, 2005

### 3.0 Complete Feature List

- Extended Operating Voltage of 2.5V to 36V

- Powerful Harvard Architecture Processor

- M8C Processor Speeds to 24 MHz

- Low Power at High Speed

- Industrial Temperature Range: -40°C to +85°C

- Additional Flexibility for Sleep Modes

- Select when System Resources are Shut Down

- Very Low Current Mode for 100 nA Sleep (Deep Sleep)

- 2 Advanced Power PSoC Blocks

- 2 High Voltage Analog Sense Inputs

- 2 High Voltage Linear Opamp Control Loops for Driving Power PFETs

- · Advanced Analog Blocks

- Analog Absolute Accuracy (0.75%)

- 2 Comparators with DAC References

- -6- to 12-Bit ADC (20 Ksps at 8 Bits)

- Configurable Analog Mux, 10:1 or 5:2 Differential

- · 4 Advanced Digital Blocks

- 8- to 16-Bit Timers and Counters

- Connectable to All GPIO Pins

- Complex Peripherals by Combining Blocks

- Flexible On-Chip Memory

- 4KB Flash Program Storage 50,000 Erase/Write Cycles

- -256 Bytes SRAM

- In-System Serial Programming (ISSP™)

- Partial Flash Updates (64-Byte Blocks)

- Flexible Protection Modes

- EEPROM Emulation in Flash

- · Precision, Programmable Clocking

- Complete Development Tools

- Free Development Software (PSoC™ Designer)

- Full-Featured, In-Circuit Emulator and Programmer

- Full Speed Emulation

- Complex Breakpoint Structure

- 128KB Trace Memory

- Free Application Generation Software (PSoC Express™)

- · Additional System Resources

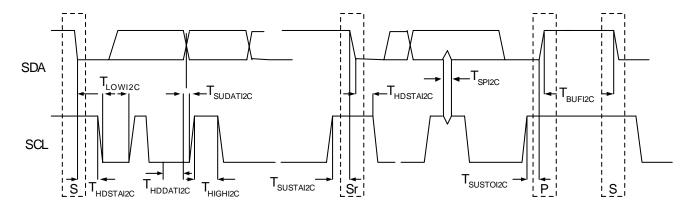

- I2C™ Master, Slave, and Multi-Master to 400 kHz

- Watchdog and Sleep Timers

- User-Configurable Low Voltage Detection

- Integrated Supervisory Circuit

- On-Chip Precision Voltage Reference

- -4-Bit Current References

#### 3.1 Differences from CY8C42x23

- The CY8C41x23 is a cost-reduced version of the CY8C42x23 and targets linear-control applications.

- The HVO pin and current DACs have been eliminated and the PWM with deadband capability has been removed from the digital blocks.

### 4.0 PSoC Functional Overview

The key feature set of the Linear Power PSoC family is the ability to be powered from and connect to voltages above the standard 5V logic voltage used by most microcontrollers. The PSoC's  ${\rm HV}_{\rm dd}$  pin can connect to a supply voltage of up to 36V. Internally, an LDO regulator converts the supply voltage to 5V for powering the analog system, digital system, the core, and the GPIO.

High voltage signals can be connected to the analog circuitry through one of two selectable attenuators, each having three ranges. These precision dividers reduce the external analog voltage by a factor of 4, 8, or 16. This allows single-ended or differential signals with up to 36V common mode to be measured with the ADC. The GPIO pins are not high-voltage tolerant. Signals with voltages exceeding V<sub>GPIO</sub> (as shown in the Absolute Maximum Ratings table, 8.2) **cannot** be connected to the GPIO pins (P0 [7:0] and P1 [1:0]). Doing so will damage the device.

The Linear Power PSoC family consists of several *Mixed-Signal Array with On-Chip Controller* devices. These devices are designed to replace multiple traditional MCU-based system components with one, low-cost single-chip programmable component. A Linear Power PSoC device includes configurable analog, digital, and power blocks, as well as programmable interconnects. This architecture allows the user to create customized peripheral configurations, to match the requirements of each individual application. Additionally, a fast CPU, Flash program memory, SRAM data memory, and configurable IO are included in a range of convenient pinouts.

The PSoC architecture, as illustrated in *Figure 2-1*, is comprised of five main areas: the Core, the System Resources, the Digital System, the Analog System, and the Power Control System. Configurable global bus resources allow all the device resources to be combined into a complete custom system. Each PSoC device includes 4 digital blocks and up to 10 general purpose IO (GPIO). The GPIO provide access to the global digital and analog interconnects.

#### 4.1 Linear Power PSoC Core

The Linear Power PSoC Core is a powerful engine that supports a rich instruction set. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers, and IMO (internal main oscillator) and ILO (internal low-speed oscillator). The CPU core, called the M8C, is a powerful processor with speeds up to 24 MHz. The M8C is a four MIPS 8-bit Harvard architecture microprocessor.

System Resources provide additional capability, such as digital clocks for increased flexibility of the PSoC mixed-signal arrays; I2C functionality for implementing master, slave, and multi-master; an internal voltage reference of 1.3V for a number of analog PSoC subsystems; and various system resets supported by the M8C.

### 4.2 Digital System

The Digital System is composed of 4 Basic (Type C) digital PSoC blocks. Each block is an 8-bit resource that can be used alone or combined with other blocks to form 8, 16, 24, and 32-bit peripherals, which are called user module references. A sampling of digital block configurations is listed below.

- Counters (8 to 32 bit)

- Timers (8 to 32 bit)

The digital blocks can be connected to any GPIO through a set of global buses that can route any signal to any pin. The buses also allow signal multiplexing and the combining of signals through logic operations. This configurability frees designs from the constraints of a fixed peripheral controller.

### 4.3 Multiple Sleep Modes

The CY8C41x23 devices can have some of the system resources (the SleepTimer/Watchdog Timer, the Voltage Regulator or the Power Supply Supervisor) powered down in order to achieve the desired level of sleep current. Sleep modes with current levels from 750  $\mu A$  in idle to 0.1  $\mu A$  in deep sleep, and wakeup times from instantaneous to 400  $\mu sec$  are available. Deeper sleep modes have longer wakeup times and sleep modes with more resource power typically have shorter wakeup times.

### 4.4 Analog System

The CY8C41x23 devices have solid analog performance, low (100  $\mu$ V) offsets, reduced temperature sensitivity, and are capable of measuring 0.75% absolute voltage accuracy.

The Analog System is composed of configurable blocks to allow creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Following are some of the more common PSoC analog functions (most available as user modules).

- Analog-to-digital converters (up to 12-bit resolution with single-ended or differential inputs).

- Adjustable input gain of 1/4, 1, 4, or 16 for the ADC.

- Pin-to-pin comparator with low power mode for operation during sleep.

- Single-ended or differential comparators (up to 2) with absolute (1.3V) reference or internal DAC reference.

- 1.3V reference (as a System Resource).

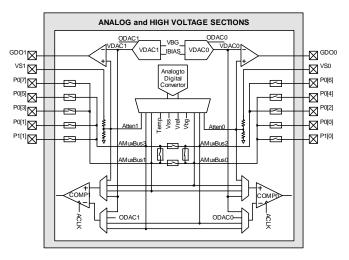

Figure 4-1. Analog Block Diagram

### 4.5 High Voltage Interface

The Gate Drive Outputs (GDO0 and GDO1) can each be used to drive the gate of a high-side PFET in a linear regulator. The GDO0 and GDO1 outputs will drive between  $HV_{dd}\text{-}5V$  and  $HV_{dd}\text{-}$  The Gate Drive Outputs are driven by an amplifier and used to control a PFET in a linear mode. A sense voltage can be fed back to the amplifier through an HV attenuator to implement a constant voltage or constant current driver. The output of the VDAC can be used to set the target voltage of the regulator.

### 4.6 The Analog Multiplexer System

The Analog Mux Bus can connect to every GPIO pin in ports P0 and P1. Pins can be connected to the bus individually or in any combination. The bus also connects to the analog system for analysis with comparators and analog-to-digital converters. This bus is split into four sections, AMux Bus 0 and AMux Bus 2, which connect to the even port pins and AMux Bus 1 and AMux Bus 3, which connect to the odd port pins.

The four sections can be combined to support dual-channel single-end processing, single-channel differential processing, or dual-channel differential processing. They can also be connected as one bus that can route to all GPIO pins.

Other multiplexer applications include:

- Chip-wide mux that allows analog input from up to 10 GPIO pins.

- Crosspoint connection between any GPIO pin combinations.

### 4.7 Additional System Resources

System Resources, some of which have been previously listed, provide additional capability useful to complete systems implemented in a single power block. Additional resources include an I2C master and slave, low voltage detection, and power on reset. Brief statements describing the merits of each system resource are presented below.

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks can be generated using digital PSoC blocks as clock dividers.

- The I2C module provides 50-, 100-, and 400-kHz communication over two wires. Slave, master, and multi-master modes are all supported.

- Low Voltage Detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced POR (Power On Reset) circuit eliminates the need for a system supervisor.

- An internal 1.3 voltage reference provides an absolute reference for the analog system, including ADCs and DACs.

### 4.8 Development Tools

- Standard Cypress PSoC IDE tools are available for debugging the CY8C41x23 family of parts. However, the additional trace length and a minimal ground plane in the Flexpod can create noise problems that make it difficult to debug a Power PSoC design. A custom bonded On-Chip Debug (OCD) device is available in an 32-pin QFN package. The OCD device is recommended for debugging designs that have high current and/or high analog accuracy requirements. The QFN package is compact and can be connected to the ICE through a high density connector.

- In-System Serial Programming (ISSP) is available. However, ISSP for Power PSoC differs from ISSP for standard PSoC devices. With Power PSoC devices, the power pin (HV<sub>dd</sub>) should not be connected directly to the V<sub>dd</sub> pin of the ISSP connector. Doing so can damage the programming device.

### 5.0 Typical Linear Power PSoC Applications

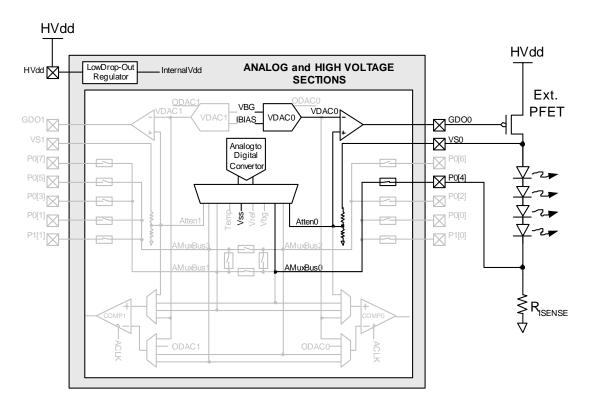

#### 5.1 Linear White LED Driver

A white LED driver is a constant current power supply. By driving the same current through a set of LEDs in series, the intensity of the LEDs can be closely matched. The CY8C41x23 Linear Power PSoC can be configured as a constant voltage or constant current linear supply. In this configuration, the HV<sub>dd</sub> voltage is high enough to drive the LEDs in series and current regulation is needed. White LEDs typically have a forward voltage of around 4V, so in the four LED configuration shown in *Figure 5-1*, HV<sub>dd</sub> would have to be around 16V (plus allowance for voltage losses in the FET and the current sense resistor, R<sub>ISENSE</sub>). The HV<sub>dd</sub> voltage is converted to 5V by the internal Low Drop-Out Regulator for use by the Power PSoC Core.

To maintain constant voltage, the gate of the External PFET is controlled by the GDO0 pin and driven in a linear mode. The voltage at the top of the load, connected to VS0, is attenuated by the internal resistive element, Atten0. The voltage out of the attenuator is fed into the positive terminal of an amplifier configured as a voltage follower. The amplifier's negative input is connected to the output of the voltage DAC, VDAC0. This creates a feedback loop that maintains the VS0 node at a voltage proportional to the VDAC0 setting. The Atten0 output is also connected to the ADC so the control software can monitor the output voltage.

To maintain constant current, the voltage across the  $R_{\mathsf{ISENSE}}$  resistor is routed through pin P0[4] and AMuxBus0 to the ADC where it is monitored. The control software adjusts the VDAC0 setting, based on current sense measurements, to achieve the desired current through the load.

#### 5.1.1 Resources

This application could connect the R<sub>ISENSE</sub> resistor to any of the GPIO pins (P0[7:0] and P1[1:0]). The Linear Power PSoC still has all of its digital resources, half of the high voltage resources, one VDAC, two IDACs, seven of the analog multiplexer channels to the ADC, and over 90% of the CPU available for other tasks.

Figure 5-1. Linear White LED Driver

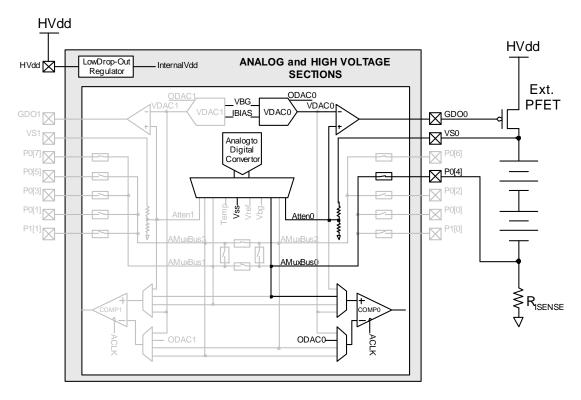

### 5.2 Linear Battery Charger

A battery charger is constant current and constant voltage power supply. At different points in a charging cycle a Lithium Ion battery requires a constant current or a constant voltage to be applied. The CY8C41x23 Linear Power PSoC can be configured as a constant voltage or constant current linear supply. In this configuration, the HV<sub>dd</sub> voltage is high enough to drive one or more battery in series. Lithium Ion batteries have a fully charged voltage of 4.2V. With the two-cell configuration in *Figure 5-2*, HV<sub>dd</sub> would have to be at least 8.4V (plus allowance for voltage losses in the FET and the current sense resistor, R<sub>ISENSE</sub>). The HV<sub>dd</sub> voltage is converted to 5V by the internal Low Drop-Out Regulator for use by the Power PSoC Core.

To maintain constant voltage, the gate of the External PFET is controlled by the GDO0 pin and driven in a linear mode. The voltage at the top of the load, connected to VS0, is attenuated by the internal resistive element, Atten0. The voltage out of the attenuator is fed into the positive terminal of an amplifier configured as a voltage follower. The amplifier's negative input is connected to the output of the voltage DAC, VDAC0. This creates a feedback loop that maintains the VS0 node at a voltage proportional to the VDAC0 setting. The Atten0 output is also connected to the ADC so the control software can monitor the output voltage. The accuracy of the ADC and the control loop are better than 0.75%. Meeting high accuracy is critical to Lithium Ion batteries.

To maintain constant current, the voltage across the R<sub>ISENSE</sub> resistor is routed through pin P0[4] and AMuxBus0 to the ADC where it is monitored. The control software adjusts the VDAC0 setting, based on current sense measurements, to achieve the desired current through the load. The current sense voltage is also connected to the positive input of COMP0. The negative input of COMP0 is controlled by the output of ODAC0. If the current sense voltage exceeds the ODAC0 setting, the output of the comparator will be latched high. This acts as an over-current detection circuit, which can be cleared by the control software. The output of the comparator, COMP0, can be connected to the enable of the GDO0 output driver. This configures the Power PSoC so that an over-current condition will shut off the External PFET.

#### 5.2.1 Resources

This application could connect the R<sub>ISENSE</sub> resistor to any of the GPIO pins (P0[7:0] and P1[1:0]). The Linear Power PSoC still has all of its digital resources, half of the high voltage resources, one VDAC, two IDACs, seven of the analog multiplexer channels to the ADC, and over 90% of the CPU available to implement the battery charging algorithm and other tasks.

Figure 5-2. Linear Battery Charger

### 6.0 Pin Assignment

This section lists, describes, and illustrates all Linear Power PSoC device pins and pinout configurations. For up-to-date ordering, pinout, and packaging information, go to http://www.cypress.com/psoc.

### 6.1 Pinouts

PSoC devices are available in a variety of packages. Refer to the following information for details on individual devices. Every port pin (labeled with a "P") in the following tables and illustrations is capable of digital IO.

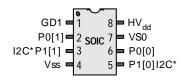

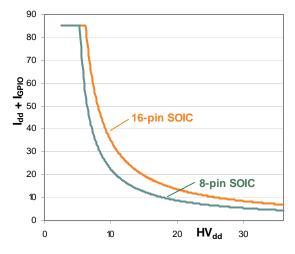

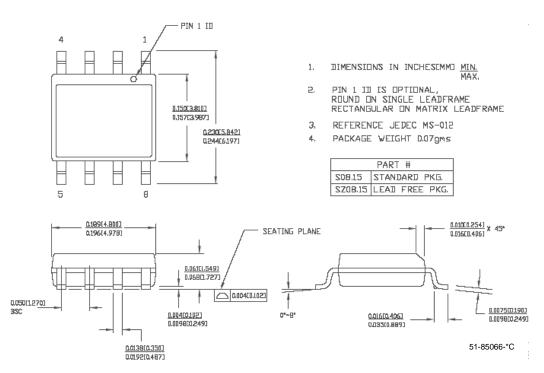

### 6.1.1 8-Pin SOIC Part Pinouts

The 8-pin SOIC part is for the CY8C41123 PSoC device.

## 8-Pin Part Pinout (SOIC)

| Pin<br>No. | Digital | Analog | Name             | Description                    |

|------------|---------|--------|------------------|--------------------------------|

| 1          |         | HVO    | GD1              | High Side Linear Gate Driver 1 |

| 2          | Ю       | I      | P0[1]            |                                |

| 3          | Ю       | I      | P1[1]            | I2C Clock*                     |

| 4          | Pov     | wer    | Vss              | Ground Connection              |

| 5          | Ю       | I      | P1[0]            | I2C Data*                      |

| 6          | Ю       | I      | P0[0]            |                                |

| 7          |         | HVI    | VS0              | High Voltage Sense 0           |

| 8          | Power I |        | HV <sub>dd</sub> | Supply Voltage                 |

### CY8C41123 PSoC Device

**LEGEND** I = Input 5V Only, O = Output 5V Only, HV = High Voltage.

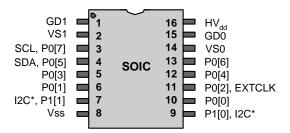

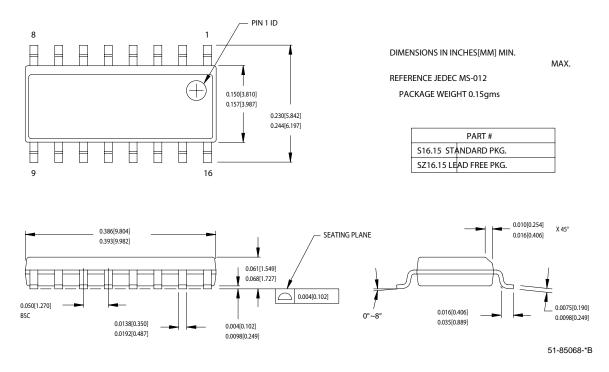

### 6.1.2 16-Pin SOIC Part Pinouts

The 16-pin SOIC part is for the CY8C41223 PSoC device.

## 16-Pin Part Pinout (SOIC)

| Pin<br>No. | Digital | Analog | Name      | Description                          |  |  |

|------------|---------|--------|-----------|--------------------------------------|--|--|

| 1          |         | HVO    | GD1       | High Side Linear Gate Driver 1       |  |  |

| 2          |         | HVI    | VS1       | High Voltage Sense 1                 |  |  |

| 3          | Ю       | ı      | P0[7]     | I2C Clock                            |  |  |

| 4          | 10      | I      | P0[5]     | I2C Data                             |  |  |

| 5          | 10      | I      | P0[3]     |                                      |  |  |

| 6          | Ю       | ı      | P0[1]     |                                      |  |  |

| 7          | Ю       | ı      | P1[1]     | I2C Clock*                           |  |  |

| 8          | Pov     | wer    | Vss       | Ground Connection                    |  |  |

| 9          | Ю       | I      | P1[0]     | I2C Data*                            |  |  |

| 10         | Ю       | I      | P0[0]     |                                      |  |  |

| 11         | Ю       | I      | P0[2]     | Optional External CLK Input (EXTCLK) |  |  |

| 12         | Ю       | ı      | P0[4]     |                                      |  |  |

| 13         | Ю       | ı      | P0[6]     |                                      |  |  |

| 14         |         | HVI    | VS0       | High Voltage Sense 0                 |  |  |

| 15         |         | HVO    | GD0       | High Side Linear Gate Driver 0       |  |  |

| 16         | Pov     | wer    | $HV_{dd}$ | Supply Voltage                       |  |  |

#### CY8C41223 PSoC Device

$\textbf{LEGEND} \ \ I = Input \ 5V \ Only, \ O = Output \ 5V \ Only, \ HV = High \ Voltage.$

<sup>\*</sup> These are the ISSP pins, which are not HighZ at POR (Power On Reset). See the Power PSoC Mixed-Signal Array Technical Reference Manual for details.

<sup>\*</sup> These are the ISSP pins, which are not HighZ at POR (Power On Reset). See the Power PSoC Mixed-Signal Array Technical Reference Manual for details.

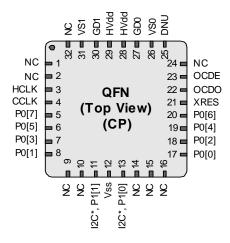

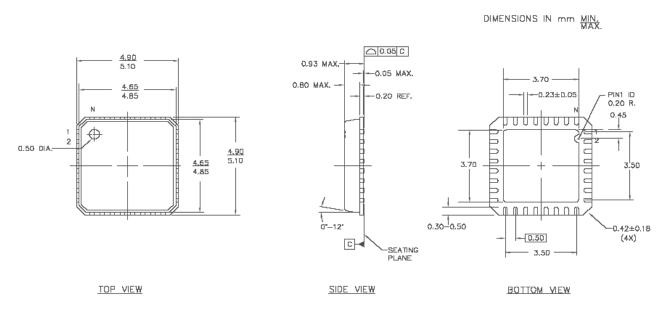

#### 6.1.3 32-Pin QFN Part Pinouts

The 32-pin QFN part is for the CY8C41000 On-Chip Debug (OCD) PSoC device.

Note This part is only used for in-circuit debugging. It is NOT available for production.

## 32-Pin OCD Part Pinout (QFN\*\*)

|            | īā      | log    |           |                                        |

|------------|---------|--------|-----------|----------------------------------------|

| Pin<br>No. | Digital | Analog | Name      | Description                            |

| 1          |         |        | NC        | No Connection                          |

| 2          |         |        | NC        | No Connection                          |

| 3          | OCD     |        | HCLK      | On-Chip Debug Clock                    |

| 4          | OCD     |        | CCLK      | On-Chip Debug Clock                    |

| 5          | Ю       | I      | P0[7]     | I2C Clock                              |

| 6          | Ю       | I      | P0[5]     | I2C Data                               |

| 7          | Ю       | I      | P0[3]     |                                        |

| 8          | Ю       | I      | P0[1]     |                                        |

| 9          |         |        | NC        | No Connection                          |

| 10         |         |        | NC        | No Connection                          |

| 11         | Ю       | I      | P1[1]     | I2C Clock*                             |

| 12         | Pov     | wer    | Vss       |                                        |

| 13         | Ю       | I      | P1[0]     | I2C Data*                              |

| 14         |         |        | NC        | No Connection                          |

| 15         |         |        | NC        | No Connection                          |

| 16         |         |        | NC        | No Connection                          |

| 17         | Ю       | _      | P0[0]     |                                        |

| 18         | Ю       | _      | P0[2]     | Optional External CLK Input (EXTCLK)   |

| 19         | Ю       | _      | P0[4]     |                                        |

| 20         | Ю       | _      | P0[6]     |                                        |

| 21         | I       |        | XRES      | External Reset                         |

| 22         | OCD     |        | OCDO      | On-Chip Debug Data                     |

| 23         | OCD     |        | OCDE      | On-Chip Debug Data                     |

| 24         |         |        | NC        | No Connection                          |

| 25         |         |        | DNU       | Do Not Use                             |

| 26         |         | HVI    | VS0       | High Voltage Sense 0                   |

| 27         | HVO     | HVO    | GD0       | High Side Gate Driver 0                |

| 28         | Pov     | wer    | $HV_{dd}$ | Supply Voltage                         |

| 29         | Pov     | wer    | $HV_{dd}$ | Supply Voltage                         |

| 30         | HVO     | HVO    | GD1       | High Side Gate Driver 1                |

| 31         |         | HVI    | VS1       | High Voltage Sense 1                   |

| 32         |         |        | NC        | No Connection                          |

| СР         | Pov     | wer    | Vss       | Center Pad Must be Connected to Ground |

### CY8C41000 OCD PSoC Device

**Not for Production**

LEGEND I = Input 5V Only, O = Output 5V Only, HV = High Voltage, NC = No Connection, OCD = On-Chip Debug.

**Important Note** For information on the preferred dimensions for mounting QFN packages, see the following Application Note at <a href="http://www.amkor.com/products/notes\_papers/MLFAppNote.pdf">http://www.amkor.com/products/notes\_papers/MLFAppNote.pdf</a>.

<sup>\*</sup> These are the ISSP pins, which are not HighZ at POR (Power On Reset). See the Power PSoC Mixed-Signal Array Technical Reference Manual for details.

<sup>\*\*</sup> The QFN package has a center pad that must be connected to ground (Vss).

## 7.0 Registers

This section discusses the registers of the Power PSoC device. It lists all the registers in mapping tables, in address order.

## 7.1 Register Conventions

The register conventions specific to this section are listed in the following table.

| Convention | Description                  |

|------------|------------------------------|

| R          | Read register or bit(s)      |

| W          | Write register or bit(s)     |

| L          | Logical register or bit(s)   |

| С          | Clearable register or bit(s) |

| #          | Access is bit specific       |

## 7.2 Register Map Bank 0 Table: User Space

|                      | Addr     |                                                  | U Table: U          | Addr     |          | Nama              | Addr     | <b>4</b> | Nama     | Addr     |        |

|----------------------|----------|--------------------------------------------------|---------------------|----------|----------|-------------------|----------|----------|----------|----------|--------|

| Name                 | (0,Hex)  | Access                                           | Name                | (0,Hex)  | Access   | Name              | (0,Hex)  | Access   | Name     | (0,Hex)  | Access |

| PRT0DR               | 00       | RW                                               |                     | 40       |          |                   | 80       |          |          | C0       |        |

| PRT0IE               | 01       | RW                                               |                     | 41       |          |                   | 81       |          |          | C1       |        |

| PRT0GS               | 02       | RW                                               |                     | 42       |          |                   | 82       |          |          | C2       |        |

| PRT0DM2              | 03       | RW                                               |                     | 43       |          |                   | 83       |          |          | C3       |        |

| PRT1DR               | 04       | RW                                               |                     | 44       |          | ASC00CR0          | 84       | RW       |          | C4       |        |

| PRT1IE               | 05       | RW                                               |                     | 45       |          | ASC00CR1          | 85       | RW       |          | C5       |        |

| PRT1GS               | 06       | RW                                               |                     | 46       |          | ASC00CR2          | 86       | RW       |          | C6       |        |

| PRT1DM2              | 07       | RW                                               |                     | 47       |          | ASC00CR3          | 87       | RW       | IDAC_D   | C7       | RW     |

| HVP2_DR              | 08       | RW                                               |                     | 48       |          | ASC01CR0          | 88       | RW       | P0_MUX   | C8       | RW     |

|                      | 09       |                                                  |                     | 49       |          | ASC01CR1          | 89       | RW       | P1_MUX   | C9       | RW     |

|                      | 0A       |                                                  |                     | 4A       |          | ASC01CR2          | 8A       | RW       |          | CA       | _      |

|                      | 0B       |                                                  |                     | 4B       |          | ASC01CR3          | 8B       | RW       |          | СВ       |        |

|                      | 0C       |                                                  |                     | 4C       |          |                   | 8C       |          |          | CC       |        |

|                      | 0D       |                                                  |                     | 4D       |          |                   | 8D       |          |          | CD       | _      |

|                      | 0E       |                                                  |                     | 4E       |          |                   | 8E       |          |          | CE       |        |

|                      | 0F       |                                                  |                     | 4F       |          |                   | 8F       |          |          | CF       |        |

|                      | 10       |                                                  |                     | 50       |          |                   | 90       |          |          | D0       |        |

|                      | 11       |                                                  |                     | 51       |          |                   | 91       |          |          | D1       |        |

|                      | 12       |                                                  |                     | 52       |          |                   | 92       |          |          | D2       |        |

|                      | 13       |                                                  |                     | 53       |          |                   | 93       |          |          | D3       |        |

|                      | 14       |                                                  |                     | 54       |          |                   | 94       |          |          | D4       |        |

|                      | 15       |                                                  |                     | 55       |          |                   | 95       |          |          | D5       |        |

|                      | 16       |                                                  |                     | 56       |          |                   | 96       |          | I2C_CFG  | D6       | RW     |

|                      | 17       |                                                  |                     | 57       |          |                   | 97       |          | I2C_SCR  | D7       | #      |

|                      | 18       |                                                  |                     | 58       |          |                   | 98       |          | I2C_DR   | D8       | RW     |

|                      | 19       |                                                  |                     | 59       |          |                   | 99       |          | I2C_MSCR | D9       | #      |

|                      | 1A       |                                                  |                     | 5A       |          |                   | 9A       |          | INT_CLR0 | DA       | RW     |

|                      | 1B       |                                                  |                     | 5B       |          |                   | 9B       |          | INT_CLR1 | DB       | RW     |

|                      | 1C       |                                                  |                     | 5C       |          |                   | 9C       |          | INT_CLR2 | DC       | RW     |

|                      | 1D       |                                                  |                     | 5D       |          |                   | 9D       |          | INT_CLR3 | DD       | RW     |

|                      | 1E       |                                                  |                     | 5E       |          |                   | 9E       |          | INT_MSK3 | DE       | RW     |

|                      | 1F       |                                                  |                     | 5F       |          |                   | 9F       |          | INT_MSK2 | DF       | RW     |

| DBC00DR0             | 20       | R                                                | AC0_MUX             | 60       | RW       | PWR0_CR           | A0       | RW       | INT_MSK0 | E0       | RW     |

| DBC00DR1             | 21       | W                                                | AC0_CR0             | 61       | RW       | PWR1_CR           | A1       | RW       | INT_MSK1 | E1       | RW     |

| DBC00DR2             | 22       | RW                                               | AC0_CR1             | 62       | RW       |                   | A2       |          | INT_VC   | E2       | RC     |

| DBC00CR0             | 23       | RW                                               | AC0_CR2             | 63       | RW       | ** 555            | A3       | DIA.     | RES_WDT  | E3       | W      |

| DBC01DR0             | 24       | R                                                | AC0_MSP             | 64       | RW       | AA_REF            | A4       | RW       |          | E4       |        |

| DBC01DR1             | 25       | W                                                | AC0_LSP             | 65       | RW       |                   | A5       |          |          | E5       |        |

| DBC01DR2             | 26       | RW                                               | AC0_MSR             | 66       | RW       | VD40.0D           | A6       | DW       |          | E6       | +      |

| DBC01CR0             | 27       | RW                                               | AC0_LSR             | 67       | RW       | VDAC_CR           | A7       | RW       |          | E7       |        |

| DBD02DR0             | 28       | R                                                | AC0_CC              | 68       | #        | VDAC_DR0          | A8       | RW       |          | E8       |        |

| DBD02DR1             | 29       | W                                                |                     | 69       |          | VDAC_DR1          | A9       | RW       |          | E9       | +      |

| DBD02DR2             | 2A       | RW                                               |                     | 6A       |          |                   | AA<br>AB |          |          | EA       | +      |

| DBD02CR0             | 2B       | RW                                               | TMD DD0             | 6B       | DW       |                   |          |          |          | EB       | +      |

| DBD03DR0<br>DBD03DR1 | 2C<br>2D | R<br>W                                           | TMP_DR0             | 6C<br>6D | RW<br>RW |                   | AC<br>AD |          |          | EC<br>ED | +      |

| DBD03DR1<br>DBD03DR2 | 2E       | RW                                               | TMP_DR1 TMP_DR2     | 6E       | RW       |                   | AE       |          |          |          | +      |

|                      |          | RW                                               |                     | 6E<br>6F | RW       |                   | AF       |          |          | EE<br>EF | 1      |

| DBD03CR0             | 2F       | IT.VV                                            | TMP_DR3 CMP_SYN     | 70       | RW       | RDIORI            | B0       | RW       |          | F0       | +      |

|                      | 30       |                                                  | CMP_SYN CMP LFN0    | 70       | RW       | RDIOSYN           | B1       | RW       |          | F1       | +      |

|                      | 32       | <del>                                     </del> | OIVIF_LFINU         | 71       | 1744     | RDI0SYN<br>RDI0IS | B2       | RW       |          | F1<br>F2 | +      |

|                      | 33       |                                                  | CMP_LMD             | 73       | RW       | RDIOLTO           | B3       | RW       |          | F3       | +      |

|                      | 34       |                                                  | CMP_LMD CMP_CDS     | 74       | RW       | RDIOLT1           | B4       | RW       |          | F4       | +      |

|                      | 35       |                                                  | CMP_CIS             | 75       | RW       | RDI0RO0           | B5       | RW       |          | F5       | +      |

|                      | 36       |                                                  | CMP_RDC             | 76       | RW       | RDI0RO1           | B6       | RW       |          | F6       | +      |

|                      | 37       | 1                                                | CMP_RDC CMP_GOEN0   | 77       | RW       | RDI0RO1           | B7       | RW       | CPU_F    | F7       | RL     |

|                      | 38       |                                                  | CIVIF_GOEINU        | 78       | 1///     | KDIOGI            | B8       | 1744     | OF U_I   | F8       | +INL   |

|                      | 39       | 1                                                | CMP CLK             | 79       | RW       |                   | В9       | -        |          | F9       | +      |

|                      | 39<br>3A |                                                  | CMP_CLK CMP CR      | 79<br>7A | RW       |                   | BA       |          |          | FA       | +      |

|                      | 3B       |                                                  | CMP_CR<br>CMP_SRC   | 7B       | RW       |                   | BB       |          |          | FB       | +      |

|                      | 3C       |                                                  | CMP_SRC<br>CMP_MUX0 | 7C       | RW       |                   | BC       |          |          | FC       | +      |

|                      | 3D       | 1                                                | CMP_MUX0            | 7D       | RW       |                   | BD       | -        | CPU_SCR2 | FD       | RSW    |

|                      | 3E       |                                                  | CIVIF_IVIUAT        | 7E       | 1///     |                   | BE       |          | CPU_SCR2 | FE       | #      |

|                      | 3F       | 1                                                | 1                   | 7E<br>7F |          |                   | BF       | 1        | CPU_SCR1 | FF       | #      |

|                      |          | <u> </u>                                         | not be accessed     | 1        | <u> </u> |                   | DF       | <u> </u> | OFU_SUKU | 1        |        |

Blank fields are Reserved and should not be accessed.

## 7.3 Register Map Bank 1 Table: Configuration Space

| Name               | Addr<br>(1,Hex) | Access                                           | Name                                             | Addr<br>(1,Hex) | Access | Name          | Addr<br>(1,Hex) | Access | Name      | Addr<br>(1,Hex) | Access |

|--------------------|-----------------|--------------------------------------------------|--------------------------------------------------|-----------------|--------|---------------|-----------------|--------|-----------|-----------------|--------|

| PRT0DM0            | 00              | RW                                               |                                                  | 40              |        |               | 80              |        |           | C0              |        |

| PRT0DM1            | 01              | RW                                               |                                                  | 41              |        |               | 81              |        |           | C1              |        |

| PRT0IC0            | 02              | RW                                               |                                                  | 42              |        |               | 82              |        |           | C2              |        |

| PRT0IC1            | 03              | RW                                               |                                                  | 43              |        |               | 83              |        |           | C3              |        |

| PRT1DM0            | 04              | RW                                               |                                                  | 44              |        |               | 84              |        |           | C4              |        |

| PRT1DM1            | 05              | RW                                               |                                                  | 45              |        |               | 85              |        |           | C5              |        |

| PRT1IC0            | 06              | RW                                               |                                                  | 46              |        |               | 86              |        |           | C6              |        |

| PRT1IC1            | 07              | RW                                               |                                                  | 47              |        |               | 87              |        | IDAC_CR   | C7              | RW     |

| HVP2_DM0           | 08              | RW                                               |                                                  | 48              |        |               | 88              |        |           | C8              | 1      |

| HVP2_DM1           | 09              | RW                                               |                                                  | 49              |        |               | 89              |        |           | C9              |        |

| HVP2_DS0           | 0A              | RW                                               |                                                  | 4A              |        |               | 8A              |        |           | CA              |        |

|                    | 0B              |                                                  |                                                  | 4B              |        |               | 8B              |        |           | СВ              | 1      |

|                    | 0C              |                                                  |                                                  | 4C              |        |               | 8C              |        |           | CC              |        |

|                    | 0D              |                                                  |                                                  | 4D              |        |               | 8D              |        |           | CD              |        |

|                    | 0E              |                                                  |                                                  | 4E              |        |               | 8E              |        |           | CE              | +      |

|                    | 0F              |                                                  |                                                  | 4F              |        |               | 8F              |        |           | CF              | -      |

|                    | 10              |                                                  |                                                  | 50              | 1      |               | 90              |        | GDI_O_IN  | D0              | RW     |

|                    | 11              |                                                  |                                                  | 51              |        |               | 91              |        | GDI_E_IN  | D1              | RW     |

|                    | 12              |                                                  |                                                  | 52              |        |               | 92              |        | GDI_O_OU  | D2              | RW     |

|                    | 13              |                                                  |                                                  | 53              |        |               | 93              |        | GDI_E_OU  | D3              | RW     |

|                    | 14              |                                                  |                                                  |                 | +      |               |                 |        |           | D3              |        |

|                    |                 |                                                  |                                                  | 54              | -      |               | 94              |        | AC0_GOEN  |                 | RW     |

|                    | 15              |                                                  |                                                  | 55              |        |               | 95              |        |           | D5              | _      |

|                    | 16              |                                                  |                                                  | 56              | -      |               | 96              |        |           | D6              | _      |

|                    | 17              |                                                  |                                                  | 57              |        |               | 97              |        |           | D7              |        |

|                    | 18              |                                                  |                                                  | 58              |        |               | 98              |        | AC0_CLK   | D8              | RW     |

|                    | 19              |                                                  |                                                  | 59              |        |               | 99              |        |           | D9              |        |

|                    | 1A              |                                                  |                                                  | 5A              |        |               | 9A              |        |           | DA              |        |

|                    | 1B              |                                                  |                                                  | 5B              |        |               | 9B              |        |           | DB              |        |

|                    | 1C              |                                                  |                                                  | 5C              |        |               | 9C              |        |           | DC              |        |

|                    | 1D              |                                                  |                                                  | 5D              |        |               | 9D              |        | OSC_GO_EN | DD              | RW     |

|                    | 1E              |                                                  |                                                  | 5E              |        |               | 9E              |        | OSC_CR4   | DE              | RW     |

|                    | 1F              |                                                  |                                                  | 5F              |        |               | 9F              |        | OSC_CR3   | DF              | RW     |

| DBC00FN            | 20              | RW                                               |                                                  | 60              |        | SLP_CR0       | A0              | RW     | OSC_CR0   | E0              | RW     |

| DBC00IN            | 21              | RW                                               |                                                  | 61              |        | SLP_CR1       | A1              | RW     | OSC_CR1   | E1              | RW     |

| DBC00OU            | 22              | RW                                               |                                                  | 62              |        | SLP_CR2       | A2              | RW     | OSC_CR2   | E2              | RW     |

|                    | 23              |                                                  |                                                  | 63              |        |               | A3              |        | VLT_CR    | E3              | RW     |

| DBC01FN            | 24              | RW                                               |                                                  | 64              |        | BUS_TOP       | A4              | RW     | VLT_CMP   | E4              | R      |

| DBC01IN            | 25              | RW                                               |                                                  | 65              |        |               | A5              |        |           | E5              | 1      |

| DBC01OU            | 26              | RW                                               |                                                  | 66              |        |               | A6              |        |           | E6              | +      |

|                    | 27              | 1                                                |                                                  | 67              |        |               | A7              |        |           | E7              | +      |

| DBD02FN            | 28              | RW                                               |                                                  | 68              | 1      | VDAC_TR       | A8              | RW     | IMO_TR    | E8              | W      |

| DBD02IN            | 29              | RW                                               |                                                  | 69              |        | VDAC_ITRIP0   | A9              | RW     | LSO_TR    | E9              | RW     |

| DBD02IN<br>DBD02OU | 2A              | RW                                               |                                                  | 6A              |        | VDAO_ITINII U | AA              | IXVV   | BDG_TR    | EA              | RW     |

| DDD0200            | 2B              | 1000                                             |                                                  | 6B              |        |               | AB              |        | DDO_IIX   | EB              | 1000   |

| DBD03EN            | 2B<br>2C        | RW                                               | TMD DDA                                          | 6C              | RW     | RDIV0         | AC              | RW     | 1         | EC              | +      |

| DBD03FN            |                 |                                                  | TMP_DR0                                          |                 |        | אוטואט        | - t             | LVV    | AA TD     |                 | D\A/   |

| DBD03IN            | 2D              | RW                                               | TMP_DR1                                          | 6D              | RW     |               | AD              | +      | AA_TR     | ED              | RW     |

| DBD03OU            | 2E              | RW                                               | TMP_DR2                                          | 6E              | RW     |               | AE              | 1      |           | EE              | +      |

|                    | 2F              | -                                                | TMP_DR3                                          | 6F              | RW     | DDIODI        | AF              | D144   |           | EF              | +      |

|                    | 30              | <del>                                     </del> |                                                  | 70              |        | RDI0RI        | B0              | RW     |           | F0              | +      |

|                    | 31              | 1                                                |                                                  | 71              |        | RDI0SYN       | B1              | RW     |           | F1              | +      |

|                    | 32              | 1                                                | <b>!</b>                                         | 72              |        | RDI0IS        | B2              | RW     |           | F2              | 4      |

|                    | 33              |                                                  |                                                  | 73              |        | RDI0LT0       | B3              | RW     |           | F3              |        |

|                    | 34              |                                                  |                                                  | 74              |        | RDI0LT1       | B4              | RW     |           | F4              |        |

|                    | 35              |                                                  |                                                  | 75              |        | RDI0RO0       | B5              | RW     |           | F5              |        |

|                    | 36              |                                                  |                                                  | 76              |        | RDI0RO1       | B6              | RW     |           | F6              |        |

|                    | 37              |                                                  |                                                  | 77              |        | RDI0GF        | B7              | RW     | CPU_F     | F7              | RL     |

|                    | 38              |                                                  |                                                  | 78              |        |               | B8              |        |           | F8              |        |

|                    | 39              |                                                  |                                                  | 79              |        |               | B9              |        |           | F9              | T      |

|                    | 3A              | İ                                                | 1                                                | 7A              |        |               | BA              |        |           | FA              | 1      |

|                    | 3B              | 1                                                | Î                                                | 7B              |        |               | BB              | 1      |           | FB              | 1      |

|                    | 3C              | 1                                                | Ī                                                | 7C              |        | Ī             | BC              | 1      | Ī         | FC              | +      |

|                    | 3D              | †                                                | 1                                                | 7D              |        |               | BD              | 1      | CPU_SCR2  | FD              | RSW    |

|                    | 3E              | +                                                | 1                                                | 7E              |        |               | BE              | +      | CPU_SCR1  | FE              | #      |

|                    | 3F              | +                                                | <del>                                     </del> | 7F              | 1      |               | BF              | 1      | CPU_SCR0  | FF              | #      |

|                    | J1              | 1                                                | not be accesse                                   |                 | Ĭ      | I             | 101             | 1      | 01 0_00KU | 111             | π      |

Blank fields are Reserved and should not be accessed.

## 8.0 Electrical Specifications

Specifications are valid for -40°C  $\leq T_{A} \leq 85^{o}C$  and  $T_{J} \leq 100^{o}C,$  except where noted.

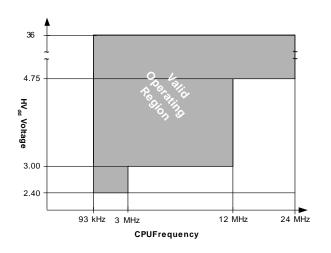

## 8.1 Frequencies

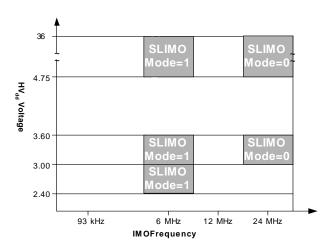

Refer to Table 8.4 for the electrical specifications on the internal main oscillator (IMO) using slow IMO (SLIMO) mode, which is set using the CPU\_SCR1 register.

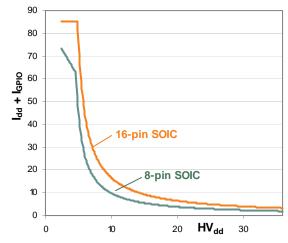

Figure 8-1a. Supply Voltage versus CPU Frequency

Figure 8-1b. IMO Frequency Trim Options

## 8.2 Absolute Maximum Ratings<sup>a</sup>

| Parameter           | Description                                           | Conditions                                                   | Min.                      | Тур. | Max.                      | Units |

|---------------------|-------------------------------------------------------|--------------------------------------------------------------|---------------------------|------|---------------------------|-------|

| T <sub>STG</sub>    | Storage Temperature                                   | Higher storage temperatures will reduce data retention time. | -50                       | -    | +100                      | °C    |

| T <sub>A</sub>      | Ambient Temperature with Power Applied                |                                                              | -40                       | _    | +85                       | °C    |

| HV <sub>dd</sub>    | Supply Voltage on HV <sub>dd</sub> Relative to Vss    |                                                              | -0.5                      | -    | +40                       | V     |

| V <sub>GPIO</sub>   | DC Input to any Low Voltage Input Pin                 | $HV_{dd} \le 5.0V.$                                          | -0.5                      | -    | HV <sub>dd</sub> +<br>0.5 | V     |

| V <sub>GPIO36</sub> | DC Input to any Low Voltage Input Pin                 | $HV_{dd} > 5.0V.$                                            | -0.5                      | -    | 5.5                       | V     |

| $V_{GD}$            | DC Input to any Gate Drive Pin                        |                                                              | HV <sub>dd</sub> -<br>5.5 | -    | HV <sub>dd</sub> +<br>0.5 | V     |

| V <sub>VS</sub>     | DC Input to High Voltage Sense<br>Pin                 |                                                              | -0.5                      | -    | HV <sub>dd</sub> +<br>0.5 |       |

| V <sub>HVO</sub>    | DC Applied to High Voltage<br>Outputs in High-Z State |                                                              | -0.5                      | -    | HV <sub>dd</sub> +<br>0.5 |       |

| I <sub>MIO</sub>    | Maximum Current into any Low Voltage Port Pin         |                                                              | -25                       | -    | +50                       | mA    |

| I <sub>MIOHV</sub>  | Maximum Current into any High Voltage Port Pin        |                                                              | -50                       | ı    | +50                       | mA    |

## 8.2 Absolute Maximum Ratings<sup>a</sup> (continued)

| I <sub>MIOGD</sub> b | Maximum Current into any Gate Drive Pin           |                       | -10  | _ | 10  | mA |

|----------------------|---------------------------------------------------|-----------------------|------|---|-----|----|

| ESD                  | Electro Static Discharge Voltage                  | Human Body Model ESD. | 2000 | _ | _   | V  |

| ESD <sub>HV</sub>    | Electro Static Discharge to High Voltage Port Pin | Human Body Model ESD. | 2000 | _ | ı   | V  |

| LU                   | Latch-up Current                                  |                       | 1    | _ | 200 | mA |

- a. Operation at these conditions degrades reliability.

- b. Cannot result in pin voltage exceeding V<sub>GD</sub> limits or thermal specifications being exceeded.

### 8.3 Operating Temperature

| Parameter      | Description          | Conditions                                                                                                                                                                                                | Min. | Тур. | Max. | Units |

|----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| T <sub>A</sub> | Ambient Temperature  |                                                                                                                                                                                                           | -40  | _    | +85  | °C    |

| TJ             | Junction Temperature | The temperature rise from ambient to junction is package specific. See "Thermal Impedances per Package" on page 32. The system designer must limit the power consumption to comply with this requirement. | -40  | -    | +100 | °C    |

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 36V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C (referred to as 5V operation), 3.0V to 3.6V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C (referred to as 3.3V operation), or 2.5V to 3.0V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C (referred to as 2.7V operation), respectively. Typical parameters apply to 5V, 3.3V, and 2.7V at 25°C and are for design guidance only.

### 8.4 DC Chip-Level Specifications

| Parameter         | Description                  | Conditions                                                                                                                                                                                            | Min. | Тур. | Max. | Units |

|-------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| HV <sub>dd</sub>  | Supply Voltage               | See DC POR and LVD specifications table 8.14 on page 20.                                                                                                                                              | 2.5  | _    | 36   | V     |

| I <sub>DD</sub>   | Supply Current, IMO = 24 MHz | Conditions are $HV_{dd} = 5.0V$ , $T_A = 25$ $^{\circ}C$ , $CPU = 3$ MHz, SYSCLK doubler disabled, VC1 = 1.5 MHz, VC2 = 93.75 kHz, VC3 = 93.75 kHz, analog power = off. SLIMO mode = 0. IMO = 24 MHz. | -    | 3    | 4    | mA    |

| I <sub>DD36</sub> | Supply Current, IMO = 24 MHz | Conditions are $HV_{dd} = 36V$ , $T_A = 25$ °C, $CPU = 3$ MHz, $SYSCLK$ doubler disabled, $VC1 = 1.5$ MHz, $VC2 = 93.75$ kHz, $VC3 = 93.75$ kHz, analog power = off. SLIMO mode = 0. IMO = 24 MHz.    | -    | 3    | 4    | mA    |

| I <sub>DD3</sub>  | Supply Current, IMO = 6 MHz  | Conditions are $HV_{dd} = 3.3V$ , $T_A = 25$ °C, CPU = 3 MHz, SYSCLK doubler disabled, VC1 = 1.5 MHz, VC2 = 93.75 kHz, VC3 = 93.75 kHz, analog power = off. SLIMO mode = 0. IMO = 24 MHz.             | -    | 1.2  | 2    | mA    |

## 8.4 DC Chip-Level Specifications (continued)

| I <sub>DD27</sub>  | Supply Current, IMO = 6 MHz                                                                           | Conditions are $HV_{dd} = 2.7V$ , $T_A = 25$ $^{o}C$ , $CPU = 0.75$ MHz, SYSCLK doubler disabled, $VC1 = 0.375$ MHz, $VC2 = 23.44$ kHz, $VC3 = 0.09$ kHz, analog power = off. SLIMO mode = 1. IMO = 6 MHz. | -     | 1.1                                  | 1.5   | mA |

|--------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------|-------|----|

| I <sub>RESET</sub> | Supply Current while Reset                                                                            | Conditions are $HV_{dd} = 5.0V$ , $-40$ $^{\circ}C \le T_A \le 85$ $^{\circ}C$ .                                                                                                                           | -     | _                                    | 250   | μΑ |

| I <sub>SBI</sub>   | Supply Current in Idle Mode                                                                           | Conditions are with internal slow speed oscillator, $HV_{dd} = 3.3V$ , $-40$ °C $\leq T_A \leq 85$ °C, analog power = off.                                                                                 | _     | _                                    | 750   | μΑ |

| I <sub>SB</sub>    | Supervised Sleep Current (POR, LVD, SleepTimer, WDT, and Voltage Regulation)                          | Conditions are with internal slow speed oscillator, $HV_{dd} = 3.3V$ , $-40$ °C $\leq T_A \leq 85$ °C, analog power = off.                                                                                 | -     | 2.8                                  | 3     | μΑ |

| I <sub>SBR</sub>   | Regulated Sleep Current<br>(No POR, No LVD, but with<br>SleepTimer, WDT, and Voltage<br>Regulation)   | Conditions are with internal slow speed oscillator, $HV_{dd} = 3.3V$ , $-40$ °C $\leq T_A \leq 85$ °C, analog power = off.                                                                                 | -     | -                                    | 1     | μΑ |

| I <sub>SBW</sub>   | Watchdog Sleep Current<br>(No POR, No LVD, No Sleep-<br>Timer, No Voltage Regulation<br>but with WDT) | Conditions are with internal slow speed oscillator, $HV_{dd} = 3.3V$ , $T_A = 25$ °C, analog power = off.                                                                                                  | -     | 0.5                                  | _     | μΑ |

| I <sub>SBD</sub>   | Deep Sleep Current<br>(No POR, No LVD, No Sleep-<br>Timer, No Voltage Regulation<br>and No WDT        | Conditions are bypass mode on, deep sleep enabled, HV <sub>dd</sub> = 3.3V, T <sub>A</sub> = 25 °C, analog power = off.                                                                                    | -     | 0.1                                  | _     | μА |

| I <sub>SBDHV</sub> | Deep Sleep Current at HV<br>(No POR, No LVD, No Sleep-<br>Timer, No Voltage Regulation<br>and No WDT  | Conditions are analog power off, deep sleep enabled, $HV_{dd}$ = 6V, $T_A$ = 25 $^{\rm o}$ C.                                                                                                              | -     | ((HV <sub>dd</sub> - 6)<br>/2) + 0.1 | _     | μΑ |

| V <sub>REF</sub>   | Reference Voltage (Bandgap)                                                                           | Trimmed for HV <sub>dd</sub> > 3.0V.                                                                                                                                                                       | 1.291 | 1.30                                 | 1.309 | V  |

| V <sub>REF27</sub> | Reference Voltage (Bandgap)                                                                           | Trimmed for HV <sub>dd</sub> = 2.5V to 3.0V.                                                                                                                                                               | 1.16  | 1.30                                 | 1.33  | V  |

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 36V and  $-40^{\circ}\text{C} \leq T_{\text{A}} \leq 85^{\circ}\text{C}$  (referred to as 5V operation), 3.0V to 3.6V and  $-40^{\circ}\text{C} \leq T_{\text{A}} \leq 85^{\circ}\text{C}$  (referred to as 3.3V operation), or 2.5V to 3.0V and  $-40^{\circ}\text{C} \leq T_{\text{A}} \leq 85^{\circ}\text{C}$  (referred to as 2.7V operation), respectively. Typical parameters apply to 5V, 3.3V, and 2.7V at  $25^{\circ}\text{C}$  and are for design guidance only.

### 8.5 4.75V to 36V DC GPIO Specifications

| Parameter                    | Description                                       | Conditions                                                                                                                                                     | Min. | Тур. | Max. | Units |

|------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| R <sub>PU</sub>              | Pull-up Resistor                                  |                                                                                                                                                                | 4    | 5.6  | 8    | kΩ    |

| R <sub>PD</sub>              | Pull-down Resistor                                |                                                                                                                                                                | 4    | 5.6  | 8    | kΩ    |

| V <sub>OH</sub> <sup>a</sup> | High Output Level                                 | IOH = 10 mA, $HV_{dd}$ = 4.75V to 36V maximum 40 mA on even port pins (for example, P0[2], P1[0]), maximum 40 mA on odd port pins (for example, P0[3], P1[1]). | 3.6  | -    | 5.4  | V     |

| V <sub>OL</sub> <sup>a</sup> | Low Output Level                                  | IOL = 25 mA, $HV_{dd}$ = 4.75V to 36V maximum 90 mA on even port pins (for example, P0[2], P1[0]), maximum 90 mA on odd port pins (for example, P0[3], P1[1]). | -    | -    | 0.75 | V     |

| V <sub>IL</sub>              | Input Low Level                                   | $HV_{dd} = 4.75V$ to 36V.                                                                                                                                      | _    | _    | 0.8  | V     |

| V <sub>IH</sub>              | Input High Level                                  | $HV_{dd} = 4.75V$ to 36V.                                                                                                                                      | 2.1  | _    | -    | V     |

| $V_{H}$                      | Input Hysteresis                                  |                                                                                                                                                                | _    | 60   | _    | mV    |

| I <sub>IL</sub>              | Input Leakage (Absolute Value)                    | Gross tested to 1 μA.                                                                                                                                          | _    | 1    | _    | nA    |

| C <sub>IN</sub>              | Capacitive Load on Pins as Input                  | Package and pin dependent. Temp = 25°C.                                                                                                                        | _    | 3.5  | 10   | pF    |

| C <sub>OUT</sub>             | Capacitive Load on Pins as<br>Output              | Package and pin dependent. Temp = 25°C.                                                                                                                        |      | 3.5  | 10   | pF    |

| I <sub>OH</sub> <sup>b</sup> | Current Supplied while Maintaining 10% Regulation | $4.5V \le V_{OH} \le 5.5V$ , $HV_{dd} = 4.75V$ to 36V.                                                                                                         | 5.5  | _    | _    | mA    |

a. IOH and IOL are also limited by the die temperature. See "Thermal Considerations" on page 31.

### 8.6 3.0V to 5.0V DC GPIO Specifications

| Parameter                    | Description        | Conditions                                                                                                                                                            | Min.                      | Тур. | Max.             | Units |

|------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------------------|-------|

| R <sub>PU</sub>              | Pull-up Resistor   |                                                                                                                                                                       | 4                         | 5.6  | 8                | kΩ    |

| R <sub>PD</sub>              | Pull-down Resistor |                                                                                                                                                                       | 4                         | 5.6  | 8                | kΩ    |

| V <sub>OH</sub> <sup>a</sup> | High Output Level  | IOH = 8 mA, HV <sub>dd</sub> = 3.0V to 3.6V maximum 30 mA on even port pins (for example, P0[2], P1[0]), maximum 30 mA on odd port pins (for example, P0[3], P1[1]).  | HV <sub>dd</sub> -<br>1.0 | -    | HV <sub>dd</sub> | V     |

| V <sub>OL</sub> <sup>a</sup> | Low Output Level   | IOL = 16 mA, HV <sub>dd</sub> = 3.0V to 3.6V maximum 60 mA on even port pins (for example, P0[2], P1[0]), maximum 60 mA on odd port pins (for example, P0[3], P1[1]). | _                         | -    | 0.75             | V     |

| V <sub>IL</sub>              | Input Low Level    | $HV_{dd} = 3.0V \text{ to } 3.6V.$                                                                                                                                    | _                         | _    | 0.8              | V     |

| V <sub>IH</sub>              | Input High Level   | $HV_{dd} = 3.0V \text{ to } 3.6V.$                                                                                                                                    | 2.1                       | _    | _                | V     |

b. Odd and even port pins are regulated separately, therefore the current limit total applies separately to all odd port pins and to all even port pins.

## 8.6 3.0V to 5.0V DC GPIO Specifications (continued)

| $V_{H}$          | Input Hysteresis                     |                                         | _ | 60  | _  | mV |

|------------------|--------------------------------------|-----------------------------------------|---|-----|----|----|

| I <sub>IL</sub>  | Input Leakage (Absolute Value)       | Gross tested to 1 μA.                   | _ | 1   | _  | nA |

| C <sub>IN</sub>  | Capacitive Load on Pins as Input     | Package and pin dependent. Temp = 25°C. | - | 3.5 | 10 | pF |

| C <sub>OUT</sub> | Capacitive Load on Pins as<br>Output | Package and pin dependent. Temp = 25°C. | - | 3.5 | 10 | pF |

a. IOH and IOL are also limited by the die temperature. See "Thermal Considerations" on page 31.

## 8.7 2.5V to 3.0V DC GPIO Specifications

| Parameter                    | Description                          | Conditions                                                                                                                                                           | Min.                      | Тур. | Max.             | Units |

|------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------------------|-------|

| R <sub>PU</sub>              | Pull-up Resistor                     |                                                                                                                                                                      | 4                         | 5.6  | 8                | kΩ    |

| R <sub>PD</sub>              | Pull-down Resistor                   |                                                                                                                                                                      | 4                         | 5.6  | 8                | kΩ    |

| V <sub>OH</sub> <sup>a</sup> | High Output Level                    | IOH = 2 mA, HV <sub>dd</sub> = 2.5V to 3.0V maximum 16 mA on even port pins (for example, P0[2], P1[0]), maximum 16 mA on odd port pins (for example, P0[3], P1[1]). | HV <sub>dd</sub> -<br>1.0 | -    | HV <sub>dd</sub> | V     |

| V <sub>OL</sub> <sup>a</sup> | Low Output Level                     | IOL = 8 mA, HV <sub>dd</sub> = 2.5V to 3.0V maximum 40 mA on even port pins (for example, P0[2], P1[0]), maximum 40 mA on odd port pins (for example, P0[3], P1[1]). | -                         | -    | 0.75             | V     |

| V <sub>IL</sub>              | Input Low Level                      | $HV_{dd} = 2.5V \text{ to } 3.0V.$                                                                                                                                   | _                         | -    | 0.8              | V     |

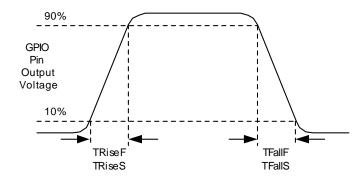

| V <sub>IH</sub>              | Input High Level                     | $HV_{dd} = 2.5V \text{ to } 3.0V.$                                                                                                                                   | 2.0                       | -    | _                | V     |