## Technical Data

# MPC106 PCI Bridge/Memory Controller Hardware Specifications

The Motorola MPC106 PCI bridge/memory controller provides a PowerPC<sup>TM</sup> microprocessor common hardware reference platform (CHRP<sup>TM</sup>) compliant bridge between the PowerPC microprocessor family and the Peripheral Component Interconnect (PCI) bus. In this document, the term '106' is used as an abbreviation for the phrase 'MPC106 PCI bridge/memory controller.' This document contains pertinent physical characteristics of the 106. For functional characteristics, refer to the MPC106 PCI Bridge/Memory Controller User's Manual.

This document contains the following topics:

| Topic                                                 | Page |

|-------------------------------------------------------|------|

| Section 1.1, "Overview"                               | 2    |

| Section 1.2, "Features"                               | 3    |

| Section 1.3, "General Parameters"                     | 5    |

| Section 1.4, "Electrical and Thermal Characteristics" | 5    |

| Section 1.5, "Pin Assignments"                        | 15   |

| Section 1.6, "Pinout Listings                         | 16   |

| Section 1.7, "Package Description"                    | 20   |

| Section 1.8, "System Design Information"              | 22   |

| Section 1.9, "Document Revision History"              | 27   |

| Section 1.10, "Ordering Information"                  | 27   |

This document contains information on a new product under development by Motorola. Motorola reserves the right to change or discontinue this product without notice.

### Overview

In this document, the term '60x' is used to denote a 32-bit microprocessor from the PowerPC architecture family that conforms to the bus interface of the PowerPC 601<sup>TM</sup>, PowerPC 603<sup>TM</sup>, or PowerPC 604<sup>TM</sup> microprocessors. Note that this does not include the PowerPC 602<sup>TM</sup> microprocessor which has a multiplexed address/data bus. 60x processors implement the PowerPC architecture as it is specified for 32-bit addressing, which provides 32-bit effective (logical) addresses, integer data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits (single-precision and double-precision).

To locate any published errata or updates for this document, refer to the website at http://www.mot.com/SPS/PowerPC/.

## 1.1 Overview

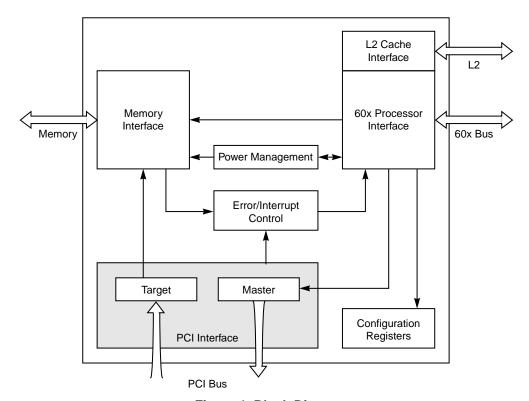

The MPC106 provides an integrated high-bandwidth, high-performance, TTL-compatible interface between a 60x processor, a secondary (L2) cache or additional (up to four total) 60x processors, the PCI bus, and main memory. This section provides a block diagram showing the major functional units of the 106 and describes briefly how those units interact.

Figure 1 shows the major functional units within the 106. Note that this is a conceptual block diagram intended to show the basic features rather than how these features are physically implemented on the device.

Figure 1. Block Diagram

The 106 provides a PowerPC microprocessor CHRP-compliant bridge between the PowerPC microprocessor family and the PCI bus. CHRP documentation provides a set of specifications that define a unified personal computer architecture. PCI support allows the rapid design of systems using peripherals already designed for PCI and the other standard interfaces available in the personal computer hardware environment. The 106 integrates secondary cache control and a high-performance memory controller, uses an advanced, 3.3-V CMOS process technology, and is fully compatible with TTL devices.

The 106 supports a programmable interface to a variety of PowerPC microprocessors operating at select bus speeds. The 60x address bus is 32 bits wide and the data bus is 64 bits wide. The 60x processor interface of the 106 uses a subset of the 60x bus protocol, supporting single-beat and burst data transfers. The address and data buses are decoupled to support pipelined transactions.

The 106 provides support for the following configurations of 60x processors and L2 cache:

- Up to four 60x processors with no L2 cache

- A single 60x processor plus a direct-mapped, lookaside L2 cache using the internal L2 cache controller of the 106

- Up to four 60x processors plus an externally controlled L2 cache (such as the Motorola MPC2605 integrated secondary cache)

The memory interface controls processor and PCI interactions to main memory and is capable of supporting a variety of configurations using DRAM, EDO, SDRAM, ROM, or Flash ROM.

The PCI interface of the 106 complies with the *PCI Local Bus Specification*, Revision 2.1, and follows the guidelines in the *PCI System Design Guide*, Revision 1.0, for host bridge architecture. The PCI interface connects the processor and memory buses to the PCI bus, to which I/O components are connected. The PCI bus uses a 32-bit multiplexed address/data bus, plus various control and error signals.

The PCI interface of the 106 functions as both a master and target device. As a master, the 106 supports read and write operations to the PCI memory space, the PCI I/O space, and the PCI configuration space. The 106 also supports PCI special-cycle and interrupt-acknowledge commands. As a target, the 106 supports read and write operations to system memory.

The 106 provides hardware support for four levels of power reduction: doze, nap, sleep, and suspend. The design of the MPC106 is fully static, allowing internal logic states to be preserved during all power-saving modes.

## 1.2 Features

This section summarizes the major features of the 106, as follows:

- 60x processor interface

- Supports up to four 60x processors

- Supports various operating frequencies and bus divider ratios

- 32-bit address bus, 64-bit data bus

- Supports full memory coherency

- Supports optional 60x local bus slave

- Decoupled address and data buses for pipelining of 60x accesses

- Store gathering on 60x-to-PCI writes

### **Features**

- Secondary (L2) cache control

- Configurable for write-through or write-back operation

- Supports cache sizes of 256 Kbytes, 512 Kbytes, and 1 Mbyte

- Up to 4 Gbytes of cacheable space

- Direct-mapped

- Supports byte parity

- Supports partial update with external byte decode for write enables

- Programmable interface timing

- Supports pipelined burst, synchronous burst, or asynchronous SRAMs

- Alternately supports an external L2 cache controller or integrated L2 cache module

### Memory interface

- 1 Gbyte of RAM space, 16 Mbytes of ROM space

- Supports parity or error checking and correction (ECC)

- High-bandwidth, 64-bit data bus (72 bits including parity or ECC)

- Supports fast page mode DRAMs, extended data out (EDO) DRAMs, and synchronous DRAMs (SDRAMs)

- Supports 1 to 8 banks of DRAM/EDO/SDRAM with sizes ranging from 2 Mbyte to 128 Mbytes per bank

- ROM space may be split between the PCI bus and the 60x/memory bus (8 Mbytes each)

- Supports 8-bit asynchronous ROM or 64-bit burst-mode ROM

- Supports writing to Flash ROM

- Configurable external buffer control logic

- Programmable interface timing

#### PCI interface

- Compliant with *PCI Local Bus Specification*, Revision 2.1

- Supports PCI interlocked accesses to memory using LOCK signal and protocol

- Supports accesses to all PCI address spaces

- Selectable big- or little-endian operation

- Store gathering on PCI writes to memory

- Selectable memory prefetching of PCI read accesses

- Only one external load presented by the MPC106 to the PCI bus

- Interface operates at 20–33 MHz

- Word parity supported

- 3.3 V/5.0 V-compatible

- Support for concurrent transactions on 60x and PCI buses

- Power management

- Fully-static 3.3-V CMOS design

- Supports 60x nap, doze, and sleep power management modes and suspend mode

- IEEE 1149.1-compliant, JTAG boundary-scan interface

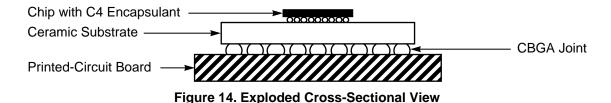

- 304-pin ceramic ball grid array (CBGA) package

## 1.3 General Parameters

The following list provides a summary of the general parameters of the 106:

Technology 0.5 µm CMOS, four-layer metal

Die size 5.8 mm x 7.2 mm (41.8 mm<sup>2</sup>)

Transistor count 250,000

Logic design Fully-static

Packages Surface mount 304-lead C4 ceramic ball grid array (CBGA)

Power supply  $3.3 \text{ V} \pm 5\% \text{ V DC}$

Maximum input rating  $5.0 \text{ V} \pm 10\% \text{ V} DC$

## 1.4 Electrical and Thermal Characteristics

This section provides both the AC and DC electrical specifications and thermal characteristics for the 106.

### 1.4.1 DC Electrical Characteristics

The tables in this section describe the 106 DC electrical characteristics. Table 1 provides the absolute maximum ratings. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause it permanent damage.

| Characteristic            | Symbol           | Value       | Unit | Notes |

|---------------------------|------------------|-------------|------|-------|

| Supply voltage            | Vdd              | -0.3 to 3.6 | V    | _     |

| PLL supply voltage        | AVdd             | -0.3 to 3.6 | V    | _     |

| Input voltage             | V <sub>in</sub>  | -0.3 to 5.5 | V    | 1     |

| Junction temperature      | Tj               | 0 to 105    | °C   | 2     |

| Storage temperature range | T <sub>stg</sub> | -55 to 150  | °C   | _     |

**Table 1. Absolute Maximum Ratings**

### Notes:

Table 2 provides the recommended operating conditions for the 106. Proper device operation outside of these recommended and tested conditions is not guaranteed.

Caution: Vin must not exceed Vdd by more than 2.5 V at all times including during power-on reset.

The extended temperature parts have die junction temperature of -40 to 105°C. See MPC106ARXTGPNS/D for more information.

### **Electrical and Thermal Characteristics**

**Table 2. Recommended Operating Conditions**

| Characteristic           | Symbol | Value        | Unit | Notes                                                                        |

|--------------------------|--------|--------------|------|------------------------------------------------------------------------------|

| Supply voltage           | Vdd    | 3.3 ± 165 mv | V    | _                                                                            |

| PLL supply voltage       | AVdd   | 3.3 ± 165 mv | V    | _                                                                            |

| Input voltage            | Vin    | 0 to 5.5     | V    | _                                                                            |

| Die junction temperature | Тј     | 0 to 105     | °C   | The extended temperature parts have die junction temperature of -40 to 105°C |

Table 3 provides the package thermal characteristics for the 106.

**Table 3. Package Thermal Characteristics**

| Characteristic                                          | Symbol          | Value | Rating |

|---------------------------------------------------------|-----------------|-------|--------|

| CBGA package thermal resistance, junction-to-top of die | θ <sub>JC</sub> | 0.133 | °C/W   |

Note: Refer to Section 1.8, "System Design Information," for more details about thermal management.

Table 4 provides the DC electrical characteristics for the 106, assuming Vdd = AVdd =  $3.3 \pm 5\%$  V DC, GND = 0 V DC, and  $0 \le T_i \le 105$  °C.

**Table 4. DC Electrical Specifications**

| Characteristic                                                                | Symbol           | Min | Max  | Unit |

|-------------------------------------------------------------------------------|------------------|-----|------|------|

| Input high voltage (all inputs except SYSCLK)                                 | V <sub>IH</sub>  | 2   | 5.5  | V    |

| Input low voltage (all inputs except SYSCLK)                                  | V <sub>IL</sub>  | GND | 0.8  | V    |

| SYSCLK input high voltage                                                     | CV <sub>IH</sub> | 2.4 | 5.5  | V    |

| SYSCLK input low voltage                                                      | CV <sub>IL</sub> | GND | 0.4  | V    |

| Input leakage current, V <sub>in</sub> =3.3 V <sup>1</sup>                    | I <sub>in</sub>  | _   | 15.0 | μA   |

| Hi-Z (off-state) leakage current, V <sub>in</sub> = 3.3 V <sup>1</sup>        | I <sub>TSI</sub> | _   | 15.0 | μA   |

| Output high voltage, $I_{OH} = -7 \text{ mA}^2$                               | V <sub>OH</sub>  | 2.4 | _    | V    |

| Output low voltage, $I_{OL} = 7 \text{ mA}^2$                                 | V <sub>OL</sub>  | _   | 0.5  | V    |

| PCI 3.3 V signaling output high voltage, $I_{OH} = -0.5 \text{ mA}^2$         | V <sub>OH</sub>  | 2.7 | _    | V    |

| PCI 3.3 V signaling output low voltage, I <sub>OL</sub> = 1.5 mA <sup>2</sup> | V <sub>OL</sub>  | _   | 0.3  | V    |

| Capacitance, V <sub>in</sub> = 0 V, f = 1 MHz <sup>3</sup>                    | C <sub>in</sub>  | _   | 7.0  | pF   |

### Notes:

Table 5 lists the power consumption of the 106.

<sup>&</sup>lt;sup>1</sup> Excludes test signals (LSSD\_MODE and JTAG signals).

This value represents worst case 40-ohm drivers (default value for Processor/L2 control signals CI, WT, GBL, TBST, TSIZ[0–2], TT[0–4], TWE, and TV) only. Other signals have lower default driver impedance and will support larger I<sub>OH</sub> and I<sub>OL</sub>. All drivers may optionally be programmed to different driver strengths.

<sup>&</sup>lt;sup>3</sup> Capacitance is periodically sampled rather than 100% tested.

**Table 5. Power Consumption**

| Mode    | SYSCLK/Core<br>33/66 MHz | SYSCLK/Core<br>33/83.3 MHz | Unit |

|---------|--------------------------|----------------------------|------|

| Full-On | I                        | 1                          |      |

| Typical | 1.2                      | 2.2                        | W    |

| Maximum | 1.4                      | 2.4                        | W    |

| Doze    | '                        |                            |      |

| Typical | 1.0                      | 1.1                        | W    |

| Maximum | 1.2                      | 1.4                        | W    |

| Nap     | 1                        |                            |      |

| Typical | 1.0                      | 1.1                        | W    |

| Maximum | 1.2                      | 1.4                        | W    |

| Sleep   |                          |                            |      |

| Typical | 260                      | 330                        | mW   |

| Maximum | 360                      | 450                        | mW   |

| Suspend | '                        |                            |      |

| Typical | 140                      | 220                        | mW   |

| Maximum | 190                      | 270                        | mW   |

- Power consumption for common system configurations assuming 50 pF loads

- Suspend power-saving mode assumes SYSCLK off and PLL in bypass mode.

- Typical power is an average value measured at Vdd = AVdd = 3.30 V and  $T_A = 25 \text{ °C}$ .

- Maximum power is measured at Vdd = AVdd = 3.45 V and T<sub>A</sub> = 25 °C.

## 1.4.2 AC Electrical Characteristics

This section provides AC electrical characteristics for the 106. After fabrication, parts are sorted by maximum 60x processor bus frequency, as shown in Section 1.4.2.1, "Clock AC Specifications," and tested for conformance to the AC specifications for that frequency. These specifications are for operation between 16.67 and 33.33 MHz PCI bus (SYSCLK) frequencies. The 60x processor bus frequency is determined by the PCI bus (SYSCLK) frequency and the settings of the PLL[0–3] signals. All timings are specified relative to the rising edge of SYSCLK.

## 1.4.2.1 Clock AC Specifications

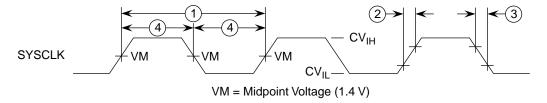

Table 6 provides the clock AC timing specifications as shown in Figure 2, and assumes Vdd = AVdd =  $3.3 \pm 5\%$  V DC, GND = 0 V DC, and  $0 \le T_j \le 105$  °C.

| Num  | Characteristic                      |       | K/Core<br>MHz |       | K/Core<br>3 MHz | Unit | Notes |  |

|------|-------------------------------------|-------|---------------|-------|-----------------|------|-------|--|

|      |                                     | Min   | Max           | Min   | Max             |      |       |  |

| _    | 60x processor bus (core) frequency  | 16.67 | 66            | 16.67 | 83.3            | MHz  | 1     |  |

| _    | VCO frequency                       | 120   | 200           | 120   | 200             | MHz  | 1, 2  |  |

| _    | SYSCLK frequency                    | 16.67 | 33.33         | 16.67 | 33.33           | MHz  | 1     |  |

| 1    | SYSCLK cycle time                   | 30.0  | 60.0          | 30.0  | 60.0            | ns   | _     |  |

| 2, 3 | SYSCLK rise and fall time           | _     | 2.0           | _     | 2.0             | ns   | 3     |  |

| 4    | SYSCLK duty cycle measured at 1.4 V | 40    | 60            | 40    | 60              | %    | 4     |  |

| _    | SYSCLK jitter                       | _     | ±200          | _     | ±200            | ps   | 5     |  |

| _    | 106 internal PLL relock time        | _     | 100           | _     | 100             | μs   | 4, 6  |  |

**Table 6. Clock AC Timing Specifications**

- Caution: The SYSCLK frequency and PLL[0–3] settings must be chosen such that the resulting SYSCLK (bus) frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL[0–3] signal description in Section 1.8, "System Design Information," for valid PLL[0–3] settings, and to Section 1.9, "Document Revision History," for available frequencies and part numbers.

- VCO operating range for extended temperature devices is different. Refer to MPC106ARXTGPNS/D for more information.

- <sup>3</sup> Rise and fall times for the SYSCLK input are measured from 0.4 V to 2.4 V.

- <sup>4</sup> Timing is guaranteed by design and characterization and is not tested.

- <sup>5</sup> The total input jitter (short-term and long-term combined) must be under ±200 ps.

- <sup>6</sup> PLL-relock time is the maximum time required for PLL lock after a stable Vdd, AVdd, and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during the sleep and suspend power-saving modes. Also note that HRST must be held asserted for a minimum of 255 bus clocks after the PLL-relock time (100 μs) during the power-on reset sequence.

Figure 2 provides the SYSCLK input timing diagram.

Figure 2. SYSCLK Input Timing Diagram

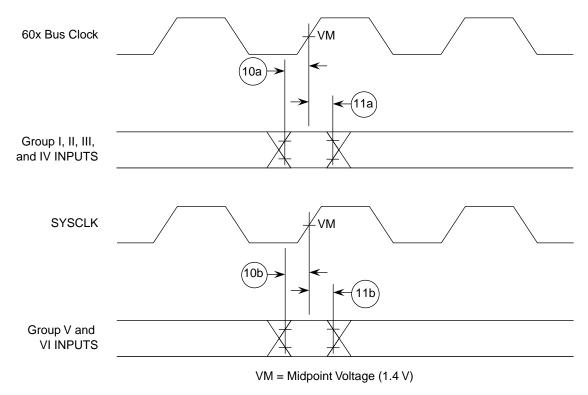

## 1.4.2.2 Input AC Specifications

Table 7 provides the input AC timing specifications for the 106 as defined in Figure 3 and Figure 4. These specifications are for operation between 16.67 and 33.33 MHz PCI bus clock (SYSCLK) frequencies. Assume Vdd =  $AVdd = 3.3 \pm 5\%$  V DC, GND = 0 V DC, and  $0 \le T_i \le 105$  °C.

**Table 7. Input AC Timing Specifications**

| Num | Characteristic                                               | 66 M                                     | Hz  | 83.3 M                                   | Hz  | Unit  | Notes        |

|-----|--------------------------------------------------------------|------------------------------------------|-----|------------------------------------------|-----|-------|--------------|

| Num | Gilaracteristic                                              | Min                                      | Max | Min                                      | Max | Oilit | Notes        |

| 10a | Group I input signals valid to 60x Bus Clock (input setup)   | 4.0                                      |     | 3.5                                      |     | ns    | 1,2,3        |

| 10a | Group II input signals valid to 60x Bus Clock (input setup)  | 3.5                                      |     | 3.5                                      |     | ns    | 1,2,4        |

| 10a | Group III input signals valid to 60x Bus Clock (input setup) | 3.0                                      |     | 2.5                                      |     | ns    | 1,2,5        |

| 10a | Group IV input signals valid to 60x Bus Clock (input setup)  | 5.0                                      |     | 4.0                                      |     | ns    | 1,2,6        |

| 10b | Group V input signals valid to SYSCLK (input setup)          | 7.0                                      |     | 7.0                                      |     | ns    | 7,8          |

| 10b | Group VI input signals valid to SYSCLK (input setup)         | 7.0                                      |     | 7.0                                      |     | ns    | 7,9          |

| 11a | 60x Bus Clock to group I–IV inputs invalid (input hold)      | 0                                        | _   | 0                                        | _   | ns    | 3,4,5,6      |

| 11b | SYSCLK to group V–VI inputs invalid (input hold)             | -0.5                                     | _   | -0.5                                     | _   | ns    | 8,9          |

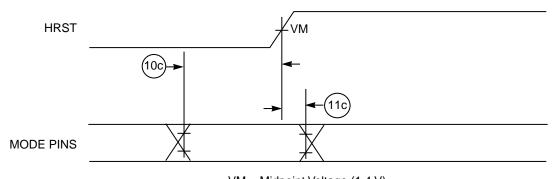

|     | HRST pulse width                                             | 255 x<br>t <sub>sysclk</sub> +<br>100 µs | _   | 255 x<br>t <sub>sysclk</sub> +<br>100 μs | _   |       | _            |

| 10c | Mode select inputs valid to HRST (input setup)               | 3 x t <sub>sysclk</sub>                  | _   | 3 x t <sub>sysclk</sub>                  | _   | ns    | 10,<br>11,12 |

| 11c | HRST to mode select input invalid (input hold)               | 1.0                                      | _   | 1.0                                      | _   | ns    | 10, 12       |

- 1 Input specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the 1.4 V of the rising edge of SYSCLK. Both input and output timings are measured at the pin (see Figure 3).

- Processor and memory interface signals are specified from the rising edge of the 60x bus clock (which is internally synchronized to SYSCLK).

- <sup>3</sup> Group I input signals include the following processor, L2, and memory interface signals: A[0–31], PAR[0–7]/AR[1–8], BR[0–4], BRL2, XATS, LBCLAIM, ADS, BA0, TV and HIT (when configured for external L2)

- <sup>4</sup> Group II input signals include the following processor and memory interface signals: TBST, TT[0–4], TSIZ[0–2], WT, CI, GBL, AACK, and TA.

- <sup>5</sup> Group III input signals include the following processor and memory interface signals: DL[0–31] and DH[0–31].

- Group IV input signals include the following processor and L2 interface signals: TS, ARTRY, DIRTY\_IN, and HIT (when configured for internal L2 controller).

- <sup>7</sup> PCI 3.3 V signaling environment signals are measured from 1.65 V (Vdd  $\div$  2) on the rising edge of SYSCLK to  $V_{OH}$  = 3.0 V or  $V_{OL}$  = 0.3 V. PCI 5 V signaling environment signals are measured from 1.65 V (Vdd  $\div$  2) on the rising edge of SYSCLK to  $V_{OH}$  = 2.4 V or  $V_{OI}$  = 0.55 V.

- <sup>8</sup> Group V input signals include the following bussed PCI interface signals: FRAME, C/BE[0-3], AD[0-31], DEVSEL, IRDY, TRDY, STOP, PAR, PERR, SERR, LOCK, FLSHREQ, and ISA\_MASTER.

- <sup>9</sup> Group VI input signal is the point-to-point PCI GNT input signal.

- <sup>10</sup> The setup and hold time is with respect to the rising edge of HRST (see Figure 4). Mode select inputs include the RCSO, FOE, and DBGO configuration inputs.

- t<sub>sysclk</sub> is the period of the external clock (SYSCLK) in nanoseconds (ns). When the unit is given as t<sub>sysclk</sub>, the numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.

- <sup>12</sup> These values are guaranteed by design and are not tested.

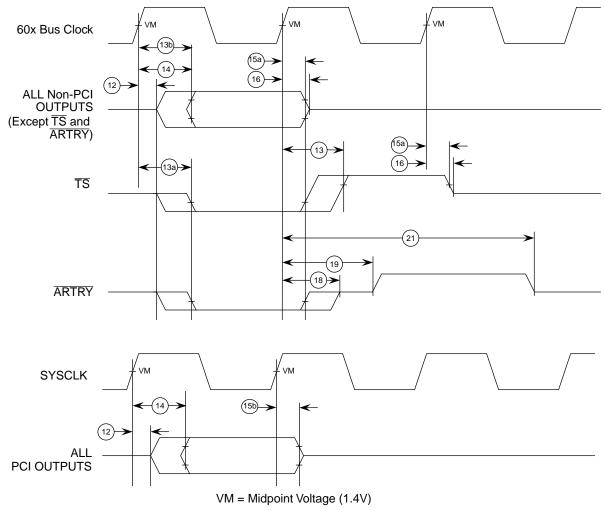

Figure 3 provides the input timing diagram for the 106.

**Figure 3. Input Timing Diagram**

Figure 4 provides the mode select input timing diagram for the 106.

VM = Midpoint Voltage (1.4 V)

Figure 4. Mode Select Input Timing Diagram

## 1.4.2.3 Output AC Specifications

Table 8 provides the output AC timing specifications for 106 (shown in Table 5). Assume Vdd = AVdd =  $3.3 \pm 5\%$  V DC, GND = 0 V DC, CL = 50 pF, and  $0 \le T_j \le 105$  °C. Processor and memory interface signals are specified from the rising edge of the 60x bus clock (which is internally synchronized to SYSCLK). All units are nanoseconds.

**Table 8. Output AC Timing Specifications**

| Num   | Characteristic                                                                                    | 66 1                               | MHz                                | 83.3                                              | MHz                                       | Notes   |

|-------|---------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|---------------------------------------------------|-------------------------------------------|---------|

| Nulli | Characteristic                                                                                    | Min                                | Max                                | Min                                               | Max                                       | Notes   |

| 12    | SYSCLK to output driven (output enable time)                                                      | 2.0                                | _                                  | 2.0                                               | _                                         | 1       |

| 13a   | SYSCLK to output valid for TS and ARTRY                                                           | _                                  | 7.0                                | _                                                 | 6.0                                       | 2, 3, 4 |

| 13b   | SYSCLK to output valid for all non-PCI signals except TS, ARTRY, RAS[0–7], CAS[0–7], and DWE[0-2] | _                                  | 7.0                                | _                                                 | 6.0                                       | 2, 3, 5 |

| 14a   | SYSCLK to output valid (for RAS[0-7] and CAS[0-7])                                                | _                                  | 7.0                                | _                                                 | 6.0                                       | 2, 3    |

| 14b   | SYSCLK to output valid for PCI signals                                                            | _                                  | 11.0                               | _                                                 | 11.0                                      | 3, 6    |

| 15a   | SYSCLK to output invalid for all non-PCI signals (output hold)                                    | 1.0                                | _                                  | 1.0                                               | _                                         | 7, 10   |

| 15b   | SYSCLK to output invalid for PCI signals (output hold)                                            | 1.0                                | _                                  | 1.0                                               | _                                         | 7       |

| 18    | SYSCLK to ARTRY high impedance before precharge (output hold)                                     |                                    |                                    | _                                                 | 8.0                                       | 1       |

| 19    | SYSCLK to ARTRY precharge enable                                                                  | (0.4 * t <sub>sysclk</sub> ) + 2.0 | _                                  | $(0.4 \text{ x} \text{ t}_{\text{sysclk}}) + 2.0$ | _                                         | 8, 1    |

| 21    | SYSCLK to ARTRY high impedance after precharge                                                    | _                                  | (1.5 * t <sub>sysclk</sub> ) + 8.0 | _                                                 | $(1.5 \text{ x} t_{\text{sysclk}}) + 8.0$ | 8, 1    |

These values are guaranteed by design and are not tested.

Output specifications are measured from 1.4 V on the rising edge of the appropriate clock to the TTL level (0.8 V or 2.0 V) of the signal in question. Both input and output timings are measured at the pin (see Figure 5).

$<sup>^{3}</sup>$  The maximum timing specification assumes  $C_L = 50$  pF.

<sup>&</sup>lt;sup>4</sup> The shared outputs TS and ARTRY require pull-up resistors to hold them negated when there is no bus master driving them.

<sup>&</sup>lt;sup>5</sup> When the 106 is configured for asynchronous L2 cache SRAMs, the DWE[0–2] signals have a maximum SYSCLK to output valid time of (0.5 x t<sub>PROC</sub>) + 8.0 ns (where t<sub>PROC</sub> is the 60x bus clock cycle time).

<sup>&</sup>lt;sup>6</sup> PCI 3.3 V signaling environment signals are measured from 1.65 V (Vdd  $\div$  2) on the rising edge of SYSCLK to  $V_{OH} = 3.0 \text{ V}$  or  $V_{OL} = 0.3 \text{ V}$ .

$<sup>^{7}</sup>$  The minimum timing specification assumes  $C_L = 0$  pF.

<sup>8</sup> t<sub>sysclk</sub> is the period of the external bus clock (SYSCLK) in nanoseconds (ns). When the unit is given as t<sub>sysclk</sub> the numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.

<sup>&</sup>lt;sup>9</sup> PCI devices which require more than the PCI-specified hold time of T<sub>h</sub> = 0ns or systems where clock skew approaches the PCI-specified allowance of 2ns may not work with the MPC106. For workarounds, see Motorola application note *Designing PCI 2.1-Compliant MPC106 Systems* (order number AN1727/D).

Figure 5 provides the output timing diagram for the 106.

Figure 5. Output Timing Diagram

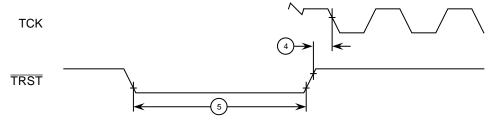

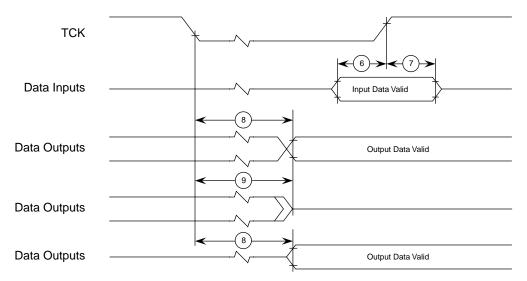

## 1.4.3 JTAG AC Timing Specifications

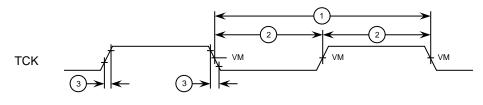

Table 9 provides the JTAG AC timing specifications. Assume Vdd = AVdd =  $3.3 \pm 5\%$  V DC, GND = 0 V DC, CL = 50 pF, and  $0 \le T_j \le 105$  °C.

| Num | Characteristic                          | Min | Max | Unit | Notes |

|-----|-----------------------------------------|-----|-----|------|-------|

| _   | TCK frequency of operation              | 0   | 25  | MHz  | _     |

| 1   | TCK cycle time                          | 40  | _   | ns   | _     |

| 2   | TCK clock pulse width measured at 1.4 V | 20  | _   | ns   | _     |

| 3   | TCK rise and fall times                 | 0   | 3   | ns   | 1     |

| 4   | TRST setup time to TCK rising edge      | 10  | _   | ns   | 2     |

| 5   | TRST assert time                        | 10  | _   | ns   | 1     |

Table 9. JTAG AC Timing Specifications (Independent of SYSCLK)

Table 9. JTAG AC Timing Specifications (Independent of SYSCLK) (Continued)

| Num | Characteristic                      | Min | Max | Unit | Notes |

|-----|-------------------------------------|-----|-----|------|-------|

| 6   | Boundary-scan input data setup time | 5   | _   | ns   | 3     |

| 7   | Boundary-scan input data hold time  | 15  | _   | ns   | 3     |

| 8   | TCK to output data valid            | 0   | 30  | ns   | 4     |

| 9   | TCK to output high impedance        | 0   | 30  | ns   | 4     |

| 10  | TMS, TDI data setup time            | 5   | _   | ns   | _     |

| 11  | TMS, TDI data hold time             | 15  | _   | ns   | 1     |

| 12  | TCK to TDO data valid               | 0   | 15  | ns   | _     |

| 13  | TCK to TDO high impedance           | 0   | 15  | ns   | _     |

- <sup>1</sup> These values are guaranteed by design, and are not tested

- <sup>2</sup> TRST is an asynchronous signal. The setup time is for test purposes only.

- <sup>3</sup> Non-test signal input timing with respect to TCK.

- <sup>4</sup> Non-test signal output timing with respect to TCK.

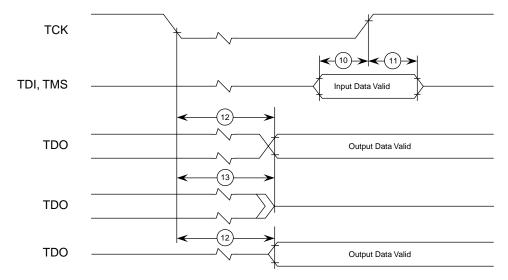

Figure 6 provides the JTAG clock input timing diagram.

VM = Midpoint Voltage (1.4 V)

Figure 6. JTAG Clock Input Timing Diagram

Figure 7 provides the TRST timing diagram.

Figure 7. TRST Timing Diagram

### **Electrical and Thermal Characteristics**

Figure 8 provides the boundary-scan timing diagram.

Figure 8. Boundary-Scan Timing Diagram

Figure 9 provides the test access port timing diagram.

Figure 9. Test Access Port Timing Diagram

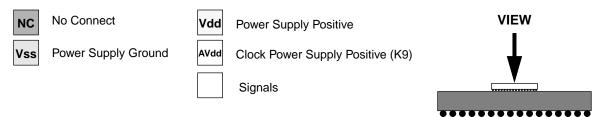

## 1.5 Pin Assignments

Figure 10 contains the pin assignments for the MPC106, and Figure 11 provides a key to the shading.

|   | 16                       | 15                              | 14            | 13             | 12           | 11            | 10             | 9     | 8      | 7    | 6          | 5             | 4                    | 3                     | 2      | 1              |   |

|---|--------------------------|---------------------------------|---------------|----------------|--------------|---------------|----------------|-------|--------|------|------------|---------------|----------------------|-----------------------|--------|----------------|---|

| W | DL26                     | DL28                            | DL30          | DH31           | DH29         | DH27          | DH25           | DH23  | DH21   | DH19 | DH17       | DH15          | DH13                 | DH11                  | DH9    | DH7            | W |

| ٧ | DL24                     | DL27                            | DL29          | DL31           | DH30         | DH28          | DH26           | DH24  | DH20   | DH18 | DH16       | DH14          | DH12                 | DH10                  | DH8    | DL22           | ٧ |

| U | MA1/<br>SDBA0/<br>AR9    | DL23                            | DL25          | DL14           | PLL2         | PLL0          | DL12           | DL10  | DL4    | DL2  | DL0        | DOE/<br>DBGL2 | TOE<br>DBG1          | DH6                   | DL21   | DL20           | U |

| Т | MA2/<br>SDMA2/<br>AR10   | WE                              | DH0           | DL15           | PLL3         | PLL1          | DL13           | DL11  | DL3    | DL1  | TV/<br>BR2 | BA0/<br>BR3   | HIT                  | DIRTY_IN/<br>BR1      | DL19   | DCS/<br>BG3    | Т |

| R | MA3/<br>SDMA3/<br>AR11   | RCS0                            | DH2           | DH1            | DL16         | Vss           | Vdd            | DL9   | DL5    | Vss  | Vdd        | TWE/<br>BG2   | DIRTY_OUT/<br>BG1    | ADS/<br>DALE/<br>BRL2 | A0     | TS             | R |

| Р | MA5/<br>SDMA5/<br>AR13   | MA4/<br>SDMA4/<br>AR12          | DH4           | DH3            | Vss          | Vdd           | Vss            | DL8   | DL6    | Vdd  | Vss        | Vdd           | BA1/<br>BAA/<br>BGL2 | DWE0/<br>DBG2         | A1     | XATS/SDMA<br>1 | Р |

| N | MA6/<br>SDMA6/<br>AR14   | MA0/<br>SDBA1/<br>SDMA0/<br>AR0 | DL17          | DH5            | Vdd          | Vss           | Vdd            | DL7   | DH22   | Vss  | Vdd        | Vss           | LBCLAIM              | CI                    | A2     | TA             | N |

| М | MA8/<br>SDMA8/<br>AR16   | MA7/<br>SDMA7/<br>AR15          | RASO/<br>CSO  | DL18           | Vss          | Vdd           | Vss            | NC    | NC     | Vdd  | Vss        | Vdd           | WT                   | GBL                   | A3     | TT4            | М |

| L | HRST                     | MA9/<br>SDMA9/<br>AR17          | QACK          | RAS1/<br>CS1   | Vdd          | CKO/<br>DWE2  | RAS5/<br>CS5   | Vss   | Vdd    | Vss  | SYSCLK     | DBG0          | TBST                 | BR0                   | A4     | TT3            | L |

| K | MA11/<br>SDMA11/<br>AR19 | MA10/<br>SDMA10/<br>AR18        | RAS3/<br>CS3  | RAS2/<br>CS2   | RAS4/<br>CS4 | RAS7/<br>CS7  | Vdd            | AVdd  | Vss    | Vdd  | A9         | A8            | A7                   | BG0                   | A5     | TT2            | к |

| J | MA12/<br>SDMA12/<br>AR20 | CASO/<br>DQM0                   | PPEN          | RCS1           | RAS6/<br>CS6 | MCP           | DBGLB/<br>CKE  | Vss   | Vdd    | Vss  | A11        | A6            | A13                  | A12                   | A10    | TEA            | J |

| Н | QREQ                     | CAS1/<br>DQM1                   | SUSPEND       | TRST           | Vss          | DWE1/<br>DBG3 | PIRQ/<br>SDRAS | NC    | NC     | Vdd  | Vss        | Vdd           | A15                  | A14                   | A16    | TT1            | Н |

| G | CAS2/<br>DQM2            | RTC                             | CAS4/<br>DQM4 | CAS5/<br>DQM5  | Vdd          | LSSD_MODE     | Vdd            | PAR   | LOCK   | Vss  | Vdd        | Vss           | TSIZ1                | TSIZ0                 | A17    | TT0            | G |

| F | BCTL0                    | BCTL1                           | CAS6/<br>DQM6 | TCK            | Vss          | Vdd           | Vss            | PERR  | DEVSEL | Vdd  | Vss        | Vdd           | A21                  | TSIZ2                 | ĀRTRY  | A18            | F |

| Е | CAS3/<br>DQM3            | NMI                             | CAS7/<br>DQM7 | MDLE/<br>SDCAS | TDO          | Vss           | Vdd            | SERR  | IRDY   | Vss  | Vdd        | A31           | A29                  | A22                   | A20    | A19            | Е |

| D | PAR0/<br>AR1             | PAR1/<br>AR2                    | TMS           | FOE            | AD28         | AD24          | AD21           | AD17  | AD14   | AD10 | C/BE0      | AD4           | AD0                  | A30                   | ĀĀCK   | A23            | D |

| С | PAR2/<br>AR3             | PAR3/<br>AR4                    | PAR5/<br>AR6  | AD30           | AD26         | AD23          | AD19           | C/BE2 | C/BE1  | AD12 | AD8        | AD6           | AD2                  | A27                   | A25    | A24            | С |

| В | PAR4/<br>AR5             | PAR7/<br>AR8                    | AD1           | TDI            | AD7          | AD11          | AD15           | TRDY  | AD18   | AD22 | AD25       | AD29          | REQ                  | ISA_MASTER/<br>BERR   | A28    | A26            | В |

| Α | PAR6/<br>AR7             | GNT                             | AD3           | AD5            | AD9          | AD13          | FRAME          | STOP  | AD16   | AD20 | C/BE3      | AD27          | AD31                 | FLSHREQ               | MEMACK |                | Α |

|   | 16                       | 15                              | 14            | 13             | 12           | 11            | 10             | 9     | 8      | 7    | 6          | 5             | 4                    | 3                     | 2      | 1              | - |

Figure 10. Pin Assignments

Figure 11. Pin Assignments Shading Key

## 1.6 Pinout Listings

Table 10 provides the pinout listing for the MPC106. Some signals have dual functions and are shown more than once.

**Table 10. Pinout Listing**

| Signal Name          | Pin Number                                                                                                                                     | Active | I/O    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| x Processor Interfac | e Signals                                                                                                                                      |        |        |

| A[0-31]              | A[0–31] R2, P2, N2, M2, L2, K2, J5, K4, K5, K6, J2, J6, J3, J4, H3, H4, H2, G2, F1, E1, E2, F4, E3, D1, C1, C2, B1, C3, B2, E4, D3, E5         |        | I/O    |

| AACK                 | D2                                                                                                                                             | Low    | I/O    |

| ARTRY                | F2                                                                                                                                             | Low    | I/O    |

| BG0                  | К3                                                                                                                                             | Low    | Output |

| BG1<br>(DIRTY_OUT)   | R4                                                                                                                                             | Low    | Output |

| BG2<br>(TWE)         | R5                                                                                                                                             | Low    | Output |

| BG3<br>(DCS)         | T1                                                                                                                                             | Low    | Output |

| BR0                  | L3                                                                                                                                             | Low    | Input  |

| BR1<br>(DIRTY_IN)    | ТЗ                                                                                                                                             | Low    | Input  |

| BR2<br>(TV)          | T6                                                                                                                                             | Low    | Input  |

| BR3<br>(BA0)         | T5                                                                                                                                             | Low    | Input  |

| CI                   | N3                                                                                                                                             | Low    | I/O    |

| DBG0                 | L5                                                                                                                                             | Low    | Output |

| DBG1<br>(TOE)        | U4                                                                                                                                             |        | Output |

| DBG2<br>(DWE0)       | <u>52</u> P3                                                                                                                                   |        | Output |

| DBG3<br>(DWE1)       | H11                                                                                                                                            | Low    | Output |

| DBGLB<br>(CKE)       | J10                                                                                                                                            | Low    | Output |

| DH[0-31]             | T14, R13, R14, P13, P14, N13, U3, W1, V2, W2, V3, W3, V4, W4, V5, W5, V6, W6, V7, W7, V8, W8, N8, W9, V9, W10, V10, W11, V11, W12, V12, W13    |        | I/O    |

| DL[0-31]             | U6, T7, U7, T8, U8, R8, P8, N9, P9, R9, U9, T9, U10, T10, U13, T13, R12, N14, M13, T2, U1, U2, V1, U15, V16, U14, W16, V15, W15, V14, W14, V13 | High   | I/O    |

| GBL                  | M3                                                                                                                                             | Low    | I/O    |

**Table 10. Pinout Listing (Continued)**

| Signal Name             | Pin Number         | Active | I/O    |  |

|-------------------------|--------------------|--------|--------|--|

| LBCLAIM                 | N4                 | Low    | Input  |  |

| MCP                     | J11                | Low    | Output |  |

| TA                      | N1                 | Low    | I/O    |  |

| TBST                    | L4                 | Low    | I/O    |  |

| TEA                     | J1                 | Low    | Output |  |

| TS                      | R1                 | Low    | I/O    |  |

| TSIZ[0-2]               | G3, G4, F3         | High   | I/O    |  |

| TT[0-4]                 | G1, H1, K1, L1, M1 | High   | I/O    |  |

| WT                      | M4                 | Low    | I/O    |  |

| XATS<br>(SDMA1)         | P1                 | Low    | Input  |  |

| L2 Cache Interface Sign | nals               |        | 1      |  |

| ADS/DALE/BRL2           | R3                 | Low    | I/O    |  |

| BA0<br>(BR3)            | T5                 | Low    | Output |  |

| BA1/BAA/BGL2            | P4                 | Low    | Output |  |

| DBGL2/DOE               | U5                 | Low    | Output |  |

| DCS<br>(BG3)            | T1                 | Low    | Output |  |

| DIRTY_IN<br>(BR1)       | Т3                 | Low    | Input  |  |

| DIRTY_OUT<br>(BG1)      | R4                 | Low    | Output |  |

| DWE0<br>(DBG2)          | P3                 | Low    | Output |  |

| DWE1<br>(DBG3)          | H11                | Low    | Output |  |

| DWE2<br>(CKO)           | L11                | Low    | Output |  |

| HIT                     | T4                 | Low    | Input  |  |

| TOE<br>(DBG1)           | U4                 | Low    | Output |  |

| TV<br>(BR2)             | Т6                 | High   | I/O    |  |

| TWE<br>(BG2)            | R5                 | Low    | Output |  |

| Memory Interface Sign   | als                | I      | 1      |  |

| BCTL[0-1]               | F16, F15           | Low    | Output |  |

| BERR<br>(ISA_MASTER)    | B3                 | Low    | Input  |  |

### **Pinout Listings**

**Table 10. Pinout Listing (Continued)**

| Signal Name                       | Pin Number                                                                                                                                    | Active | I/O    |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| CAS/DQM[0-7]                      | J15, H15, G16, E16, G14, G13, F14, E14                                                                                                        | Low    | Output |

| CKE/DBGLB                         | J10                                                                                                                                           | High   | Output |

| FOE                               | D13                                                                                                                                           | Low    | Output |

| MA0/SDBA1/SDMA0/AR0               | N15                                                                                                                                           | High   | Output |

| SDMA1<br>(XATS)                   | P1                                                                                                                                            | High   | Output |

| MA1/SDBA0/AR9                     | U16                                                                                                                                           | High   | Output |

| MA[2-12]/SDMA[2-12]/AR<br>[10-20] | T16, R16, P15, P16, N16, M15, M16, L15, K15, K16, J16                                                                                         | High   | Output |

| MDLE/SDCAS                        | E13                                                                                                                                           | Low    | Output |

| PAR[0-7]/AR[1-8]                  | D16, D15, C16, C15, B16, C14, A16, B15                                                                                                        | High   | I/O    |

| PPEN                              | J14                                                                                                                                           | Low    | Output |

| RAS/CS[0-7]                       | M14, L13, K13, K14, K12, L10, J12, K11                                                                                                        | Low    | Output |

| RCS0                              | R15                                                                                                                                           | Low    | I/O    |

| RCS1                              | J13                                                                                                                                           | Low    | Output |

| RTC                               | G15                                                                                                                                           | High   | Input  |

| SDRAS<br>(PIRQ)                   | H10                                                                                                                                           | Low    | Output |

| WE                                | T15                                                                                                                                           | Low    | Output |

| PCI Interface Signals1            |                                                                                                                                               |        | •      |

| AD[31-0]                          | A4, C13, B5, D12, A5, C12, B6, D11, C11, B7, D10, A7, C10, B8, D9, A8, B10, D8, A11, C7, B11, D7, A12, C6, B12, C5, A13, D5, A14, C4, B14, D4 | High   | I/O    |

| C/BE[3-0]                         | A6, C9, C8, D6                                                                                                                                | Low    | I/O    |

| DEVSEL                            | F8                                                                                                                                            | Low    | I/O    |

| FLSHREQ                           | A3                                                                                                                                            | Low    | Input  |

| FRAME                             | A10                                                                                                                                           | Low    | I/O    |

| GNT                               | A15                                                                                                                                           | Low    | Input  |

| ĪRDY                              | E8                                                                                                                                            | Low    | I/O    |

| ISA_MASTER<br>(BERR)              | B3                                                                                                                                            | Low    | Input  |

| LOCK                              | G8                                                                                                                                            | Low    | Input  |

| MEMACK                            | A2                                                                                                                                            | Low    | Output |

| PAR                               | G9                                                                                                                                            | High   | I/O    |

| PERR                              | F9                                                                                                                                            | Low    | I/O    |

| PIRQ<br>(SDRAS)                   | H10                                                                                                                                           | Low    | Output |

| REQ                               | B4                                                                                                                                            | Low    | Output |

**Table 10. Pinout Listing (Continued)**

| Signal Name              | Pin Number                                                                                                        | Active | I/O            |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|--------|----------------|--|

| SERR                     | E9                                                                                                                | Low    | I/O            |  |

| STOP                     | A9                                                                                                                | Low    | I/O            |  |

| TRDY                     | B9                                                                                                                | Low    | I/O            |  |

| Interrupt, Clock, and Po | ower Management Signals                                                                                           | !      |                |  |

| CKO<br>(DWE2)            | L11                                                                                                               | High   | Output         |  |

| HRST                     | L16                                                                                                               | Low    | Input          |  |

| NMI                      | E15                                                                                                               | High   | Input          |  |

| QACK                     | L14                                                                                                               | Low    | Output         |  |

| QREQ                     | H16                                                                                                               | Low    | Input          |  |

| SYSCLK                   | L6                                                                                                                | Clock  | Input          |  |

| SUSPEND                  | H14                                                                                                               | Low    | Input          |  |

| Test/Configuration Sign  | nals                                                                                                              | !      |                |  |

| PLL[0-3]                 | U11, T11, U12, T12                                                                                                | High   | Input          |  |

| TCK                      | F13                                                                                                               | Clock  | Input          |  |

| TDI                      | B13                                                                                                               | High   | Input          |  |

| TDO                      | E12                                                                                                               | High   | Output         |  |

| TMS                      | D14                                                                                                               | High   | Input          |  |

| TRST                     | H13                                                                                                               | Low    | Input          |  |

| Power and Ground Sign    | nals                                                                                                              | •      |                |  |

| AVdd                     | K9                                                                                                                | High   | Clock<br>Power |  |

| LSSD_MODE 2              | G11                                                                                                               | Low    | Input          |  |

| Vdd                      | E10, E6, F11, F5, F7, G10, G12, G6, H5, H7, K10, K7, L12, M11, M5, M7, N10, N12, N6, P11, P5, P7, R10, R6, J8, L8 | High   | Power          |  |

| Vss                      | E11, E7, F10, F12, F6, G5, G7, H12, H6, J7, L7, M10, M12, M6, N11, N5, N7, P10, P12, P6, R11, R7, K8, J9, L9      | Low    | Ground         |  |

| NC                       | H8, H9, M8, M9                                                                                                    | _      | -              |  |

Note:

1 All PCI signals are in little-endian bit order.

$<sup>^{\</sup>rm 2}\,$  This test signal is for factory use only. It must be pulled up to Vdd for normal device operation.

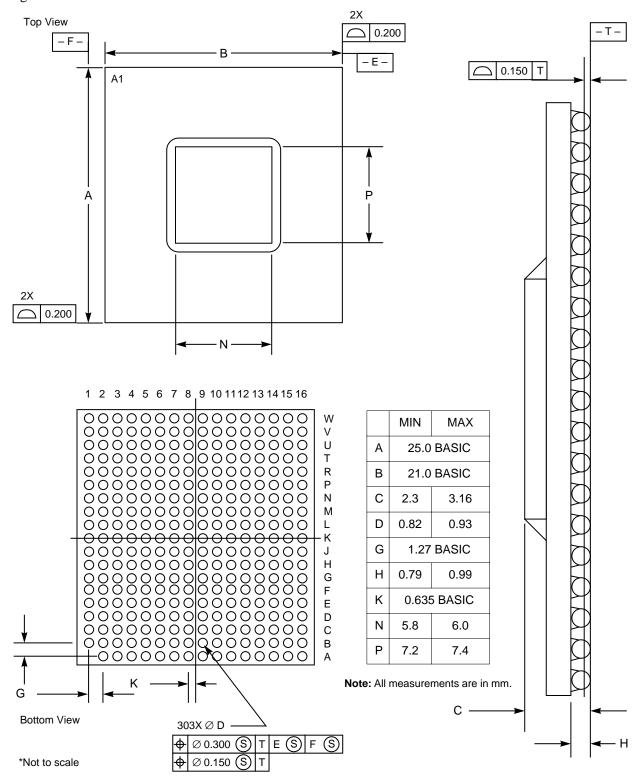

## 1.7 Package Description

The following sections provide the package parameters and the mechanical dimensions for the 106.

## 1.7.1 Package Parameters

The package parameters are as provided in the following list. The package type is a 21 mm x 25 mm, 304-lead C4 ceramic ball grid array (CBGA).

Package outline 21 mm x 25 mm

Interconnects 303 (16 x 19 ball array minus one)

Pitch 1.27 mm Solder attach 63/37 Sn/Pb

Solder balls 10/90 Sn/Pb, 0.89 mm diameter

Maximum module height 3.16 mm

Co-planarity specification 0.15 mm

## 1.7.2 Mechanical Dimensions

Figure 12 shows the mechanical dimensions for the MPC106.

Figure 12. Mechanical Dimensions

## 1.8 System Design Information

This section provides electrical and thermal design recommendations for successful application of the 106.

## 1.8.1 PLL Configuration

The 106 requires a single system clock input, SYSCLK. The SYSCLK frequency dictates the frequency of operation for the PCI bus. An internal PLL on the MPC106 generates a master clock that is used for all of the internal (core) logic. The master clock provides the core frequency reference and is phase-locked to the SYSCLK input. The 60x processor, L2 cache, and memory interfaces operate at the core frequency. In the 5:2 clock mode (Rev. 4.0 only), the MPC106 needs to sample the 60x bus clock (on the LBCLAIM configuration input) to resolve clock phasing with the PCI bus clock (SYSCLK).

The PLL is configured by the PLL[0–3] signals. For a given SYSCLK (PCI bus) frequency, the clock mode configuration signals (PLL[0–3]) set the core frequency (and the frequency of the VCO controlling the PLL lock). The supported core and VCO frequencies and the corresponding PLL[0–3] settings are provided in Table 11.

|                       | Core/SYSCL VCO   |                    | Core Frequency (VCO Frequency) in MHz                                      |                     |                     |                     |

|-----------------------|------------------|--------------------|----------------------------------------------------------------------------|---------------------|---------------------|---------------------|

| PLL[0-3] <sup>1</sup> | K Ratio          | Multiplier         | PCI Bus<br>16.6 MHz                                                        | PCI Bus<br>20 MHz   | PCI Bus<br>25 MHz   | PCI Bus<br>33.3 MHz |

| 0001                  | 1:1              | x4                 | _                                                                          | _                   | _                   | 33.3 (133)          |

| 0100                  | 2:1              | x2                 | _                                                                          | _                   | _                   | 66.6 (133)          |

| 0101                  | 2:1              | x4                 | 33.3 (133)                                                                 | 40 (160)            | 50 (200)            | _                   |

| 0110                  | 5:2 <sup>2</sup> | x2                 | _                                                                          | _                   | _                   | 83.3 (166)          |

| 0111                  | 5:2 <sup>2</sup> | x4                 | 41.6 (166)                                                                 | _                   | _                   | _                   |

| 1000                  | 3:1              | x2                 | _                                                                          | 60(120)             | 75 (150)            | _                   |

| 0011                  | PLL-by           | pass <sup>3</sup>  | PLL off SYSCLK clocks core circuitry directly 1x core/SYSCLK ratio implied |                     |                     |                     |

| 1111                  | Clock            | c off <sup>4</sup> |                                                                            | PLL<br>no core clos | off<br>cking occurs |                     |

**Table 11. PLL Configuration**

#### Notes

- PLL[0-3] settings not listed are reserved. Some PLL configurations may select bus, CPU, or VCO frequencies which are not useful, not supported, or not tested. See Section 1.4.2.1, "Clock AC Specifications," for valid SYSCLK and VCO frequencies.

- 5:2 clock modes are only supported by MPC106 Rev 4.0; earlier revisions do not support 5:2 clock modes. The 5:2 modes require a 60x bus clock applied to the 60x clock phase (LBCLAIM) configuration input signal during power-on reset, hard reset, and coming out of sleep and suspend power-saving modes.

- In PLL-bypass mode, the SYSCLK input signal clocks the internal circuitry directly, the PLL is disabled, and the core/SYSCLK ratio is set for 1:1 mode operation. This mode is intended for factory use and third-party tool vendors only. Note also: The AC timing specifications given in this document do not apply in PLL-bypass mode.

- <sup>4</sup> In clock-off mode, no clocking occurs inside the MPC106 regardless of the SYSCLK input.

- <sup>5</sup> PLL[0-3] = 0010 (2:1 Core/SYSCLK Ratio; X8 VCO multiplier) exists on the chip but will fail to lock 50% of the time. Therefore, this configuration should not be used and 1:1 modes between 16-25MHz are not supported.

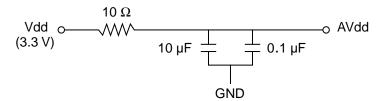

## 1.8.2 PLL Power Supply Filtering

The AVdd power signal is provided on the 106 to provide power to the clock generation phase-locked loop. To ensure stability of the internal clock, the power supplied to the AVdd input signal should be filtered using a circuit similar to the one shown in Figure 13. The circuit should be placed as close as possible to the AVdd pin to ensure it filters out as much noise as possible.

Figure 13. PLL Power Supply Filter Circuit

## 1.8.3 Decoupling Recommendations

Due to the 106's large address and data buses and high operating frequencies, it can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the system, and the 106 itself requires a clean, tightly regulated source of power.

It is strongly recommended that the system design include six to eight 0.1  $\mu$ F (ceramic) and 10  $\mu$ F (tantalum) decoupling capacitors to provide both high- and low-frequency filtering. These capacitors should be placed closely around the perimeter of the 106 package (or on the underside of the PCB). It is also recommended that these decoupling capacitors receive their power from separate Vdd and GND power planes in the PCB, utilizing short traces to minimize inductance. Only surface mount technology (SMT) capacitors should be used to minimize lead inductance.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the Vdd plane, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low equivalent series resistance (ESR) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors— $100 \, \mu F$  (AVX TPS tantalum) or  $330 \, \mu F$  (AVX TPS tantalum).

## 1.8.4 Connection Recommendations

To ensure reliable operation, it is recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied (using pull-up resistors) to Vdd. Unused active high inputs should be tied (using pull-down resistors) to GND. All no-connect (NC) signals must remain unconnected.

Power and ground connections must be made to all external Vdd, AVdd, and GND pins of the 106.

## 1.8.4.1 Pull-up Resistor Recommendations

The MPC106 requires pull-up (or pull-down) resistors on several control signals of the 60x and PCI buses to maintain the control signals in the negated state after they have been actively negated and released by the 106 or other bus masters. The JTAG test reset signal, TRST, should be pulled down during normal system operation. Also, as indicated in Table 10, the factory test signal, LSSD\_MODE, must be pulled up for normal device operation

During inactive periods on the bus, the address and transfer attributes on the bus (A[0–31], TT[0-4],  $\overline{TBST}$ ,  $\overline{WT}$ ,  $\overline{CI}$ , and  $\overline{GBL}$ ) are not driven by any master and may float in the high-impedance state for relatively long periods of time. Since the MPC106 must continually monitor these signals, this float

### **System Design Information**

condition may cause excessive power draw by the input receivers on the MPC106 or by other receivers in the system. It is recommended that these signals be pulled up or restored in some manner by the system.

The 60x data bus input receivers on the MPC106 do not require pull-up resistors on the data bus signals (DH[0-31], DL[0-31], and PAR[0-7]). However, other data bus receivers in the system may require pull-up resistors on these signals.

In general, the 60x address and control signals are pulled up to 3.3 VDC and the PCI control signals are pulled up to 5 VDC through weak  $(2-10 \text{ k}\Omega)$  resistors. Resistor values may need to be adjusted stronger to reduce induced noise on specific board designs. Table 12 summarizes the pull-up/pull-down recommendations for the MPC106.

Pull-Up/Pull-Down Signal Type **Signals**  $\overline{\mathsf{BR}}n$ 60x bus control Pull up to 3.3 VDC TS, XATS, AACK **ARTRY** TA A[0-31], TT[0-4], TBST Pull up to 3.3 VDC 60x bus address/transfer WT, CI, GBL attributes **ADS** Pull up to 3.3 VDC Cache control HIT. TV Pull up to 3.3 VDC or pull-down to GND depending on programmed polarity PCI bus control **REQ** Typically pull up to 5 VDC FRAME, IRDY DEVSEL, TRDY, STOP Note: For closed systems not requiring 5V power. SERR. PERR these may be pulled up to 3.3 VDC. **LOCK** FLSHREQ, ISA\_MASTER. **JTAG** TRST Pull down to GND (during normal system operation) LSSD\_MODE Factory test Pull up to 3.3 VDC

Table 12. Pull-Up/Pull-Down Recommendations

## 1.8.5 Thermal Management Information

This section provides thermal management information for the C4/CBGA package. Proper thermal control design is primarily dependent on the system-level design.

The use of C4 die on a CBGA interconnect technology offers significant reduction in both the signal delay and the microelectronic packaging volume. Figure 14 shows the salient features of the C4/CBGA interconnect technology. The C4 interconnection provides both the electrical and the mechanical connections for the die to the ceramic substrate. After the C4 solder bump is reflowed, epoxy (encapsulant) is under-filled between the die and the substrate. Under-fill material is commonly used on large high-power die; however, this is not a requirement of the C4 technology. The package substrate is a multilayer-cofired ceramic. The package-to-board interconnection is by an array of orthogonal 90/10 (lead/tin) solder balls on 1.27 mm pitch. During assembly of the C4/CBGA package to the board, the high-melt balls do not collapse.

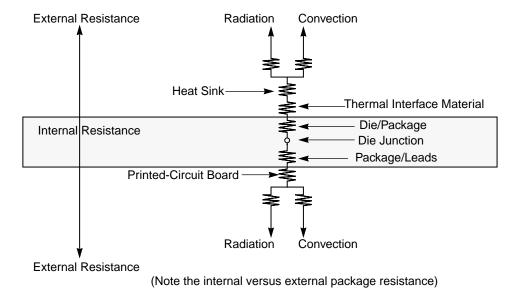

## 1.8.5.1 Internal Package Conduction Resistance

For this C4/CBGA packaging technology, the intrinsic conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance

- The die junction-to-lead thermal resistance

These parameters are shown in Table 13. In this C4/CBGA package, the silicon chip is exposed; therefore, the package "case" is the top of the silicon.

Table 13. Thermal Resistance

| Thermal Metric                             | Effective Thermal Resistance |  |

|--------------------------------------------|------------------------------|--|

| Junction-to-case thermal resistance        | 0.133 °C/W                   |  |

| Junction-to-lead (ball) thermal resistance | 3.8 °C/W                     |  |

Figure 15 provides a simplified thermal network in which a C4/CBGA package is mounted to a printed-circuit board.

Figure 15. C4/CBGA Package Mounted to a Printed-Circuit Board

## 1.8.5.2 Board and System-Level Modeling

A common figure-of-merit used for comparing the thermal performance of various microelectronic packaging technologies is the junction-to-ambient thermal resistance. The final chip-junction operating temperature is not only a function of the component-level thermal resistance, but the system-level design and its operating conditions. In addition to the component's power consumption, a number of factors affect the final operating die-junction temperature. For example, these factors might include airflow, board population, heat sink efficiency, heat sink attach, next-level interconnect technology, and system air temperature rise.

Due to the complexity and the many variations of system-level boundary conditions for today's microelectronic equipment, the combined effects of the heat transfer mechanisms (radiation, convection, and conduction) may vary widely. For this reason, we recommend using conjugate heat transfer models for the board as well as system-level designs. To expedite system-level thermal analysis, several "compact" CBGA thermal models are available on request within FLOTHERM<sup>®</sup>.

The die junction-to-ambient thermal resistance is shown in Table 14. The model results are in accordance with SEMI specification G38. This standard specifies a single component be placed on a 7.5 cm x 10 cm single-layer printed-circuit card. Note that this single metric may not adequately describe three-dimensional heat flow.

Table 14. Die Junction-to-Ambient Thermal Resistance

| Airflow Velocity<br>(Meter/Second) | Airflow Velocity<br>(Feet/Minute) | Die Junction-to-AmbientThermal Resistance<br>(SEMI G38) (°C/W) |

|------------------------------------|-----------------------------------|----------------------------------------------------------------|

| 1                                  | 196.8                             | 22.0                                                           |

| 2                                  | 393.7                             | 18.5                                                           |

| 3                                  | 590.0                             | 17.0                                                           |

## 1.9 Document Revision History

Table 15 lists significant changes between revisions of this document.

**Table 15. Document Revision History**

| Document<br>Revision | Substantive Change(s)                                                                                                                                                                                                                                                             |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 0                | Initial release                                                                                                                                                                                                                                                                   |

| Rev 1                | Changed VCO maximum frequency in Table 6 to 200 MHz                                                                                                                                                                                                                               |

|                      | Changed input and Hi-Z leakage current in Table 4. from 10µA to 15µA                                                                                                                                                                                                              |

|                      | Changed I <sub>OH</sub> and I <sub>OL</sub> in Table 4 from 18mA and 14mA respectively to -7mA and 7mA to correct the sign and reduce the current to worst case value for the lowest strength default driver                                                                      |

|                      | Changed footnote 4 to Table 6 to be consistent with SYSCLK jitter spec of 200ps                                                                                                                                                                                                   |

|                      | Modified Table 7, Figure 3, Table 8, and Figure 5 to clarify reference clock (60x Bus Clock or SYSCLK) for input and output specifications                                                                                                                                        |

|                      | Changed Group I and Group II signals input setup requirement for 83 MHz in Table 7 from 3.0 ns to 3.5 ns min.                                                                                                                                                                     |

|                      | Changed Group I-IV (non-PCI signals) input hold requirement (Spec 11a) in Table 7 from 1.0 ns to 0 ns                                                                                                                                                                             |

|                      | Changed Group V and VI (PCI signals) input hold requirement (Spec 11b) in Table 7 from 1.0ns to -0.5ns                                                                                                                                                                            |

|                      | Changed output valid times for all non-PCI signals (Specs 13a, 13b and 14a) from 8 ns to 7 ns at 66 Mhz and from 7 ns to 6 ns at 83 MHz                                                                                                                                           |

|                      | Corrected Figure 10 to reflect TOE signal is shared with DBG1 on pin U5                                                                                                                                                                                                           |

| Rev 2                | Changed input and Hi-Z leakage current, V <sub>in</sub> in Table 4 from 5.5V to 3.3V                                                                                                                                                                                              |

|                      | Changed the power consumption data in Table 5                                                                                                                                                                                                                                     |

|                      | Changed note 7 of Table 8 to show the minimum timing specification assumes CL=0 pF                                                                                                                                                                                                |

| Rev 3                | Deleted PLL[0-3] = 0010 from Table 11 to remove 1:1 mode operation between 16MHz and 25MHz                                                                                                                                                                                        |

|                      | Added note 10 to Table 8 regarding PCI hold time                                                                                                                                                                                                                                  |