## *MPC82x52A*

# 8-bit micro-controller

| Features                                             | 3  |

|------------------------------------------------------|----|

| General Description                                  | 5  |

| Order Information:                                   | 5  |

| Pin Description                                      | 6  |

| Pin Definition                                       | 6  |

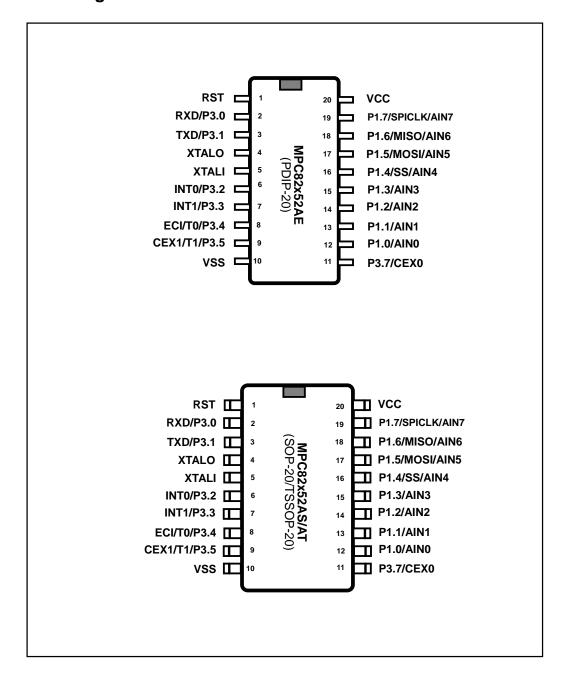

| Pin Configuration                                    | 10 |

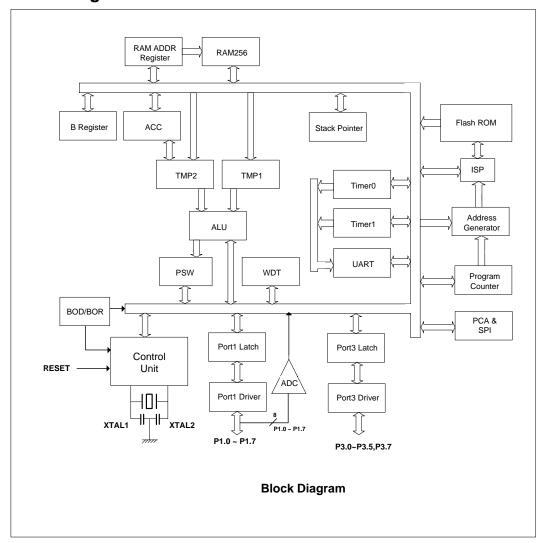

| Block Diagram                                        | 11 |

| Special Function Register                            | 12 |

| Address Map                                          | 12 |

| Bits Description                                     | 13 |

| Memory                                               | 15 |

| Organization                                         | 15 |

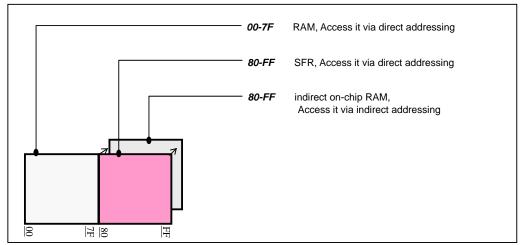

| RAM                                                  | 16 |

| Nonvolatile Registers:                               | 16 |

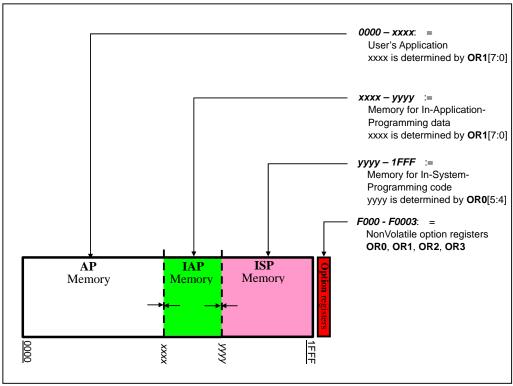

| Embedded Flash                                       | 19 |

| Functional Description                               | 20 |

| I/O Port Configuration                               | 20 |

| Timer/Counter                                        | 24 |

| Interrupt                                            | 29 |

| Watch Dog Timer                                      | 33 |

| Universal Asynchronous Serial Port (UART)            | 35 |

| Programmable Counter Array (PCA)                     | 38 |

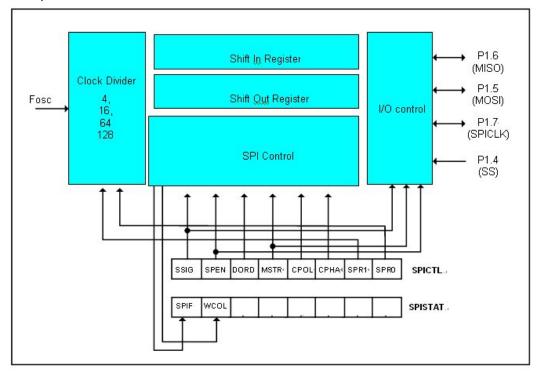

| Serial Peripheral Interface (SPI)                    | 47 |

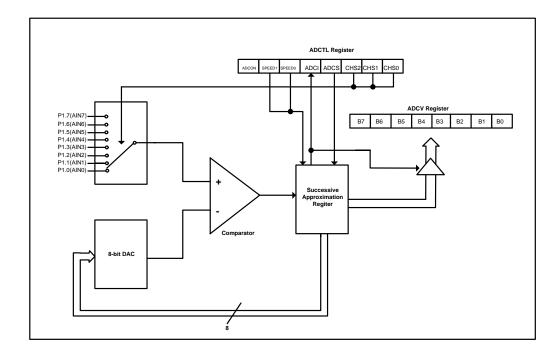

| Analog to Digital Converter                          | 54 |

| Built-In Oscillator                                  | 56 |

| Power-Up and Low Voltage Detector and Reset          | 56 |

| Power Management                                     | 57 |

| Reset and Boot Entrance                              | 59 |

| In System Programming and In Application Programming | 60 |

| In System Programming (ISP)                          | 60 |

| In-Application Program (IAP)                         | 63 |

| Avoid Inadvertent Data Lost from IAP/ISP             | 64 |

This document contains information on a new product under development by Megawin. Megawin reserves the right to change or discontinue this product without notice.

discontinue this product without notice.

© Megawin Technology Co., Ltd. 2008 All rights reserved.

| Instructions Set                    | 65 |

|-------------------------------------|----|

| Absolute Maximum Rating (MPC82E52A) | 68 |

| DC Characteristics (MPC82E52A)      |    |

| Absolute Maximum Rating (MPC82L52A) | 69 |

| DC Characteristics (MPC82L52A)      | 69 |

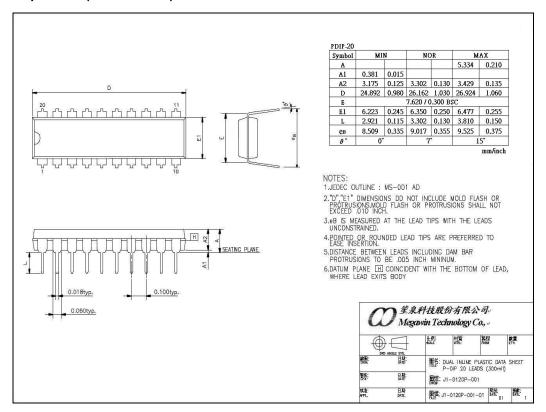

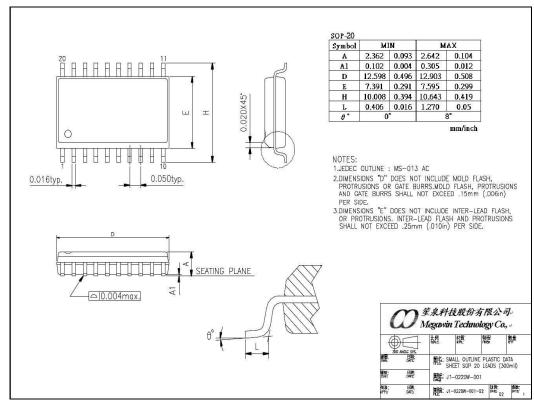

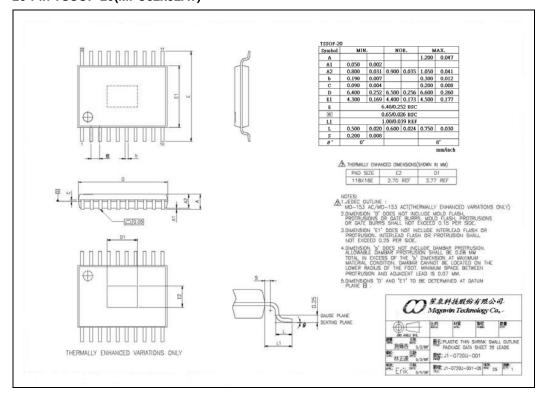

| Package Dimension                   |    |

| Revision History                    | 72 |

2

## **Features**

- Enhanced 80C51 Central Processing Unit

- 8 K bytes on-chip flash memory with ISP/IAP capability

- 256 bytes scratch-pad RAM

- Two-level code protection for flash memory access

- Two 16-bits timer/counter

- 7 sources, 4-level-priority interrupt capability

- One enhanced UART with automatic address recognition and frame error detection

- 15 bits Watch-Dog-Timer with 8-bit pre-scalar, one-time enabled

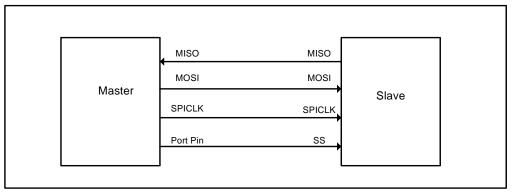

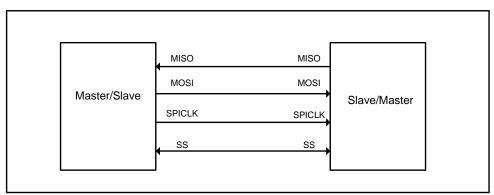

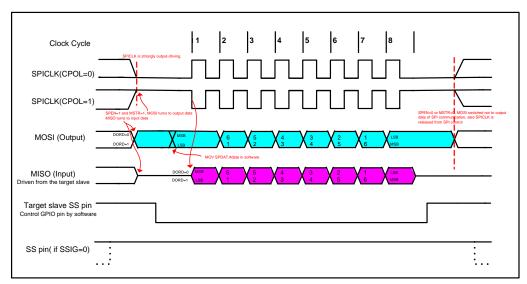

- SPI Master/Slave mode

- One Programmable Counter Array (PCA)

- 8-bit Analog-to-Digital Converter (ADC)

- Power control: Idle mode and Power-Down mode, Power-down can be woken-up through INT0 and INT1

- 15 programmable I/O ports

- Alternative built-in 6 MHz oscillator

- Fully static operation

- Excellent noise immunity

- Very low power consumption

- On-Chip flash program/data memory:

- The data endurance of the embedded flash gets over 20,000 times.

- Greater than 100 years data rentention under room temperature

- Operating Voltage:

- 4.5V~5.5V for MPC82E52A

- 2.4V~3.6V for MPC82L52A, minimum 2.7V requirement in flash write operation (ISP/ICP/.....)

- Built-in Low-Voltage Detector and Reset circuit.

- Operating Temperature

- Industrial (-40°C to +85°C)\*

- Maximum Operating Frequency:

- Up to 24MHz, Industrial range

- Package type:

- -PDIP-20: MPC82x52AE

- -SOP-20: MPC82E52AS

- -TSSOP-20: MPC82x52AT

- \*: Tested by sampling

MEGAWIN

4

## **General Description**

MPC82x52A is a single-chip 8-bit micro-controller with instruction sets fully compatible with industrial-standard 80C51 series micro controller.

There is an excellent MCU kernel built in this device compared to general 80C51 MCUs those take twelve oscillating cycles to finish an instruction, and this unique device would take only one oscillating cycle to finish one instruction.

There is 8 Kbytes flash memory embedded which could be used as program or data. Also the In-System Programming and In-Application Programming mechanisms are supported. The data endurance of the embedded flash gets over 20,000 times, and 21 years data retention is guaranteed.

The operation frequency reaches at 24 MHz. An user can apply a crystal oscillator for the oscillating source, or alternatively uses the built in 6 MHz RC oscillator to save system cost.

The built in high performance Analog-to-Digital Converter make it easy to sensing the environment or implement a set of scan keys in low cost.

The UART and SPI interfaces make the device convenient to communicate with the peripheral component, i.e., talking to a personal computer via RS-232 port, or communicating with a serial memory.

The Pulse-Width-Modulator (PWM) and Programmable Counter Array (PCA) make the device to drive the peripheral step motor or LED in least cost.

The MPC82x52A is really the most efficient MCU adapted for simple control: electronic scales, remote controller, security encoder/decoder, and user interface controller.

## **Order Information:**

| Part Number | Temperature | Package  | Packing | Operation     |

|-------------|-------------|----------|---------|---------------|

|             | Range       |          |         | Voltage       |

| MPC82x52AE  | Industrial  | PDIP-20  | Tube    | L: 3V / E: 5V |

| MPC82x52AS  | Industrial  | SOP-20   | Tube    | L: 3V / E: 5V |

| MPC82x52AT  | Industrial  | TSSOP-20 | Tube    | L: 3V / E: 5V |

# **Pin Description**

# **Pin Definition**

| Pin Name    | Pin Name | TYPE | DESCRIPTION                                                                                               |

|-------------|----------|------|-----------------------------------------------------------------------------------------------------------|

| RST         | 1        | ID   | RST: =                                                                                                    |

|             |          |      | A high duty on this pin keeps for at least 10us plus 36 oscillation cycles will reset the device.         |

| P3.0 (RXD)  | 2        | BU   | P3.0: =                                                                                                   |

|             |          |      | General purpose 4-state I/O port with internal pull-up mechanism; can be configured as open-drain output. |

|             |          |      | RXD: =                                                                                                    |

|             |          |      | Data Receiving pin for built-in UART functionality.                                                       |

| P3.1 (TXD)  | 3        | BU   | P3.1: =                                                                                                   |

|             |          |      | General purpose 4-state I/O port with internal pull-up mechanism; can be configured as open-drain output. |

|             |          |      | TXD: =                                                                                                    |

|             |          |      | Data Transmitting pin for built-in UART functionality.                                                    |

| XTALO       | 4        | 0    | XTALO: =                                                                                                  |

|             |          |      | Output from the inverting oscillator amplifier.                                                           |

| XTALI       | 5        | I    | XTALI: =                                                                                                  |

|             |          |      | Input to the inverting oscillator amplifier.                                                              |

| P3.2 (INT0) | 6        | BU   | P3.2: =                                                                                                   |

|             |          |      | General purpose 4-state I/O port with internal pull-up mechanism; can be configured as open-drain output. |

|             |          |      | INTO: =                                                                                                   |

|             |          |      | External interrupt source                                                                                 |

| P3.3 (INT1) | 7        | BU   | P3.3: =                                                                                                   |

|             |          |      | General purpose 4-state I/O port with internal pull-up                                                    |

|             |          |      | mechanism; can be configured as open-drain                                                                |

|             |          |      | output.                                                                                                   |

|             |          |      | INT1: =                                                                                                   |

|             |          |      | External interrupt source                                                                                 |

| Do 4 (FO: Fo:  |    |    | <b></b>                                                                                                   |  |  |  |  |  |

|----------------|----|----|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| P3.4 (ECI/T0)  | 8  | BU | P3.4: =                                                                                                   |  |  |  |  |  |

|                |    |    | General purpose 4-state I/O port with internal pull-up mechanism; can be configured as                    |  |  |  |  |  |

|                |    |    | pull-up mechanism; can be configured                                                                      |  |  |  |  |  |

|                |    |    | open-drain output.                                                                                        |  |  |  |  |  |

|                |    |    | ECI: =                                                                                                    |  |  |  |  |  |

|                |    |    | External Clock Input to Programmable Counter                                                              |  |  |  |  |  |

|                |    |    | Array (PCA)                                                                                               |  |  |  |  |  |

|                |    |    | T0: =                                                                                                     |  |  |  |  |  |

|                |    |    | Alternative clock input to timer-0                                                                        |  |  |  |  |  |

| P3.5 (CEX1/T1) | 9  | BU | P3.5: =                                                                                                   |  |  |  |  |  |

|                |    |    | General purpose 4-state I/O port with internal pull-up mechanism; can be configured as open-drain output. |  |  |  |  |  |

|                |    |    | CEX1: =                                                                                                   |  |  |  |  |  |

|                |    |    | Capture Event trigger to Programmable Counter                                                             |  |  |  |  |  |

|                |    |    | Array (PCA) module-1 or PWM output                                                                        |  |  |  |  |  |

|                |    |    | T1: =                                                                                                     |  |  |  |  |  |

|                |    |    | Alternative clock input to timer-1                                                                        |  |  |  |  |  |

| VSS            | 10 | G  | Ground                                                                                                    |  |  |  |  |  |

| P3.7 (CEX0)    | 11 | BU | P3.7: =                                                                                                   |  |  |  |  |  |

|                |    |    | General purpose 4-state I/O port with internal                                                            |  |  |  |  |  |

|                |    |    | pull-up mechanism; can be configured as                                                                   |  |  |  |  |  |

|                |    |    | open-drain output.                                                                                        |  |  |  |  |  |

|                |    |    | CEX0: =                                                                                                   |  |  |  |  |  |

|                |    |    | Capture Event trigger to Programmable Counter                                                             |  |  |  |  |  |

|                |    |    | Array (PCA) module-0 or PWM output                                                                        |  |  |  |  |  |

| P1.0 (AIN0)    | 12 | BU | P1.0: =                                                                                                   |  |  |  |  |  |

|                |    |    | General purpose 4-state I/O port with internal pull-up mechanism; can be configured as open-drain output. |  |  |  |  |  |

|                |    |    | AIN0: =                                                                                                   |  |  |  |  |  |

|                |    |    | Alternative ADC input                                                                                     |  |  |  |  |  |

| P1.1 (AIN1)    | 13 | BU | P1.1: =                                                                                                   |  |  |  |  |  |

| (,             |    |    | General purpose 4-state I/O port with internal                                                            |  |  |  |  |  |

|                |    |    | pull-up mechanism; can be configured as                                                                   |  |  |  |  |  |

|                |    |    | open-drain output.                                                                                        |  |  |  |  |  |

|                |    |    | AIN1: =                                                                                                   |  |  |  |  |  |

|                |    |    | Alternative ADC input                                                                                     |  |  |  |  |  |

| P1.2 (AIN2)    | 14 | BU | P1.2: =                                                                      |  |  |  |  |  |

|----------------|----|----|------------------------------------------------------------------------------|--|--|--|--|--|

|                |    |    | General purpose 4-state I/O port with internal                               |  |  |  |  |  |

|                |    |    | pull-up mechanism; can be configured as                                      |  |  |  |  |  |

|                |    |    | open-drain output.                                                           |  |  |  |  |  |

|                |    |    | AIN2: =                                                                      |  |  |  |  |  |

|                |    |    | Alternative ADC input                                                        |  |  |  |  |  |

| P1.3 (AIN3)    | 15 | BU | P1.3: =                                                                      |  |  |  |  |  |

|                |    |    | General purpose 4-state I/O port with internal                               |  |  |  |  |  |

|                |    |    | pull-up mechanism; can be configured as open-drain output.                   |  |  |  |  |  |

|                |    |    | AIN3: =                                                                      |  |  |  |  |  |

|                |    |    | Alternative ADC input                                                        |  |  |  |  |  |

| P1.4 (SS/AIN4) | 16 | BU | P1.4: =                                                                      |  |  |  |  |  |

| F1.4 (33/AIN4) | 10 | ВО | General purpose 4-state I/O port with internal                               |  |  |  |  |  |

|                |    |    | pull-up mechanism; can be configured as                                      |  |  |  |  |  |

|                |    |    | open-drain output.                                                           |  |  |  |  |  |

|                |    |    | <b>SS</b> : =                                                                |  |  |  |  |  |

|                |    |    | Serial mode Selector or Chip-Enabling pin for                                |  |  |  |  |  |

|                |    |    | Serial Peripheral Interface (SPI)                                            |  |  |  |  |  |

|                |    |    | AIN4: =                                                                      |  |  |  |  |  |

|                |    |    | Alternative ADC input                                                        |  |  |  |  |  |

| P1.5           | 17 | BU | P1.5: =                                                                      |  |  |  |  |  |

| (MOSI/AIN5)    |    |    | General purpose 4-state I/O port with internal                               |  |  |  |  |  |

|                |    |    | pull-up mechanism; can be configured as                                      |  |  |  |  |  |

|                |    |    | open-drain output.                                                           |  |  |  |  |  |

|                |    |    | MOSI: =                                                                      |  |  |  |  |  |

|                |    |    | Master data Output or Slave data Input for Serial Peripheral Interface (SPI) |  |  |  |  |  |

|                |    |    | AIN5: =                                                                      |  |  |  |  |  |

|                |    |    | Alternative ADC input                                                        |  |  |  |  |  |

| P1.6           | 18 | BU | P1.6: =                                                                      |  |  |  |  |  |

| (MISO/AIN6)    | 10 | 50 | General purpose 4-state I/O port with internal                               |  |  |  |  |  |

|                |    |    | pull-up mechanism; can be configured as                                      |  |  |  |  |  |

|                |    |    | open-drain output.                                                           |  |  |  |  |  |

|                |    |    | MISO: =                                                                      |  |  |  |  |  |

|                |    |    | Master data Input or Slave data Output for Serial                            |  |  |  |  |  |

|                |    |    | Peripheral Interface (SPI)                                                   |  |  |  |  |  |

|                |    |    | AIN6: =                                                                      |  |  |  |  |  |

|                |    |    | Alternative ADC input                                                        |  |  |  |  |  |

| P1.7<br>(SPICLK/AIN7) | 19 | BU | P1.7: =  General purpose 4-state I/O port with internal pull-up mechanism; can be configured as open-drain output.  SPICLK: =  Serial Clock for Serial Peripheral Interface (SPI)  AIN7: =  Alternative ADC input |

|-----------------------|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC                   | 20 | Р  | Power supply                                                                                                                                                                                                      |

# **Pin Configuration**

# **Block Diagram**

# **Special Function Register**

# Address Map

|           |      | 9     | Α        | В        | С       | D      | E      | F        |

|-----------|------|-------|----------|----------|---------|--------|--------|----------|

| F8        |      | СН    | CCAP0H   | CCAP1H   |         |        |        |          |

| F0        | В    |       | PCAPWM0* | PCAPWM1* |         |        |        |          |

| E8        |      | CL    | CCAP0L   | CCAP1L   |         |        |        |          |

| E0        | ACC  | WDTCR | IFD      | IFADRH   | IFADRL  | IFMT   | SCMD   | ISPCR    |

| D8        | CCON | CMOD  | CCAPM0   | CCAPM1   |         |        |        |          |

| D0        | PSW  |       |          |          |         |        |        |          |

| C8        |      |       |          |          |         |        |        |          |

| C0        |      |       |          |          |         | ADCTL  | ADCV   | PCON2 *  |

| В8        | IP   | SADEN |          |          |         |        |        |          |

| В0        | P3   | P3M0  | P3M1     |          |         |        |        | IPH      |

| <b>A8</b> | ΙE   | SADDR |          |          |         |        |        |          |

| A0        |      |       |          |          |         |        |        | reserved |

| 98        | SCON | SBUF  |          |          |         |        |        |          |

| 90        | P1   | P1M0  | P1M1     |          |         |        |        |          |

| 88        | TCON | TMOD  | TL0      | TL1      | TH0     | TH1    | AUXR   |          |

| 80        |      | SP    | DPL      | DPH      | SPISTAT | SPICTL | SPIDAT | PCON     |

<sup>\*</sup> Write Only

# **Bits Description**

| SYMBOL  | DESCRIPTION                       |        |           |           |       |      |        |      |       | INITIAL<br>VALUE |

|---------|-----------------------------------|--------|-----------|-----------|-------|------|--------|------|-------|------------------|

| SP      | Stack Pointer                     |        |           |           |       |      |        |      |       | 00000111B        |

| )PL     | Data Pointer Low                  |        |           |           |       |      |        |      |       | 00000000B        |

| PH      | Data Pointer High                 |        |           |           |       |      |        |      |       | 00000000B        |

| SPISTAT | SPI status register               | SPIF   | WCOL      |           |       |      |        |      |       | 00xxxxxxB        |

| SPICTL  | SPI control register              | SSIG   | SPEN      | DORD      | MSTR  | CPOL | СРНА   | SPR1 | SPR0  | 00000000B        |

| SPIDAT  | SPI data register                 |        | •         | •         |       |      | +      |      | •     | 00000000B        |

| PCON    | Power Control                     | SMOD   | reserved0 | LVF       | POF   | GF1  | GF0    | PD   | IDL   | 00110000B        |

| CON     | Timer/Counter Control             | TF1    | TR1       | TF0       | TR0   | IE1  | IT1    | IE0  | IT0   | 00000000B        |

| MOD     | Timer/Counter Mode.               | GATE   | C//T      | M1        | MO    | GATE | C//T   | M1   | MO    | 00000000B        |

| TL0     | Timer Low 0                       |        | •         | •         | •     |      | •      |      | •     | 00000000B        |

| L1      | Timer Low 1                       |        |           |           |       |      |        |      |       | 00000000B        |

| H0      | Timer High 0                      |        |           |           |       |      |        |      |       | 00000000B        |

| ГН1     | Timer High 1                      |        |           |           |       |      |        |      |       | 00000000B        |

| AUXR    | Auxiliary                         | T0X12  | T1X12     | URM0X6    | EADCI | ESPI | ENLVFI |      |       | 000000xxB        |

| 21      | Port 1                            |        |           |           |       |      |        |      |       | 11111111B        |

| P1M0    | Port1 configure register 0        |        |           | •         | _     |      | •      |      | •     | 00000000B        |

| P1M1    | Port1 configure register 1        |        |           |           |       |      |        |      |       | 00000000B        |

| SCON    | Serial Control                    | SM0/FE | SM1       | SM2       | REN   | TB8  | RB8    | TI   | RI    | 00000000B        |

| BUF     | Serial Buffer                     |        | •         |           | -     |      | •      |      | •     | xxxxxxxxB        |

| E       | Interrupt Enable                  | EA     | EPCA_LVD  | ESPI_ADC  | ES    | ET1  | EX1    | ET0  | EX0   | 00000000B        |

| SADDR   | Slave Address                     |        | •         | •         |       |      | •      |      | •     | 00000000B        |

| 23      | Port 3                            | P3.7   | -         | P3.5      | P3.4  | P3.3 | P3.2   | P3.1 | P3.0  | 11111111B        |

| P3M0    | Port3 configure register 0        |        | •         |           | -     |      | •      |      |       | 00000000B        |

| P3M1    | Port3 configure register 1        |        | •         |           |       | •    | •      |      |       | 00000000B        |

| PH      | Interrupt Priority High           | -      | PPCAH_LVD | PSPIH_ADC | PSH   | PT1H | PX1H   | PT0H | PX0H  | x0000000B        |

| P       | Interrupt Priority Low            | -      | PPCA      | PSPI      | PS    | PT1  | PX1    | PT0  | PX0   | x0000000B        |

| SADEN   | Slave Address Mask                |        |           |           |       |      |        |      |       | 00000000B        |

| ADCTL   | ADC Control Register              | ADCON  | SPEED1    | SPEED0    | ADCI  | ADCS | CHS2   | CHS1 | CHS0  | 00000000B        |

| ADCV    | ADC Result Register               |        | •         |           | -     |      | •      |      | •     | 00000000B        |

| PCON2   | Power Control register 2          |        |           |           |       |      | CKS2   | CKS1 | CKS0  | xxxxx000B        |

| PSW     | Program Status Word               | CY     | AC        | F0        | RS1   | RS0  | OV     | -    | Р     | 00000000B        |

| CCON    | PCA counter control register      | CF     | CR        | -         | -     | -    | -      | CCF1 | CCF0  | 00xxxx00B        |

| CMOD    | PCA counter mode register         | CIDL   | -         | -         | -     | -    | CPS1   | CPS0 | ECF   | 0xxxx000B        |

| CCAPM0  | PCA module-0 mode                 | -      | ECOM0     | CAPP0     | CAPN0 | MAT0 | TOG0   | PWM0 | ECCF0 | x0000000B        |

| CCAPM1  | register. PCA module-1 mode       | -      | ECOM1     | CAPP1     | CAPN1 | MAT1 | TOG1   | PWM1 | ECCF1 | x0000000B        |

| VDTCR   | register. Watch-dog-timer Control | WRF    | -         | ENW       | CLW   | WIDL | PS2    | PS1  | PS0   | 0x000000B        |

| FD      | ISP Flash data register           |        |           |           |       |      |        |      |       | 11111111B        |

| FADRH   | ISP Flash Address High            |        |           |           |       |      |        |      |       | 00000000B        |

|         | Byte                                                 |       |    |       |       |   |   |       |       |           |

|---------|------------------------------------------------------|-------|----|-------|-------|---|---|-------|-------|-----------|

| IFADRL  | ISP Flash Address Low<br>Byte                        |       |    |       |       |   |   |       |       | 00000000B |

| IFMT    | ISP Mode Table                                       | -     | -  | -     | -     | - | - | MS1   | MS0   | xxxxxx00B |

| SCMD    | ISP Serial Command                                   |       |    |       |       |   |   |       |       | xxxxxxxxB |

| ISPCR   | ISP Control Register                                 | ISPEN | BS | SWRST | CFAIL | - |   | WAIT  |       | 00001000B |

| CL      | PCA Counter Low Byte                                 |       |    | •     |       |   |   |       |       | 00000000B |

| CCAP0L  | Low byte of PCA module0<br>Compare/Capture register  |       |    |       |       |   |   |       |       | 00000000B |

| CCAP1L  | Low byte of PCA module1<br>Compare/Capture register  |       |    |       |       |   |   |       |       | 00000000B |

| В       | B Register                                           |       |    |       |       |   |   |       |       | 00000000B |

| PCAPWM0 | PCA PWM mode auxiliary register 0                    |       |    |       |       |   |   | EPC0H | EPC0L | xxxxxx00B |

| PCAPWM1 | PCA PWM mode auxiliary register 1                    |       |    |       |       |   |   | EPC1H | EPC1L | xxxxxx00B |

| СН      | PCA Counter High Byte                                |       |    |       |       |   |   |       |       | 00000000B |

| CCAP0H  | High byte of PCA module0<br>Compare/Capture register |       |    |       |       |   |   |       |       | 00000000B |

| CCAP1H  | High byte of PCA module1<br>Compare/Capture register |       |    |       |       |   |   |       |       | 00000000B |

| ACC     | Accumulator                                          |       |    |       |       |   |   |       |       | 00000000B |

## **Memory**

# Organization

Address Space for MPC82x52A RAM

Address Space for MPC82x52A embedded Flash memory

## **RAM**

There are 256 bytes RAM built in MPC82x52A.

The user can visit the leading 128-byte RAM via direct addressing instructions, and we name those RAM as *direct RAM* that occupies address space 00h to 7Fh.

Followed 128-byte RAM can be visited via indirect addressing instructions, and we name those RAM as *indirect RAM* that occupied address space 80h to *FF*h.

Since the MPC82x52A has 256 bytes RAM only, any instruction to access RAM addressing over  $FF_H$  is inhibited. Furthermore, since the MPC82x52A is lack of PORT0 and PORT2 to address chip-external memory, all  $\underline{MOVX}$  instructions are inhibited.

## Nonvolatile Registers:

There are four Nonvolatile Registers named **OR0**, **OR1**, **OR2**, and **OR3** individually. They are designed to configure the MPC82x52A, i.e., to decide to use internal RC oscillator or use crystal oscillator as oscillating source, or to allocate the built-in flash for application program, application data and In-System-Program code.

Generally, the only way to program those four nonvolatile registers is making use of a popular NVM writer, such as: Hi-Lo System All-11, Leaper-48 and Megawin-Provided MCU writer. The user's program and the ISP program never can change those option registers.

#### NVM register: OR0 (Option Register 0):

| Bit-7 | Bit-6 | Bit-5  | Bit-4  | Bit-3 | Bit-2     | Bit-1 | Bit-0 |

|-------|-------|--------|--------|-------|-----------|-------|-------|

| LVFWP | ENLVR | ISPAS1 | ISPAS0 | HWBS  | reserved1 | SB    | LOCK  |

LVFWP: = Low-Voltage-Flag-Write-Protecting bit.

**0**: =

inhibit the flash read/write action via ISP/IAP mechanism while the power supply drops under a specific voltage level. Typically, the Low-Voltage is identified to 3.7V/2.3V (Operate in the 5V / 3V) associated with 12 MHz oscillator.

1: = (default)

No inhibition on the flash-writing action.

**ENLVR:** = Enable-Low-Voltage-Reset

0: =

Clearing the bit will reset the device while the power supply drops under a specific voltage level. Typically, the Low-Voltage is identified to 3.7V/2.3V (Operate in the 5V / 3V) associated with 12 MHz oscillator.

1: = (default)

Setting the bit implies never reset the device in spite of voltage dropping.

{ISPAS1, ISPAS0}: = ISP-Address-Start

*{0,0}:* =

Set the ISP start address 1400<sub>H</sub>. (ISP code could take 3K bytes)

$\{0,1\}:=$

Set the ISP start address 1800<sub>H</sub>. (ISP code could take 2K bytes)

*{1,0}:* =

Set the ISP start address 1C00<sub>H</sub>. (ISP code could take 1K bytes)

$\{1,1\}$ : = (default)

Express no ISP code.

HWBS: = HardWare-Boot-Selector

0: = (default)

Clearing the bit is to configure the device to boot from ISP program after power-up.

1:=

Setting the bit is to configure the device to boot normally from user's application program after power-up.

In fact, the boot entrance is determined by register SWBS from SFR ISPCR ignoring the boot comes from RST-pin press, software-trigger, or power-up. However, if a boot happens and that boot comes from power-up action, the device will first load the complement of the HWBS to SWBS, and decides the boot entrance according to the state of bit SWBS. So the HWBS is named HardWare Boot Selector. It influence on power-up boot, but not on the boot from RST-pin or software-trigger.

reserved1:= The bit is reserved for afterward user, and should be left at set.

The user must not clear the bit; otherwise, there could be inadvertent effect impacted on the device.

SB: = Used to decide if the program code will be Scrambled while it is dumped.

0:=

Code dump from Writer is scrambled.

1: = (default)

Code dump from Writer is transparent.

LOCK: = Used to decide if the program code will be Locked against the popular writer.

0:=

Code dumping from Writer is locked.

1: = (default)

Permit code dumping from general Writers.

#### NVM register: OR1 (Option Register 1):

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       |       |       |       |       | -     |

### OR1 [7:1]: = Used to set the boundary of IAP memory

The user's application program can change only the IAP flash memory, neither of AP flash memory itself, nor the ISP flash memory. The IAP memory is defined between address scope

$\textbf{OR1} \ [7:1]^* \\ \textbf{512} \ \text{and} \ ISP-Address-Start. \quad \text{Setting the OR1} \ [7:1] \ \textbf{11111111}_{B} \ \text{means no IAP memory.}$

### NVM register: OR2 (Option Register 2):

| Bit-7     | Bit-6 | Bit-5 | Bit-4     | Bit-3 | Bit-2     | Bit-1  | Bit-0     |

|-----------|-------|-------|-----------|-------|-----------|--------|-----------|

| reserved1 | OSCDN | -     | reserved1 | -     | reserved1 | ENROSC | reserved1 |

reserved1:= The bit is reserved for afterward user, and should be left at set.

The user must not clear the bi; otherwise, there could be inadvertent effect impacted on the device.

**OSCDN:** = Used to adjust the behavior of crystal oscillator.

0: =

The current gain of crystal oscillator amplifier is reduced. It will bring help to EMI reducing and improve the power consumption. Dealing with application does not need high frequency clock (under 12 MHz). It is recommended to do so.

1: = (default)

The current gain of crystal oscillator is enough for oscillator to start oscillating up to 24 MHz.

ENROSC: = Used to determined if to enable the built-in RC oscillator.

0. =

Clearing the bit will enable the built-in RC oscillator, and set that oscillator as the oscillating source

1: = (default)

Setting the bit means to disable the built-in RC oscillator.

#### NVM register: OR3 (Option Register 3):

| Bit-7     | Bit-6     | Bit-5 | Bit-4 | Bit-3  | Bit-2 | Bit-1 | Bit-0 |

|-----------|-----------|-------|-------|--------|-------|-------|-------|

| reserved1 | reserved1 | HWENW |       | HWWIDL | HWPS2 | HWPS1 | HWPS0 |

reserved1:= The bit is reserved for afterward user, and should be left at set.

The user must not clear the bit; otherwise, there could be inadvertent effect impacted on the device.

### HWENW: = Hardware Enable Watch-dog-timer

0: =

Clearing the bit will automatically enable the watch-dog-timer after power-up immediately. **HWWIDL**, **HWPS2**, **HWPS1** and **HWPS0** will be loaded Into SFR WDTCR after power-up if and only if **HWENW =0**.

1: = (default)

No Hardware Enable for Watch-dog-timer.

HWWIDL: = Hardware enables reset from Watch-dog-timer in spite of the MCU lies idle.

O: =

Watch-dog-timer is also suspended while the MCU lies idle.

1: = (default)

Enable watch-dog-timer to keep working in spite of the MCU has been put into idle mode.

If the bit HWENW is left 1, the bits HWWIDL, HWPS2, HWPS1 and HWPS0 make no sense.

### {HWPS2, HWPS1, HWPS0}: = Hardware Watch-dog-timer Pre-Scalar

If the bit **HWENW** is cleared to 0, those bits will be loaded into SFR **WDTCR** after power-up.

Those three bits set the pre-scalar of the watch-dog-timer.

If the bit **HWENW** is left 1, those three bits makes no sense.

*{0,0,0}:* =

The frequency of the clock source for the watch-dog-timer is divided by 2.

$\{0,0,1\}:=$

The frequency of the clock source for the watch-dog-timer is divided by 4.

*{0,1,0}:* =

The frequency of the clock source for the watch-dog-timer is divided by 8.

{0,1,1}: =

The frequency of the clock source for the watch-dog-timer is divided by 16

{1.0.03· =

The frequency of the clock source for the watch-dog-timer is divided by 32 {1,0,1}: =

The frequency of the clock source for the watch-dog-timer is divided by 64 {1,1,0}: =

The frequency of the clock source for the watch-dog-timer is divided by 128 {1,1,1}: =

The frequency of the clock source for the watch-dog-timer is divided by 256

## **Embedded Flash**

There is totally 8 Kbyte flash embedded in the MPC82x52A.

The user can configure the whole flash to store his application program, can configure the flash for both storage of application (AP) program and In-System-Program (ISP) code, or even can configure the flash for storage of AP, ISP, and In-Application-Program (IAP) memory. While the program counter of MPC82x52A is spanning over 1FFF<sub>H</sub>, the device will do nothing. The user can develop the ISP program, and put it into the embedded flash that addressed from 1400<sub>H</sub>, 1800<sub>H</sub>, or 1C00<sub>H</sub>, meanwhile configure **OR0** [5:4], and set **OR0** [3] to 0, and direct the device to boot from the ISP code.

If there is requirement from the user's application program to store nonvolatile parameters, the user can allocate part of the embedded flash as IAP memory by configure **OR1** [7:1].

## **Functional Description**

# **I/O Port Configuration**

All 15 port pins on MPC82x52A may be independently configured to one of four modes: quasi-bidirectional (standard 8051 port output), push-pull output, open-drain output or input-only. All port pins default to quasi-bidirectional after reset. Each port pin has a Schmitt-triggered input for improved input noise rejection. During power-down, all the schmitt-triggered inputs are disabled with the exception of P3.2 and P3.3, which may be used to wake-up the device. Therefore P3.2 and P3.3 should not be left floating during power-down.

There are several special function registers designed to configure those I/O ports.

## SFR: P1M0(P0 Configuration 0)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P1M07 | P1M06 | P1M05 | P1M04 | P1M03 | P1M02 | P1M01 | P1M00 |

## SFR: P1M1(P0 Configuration 1)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P1M17 | P1M16 | P1M15 | P1M14 | P1M13 | P1M12 | P1M11 | P1M10 |

## SFR: P3M0(P3 Configuration 0)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P3M07 | P3M06 | P3M05 | P3M04 | P3M03 | P3M02 | P3M01 | P3M00 |

## SFR: P3M1(P3 Configuration 1)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| P3M17 | P3M16 | P3M15 | P3M14 | P3M13 | P3M12 | P3M11 | P3M10 |

## Configuration of I/O port

| PxM0n | P <i>x</i> M1 <i>n</i> | Port Mode                    |

|-------|------------------------|------------------------------|

| 0     | 0                      | Quasi-bidirectional(default) |

| 0     | 1                      | Push-Pull output             |

| 1     | 0                      | Input Only (High-impedance)  |

| 1     | 1                      | Open-Drain Output            |

$(x = 1 \text{ or } 3 \qquad n = 7, 6, 5, 4, 3, 2, 1 \text{ or } 0)$

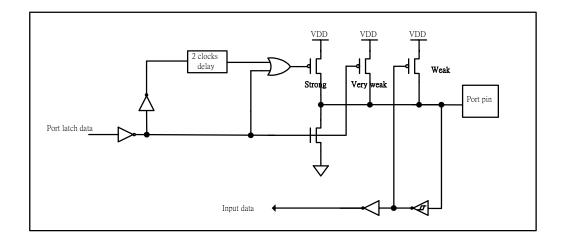

### **Quasi-bidirectional Mode**

Port pins in quasi-bidirectional output mode function similar to the standard 8051 port pins. A quasi-bidirectional port can be used as an input and output without the need to reconfigure the port. This is possible because when the port outputs logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin outputs low, it is driven strongly and able to sink a large current. There are three pull-up transistors in the quasi-bidirectional output that serve different purposes.

One of these pull-ups, called the "very weak" pull-up, is turned on whenever the port register for the pin contains a logic "1". This very weak pull-up sources a very small current that will pull the pin high if it is left floating.

A second pull-up, called the "weak" pull-up, is turned on when the port register for the pin contains a logic "1" and the pin itself is also at a logic "1" level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a '1'. If this pin is pulled low by the external device, this weak pull-up turns off, and only the very weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to over-power the weak pull-up and pull the port pin below its input threshold voltage.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port register changes from a logic "0" to a logic "1". When this occurs, the strong pull-up turns on for two CPU clocks, quickly pulling the port pin high.

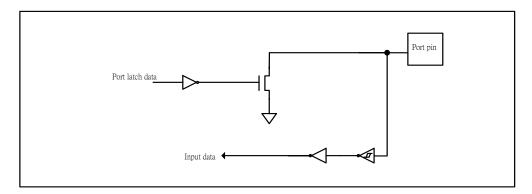

## **Open-drain Output**

The open-drain output configuration turns off all pull-ups and only drives the pull-down transistor of the port pin when the port register contains logic "0". To use this configuration in application, a port pin must have an external pull-up, typically tied to VDD. The input path of the port pin in this configuration is the same as quasi-bidirection mode.

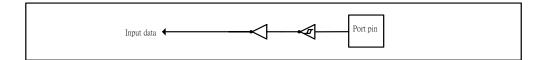

## **Input-only Mode**

The input-only configuration is a Schmitt-triggered input without any pull-up resistors on the pin.

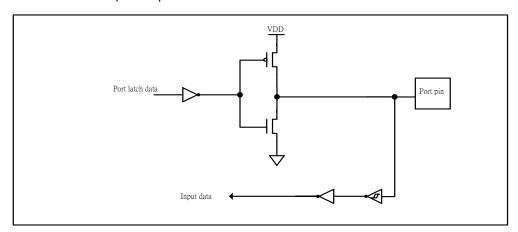

## **Push-pull Output**

The push-pull output configuration has the same pull-down structure as both the open-drain and the quasi-bidirectional output modes, but provides a continuous strong pull-up when the port register contains a logic "1". The push-pull mode may be used when more source current is needed from a port output.

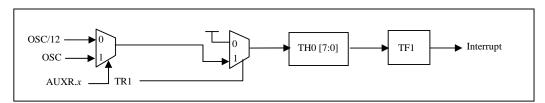

## Timer/Counter

MPC82x52A has two 16-bit timers, and they are named **T0** and **T1**. Each of them can also be used as a general event counter which counts the transition from 1 to 0.

Since the MPC82x52A is a RISC-like MCU which executes faster than traditional 80C51 MCU from other providers. Based on consideration of compatibility with traditional 80C51 MCUs, the frequency of the clock source for **T0** and **T1** is designed to be selectable between oscillator frequency divided-by-12 (default) or oscillator frequency.

The user can configure T0/T1 to work under mode-0, mode-1, mode-2 and mode-3. It is entirely identical to the traditional 80C51 MCU.

There are two SFR designed to configure timers T0 and T1. They are TMOD, and TCON.

The user also should take a glace of SFR **AUXR** which settle on the frequency of the clock source driving the **T0** and **T1**.

SFR: TMOD(Timer Mode Control Register)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GATE  | C//T  | M1    | MO    | GATE  | C//T  | M1    | МО    |

(for timer1 use) (for timer0 use)

**GATE:** = Gating control

0: = (default)

Timer x is enabled whenever "TRx" control bit is set.

1: =

Timer/Counter x is enabled only while "/INTx" pin is high and "TRx" control bit is set.

C//T: = Timer or Counter function selector. 0: =timer, 1: =counter

**0**: = (default)

Configure Tx as Timer use

1: =

Configure Tx as Counter use

{M1, M0}: mode select

*{0, 0}*: =

Configure Tx as 13-bit timer/counter

{0, 1}:=

Configure Tx as 16-bit timer/counter

*{1, 0}*: =

Configure Tx as 8-bit timer/counter with automatic reload capability

*{1, 1}*: =

for T0, set TL0 as 8-bit timer/counter, TH0 is locked into 8-bit timer

for T1, set Timer/Counter1 Stopped

## SFR: TCON

| ı | Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | TF1   | TR1   | TF0   | TR0   | IE1   | IT1   | IE0   | IT0   |

#### **TF1**: = Timer1 overflow flag.

This bit is automatically set by hardware on **T1** overflow, and will be automatically cleared by hardware when the processor vectors to the interrupt routine.

TR1: = Timer1 run control bit.

**0**: = (default)

Stop T1 counting

1:=

Start T1 counting

**TF0**: = Timer0 overflow flag.

This bit is automatically set by hardware on **T0** overflow, and will be automatically cleared by hardware when the processor vectors to the interrupt routine.

TR0: = Timer0 run control bit.

0: = (default)

Stop T0 counting

1: =

Start T0 counting

#### IE1: = External Interrupt-1 flag.

This bit is automatically set by hardware on interrupt from the external interrupt-1, and will be automatically cleared by hardware when the processor vectors to the interrupt routine.

IT1: = Interrupt-1 type control bit.

0: = (default)

Set the interrupt-1 triggered by low duty from pin EX1

1: =

Set the interrupt-1 triggered by negative falling edge from pin EX1

#### IE0: = External Interrupt-0 flag.

This bit is automatically set by hardware on interrupt from the external interrupt-0, and will be automatically cleared by hardware when the processor vectors to the interrupt routine.

IT0: = Interrupt-0 type control bit.

**0**: = (default)

Set the interrupt-0 triggered by low duty from pin EX1

1:=

Set the interrupt-0 triggered by negative falling edge from pin EX1

### SFR: AUXR (Auxiliary Register)

| Bit-7 | Bit-6 | Bit-5  | Bit-4 | Bit-3 | Bit-2  | Bit-1 | Bit-0 |

|-------|-------|--------|-------|-------|--------|-------|-------|

| T0X12 | T1X12 | URM0X6 | EADCI | ESPI  | ENLVFI | -     | -     |

#### T0X12: = T0 clock source selector

0: = (default)

Set the frequency of the clock source for **T0** as the oscillator frequency divided-by-12. It will compatible to the traditional 80C51 MCU.

1: =

Set the frequency of the clock source for **T0** as the oscillator frequency. It will drive the **T0** faster than a traditional 80C51 MCU.

### T1X12: = T1 clock source selector

0: = (default)

Set the frequency of the clock source for **T1** as the oscillator frequency divided-by-12. It will compatible to the traditional 80C51 MCU.

1: =

Set the frequency of the clock source for **T1** as the oscillator frequency. It will drive the **T1** faster than a traditional 80C51 MCU.

URM0X6: = Baud rate selector of UART while it is working under Mode-0

0: = (default)

Set the baud rate of the UART functional block as oscillator frequency divided-by-12. It will compatible to the traditional 80C51 MCU.

1: =

Set the baud rate of the UART functional block as oscillator frequency divided-by-2. It will transmit/receive data faster than a traditional 80C51 MCU.

## **EADCI**: = Enable/Disable interrupt from A/D converter

0: = (default)

Inhibit the ADC functional block to generate interrupt to the MCU

1: =

Enable the ADC functional block to generate interrupt to the MCU

**ESPI**: = Enable/Disable interrupt from Serial Peripheral Interface (SPI)

**0**: = (default)

Inhibit the SPI functional block to generate interrupt to the MCU

1: =

Enable the SPI functional block to generate interrupt to the MCU

**ENLVFI**: = Enable/Disable interrupt from low-voltage sensor

0: = (default)

Inhibit the low-voltage sensor functional block to generate interrupt to the MCU

1: =

Enable the low-voltage sensor functional block to generate interrupt to the MCU

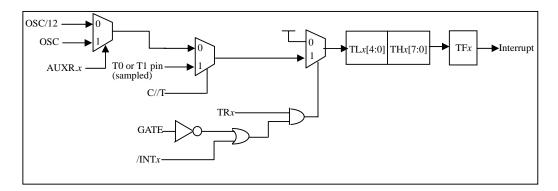

## Mode 0

The timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the timer interrupt flag **TFx**. The counted input is enabled to the timer when **TRx** = 1 and either GATE=0 or INTx = 1. Mode 0 operation is the same for Timer0 and Timer1.

### Mode 1

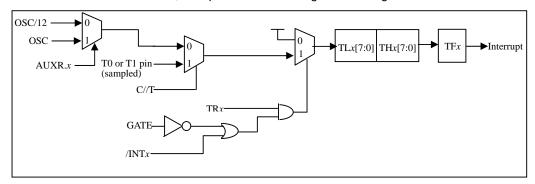

Mode1 is the same as Mode0, except that the timer register is being run with all 16 bits.

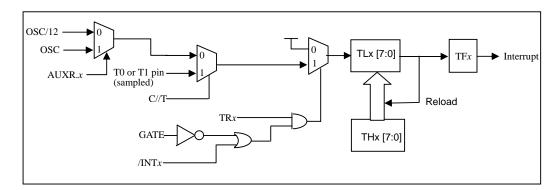

## Mode 2

Mode 2 configures the timer register as an 8-bit counter (TLx) with automatic reload. Overflow from TLx does not only set TFx, but also reloads TLx with the content of THx, which is determined by user's program. The reload leaves THx unchanged. Mode 2 operation is the same for Timer0 and Timer1.

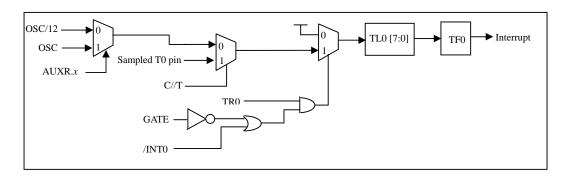

## Mode 3

Timer1 in Mode3 simply holds its count, and the effect is the same as setting TR1 = 1. Timer0 in Mode 3 enables TL0 and TH0 as two separate 8-bit counters. TL0 uses the Timer0 control bits such like C/T, GATE, TR0, INT0 and TF0. TH0 is locked into a timer function (can not be external event counter), and take over the use of TR1, TF1 from Timer1. TH0 now controls the Timer1 interrupt.

28

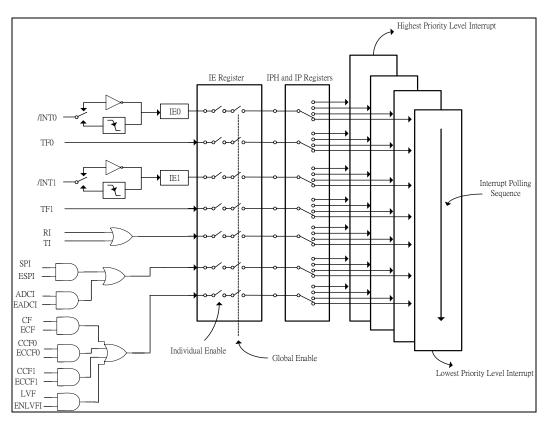

## Interrupt

There are seven interrupt sources available in MPC82x52A. Each interrupt source can be individually enabled or disabled by setting or clearing a bit in the SFR named **IE**. This register also contains a global disable bit (**EA**), which can be cleared to disable all interrupts at once.

Each interrupt source has two corresponding bits to represent its priority. One is located in SFR named **IPH** and the other is in **IP** register. Higher-priority interrupt will be not interrupted by lower-priority interrupt request. If two interrupt requests of different priority levels are received simultaneously, the request of higher priority is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determine which request is serviced. The following table shows the internal polling sequence in the same priority level and the interrupt vector address.

| Source               | Vector address | Priority within level |

|----------------------|----------------|-----------------------|

| External interrupt 0 | 03H            | 1 (highest)           |

| Timer 0              | 0BH            | 2                     |

| External interrupt 1 | 13H            | 3                     |

| Timer1               | 1BH            | 4                     |

| Serial Port          | 23H            | 5                     |

| SPI/ADC              | 2BH            | 6                     |

| PCA/LVF              | 33H            | 7                     |

The external interrupt /INT0, and /INT1 can each be either level-activated or transition-activated, depending on bits **IT0** and **IT1** in register **TCON**. The flags that actually generate these interrupts are bits **IE0** and **IE1** in **TCON**. When an external interrupt is generated, the flag, that generated it, is cleared by the hardware as soon as the service routine is vectored to *only if the interrupt was transition –activated*. Then the external requesting source is what controls the request flag, rather than the on-chip hardware.

The Timer0 and Timer1 interrupts are generated by TF0 and TF1, which are set by a rollover in their respective Timer/Counter registers in most cases. When a timer interrupt is generated, the flag, that generated it, is cleared by the on-chip hardware as soon as the service routine is vectored to.

The serial port interrupt is generated by the logical OR of RI and TI. Neither of these flags is cleared by hardware when the service routine is vectored to. The service routine should poll RI and TI to determine which one to request service, and it will be cleared by software.

The 2B<sub>H</sub> interrupt is shared by the logical OR of SPI interrupt and ADC interrupt. Neither of these flags is cleared by hardware when the service routine is vectored to. The service routine should poll them to determine which one to request service and it will be cleared by software.

The  $33_{\rm H}$  interrupt is shared by the logical OR of PCA interrupt and LVD (Low-Voltage Detector) interrupt. Neither of these flags is cleared by hardware when the service routine is vectored to. The service routine should poll them to determine which one to request service and it will be cleared by software.

All of the bits that generate interrupts can be set or cleared by software with the same result as done through it by hardware. In other words, interrupts or pending interrupts can be generated or canceled in software.

The following content describes several SFR related to interrupt mechanism.

### SFR: IE(Interrupt Enable)

| Bit-7 | Bit-6    | Bit-5    | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|----------|----------|-------|-------|-------|-------|-------|

| EA    | EPCA_LVD | ESPI_ADC | ES    | ET1   | EX1   | ET0   | EX0   |

**EA:** =Global interrupt controller.

0: = (default)

Disable all interrupts

1: =

Release interrupt control to all individual interrupt controllers.

**EPCA\_LVD:** =Interrupt controller of Programmable Counter Array (PCA) and Low-Voltage Detector

**0**: = (default)

Disable

1: =

Enable

**ESPI\_ADC:** =Interrupt controller of Serial Peripheral Interface (SPI) and A/D Converter (ADC).

0: = (default)

Disable

1: =

Enable

**ES:** =Interrupt controller of Universal Asynchronous Receiver/Transmitter (UART).

0: = (default)

Disable

1: =

Enable

ET1: =Interrupt controller of Timer-1 interrupt.

**0**: = (default)

Disable

1: =

Enable

**EX1:** =Interrupt controller of external interrupt-1.

0: = (default)

Disable

1: =

Enable

**ET0:** =Interrupt controller of Timer-0 interrupt.

0: = (default)

Disable

1: =

Enable

EX0: =Interrupt controller of external interrupt-0.

0: = (default)

Disable

1: =

Enable

## SFR: IP(Interrupt Priority Low)

| I | Bit-7 | Bit-6    | Bit-5    | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|---|-------|----------|----------|-------|-------|-------|-------|-------|

|   | -     | PPCA_LVD | PSPI_ADC | PS    | PT1   | PX1   | PT0   | PX0   |

**PPCA\_LVD:** = If set, Set priority for PCA /LVF interrupt higher **PSPI\_ADC:** = If set, Set priority for SPI/ADC interrupt higher

PS := If set, Set priority for serial port interrupt higher (UART)

PT1 := If set, Set priority for timer1 interrupt higher

PX1 := If set, Set priority for external interrupt 1 higher

PT0 := If set, Set priority for timer0 interrupt higher

PX0 := If set, Set priority for external interrupt 0 higher

## SFR: IPH (Interrupt Priority High)

| Bit-7 | Bit-6     | Bit-5     | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-----------|-----------|-------|-------|-------|-------|-------|

| -     | PPCAH_LVD | PSPIH_ADC | PSH   | PT1H  | PX1H  | РТ0Н  | РХ0Н  |

**PPCAH\_LVD**: = If set, Set priority for PCA /LVF interrupt higher **PSPIH\_ADC**: = If set, Set priority for SPI/ADC interrupt higher

PSH := If set, Set priority for serial port interrupt higher (UART)

PT1H := If set, Set priority for timer1 interrupt higher

PT1H := If set, Set priority for timer1 interrupt higher

PX1H := If set, Set priority for external interrupt 1 higher

PT0H := If set, Set priority for timer0 interrupt higher

PX0H := If set, Set priority for external interrupt 0 higher

#### IP and IPH are combined to form 4-level priority interrupt as the following table.

| {IPH.x, IP.x} | Priority<br>Level |  |  |

|---------------|-------------------|--|--|

| 11            | 1 (highest)       |  |  |

| 10            | 2                 |  |  |

| 01            | 3                 |  |  |

| 00            | 4                 |  |  |

Interrupt Control Block

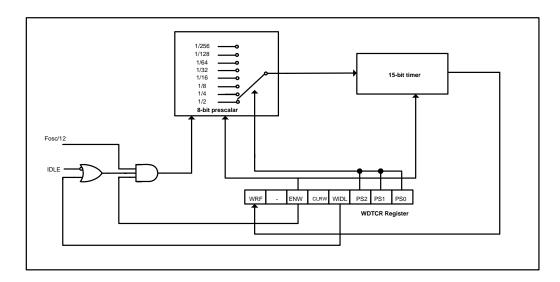

## **Watch Dog Timer**

The watch dog timer in MPC82x52A consists of an 8-bit pre-scalar timer and a 15-bit timer. The timer is one-time enabled by setting ENW. Clearing ENW can not stop WDT counting. When the WDT is enabled, software should always reset the timer by writing 1 to CLRW bit before the WDT overflows. If MPC82x52A is out of control by any disturbance, that means the CPU can not run the software normally then WDT may miss the "writing 1 to CLRW", and overflow will come. WDT overflow reset the CPU to restart. Associated with the WDTCR SFR, a NVM option register bytes named **OR3** are designed to enable WDT, and initiate WDTCR with initial states. See Option Register description to know in more details.

To make good use of the watch-dog-timer, the user should take notice on SFR WDTCR.

SFR: WDTCR (WDT Control Register)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WRF   | -     | ENW   | CLRW  | WIDL  | PS2   | PS1   | PS0   |

WRF: = When WDT overflows, this bit is set. It can be cleared by software.

ENW: = Control bit to enable Watch-Dog-Timer. (One-time enabled, can not be disabled)

**0**: = (default)

Disable Watch Dog Timer

1: =

Enable Watch Dog Timer start counting

**CLRW:** = Set this bit to recount WDT. Hardware will automatically clear this bit.

WIDL: = Behavior controller of the WDT while the device is put under idle

0: = (default)

Stop Watch Dog Timer counting

1: =

Keep Watch Dog Timer counting (so further reset could happen)

{PS2, PS1, PS0}: selector of the WDT pre-scalar output.

{0, 0, 0}: = set the pre-scaling value 2

{0, 0, 1}: = set the pre-scaling value 4

{0, 1, 0}: = set the pre-scaling value 8

{0, 1, 1}: = set the pre-scaling value 16

{1, 0, 0}: = set the pre-scaling value 32

{1, 0, 1}: = set the pre-scaling value 64

{1, 1, 0}: = set the pre-scaling value 128

{1, 1, 1}: = set the pre-scaling value 256

## **Universal Asynchronous Serial Port (UART)**

The serial port of MPC82x52A is duplex. It can transmit and receive simultaneously. The receiving and transmitting of the serial port share the same SFR **SBUF**, but actually there are two SBUF registers implemented in the chip. One is for transmitting and the other is for receiving. The serial port can be operated in 4 different modes.

#### Mode 0

Generally, this mode purely is used to extend the I/O features of this device.

Operating under this mode, the device receives the serial data or transmits the serial data via pin RXD while there is a clock stream shifted via pin TXD which makes convenient for external synchronization. An 8-bit data is serially transmitted/received with LSB first. The baud rate is fixed at 1/12 the oscillator frequency. If **AUXR**.5 (**URM0X6**) is set, the baud rate is 1/2 oscillator frequency.

### Mode1

A 10-bits data is serially transmitted through pin TXD or received through pin RXD. The frame data includes a start bit (0), 8 data bits and a stop bit (1). After finishing a receiving, the device will keep the stop bit in **RB8** which from SRF **SCON**.

Baud Rate (for Mode 1) =

$$\frac{2^{\text{SMOD}}}{32}$$

X (Timer-1 overflow rate)

## Mode2

An 11-bit data is serially transmitted through **TXD** or received through **RXD**. The frame data includes a start bit (0), 8 data bits, a programmable 9th bit and a stop bit (1). On transmit; the 9th data bit comes from **TB8** in SFR **SCON**. On receive; the 9th data bit goes into **RB8** in **SCON**. The baud rate is programmable, and permitted to be set either 1/32 or 1/64 the oscillator frequency.

Baud Rate (for Mode 2) =

$$\frac{2^{\text{SMOD}}}{64}$$

X Fosc

### Mode3

Mode 3 is the same as mode 2 except the baud rate is variable.

Baud Rate (for Mode 3) =

$$\frac{2^{\text{SMOD}}}{32}$$

X (Timer-1 overflow rate)

In all four modes, transmission is initiated by any instruction that uses SBUF as a destination register. Reception is initiated in mode 0 by the condition  $\mathbf{RI} = 0$  and  $\mathbf{REN} = 1$ . Reception is initiated in the other modes by the incoming start bit with 1-to-0 transition if  $\mathbf{REN} = 1$ .

There are several SFRs related to serial port configuration described as following.

## SFR: SCON (Serial Control)

| Bit-7  | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SM0/FE | SM1   | SM2   | REN   | TB8   | RB8   | TI    | RI    |

**FE:** = Frame Error bit

This bit is set by the receiver when an invalid stop bit is detected. The FE bit is not cleared by valid frames but should be cleared by software. The SMOD0 bit must be set to enable access to the FE bit.

**(SM0, SM1)**: = Used to set operating mode of the serial port.

**{0, 0}**: = set the serial port operate under Mode 0

**(0, 1)**: = set the serial port operate under Mode 1

**{1, 0}**: = set the serial port operate under Mode 2

{1, 1}: = set the serial port operate under Mode 3

**SM2:** = Enable the *automatic address recognition* feature in mode 2 and 3.

If **SM2**=1, **RI** will not be set unless the received 9th data bit is 1, indicating an address, and the received byte is a Given or Broadcast address. In mode1, if SM2=1, RI will not be set unless a valid stop Bit was received, and the received byte is a Given or Broadcast address.

**REN:** = Enable the serial port reception.

0: = (default)

Disable the serial port reception.

1: =

Enable the serial port reception.

TB8: = The 9th data bit, which will be transmitted in Mode 2 and Mode 3.

RB8: = In mode 2 and 3, the received 9th data bit will be put into this bit.

TI := Transmitting done flag. After a transmitting has been finished, the hardware will set this bit.

RI := Receive done flag. After reception has been finished, the hardware will set this bit.

SFR: SBUF (Serial Buffer)

| Bit-7 | Bit-6 | Bit-5    | Bit-4        | Bit-3        | Bit-2    | Bit-1 | Bit-0 |

|-------|-------|----------|--------------|--------------|----------|-------|-------|

|       |       | (data to | be transmitt | ed or receiv | ed data) |       |       |

#### Frame Error Detection

When used for frame error detect, the UART looks for missing stop bits in the communication. A missing bit will set the FE bit in the SCON register. The FE bit shares the SCON.7 bit with SM0, and the function of SCON.7 is determined by PCON.6 (SMOD0). If SMOD0 is set then SCON.7 functions as FE. When SMOD0 is cleared, SCON.7 functions as SM0. When used as FE, SCON.7 can only be cleared by software.

## **Automatic Address Recognition**

There is an extra feature makes the device convenient to act as a master, which communicates to multiple slaves simultaneously. It is really *Automatic Address Recognition*.

There are two SFR **SADDR** and **SADEN** implemented in the device. The user can read or write both of them. Finally, the hardware will make use of these two SFR to "generate" a "compared byte". The formula specifies as following.

For example:

Set **SADDR** = 11000000b Set **SADEN** = 11111101b

⇒ The achieved "Compared Byte" will be "110000x0" (x means don't care)

For another example:

Set **SADDR** = 11100000b Set **SADEN** = 11111010b

⇒ The achieved "Compared Byte" will be "11100x0x"

After the generic "Compared Byte" has been worked out, the MPC82x52A will make use of this byte to determine how to set the bit **RI** in SFR **SCON**.

Normally, an UART will set bit **RI** whenever it has done a byte reception; but for the UART in the MPC82x52A, if the bit **SM2** is set, it will set **RI** according to the following formula.

In other words, not all data reception will respond to RI, while specific data does.

By setting the SADDR and the SADEN, the user can filter out those data byte that doesn't like to care. This feature brings great help to reduce software overhead.

The above feature adapts to the serial port when operated in Mode1, Mode2, and Mode3. Dealing with Mode 0, the user can ignore it.

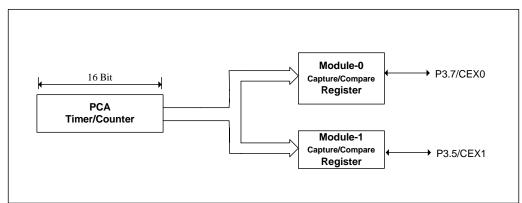

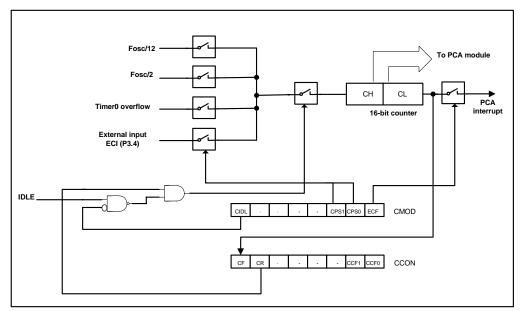

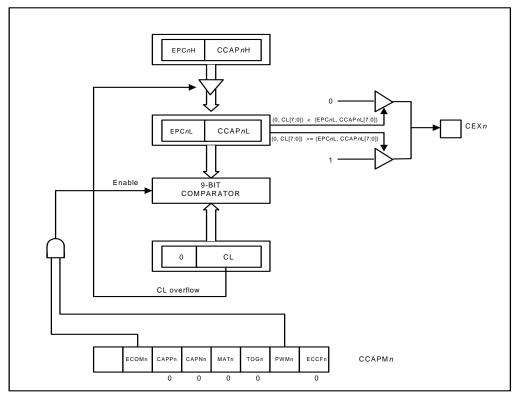

# **Programmable Counter Array (PCA)**

The Programmable Counter Array is a special 16-bit Timer that has two 16-bit capture/compare modules associated with it. Each of the modules can be programmed to operate in one of four modes:

- rising and/or falling edge capture (calculator of duty length for high/low pulse)

- software timer

- high-speed output

- pulse width modulator

Each module has a pin associated with it in port 3. Module-0 is connected to pin P3.7, module-1 to pin P3.5.

The PCA timer is a common time base for all two modules, and can be programmed to run at 1/12 the oscillator frequency, 1/2 the oscillator frequency, the Timer-0 overflow or the input on pin ECI (P3.4). The timer count source is determined from **CPS1** and **CPS0** bits in the SFR **CMOD**.

**Programmable Counter Array**

In the **CMOD** SFR, there are two additional bits associated with the PCA. On of them is **CIDL** which determines if to stop the PCA while the MCU is put under idle. The other bit is **ECF** which controls if to pass the interrupt from PCA into the MCU.

The **CCON** SFR contains the run control bit for PCA and several flags for the PCA timer and each module. To start the PCA counting, the **CR** bit (**CCON**.6) must be set by software; oppositely, clearing bit CR will shut off the PCA. There is a bit named **CF** in SFR **CCON**. The **CF** bit (**CCON**.7) will be set when the PCA timer overflows, and an interrupt will be generated if the **ECF** (**CMOD**.0) is set. The **CF** bit can only be cleared by software. There are two bits

named CCF0 and **CCF1** in SFR **CCON**. The **CCF0** and **CCF1** serve as flags for module-0 and module-1 respectively. They are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

PCA Timer/Counter

## SFR: CMOD (PCA Mode Control Register)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CIDL  |       | -     | -     | -     | CPS1  | CPS0  | ECF   |

CIDL:=Behavior control of the PCA.

0:= (default)

Disable counting of the PCA counter while the MCU is put under idle state.

1 -

Enable counting of the PCA counter while the MCU is put under idle state.

{ CPS1, CPS0 } := Used to select the clocking source for PCA counter

{ 0, 0 } := set the frequency of the PCA counter clock source as oscillator's frequency over

{ 0, 1} := set the frequency of the PCA counter clock source as oscillator's frequency over 2

{ 1, 0} := set the PCA counter clock source as Timer-0 overflow

{ 1, 1} := set the PCA counter clock source as pin ECI(pin P3.4)

ECF:=Control bit of deciding if to pass interrupt from PCA timer overflow to the MCU

0:= (default)

Inhibit the interrupt from PCA timer to the MCU

1:=

Permit the interrupt from PCA timer to the MCU

## SFR: CCON (PCA Counter Control Rregister)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CF    | CR    | -     | -     | -     | -     | CCF1  | CCF0  |

#### CF:=PCA Counter overflow Flag

This bit must be set by hardware itself. It can be cleared by software program.

#### CR:=PCA Run control bit

0 := (default)

Disable counting of the PCA counter

1 -

Start counting of the PCA counter

#### CCF1:=Module-1 interrupt Flag

This bit must be set by hardware itself when a match or capture from module-1 occurs. It can be cleared by software program.

A match means the value of the PCA counter equals the value of the Capture/Compare Register in the module-1.

A capture means a specific edge from CEX1 happens, so the Capture/Compare register latches the value of the PCA counter, and the CCF1 is set.

#### CCF0:=Module-0 interrupt Flag

This bit must be set by hardware itself when a match or capture from module-0 occurs. It can be cleared by software program.

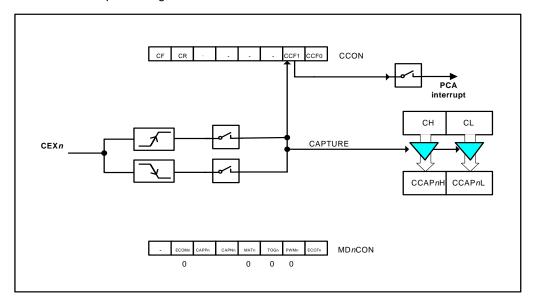

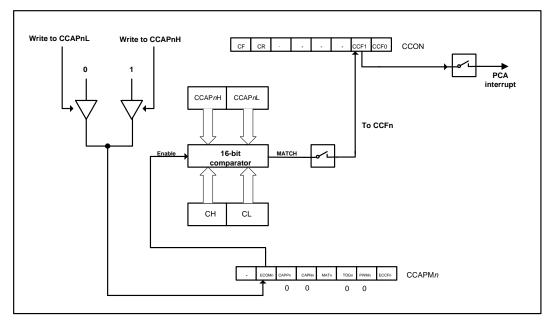

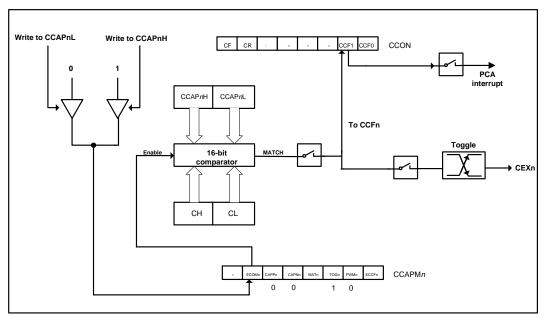

Each module in the PCA has a special function register associated with it: **CCAPM0** for module0 and **CCAPM1** for module-1. The register contains the bits that control the mode in which each module will operate. The **ECCF***n* bit controls if to pass the interrupt from **CCF***n* flag in the **CCON** SFR to the MCU when a match or compare occurs in the associated module. **PWM***n* enables the pulse width modulation mode. The **TOG***n* bit when set causes the pin **CEX***n* output associated with the module to toggle when there is a match between the PCA counter and the module's *Capture/Compare register*. The match bit(**MAT***n*) when set will cause the **CCF***n* bit in the CCON register to be set when there is a match between the PCA counter and the module's *Capture/Compare register*.

The next two bits **CAPN***n* and **CAPP***n* determine the edge type that a capture input will be active on. The **CAPN***n* bit enables the negative edge, and the **CAPP***n* bit enables the positive edge. If both bits are set, both edges will be enabled and a capture will occur for either transition. The bit **ECOM***n* when set enables the comparator function.

## SFR: CL (PCA Counter Low Byte)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       |       |       |       |       | ,     |

#### SFR: CH (PCA Counter High Byte)

## SFR: CCAP0L (Low byte of PCA module-0 Compare/Capture register)

| Bit-7 | Bit-7         Bit-6         Bit-5         Bit-4         Bit-3         Bit-2         Bit-1         Bit-0 |               |              |                |            |        |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------|---------------|--------------|----------------|------------|--------|--|--|--|

|       | Low                                                                                                     | Byte of the C | Compare/ Cap | oture register | in PCA Mod | lule 0 |  |  |  |

## SFR: CCAP0H (High byte of PCA module-0 Compare/Capture register)

| Bit-7 | Bit-7 Bit-6 Bit-5 Bit-4 Bit-3 Bit-2 Bit-1 Bit-0 |               |             |               |              |        |  |  |  |

|-------|-------------------------------------------------|---------------|-------------|---------------|--------------|--------|--|--|--|

|       | High                                            | Byte of the C | Compare/ Ca | pture registe | r in PCA Mod | lule 0 |  |  |  |

## SFR: CCAP1L (Low byte of PCA module-1 Compare/Capture register)

| Bit-7 | Bit-6 | Bit-5         | Bit-4       | Bit-3          | Bit-2        | Bit-1  | Bit-0 |

|-------|-------|---------------|-------------|----------------|--------------|--------|-------|

|       | Low   | Byte of the C | Compare/ Ca | pture register | r in PCA Mod | lule 1 |       |

## SFR: CCAP1H (High byte of PCA module-1 Compare/Capture register)

| Bit-7 | Bit-7 Bit-6 Bit-5 Bit-4 Bit-3 Bit-2 Bit-1 Bit-0 |               |             |               |              |        |  |  |  |

|-------|-------------------------------------------------|---------------|-------------|---------------|--------------|--------|--|--|--|

|       | High                                            | Byte of the C | Compare/ Ca | pture registe | r in PCA Mod | dule 1 |  |  |  |

## SFR: CCAPM0 (PCA Module-0 Mode Register)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | ECOM0 | CAPP0 | CAPN0 | MAT0  | TOG0  | PWM0  | ECCF0 |

## SFR: CCAPM1 (PCA Modul-1 Mode Register)

| Bit-7 | Bit-6 | Bit-5 | Bit-4 | Bit-3 | Bit-2 | Bit-1 | Bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| -     | ECOM1 | CAPP1 | CAPN1 | MAT1  | TOG1  | PWM1  | ECCF1 |

**ECOM**n: = used to determine if Enable Comparator

0:= (default)

Disable the comparator function

1:=

Enable the comparator function

**CAPP***n*: = configure the module-*n*'s register to latch the PCA counter on Positive edge of EXI*n* or not

0:= (default)

configure the module-n's register not to latch the PCA counter on CEXn posedge.

1:=

configure the module-n's register to latch the PCA counter on CEXn posedge.

**CAPN***n*: = configure the module-*n*'s register to latch the PCA counter on Negative edge of EXI*n* or not

0:= (default)

configure the module-n's register not to latch the PCA counter on pin CEXn negedge.

1:=

configure the module-n's register to latch the PCA counter on pin CEXn negedge.

**MAT***n*: = used to determine if set the bit **CCF***n* in SFR **CCON** while a match from module-*n* occurs.

0:= (default)

Don't set the bit  $\mathbf{CCF}n$  while a match occurs between the PCA counter and module-n's register.

1:=

Set the bit **CCF***n* while a match occurs between the PCA counter and module-*n*'s register.

**TOG***n*: = Toggle the output pin

0:= (default)

Don't toggle the pin CEXn while a match occurs between the PCA counter and module-n's register.

1:=

Toggle the pin CEXn while a match occurs between the PCA counter and module-n's register.

**PWM**n: = Enable plus width modulation mode n.

0:= (default)

Inhibit the PWM functionality from module-n output to pin CEXn

1:=

Enable the pin CEXn as the output of the PWM functionality from module-n

**ECCF**n: = Enable the CCFn flag in the **CCON** SFR to generate an interrupt.

0:= (default)

Inhibit the interrupt(CCFn) from module-n to the MCU

1:=

Permit the interrupt(CCFn) from module-n to the MCU

## **Configure PCA Module**

| ECOM <i>n</i> | CAPPn | CAPNn | MAT <i>n</i> | TOGn | PWM <i>n</i> | ECCFn | Module function                              |

|---------------|-------|-------|--------------|------|--------------|-------|----------------------------------------------|

| 0             | 0     | 0     | 0            | 0    | 0            | 0     | No operation                                 |

| Х             | 1     | 0     | 0            | 0    | 0            | Х     | 16-bit capture by a positive-edge trigger on |

|               |       |       |              |      |              |       | CEXn                                         |

| Х             | 0     | 1     | 0            | 0    | 0            | Х     | 16-bit capture by a negative trigger on CEXn |

| Х             | 1     | 1     | 0            | 0    | 0            | Х     | 16-bit capture by a transition on CEXn       |

| 1             | 0     | 0     | 1            | 0    | 0            | Х     | 16-bit Software Timer                        |

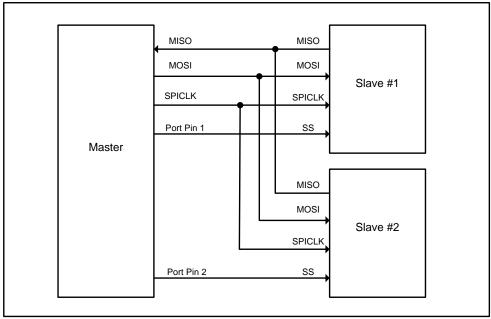

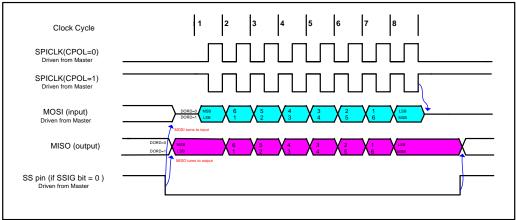

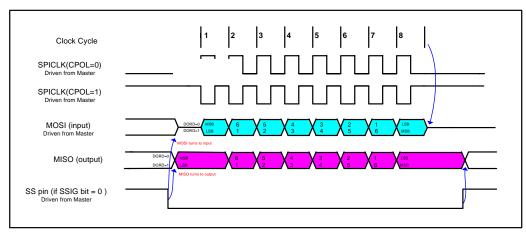

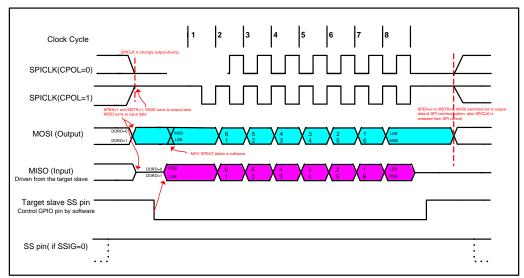

| 1             | 0     | 0     | 1            | 1    | 0            | Х     | 16-bit High Speed Output                     |