# Features

- Full TCG/TCPA V1.1b Compatibility

- Single Chip Turnkey Solution

- Hardware Asymmetric Crypto Engine

- 2048 RSA Sign in 500 ms Using CRT

- AVR 8-bit RISC Microprocessor

- Internal EEPROM Storage for 10+ RSA Keys

- 33 MHz LPC (Low Pin Count) Bus for Easy PC Interface

- 100 KHz System Management Bus (SMBus) Two-wire Interface

- Secure Hardware and Firmware Design and Chip Layout

- True Random Number Generator (RNG)

- Secure Real-time Clock Option

- 3.3V ±10% Supply Voltage

- 28-lead TSSOP Package or 40-lead MLF Package

- 0–70°C Temperature Range

# Description

The AT97SC3201 is a fully integrated security module designed to be integrated into personal computers and other embedded systems. It implements version 1.1b of the Trusted Computing Platform Alliance (TCPA) specification for Trusted Platform Modules (TPM). This specification has been adopted by the Trusted Computing Group (TCG).

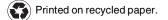

The TPM includes a crypto accelerator capable of computing a 2048-bit RSA signature in 500 ms and a 1024-bit RSA signature in 100 ms, both using CRT. Communication to and from the TPM can occur through one of two interface protocols: either a 33-MHz LPC interface or a 100-KHz SMBus two-wire interface.

# Figure 1. AT97SC3201 Block Diagram

The chip includes a full hardware random number generator that is used for the TCG protocol and is also available to the system for any random numbers it may need during normal operation.

Trusted Platform Module

# AT97SC3201

# Summary

Rev. 2015DS-TPM-7/04

A real-time clock function is available using an external battery and crystal. The chip provides tamper detection if the battery or crystal are removed or tampered with, and the current time value can be signed by the appropriate internal keys to verify its accuracy. (Contact Atmel for current status of this option.)

The battery detector can be used without the crystal for lower cost. In this mode, the TPM can indicate to the system if it has been removed from the PC in any way and can also take actions internally.

The chip uses a dynamic internal memory management scheme to store from 10 to 20 keys. Other than the standard TCG commands (TPM\_Evictkey, TPM\_Loadkey), no system intervention is required to manage this internal key cache.

The TPM is offered to OEM manufacturers as a turnkey solution, including the firmware integrated on the chip. In addition, Atmel provides the necessary driver software for integration into certain operating systems, along with BIOS drivers. A TCG Software Stack (TSS), also supplied by Atmel and available under license, provides communication support to any application using MSCAPI or PKCS #11 Cryptographic APIs. (Contact Atmel for a complete list of operating systems supported.)

Full documentation for TCG primitives can be found on the TCG Web site, <u>www.trustedcomputinggroup.org</u>. This specification includes only mechanical and electrical information.

# **Absolute Maximum Ratings**

| Operating Temperature0°C to +70°C               |

|-------------------------------------------------|

| Storage Temperature (without Bias)0°C to + 70°C |

| Voltage on I/O Pins0.1 to $V_{CC}$ +0.3V        |

| Voltage on VCC with Respect to Ground6.0V       |

| Maximum ESD Voltage2000V                        |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification may cause temporary or permanent failure. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Table 1. DC Parameters\*

| Symbol            | Parameter                          | Min                   | Nom                    | Мах                   | Units | Notes                                            |

|-------------------|------------------------------------|-----------------------|------------------------|-----------------------|-------|--------------------------------------------------|

| V <sub>CC</sub>   | Supply Voltage                     | 3.0                   | 3.3                    | 3.6                   | V     |                                                  |

| I <sub>CC</sub>   | Operating Current at fclk = 33 MHz |                       | 25                     | 50                    | mA    |                                                  |

| I <sub>ST</sub>   | Static Current                     |                       | 5                      | 10                    | mA    | $V_{CC} = 3.6V$ ; fxtal = 0 Hz,<br>active inputs |

| I <sub>SL</sub>   | Sleep Current, Chip Idle           |                       | 40                     | 100                   | μA    | $V_{CC} = 3.6V$ ; fxtal = 0 Hz                   |

| I <sub>BB</sub>   | Battery Current                    |                       | 2                      | 4                     | μA    | $V_{CC} = 0V$ ; fxtal = 0 Hz.                    |

| I <sub>LIO</sub>  | Input Leakage                      |                       | 0.1                    | 3                     | μA    | Vin = V <sub>CC</sub> or GND                     |

| V <sub>IH</sub>   | Input High Threshold               | 0.5 * V <sub>CC</sub> |                        | V <sub>CC</sub> + 0.5 | V     |                                                  |

| V <sub>IL</sub>   | Input Low Threshold                | -0.5                  |                        | 0.3 * V <sub>CC</sub> | V     |                                                  |

| V <sub>OH</sub>   | Output High Voltage                | 0.9 * V <sub>CC</sub> | 0.98 * V <sub>CC</sub> |                       | V     | At I <sub>OUT</sub> = -500 uA                    |

| V <sub>OL</sub>   | Output Low Voltage                 |                       |                        | 0.1 * V <sub>CC</sub> | V     | At I <sub>OUT</sub> = 1.5mA                      |

| I <sub>OLCR</sub> | Output Low Current, CLKRUN#        | 7                     |                        |                       | mA    | At V <sub>OUT</sub> = .615 * V <sub>CC</sub>     |

| CI                | Input Pin Capacitance              |                       | 6                      |                       | pF    | Note 1                                           |

\*  $V_{CC}$  = 3.0 to 3.6V; Temperature = 0 to 70°C

Note: These parameters guaranteed but not tested.

### Table 2. AC Parameters\*

| Symbol               | Parameter                            | Min  | Nom  | Max | Units | Notes                                                                                                                                                      |

|----------------------|--------------------------------------|------|------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>VAL</sub>     | CLK to Signal Valid Delay – LAD0-3   | 2    | 5    | 11  | ns    | Measured at Vtrise = 0.285 * V <sub>CC</sub> and Vtfal = 0.615 * V <sub>CC</sub> . Measured from clk at Vtest = 0.4 * V <sub>CC</sub> ; Load = $200\Omega$ |

| T <sub>ON</sub>      | Float to Active Delay                | 2    | 4    |     | ns    |                                                                                                                                                            |

| T <sub>OFF</sub>     | Active to Float Delay                |      |      | 28  | ns    |                                                                                                                                                            |

| Τ <sub>SU</sub>      | Input Setup Time to CLK              | 7    | 2    |     | ns    |                                                                                                                                                            |

| Т <sub>н</sub>       | Input Hold Time from CLK             | 0    | -500 |     | ns    |                                                                                                                                                            |

| T <sub>RST</sub>     | Reset Active Time after Power Stable | 1    |      |     | ms    | Note 2                                                                                                                                                     |

| T <sub>RST-CLK</sub> | Reset Active after CLK Stable        | 100  |      |     | m     | Note 2                                                                                                                                                     |

| T <sub>RST-OFF</sub> | Reset Active to Output Float Delay   |      |      | 40  | ns    | Note 2                                                                                                                                                     |

| T <sub>CLKIN</sub>   | CLK Period                           | 29.5 | 30   | 31  | ns    | Note 3                                                                                                                                                     |

| T <sub>CLKLO</sub>   | CLK Low Duration                     | 13.4 |      | 18  | ns    | Note 1, Note 3                                                                                                                                             |

| Т <sub>СLKHI</sub>   | CLK High Duration                    | 13.4 |      | 18  | ns    | Note 1, Note 3                                                                                                                                             |

\* CI = 10pf.  $V_{CC}$  = 3.0 to 3.7V; Temperature = 0 to 70°C

Note: 1. All parameters measured with respect to signal crossing Vtest =  $0.4 * V_{CC}$  unless otherwise noted.

2. These parameters guaranteed but not tested.

3. The minimum parameter must never be violated under any circumstances unless Ireset# is asserted. If proper CLKRUN# signaling is observed, the maximum specification can be violated.

### Table 3. Ordering Information

| Ordering Code   | Package |           | Operation Range          |

|-----------------|---------|-----------|--------------------------|

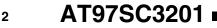

| AT97SC3201-01AC | 28A3    |           | Commercial (0° to 70° C) |

| AT97SC3201-X1AC | 28A3    | lead-free | Commercial (0° to 70° C) |

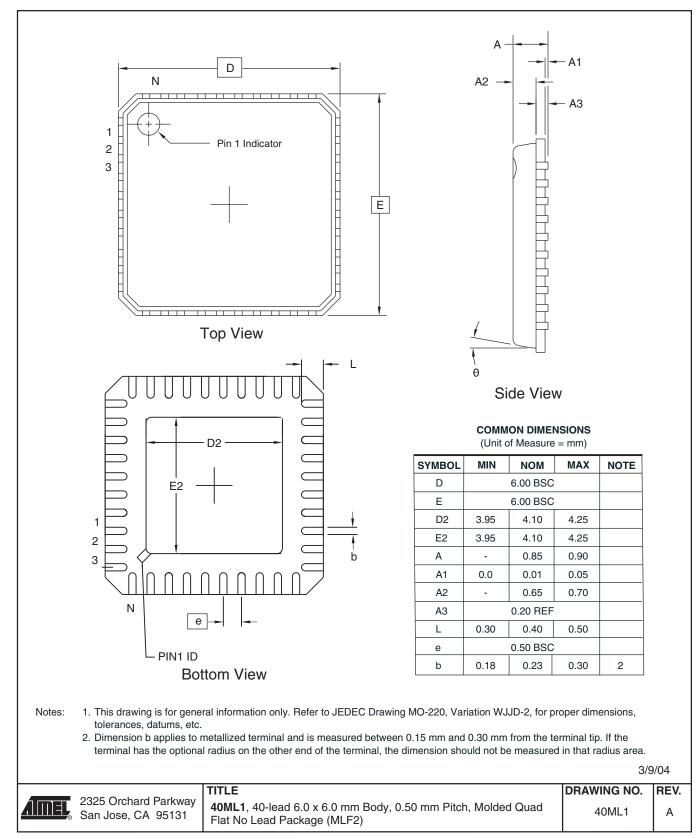

| AT97SC3201-01MC | 40ML1   |           | Commercial (0° to 70° C) |

| AT97SC3201-X1MC | 40ML1   | lead-free | Commercial (0° to 70° C) |

4

# AT97SC3201

# **Package Drawing**

## 28A3 – TSSOP

Downloaded from Elcodis.com electronic components distributor

6

AT97SC3201

# **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

## Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

# **Atmel Operations**

Memory 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2004.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL<sup>®</sup> is the registered trademark of Atmel Corporation.

Other terms and product names may be the trademark of others.