S G S-THOMSON

MK62486

# VERY FAST CMOS 32K x 9 CACHE BRAM

#### **ADVANCE DATA**

- 32K x 9 CMOS SYNCHRONOUS BURSTSRAM

- FAST CYCLE TIMES: 25, 30ns

- FAST ACCESS: 19, 24ns Max

- ON-BOARD BURST COUNTER

- INPUT REGISTERS (ADDR.,DATA,CTRL)

- SELF-TIMED WRITE CYCLE

- THREE STATE COMMON I/O

- HIGH OUTPUT DRIVE CAPABILITY

- ASYNCHRONOUS OUTPUT ENABLE (G)

- BURST CONTROL INPUTS: ADSP, ADSC, ADV

- DUAL CHIP SELECTS FOR EASY DEPTH EXPANSION

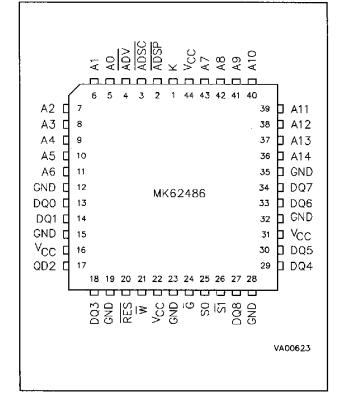

Figure 1. Pin Connection

### **PIN NAMES**

| A0 - A14              | Address Inputs             |

|-----------------------|----------------------------|

| DQ0 - DQ8             | Data Inputs/Outputs        |

| К                     | Clock                      |

| W                     | Write Enable               |

| G                     | Output Enable              |

| S0                    | Chip Select, Active High   |

| <u>\$1</u>            | Chip Select, Active Low    |

| ADSP                  | Address Status Processor   |

| ADSC                  | Address Status Cache Ctrl. |

| ADV                   | Burst Address Advance      |

| RES                   | Reserve, Tied Low          |

| V <sub>CC</sub> , GND | 5 Volts, Ground            |

February 1992

1/12

S G S-THOMSON

T-46-23-13

#### DESCRIPTION

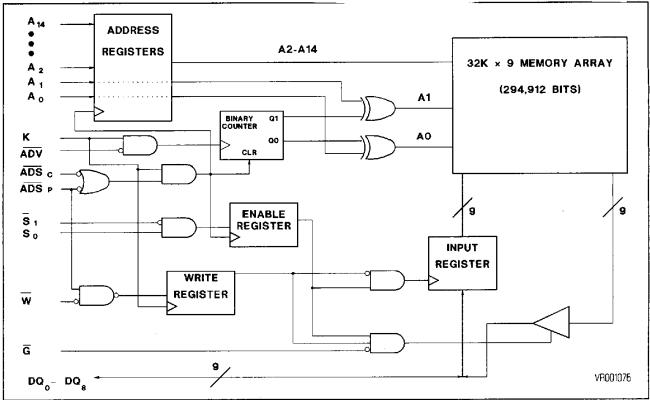

The MK62486 BRAM™ is a 288K (294,912-bit) CMOS Burst SRAM, organized as 32,768 words x 9 bits. It is fabricated using SGS-Thomson's low power, high performance, CMOS technology. The device integrates a 2-bit burst counter, input registers, high output drive capability, and high speed synchronous SRAM onto a single chip. The syn-chronous design provides precise control using an external clock (K) input. The MK62486 is specifically adapted to provide a burstable, high performance secondary cache for the i486™ microprocessor.

The MK62486 is available in a 44 pin plastic leaded chip-carrier (PLCC). The device provides multiple power and ground pins to reduce effects induced by output noise for high performance applications. Separate power and ground pins (V<sub>CCQ</sub> and GND<sub>Q</sub>) have been employed for DQ0-8 to allow output levels referenced to 5 Volts or 3.3 Volts. The main Burst SRAM power requires a single 5V ± 5% supply, and all inputs and outputs are TTL compatible.

#### **DEVICE OPERATIONS**

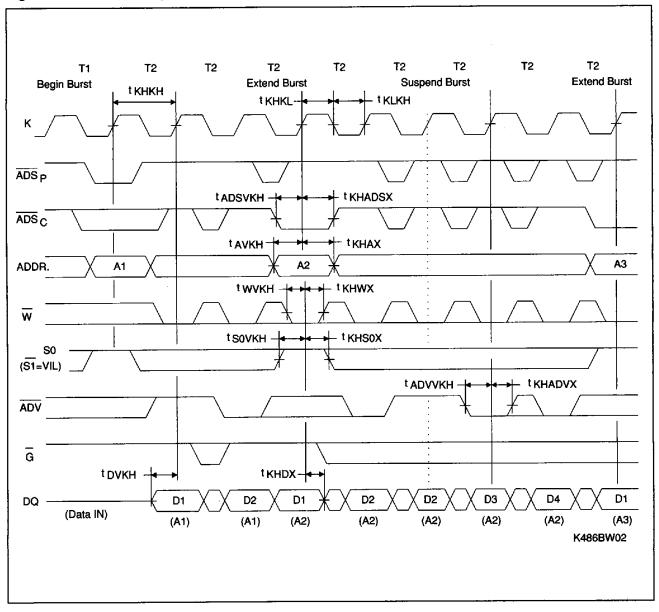

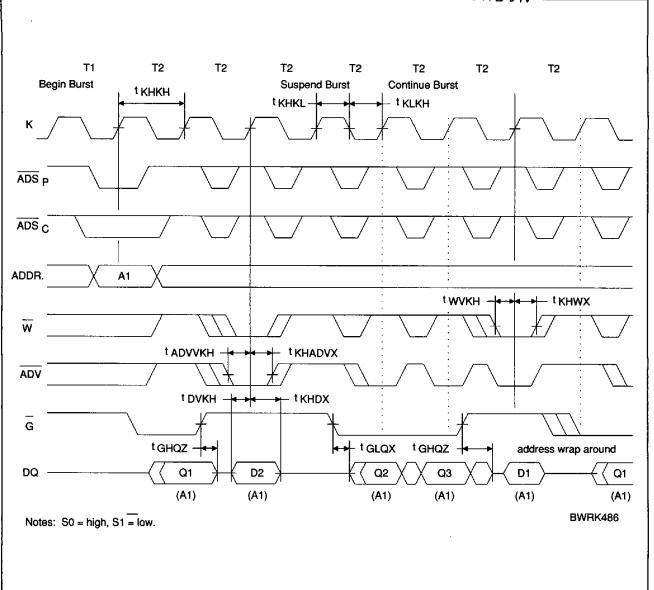

Addresses (A0-A14), data inputs (DQ0-DQ8), and control signals, with exception of Output Enable (G), are clock controlled inputs through non-inverting, pos-itive edge triggered registers. A cache burst address sequence can be initiated by either ADSP (Address Status Processor) or ADSC (Address Sta-tus Cache Controller) inputs, with subsequent burst addresses being internally generated by the Burst SRAM. The ADV input (burst address advance) provides control of the burst sequence, which imitates the i486 cache burst address sequence. Once a cache burst cycle begins, the subsequent burst address is generated internally each time the ADV input is asserted at the rising edge of the clock (K) input. The burst counter operates in the same manner for either cache burst write or read cycles.

The ADSP and the ADSC inputs control the start and the duration of the burst sequence respectively. Each time either address status input is asserted low, a new external base address is registered on the positive going edge of the clock (K).

## **ASYNCHRONOUS TRUTH TABLE**

| Mode                 | G | DQ Status        |

|----------------------|---|------------------|

| Read                 | L | Data Out         |

| Read                 | Н | High-Z           |

| Write <sup>(2)</sup> | Х | Data In (High-Z) |

| Deselect             | × | High-Z           |

#### Notes:

- X = Don't Care.

- For a cache write cycle following a read operation, G

must be high before the input data required set-up time, and be held high through the input data hold time.

# **BURST COUNT SEQUENCE**

T-46-23-13

| External Address  | A14-A2 | A1 | <b>A</b> 0 |

|-------------------|--------|----|------------|

| 1st Burst Address | A14-A2 | A1 | ĀŪ         |

| 2nd Burst Address | A14-A2 | Ā1 | AO         |

| 3rd Burst Address | A14-A2 | Ā1 | ĀŌ         |

**Note :** The burst count sequence wraps around to the initial address after a full count is completed.

S G S-THOMSON

## SYNCHRONOUS TRUTH TABLE

| S0 | <u>\$1</u> | ADSP | ADSC | ADV | w | К | Address                       | Operation                                |

|----|------------|------|------|-----|---|---|-------------------------------|------------------------------------------|

| L  | Х          | L    | Х    | Х   | Х | 1 | N/A                           | Deselected                               |

| Х  | Н          | Н    | L    | Х   | Х | 1 | N/A                           | Deselected                               |

| Н  | L          | L    | х    | Х   | х | Î | External Base Address         | Read Cycle - Begin<br>Burst              |

| Н  | L          | Н    | L    | Х   | L | 1 | External Base Address         | Write Cycle - Extend<br>Burst            |

| Н  | L          | Н    | L    | х   | Н | 1 | External Base Address         | Read Cycle - Extend<br>Burst             |

| Х  | х          | Н    | Н    | L   | L | 1 | Advance Burst Address         | Write Cycle - Continue<br>Burst Sequence |

| х  | х          | Н    | Н    | L   | Н | 1 | Advance Burst Address         | Read Cycle - Continue<br>Burst Sequence  |

| х  | х          | Н    | Н    | Н   | L | 1 | Hold Current Burst<br>Address | Write Cycle - Suspend<br>Burst Sequence  |

| х  | х          | Н    | Н    | Н   | н | 1 | Hold Current Burst<br>Address | Read Cycle - Suspend<br>Burst Sequence   |

#### Notes:

- 1. X = Don't Care.

- All inputs except G require set-up and hold times to the rising edge (low to high transition) of the external clock (K).

- 3. All read and write timings are referenced from  $\overline{G}$  or K.

- A read cycle is defined by W high or ADSP low for the required set-up and hold times. A write cycle is defined by W being asserted low for the set-up and hold times.

- 5.  $\overline{G}$  is a don't care when  $\overline{W}$  is registered low from the previous rising clock edge.

- 6. Chip Selects must be true (S0 = high, \$\overline{S1}\$ = low) at each rising of the clock while \$\overline{ADSP}\$ or \$\overline{ADSC}\$ is asserted for the device to remain enabled; Chip Selects are registered whenever \$\overline{ADSP}\$ or \$\overline{ADSC}\$ is asserted low at the rising edge of the clock.

## **ABSOLUTE MAXIMUM RATINGS**

S G S-THOMSON

T-46-23-13

| Symbol           | Parameter                             | Value      | Unit |

|------------------|---------------------------------------|------------|------|

| Vı               | Voltage on any Pin Relative to Ground | 0.5 to 6   | ٧    |

| TA               | Ambient Operating Temperature         | 0 to 70    | °C   |

| T <sub>STG</sub> | Storage Temperature                   | -65 to 150 | °C   |

| PD               | Power Dissipation                     | 1.2        | w    |

| ЮП               | Output Current                        | 20         | mA   |

## RECOMMENDED DC OPERATING CONDITIONS

$(0 \, ^{\circ}\text{C} \le T_{A} \le +70 \, ^{\circ}\text{C})$

| Symbol          | Parameter          | Min. | Тур. | Max.                  | Unit     |

|-----------------|--------------------|------|------|-----------------------|----------|

| Vcc             | Supply Voltage     | 4.75 | 5    | 5.25                  | ٧        |

| GND             | Ground             | 0    | 0    | 0                     | V        |

| V <sub>IH</sub> | Logic 1 All Inputs | 2.2  | 3    | V <sub>CC</sub> + 0.3 | ٧        |

| VIL             | Logic 0 All Inputs | -0.3 | 0.2  | 0.8                   | <b>V</b> |

## DC ELECTRICAL CHARACTERISTICS

$(0 \, ^{\circ}\text{C} \le T_{A} \le +70 \, ^{\circ}\text{C}; \, V_{CC} = 5\text{V} \pm 5\%)$

| Symbol           | Parameter                                                                                                                                                                      | Min. | Max. | Unit | Note |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>CC1</sub> | Average AC Power Supply Current ( $\overline{G}$ = S0 = V <sub>IH</sub> , $\overline{S1}$ = V <sub>IL</sub> ). All inputs = V <sub>IL</sub> = 0V and V <sub>IH</sub> $\geq$ 3V |      | 160  | mA   | 4    |

| ISB              | TTL Standby Current (S0 = V <sub>IL</sub> , $\overline{S1}$ = V <sub>IH</sub> )                                                                                                |      | 40   | mA   | 5    |

| I <sub>SB1</sub> | CMOS Standby Current (S0 ≤ 0.2V, \$\overline{S1} \ge V_{CC} - 0.2V)                                                                                                            |      | 30   | mA   | 6    |

| lu               | Input Leakage Current (Any Input)                                                                                                                                              | -1   | 1    | μА   | 2    |

| llo              | Output Leakage Current                                                                                                                                                         | -1   | 1    | μΑ   | 2    |

| VoH              | Output Logic 1 Voltage (I <sub>OH</sub> = -4.0mA)                                                                                                                              | 2.4  |      | ٧    | 1    |

| VoL              | Output Logic 0 Voltage (I <sub>OL</sub> = 8mA)                                                                                                                                 |      | 0.4  | V    | 1    |

<sup>1.</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect

<sup>2.</sup> Output current absolute maximum rating is specified for one output at a time, not to exceed a duration of 1 second.

CAPACITANCE

S G S-THOMSON

T-46-23-13

| (T <sub>A</sub> = | 25 | °C, | f = | 1MHz) |

|-------------------|----|-----|-----|-------|

| Symbol | Parameter                                 | Тур. | Max. | Unit | Notes |

|--------|-------------------------------------------|------|------|------|-------|

| Cı     | Input Capacitance on all pins (except DQ) | 4    | 5    | pF   | 7     |

| Co     | Output Capacitance                        | 8    | 10   | pF   | 3, 7  |

#### Notes:

- 1. All voltages referenced to GND.

- 2. Measured with GND  $\leq$  V  $\leq$  V<sub>CC</sub> and outputs deselects.

- Output buffers are deselected.

- I<sub>CC1</sub> measured as average AC current, with outputs open, V<sub>CC</sub> max, tкнкн min duty cycle 100%.

- 5. All other inputs at  $V_{IL}$  or  $V_{IH}$ , f=0,  $V_{CC}$  max.

- 6. All other inputs  $\geq V_{CC} 0.2$  or  $\leq$  GND +0.2, f = 0,  $V_{CC}$  max.

- 7. Capacitances are sampled and not 100% tested.

- 8. For proper operation the RES input should be tied to ground.

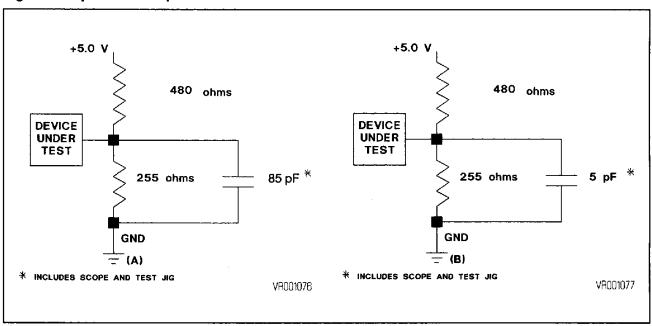

## **AC TEST CONDITIONS**

| Parameter                                      | Value   | Unit |

|------------------------------------------------|---------|------|

| Input Levels                                   | 0 to 3  | ٧    |

| Transition Time                                | 1.5     | ns   |

| Input and Output Signal Timing Reference Level | 1.5     | V    |

| Ambient Temperature                            | 0 to 70 | °C   |

| Supply Voltage                                 | 5 ± 15  | %    |

Figure 3. Equivalent Output Load Circuits

# READ/WRITE CYCLE TIMING - AC OPERATING CONDITIONS AND CHARACTERISTICS

$(0^{\circ}C \le T_A \le 70^{\circ}C; V_{CC} = 5V \pm 5\%)$

S G S-THOMSON

T-46-23-13

| Symbol             | Parameter                      | -1   | 19   | -24  |      | Unit | Note   |

|--------------------|--------------------------------|------|------|------|------|------|--------|

| Symbol             | T didiffeter                   | Min. | Max. | Min. | Max. | J    | ,,,,,, |

| tĸĸĸ               | Cycle Time                     | 25   |      | 30   |      | ns   |        |

| tkhqv              | Clock Access Time              |      | 19   |      | 24   | ns   | 1      |

| tkhkl              | Clock High Pulse Width         | 9.5  |      | 11   |      | ns   |        |

| tkLKH              | Clock Low Pulse Width          | 9.5  |      | 11   |      | ns   |        |

| tGLQV              | Output Enable Access Time      |      | 8    |      | 9    | ns   | 1      |

| tкнох              | Clock High to Output Active    | 3    |      | 3    |      | ns   | 1      |

| tgLax              | Output Enable to Output Active | 0    |      | 0    |      | ns   | 2      |

| tkHQX2             | Clock High to Q Active (Low-Z) | 3    |      | 3    |      | ns   | 2      |

| tkHQZ              | Clock High to Q High-Z         |      | 12   |      | 15   | ns   | 2      |

| tgHQZ              | Output Disable to Q High-Z     |      | 8    |      | 9    | ns   | 2      |

| tavkh              | Address Set-up Time            | 3    |      | 3    |      | ns   | 3      |

| tadsvkh            | Address Status Set-up Time     | 3    |      | 3    |      | ns   | 3      |

| t <sub>DVKH</sub>  | Data In Set-up Time            | 3    |      | 3    |      | ns   | 3      |

| twvkH              | Write/Read Set-up Time         | 3    |      | 3    |      | ns   | 3      |

| tadvvkh            | Address Advance Set-up Time    | 3    |      | 3    |      | ns   | 3      |

| tsovкн             | Chip Select 0 (S0) Set-up Time | 3    |      | 3    |      | ns   | 3      |

| tsıvkh             | Chip Select 1 (S1) Set-up Time | 3    |      | 3    |      | ns   | 3      |

| tkhax              | Address Hold Time              | 2    |      | 2    |      | ns   | 3      |

| tkhadsx            | Address Status Hold Time       | 2    |      | 2    |      | ns   | 3      |

| tкнох              | Data In Hold Time              | 2    |      | 2    |      | ns   | 3      |

| tkHWX              | Write/Read Hold Time           | 2    |      | 2    |      | ns   | 3      |

| tkhadvx            | Address Advance Hold Time      | 2    |      | 2    |      | ns   | 3      |

| tkHSOX             | Chip Select 0 (S0) Hold Time   | 2    |      | 2    |      | ns   | 3      |

| t <sub>KHS1X</sub> | Chip Select 1 (S1) Hold Time   | 2    |      | 2    |      | ns   | 3      |

#### Notes:

- 1. Measured with load as shown in Figure 3A.

- Transition is measured ± 500 mV from steady-stage voltage with load as shown in Figure 3B. This parameter is sampled and not 100 % tested.

- 3. This is a synchronous device requiring that all inputs must meet the specified set-up and hold times with stable logic levels for all rising edges of the clock input (K).

6/12

SGS-THOMSON

## **DEVICE OPERATIONS (Continued)**

When ADSP is asserted low, any ongoing burst cycle is interrupted, and a read operation (independent of W and ADSC) is performed at the new registered external base address. A new burst cycle is initiated each time ADSP is asserted. By asserting ADSC low, the present burst cycle (initiated by ADSP) is interrupted and an extended burst read or write (depending upon the logic state of  $\overline{W}$  at the rising edge of K) is performed at the new registered base address. Chip selects (S0 and S1) are only sampled when a new base address is loaded. Therefore, the chip selects are registered when either address status input is asserted low at the rising edge of the clock (K), and remain latched internally until the next assertion of either ADSP or ADSC. The MK62486 Truth Tables and timing diagrams reference specific device operations.

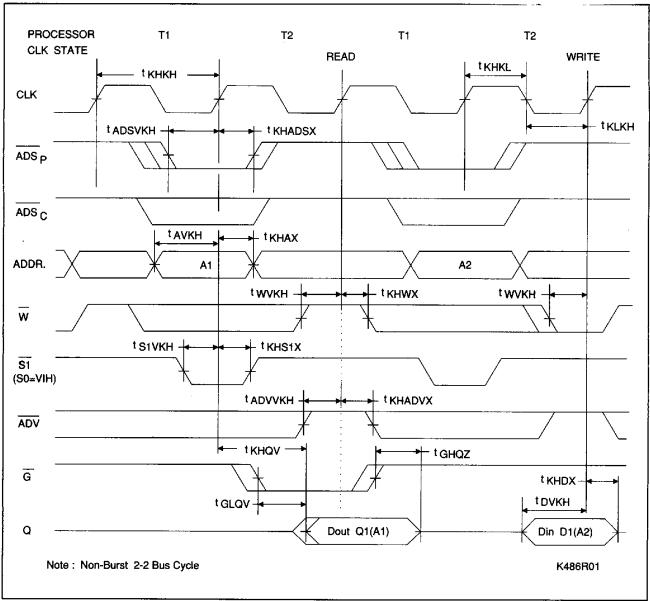

It should be noted that the MK624<u>86</u> allows a non-burst mode of operation where ADSP is the ADS# of the i48<u>6</u> processor in a 2-2 cycle mode of operation, and ADSC is held high during T2 (see Figure 4). However, the non-burst mode obviously negates the advantage of the internal burst counter for fast cache fill operations. In either mode (burst or non-burst), the write cycles are internally self-

timed, and are initiated by the rising edge of the clock input. Self-timed write cycles eliminate complex off-chip write pulse generation providing more flexibility for incoming signals.

The ADV input controls subsequent burst data accesses after the first data of the burst cycle is processed. Each time ADV is asserted low for subsequent bursts at the rising edge of the clock input, the burst counter is advanced to the next burst address sequence. The address is advanced before the operation. Wait states can be inserted during burst cycles by holding the ADV pin high during positive clock transitions. Upon completion of the full internal burst count, the address will wrap-around to its initial base address

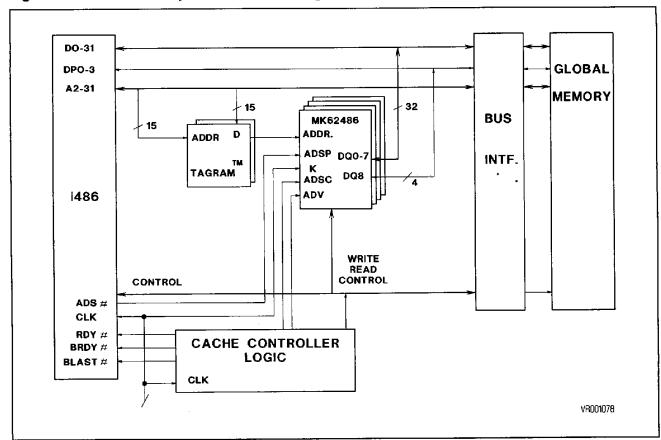

### **GENERAL APPLICATION**

The MK62486 is organized using the ninth bit as the parity bit to support byte parity. Since the i486 processor provides on-board parity generation and checking, the ninth bit of the cache Burst SRAM can be passed to one of the DP0-DP3 pins of the microprocessor. Thus the MK62486 provides an architecture for building a 32K x 32-bit burstable data cache SRAM array, with byte parity, by using four devices in a 128K byte cache application.

Figure 4. General 128K Byte Cache Block Diagram

S G S-THOMSON

SGS-THOMSON MICROELECTRONICS

Figure 5. Non-Burst Read/Write 2-2 Cycles

S G S-THOMSON

T-46-23-13

T-46-23-13

Figure 6. Burst Read Cycle

MOZMOHT-Z B Z \_\_\_\_ T2 T1 T2 T2 T2 T2 T2 T2 T1 Begin Burst **Extend Burst** Suspend Burst <sup>t</sup> KHKH t KHKL-→ ¹ KLKH Κ t ADSVKH t KHADSX ADS p ADS<sub>C</sub> t AVKH <sup>t</sup>KHAX ADDR. АЗ t WVKH-- tKHWX  $\overline{\mathsf{w}}$ tStVKH t KHS1X S1 (S0=VIH) t ADVVKH --†KHADVX ADV **†GLQV** tKHQZ 🔫 † KHQV G ¹KHQX--t GHQZ t GLQX <sup>†</sup> KHQX1 -DQ -Q1 Q2 Q3 Q4 Q1 Q2 Q3 (Data OUT) (A1)(A1) (A1) (A1)(A2)(A2)(A2)BRAMBR2

Figure 7. Burst Write Cycle

S G S-THOMSON

T-46-23-13

Figure 8. Combined Burst Read/Write Cycle

S 6 S-THOMSON

S G S-THOMSON

T-46-23-13

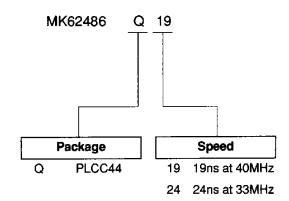

**ORDERING INFORMATION**

Example:

For a list of available options of Package and Speed refer to the Selector Guide in this Data Book or the current Memory Shortform that will be periodically up-dated.

For further information on any aspect of this device, please contact our Sales Office nearest to you.