# TC1322

# 12-Bit Digital-to-Analog Converter with Two-Wire Interface

### Features

- 12-Bit Digital-to-Analog Converter

- 2.7-5.5V Single Supply Operation

- Simple SMBus/I<sup>2</sup>C<sup>™</sup> Serial Interface

- Low Power: 350μA Operation, 0.5μA Shutdown

- 8-Pin SOIC and 8-Pin MSOP Packages

### **Applications**

- Programmable Voltage Sources

- Digital Controlled Amplifiers/Attenuators

- Process Monitoring and Control

### **Device Selection Table**

| Part<br>Number | Package             | Temperature Range |

|----------------|---------------------|-------------------|

| TC1322EOA      | 8-Pin SOIC (Narrow) | -40°C to +85°C    |

| TC1322EUA      | 8-Pin MSOP          | -40°C to +85°C    |

### **General Description**

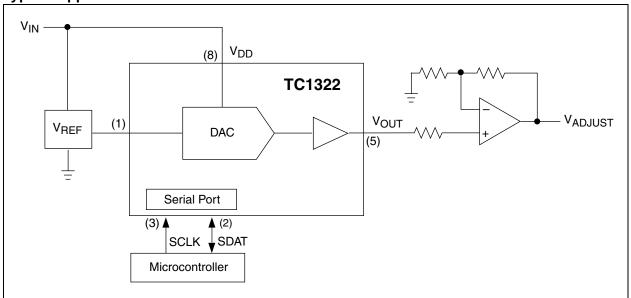

The TC1322 is a serially accessible 12-bit voltage output digital-to-analog converter (DAC). The DAC produces an output voltage that ranges from ground to an externally supplied reference voltage. It operates from a single power supply that can range from 2.7V to 5.5V, making it ideal for a wide range of applications. Built into the part is a Power-on Reset function that ensures that the device starts at a known condition.

Communication with the TC1322 is accomplished via a simple 2-wire SMBus/I<sup>2</sup>C compatible serial port with the TC1322 acting as a slave only device. The host can enable the SHDN bit in the CONFIG register to activate the Low Power Standby mode.

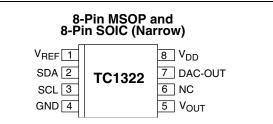

### Package Type

# Typical Application

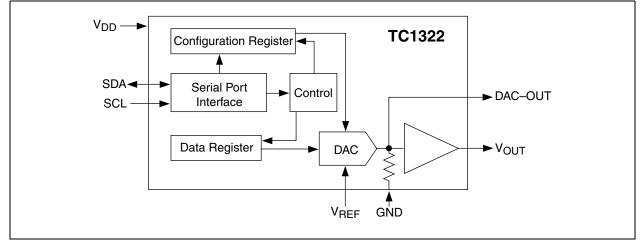

# **Functional Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

## **Absolute Maximum Ratings\***

| Supply Voltage (V <sub>DD</sub> )+6V                        |

|-------------------------------------------------------------|

| Voltage on any Pin (GND – 0.3V) to (V <sub>DD</sub> + 0.3V) |

| Current on any Pin ±50mA                                    |

| Package Thermal Resistance ( $\theta_{JA}$ )                |

| Operating Temperature (T <sub>A</sub> ) See Below           |

| Storage Temperature (T_{STG})65°C to +150°C                 |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

## **TC1322 ELECTRICAL SPECIFICATIONS**

|                         | <b>naracteristics:</b> $V_{DD} = 2.7V$ to 5.5V, -40°C $\leq$ |     |          |                       |          |                                                                                         |

|-------------------------|--------------------------------------------------------------|-----|----------|-----------------------|----------|-----------------------------------------------------------------------------------------|

| Symbol                  | Parameter                                                    | Min | Тур      | Max                   | Unit     | Test Conditions                                                                         |

| Power Supp              | ly                                                           |     |          |                       |          |                                                                                         |

| V <sub>DD</sub>         | Supply Voltage                                               | 2.7 | _        | 5.5                   |          |                                                                                         |

| I <sub>DD</sub>         | Operating Current                                            | _   | 0.35     | 0.5                   | mA       | V <sub>DD</sub> = 5.5V, V <sub>REF</sub> = 1.2V<br>Serial Port Inactive <b>(Note 1)</b> |

| I <sub>DD-STANDBY</sub> | Standby Supply Current                                       | _   | 0.1      | 1                     | μΑ       | V <sub>DD</sub> = 3.3V<br>Serial Port Inactive (Note 1)                                 |

| Static Perfor           | mance - Analog Section                                       |     |          |                       |          |                                                                                         |

|                         | Resolution                                                   | _   |          | 10                    | Bits     |                                                                                         |

| INL                     | Integral Non-Linearity at FS, $T_A = +25^{\circ}C$           | _   | _        | ±16                   | LSB      | (Note 2)                                                                                |

| FSE                     | Full Scale Error                                             | _   | —        | ±3                    | %FS      |                                                                                         |

| DNL                     | Differential Non-Linearity, $T_A = +25^{\circ}C$             | _   | _        | +4                    | LSB      | All Codes (Note 2)                                                                      |

| V <sub>OS</sub>         | Offset Error at V <sub>OUT</sub>                             |     | ±0.3     | ±8                    | mV       | (Note 2)                                                                                |

| TCV <sub>OS</sub>       | Offset Error Tempco at V <sub>OUT</sub>                      | _   | 10       | _                     | μv/°C    |                                                                                         |

| PSRR                    | Power Supply Rejection Ratio                                 |     | 80       | _                     | dB       | V <sub>DD</sub> at DC                                                                   |

| V <sub>REF</sub>        | Voltage Reference Range                                      | 0   | _        | V <sub>DD</sub> – 1.2 | V        |                                                                                         |

| I <sub>REF</sub>        | Reference Input Leakage Current                              |     |          | ±1.0                  | μA       |                                                                                         |

| V <sub>SW</sub>         | Voltage Swing                                                | 0   |          | V <sub>REF</sub>      | V        | $V_{REF} \le (V_{DD} - 1.2V)$                                                           |

| R <sub>OUT</sub>        | Output Resistance @ V <sub>OUT</sub>                         | _   | 5.0      | —                     | Ω        | R <sub>OUT</sub> (Ω)                                                                    |

| I <sub>OUT</sub>        | Output Current (Source or Sink)                              |     | 2        | —                     | mA       |                                                                                         |

| I <sub>SC</sub>         | Output Short-Circuit Current<br>$V_{DD} = 5.5V$              | _   | 30<br>20 | 50<br>50              | mA<br>mA | Source<br>Sink                                                                          |

| Dynamic Pe              |                                                              |     |          |                       |          |                                                                                         |

| SR                      | Voltage Output Slew Rate                                     |     | 0.8      | —                     | V/µs     |                                                                                         |

| t <sub>SETTLE</sub>     | Output Voltage Full Scale Settling Time                      |     | 10       | _                     | μsec     |                                                                                         |

| t <sub>WU</sub>         | Wake-up Time                                                 | _   | 20       | _                     | μs       |                                                                                         |

|                         | Digital Feed through and Crosstalk                           | _   | 5        | _                     | nV-s     | SDA = V <sub>DD</sub> , SCL = 100kHz                                                    |

| Serial Port Ir          | nterface                                                     |     |          |                       |          |                                                                                         |

| V <sub>IH</sub>         | Logic Input High                                             | 2.4 | —        | V <sub>DD</sub>       | V        |                                                                                         |

| V <sub>IL</sub>         | Logic Input Low                                              | _   | _        | 0.6                   | _        |                                                                                         |

| V <sub>OL</sub>         | SDA Output Low                                               | _   |          | 0.4<br>0.6            | V<br>V   | $I_{OL} = 3mA$ (Sinking Current)<br>$I_{OL} = 6mA$                                      |

| C <sub>IN</sub>         | Input Capacitance SDA, SCL                                   | _   | 5        | 0.4                   | pF       |                                                                                         |

| I <sub>LEAK</sub>       | I/O Leakage                                                  | _   | _        | ±1.0                  | μA       |                                                                                         |

**Note 1:** SDA and SCL must be connected to V<sub>DD</sub> or GND.

**2:** Measured at  $V_{OUT} \ge 50 \text{ mV}$  referred to GND to avoid output buffer clipping.

## **TC1322 ELECTRICAL SPECIFICATIONS (CONTINUED)**

| Symbol                 | Parameter                             | Min | Тур | Max  | Unit | Test Conditions                                         |

|------------------------|---------------------------------------|-----|-----|------|------|---------------------------------------------------------|

| Serial Port A          | AC Timing                             |     |     |      | •    |                                                         |

| f <sub>SMB</sub>       | SMBus Clock Frequency                 | 10  | _   | 100  | kHz  |                                                         |

| t <sub>IDLE</sub>      | Bus Free Time Prior to New Transition | 4.7 | _   | _    | μsec |                                                         |

| t <sub>H(START)</sub>  | START Condition Hold Time             | 4.0 | _   | _    | μsec |                                                         |

| t <sub>SU(START)</sub> | START Condition Setup Time            | 4.7 | _   | _    | μsec | 90% SCL to 10% SDA<br>(for Repeated START<br>Condition) |

| t <sub>SU(STOP)</sub>  | STOP Condition Setup Time             | 4.0 | _   | _    | μsec |                                                         |

| t <sub>H-DATA</sub>    | Data In Hold Time                     | 100 | _   | _    | nsec |                                                         |

| t <sub>SU-DATA</sub>   | Data In Setup Time                    | 100 | _   | _    | nsec |                                                         |

| t <sub>LOW</sub>       | Low Clock Period                      | 4.7 | _   | _    | μsec | 10% to 10%                                              |

| t <sub>HIGH</sub>      | High Clock Period                     | 4   | _   | _    | μsec | 90% to 90%                                              |

| t <sub>F</sub>         | SMBus Fall Time                       | _   | _   | 300  | nsec | 90% to 10%                                              |

| t <sub>R</sub>         | SMBus Rise Time                       | _   | _   | 1000 | nsec | 10% to 90%                                              |

| t <sub>POR</sub>       | Power-on Reset Delay                  | _   | 500 | _    | μsec | $V_{DD} \ge V_{POR}$ (Rising Edge                       |

Note 1: SDA and SCL must be connected to V<sub>DD</sub> or GND.

2: Measured at V<sub>OUT</sub> ≥ 50mV referred to GND to avoid output buffer clipping.

# 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

| Pin Number | Symbol           | Туре           | Description                                                                                                                                                                                                                                            |

|------------|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>REF</sub> | Input          | Input. Voltage Reference Input can range from 0V to 1.2V below $V_{DD}$ .                                                                                                                                                                              |

| 2          | SDA              | Bi-Directional | Bi-directional. Serial data is transferred on the SMBus in both directions using this pin.                                                                                                                                                             |

| 3          | SCL              | Input          | Input. SMBus serial clock. Clocks data into and out of the TC1322.                                                                                                                                                                                     |

| 4          | GND              | Power          | Ground.                                                                                                                                                                                                                                                |

| 5          | V <sub>OUT</sub> | Output         | Output. Buffered DAC output voltage. This voltage is a function of the reference voltage and the contents of the DATA register.                                                                                                                        |

| 6          | NC               | None           | No connection.                                                                                                                                                                                                                                         |

| 7          | DAC-OUT          | Output         | Output. Unbuffered DAC output voltage. This voltage is a function of the ref-<br>erence voltage and the contents of the DATA register. This output is<br>unbuffered and care must be taken that the pin is connected only to a<br>high-impedance node. |

| 8          | V <sub>DD</sub>  | Power          | Input. Positive power supply input. See electrical specifications.                                                                                                                                                                                     |

<sup>© 2002</sup> Microchip Technology Inc.

# 3.0 DETAILED DESCRIPTION

The TC1322 is a monolithic 10-bit digital-to-analog converter that is designed to operate from a single supply that can range from 2.7V to 5.5V. The DAC consists of a data register (DATA), a configuration register (CONFIG), and a current output amplifier. The TC1322 uses an external reference, which also determines the maximum output voltage.

The TC1322 uses a current steering DAC based on an array of matched current sources. This current, along with a precision resistor, converts the contents of the Data register and  $V_{\text{REF}}$  into an output voltage,  $V_{\text{OUT}}$  given by:

$V_{OUT} = V_{REF} (DATA/4096)$

### 3.1 Reference Input

The reference pin, V<sub>REF</sub> is a buffered high-impedance input and because of this, the load regulation of the reference source needs only to be able to tolerate leakage levels of current (less than 1µA). V<sub>REF</sub> accepts a voltage range from 0 to (V<sub>DD</sub> – 1.2V). Input capacitance is typically 10pF.

### 3.2 Output Amplifier

The TC1322 DAC output is buffered with an internal unity gain rail-to-rail input/output amplifier with a typical slew rate of  $0.8V/\mu$ sec. Maximum full scale transition settling time is 10 $\mu$ sec to within ±1/2LSB when loaded with 1k $\Omega$  in parallel with 100pF.

### 3.3 Standby Mode

The TC1322 allows the host to put it into a Low Power ( $I_{DD} = 0.5\mu A$ , typical) Standby mode. In this mode, the D/A conversion is halted. The SMBus port operates normally. Standby mode is enabled by setting the SHDN bit in the CONFIG register. The table below summarizes this operation.

TABLE 3-1: STANDBY MODE OPERATION

| SHDN Bit | Operating Mode |

|----------|----------------|

| 0        | Normal         |

| 1        | Standby        |

### 3.4 SMBus Slave Address

The TC1322 is internally programmed to have a default SMBus address value of 1001 000b. Seven other addresses are available by custom order (contact factory). See Figure 3-1 for location of address bits in SMBus protocol.

## FIGURE 3-1: SMBus PROTOCOLS

|                                                                                                                                                                                                                                                                                                                                                                                                                               | s /                                                                                             | Addres                                           | s                                    | R/W                                                                                                 | ACK                                                                                                                                 | Con                                        | nmand                                                                           | ACK                              | Da   | ata /             | ACK                                | Р                 | ]  |      |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------|----------------------------------|------|-------------------|------------------------------------|-------------------|----|------|----------|

|                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                 | 7-Bits                                           |                                      | 0                                                                                                   |                                                                                                                                     |                                            | -Bits                                                                           |                                  |      | Bits              |                                    |                   | -  |      |          |

| Vri                                                                                                                                                                                                                                                                                                                                                                                                                           | Slave                                                                                           | Addre                                            |                                      |                                                                                                     | Command Byte: selects<br>which register you are<br>writing to.Data Byte: data goes<br>into the register set<br>by the command byte. |                                            |                                                                                 |                                  |      |                   | _                                  |                   |    |      |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                               | Addres                                           |                                      | R/W                                                                                                 | ACK                                                                                                                                 | Co                                         | mmand                                                                           | ACK [                            |      | Data              | ACK                                | Data              | a  | ACK  | Р        |

|                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                 | 7-Bi                                             | s                                    | 0                                                                                                   |                                                                                                                                     |                                            | 8-Bits                                                                          |                                  | 8    | -Bits             |                                    | 8-Bi              | ts |      |          |

| lea                                                                                                                                                                                                                                                                                                                                                                                                                           | Sla<br>ad 1-Byte I                                                                              | ve Add<br>Forma                                  |                                      |                                                                                                     |                                                                                                                                     |                                            | mand Byte<br>n register y<br>ng to.                                             |                                  | into | the reg           | data go<br>gister se<br>Imand b    | t                 |    |      |          |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                             | Address                                                                                         | R/W                                              | ACK                                  | Comman                                                                                              | d AC                                                                                                                                | (S                                         | Address                                                                         | R/W                              | ACK  | Data              | NACK                               | Р                 | ]  |      |          |

| -                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-Bits                                                                                          | 0                                                |                                      | 8-Bits                                                                                              |                                                                                                                                     |                                            | 7-Bits                                                                          | 1                                |      | 8-Bits            |                                    |                   |    |      |          |

| Slave Address       Command Byte: selects which register you are reading from.       Slave Address: repeated due to change in data flow direction.       Data Byte: reads from the register set by the command byte.         Read 2-Byte Format       S       Address       R/W       ACK       Command       ACK       S       Address       R/W       ACK       Data Byte: reads from the register set by the command byte. |                                                                                                 |                                                  |                                      |                                                                                                     |                                                                                                                                     |                                            |                                                                                 |                                  |      |                   |                                    |                   |    | NACK |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                 |                                                  | /.0/.                                | Comman                                                                                              | Id AC                                                                                                                               | · · ·                                      |                                                                                 |                                  |      |                   |                                    |                   |    |      |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-Bits                                                                                          | 0                                                |                                      | 8-Bits                                                                                              |                                                                                                                                     |                                            | 7-Bits                                                                          | 1                                |      | 8-Bits            |                                    | 8-B               |    |      |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                               | 7-Bits<br>Slave Addro<br>ceive 1-Byt                                                            | ess                                              | wh<br>rea                            | 8-Bits<br>mmand B<br>ich registe<br>ading from                                                      | yte: sele<br>er you ar                                                                                                              | e d                                        |                                                                                 | 1<br>ess: rep<br>ige in da       |      | Data B<br>the reg | yte: read<br>ister set<br>and byte | ds fror<br>by the | m  |      | Р        |

|                                                                                                                                                                                                                                                                                                                                                                                                                               | Slave Addr                                                                                      | ess<br>e Fori                                    | wh<br>rea<br>nat                     | mmand B<br>ich registe<br>ading from                                                                | yte: sele<br>er you ar                                                                                                              | e d                                        | 7-Bits<br>Slave Addre<br>due to char                                            | 1<br>ess: rep<br>ige in da       |      | Data B<br>the reg | yte: read<br>ister set             | ds fror<br>by the | m  |      | <u> </u> |

| lec                                                                                                                                                                                                                                                                                                                                                                                                                           | Slave Addr                                                                                      | e Fori                                           | wh<br>rea<br>nat                     | mmand B<br>ich registe<br>ading from                                                                | yte: sele<br>er you ar                                                                                                              | e c<br>f                                   | 7-Bits<br>Slave Addre<br>due to char                                            | 1<br>ess: rep<br>ige in da       |      | Data B<br>the reg | yte: read<br>ister set             | ds fror<br>by the | m  |      |          |

| S<br>S<br>S<br>S                                                                                                                                                                                                                                                                                                                                                                                                              | Slave Address                                                                                   | e Forn<br>R/W<br>1<br>ndition<br>dition<br>Frans | wh<br>rea<br>mat<br>7 ACk<br>mission | mmand B<br>ich registe<br>ading from<br>Data<br>B-Bits<br>Data By<br>the reg<br>n the last          | NACK<br>yte: read<br>ister com                                                                                                      | P<br>S data<br>mand<br>te or w             | 7-Bits<br>Slave Addre<br>due to char<br>low direction<br>from<br>ed by          | 1<br>ess: rep<br>ige in da       |      | Data B<br>the reg | yte: read<br>ister set             | ds fror<br>by the | m  |      |          |

| S<br>S<br>S<br>S                                                                                                                                                                                                                                                                                                                                                                                                              | Slave Address<br>ceive 1-Byt<br>Address<br>START Cor<br>STOP Con-<br>ded = Slave<br>ceive 1-Byt | e Forn<br>R/W<br>dition<br>dition<br>a Trans     | wh<br>rea<br>mat<br>mission<br>mat   | mmand B<br>ich registe<br>ading from<br>Data<br>8-Bits<br>Data B<br>the reg<br>the last<br>byte tra | yte: sele<br>er you ard<br>NACK<br>yte: read<br>ister com<br>t read by                                                              | P<br>S data<br>mand<br>te or w             | 7-Bits<br>Slave Addre<br>due to char<br>low direction<br>from<br>ed by<br>rrite | 1<br>ess: rep<br>ige in da       |      | Data B<br>the reg | yte: read<br>ister set             | ds fror<br>by the | m  |      |          |

| Rec<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S                                                                                                                                                                                                                                                                                                                            | Slave Address<br>ceive 1-Byt<br>Address<br>START Cor<br>STOP Con-<br>ded = Slave<br>ceive 1-Byt | e Forn<br>R/W<br>dition<br>dition<br>a Trans     | wh<br>rea<br>mat<br>mission<br>mat   | mmand B<br>ich registe<br>ading from<br>Data<br>8-Bits<br>Data B<br>the reg<br>the last<br>byte tra | NACK<br>yte: read<br>ister com<br>t read by<br>ACK                                                                                  | P<br>P<br>s data<br>mand<br>te or w<br>on. | 7-Bits<br>Slave Addre<br>due to char<br>low direction<br>from<br>ed by<br>rrite | 1<br>ess: rep<br>ge in da<br>on. |      | Data B<br>the reg | yte: read<br>ister set             | ds fror<br>by the | m  |      |          |

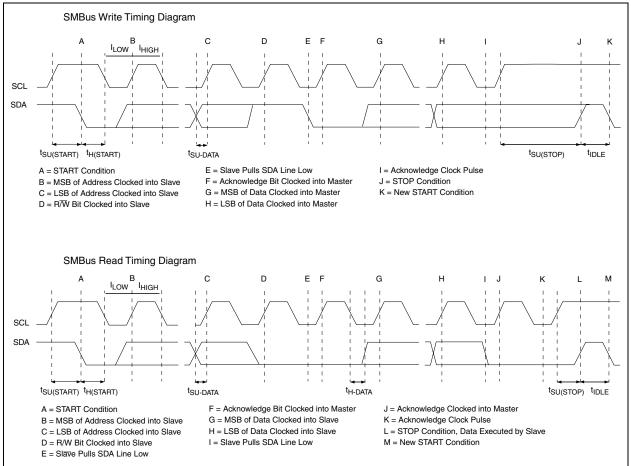

# 4.0 SERIAL PORT OPERATION

The Serial Clock input (SCL) and bi-directional data port (SDA) form a 2-wire bi-directional serial port for programming and interrogating the TC1322. The following conventions are used in this bus architecture:

### TABLE 4-1: TC1322 SERIAL BUS CONVENTIONS

| Term        | Explanation                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter | The device sending data to the bus.                                                                                                                                                                                                   |

| Receiver    | The device receiving data from the bus.                                                                                                                                                                                               |

| Master      | The device which controls the bus: initiating transfers (START), generating the clock, and terminating transfers (STOP).                                                                                                              |

| Slave       | The device addressed by the master.                                                                                                                                                                                                   |

| START       | A unique condition signaling the beginning of<br>a transfer indicated by SDA falling<br>(High - Low) while SCL is high.                                                                                                               |

| STOP        | A unique condition signaling the end of a transfer indicated by SDA rising (Low - High) while SCL is high.                                                                                                                            |

| ACK         | A Receiver Acknowledges the receipt of each<br>byte with this unique condition. The Receiver<br>drives SDA low during SCL high of the ACK<br>clock pulse. The Master provides the clock<br>pulse for the ACK cycle.                   |

| Busy        | Communication is not possible because the bus is in use.                                                                                                                                                                              |

| Not Busy    | When the bus is IDLE, both SDA and SCL will remain high.                                                                                                                                                                              |

| Data Valid  | The state of SDA must remain stable during<br>the High period of SCL, in order for a data bit<br>to be considered valid. SDA only changes<br>state while SCL is low during normal data<br>transfers. (See START and STOP conditions.) |

All transfers take place under control of a host, usually a CPU or microcontroller acting as the Master, which provides the clock signal for all transfers. The TC1322 *always* operates as a Slave. The serial protocol is illustrated in Figure 3-1. All data transfers have two phases; all bytes are transferred MSB first. Accesses are initiated by a START condition (START), followed by a device address byte and one or more <u>data</u> bytes. The device address byte includes a Read/Write selection bit. Each access must be terminated by a STOP condition (STOP). A convention called *Acknowledge* (ACK) confirms receipt of each byte. Note that SDA can change only during periods when SCL is LOW (SDA changes while SCL is HIGH are reserved for START and STOP conditions).

### 4.1 START Condition (START)

The TC1322 continuously monitors the SDA and SCL lines for a START condition (a HIGH to LOW transition of SDA while SCL is HIGH), and will not respond until this condition is met.

### 4.2 Address Byte

Immediately following the START condition, the host must transmit the address byte to the TC1322. The 7-bit SMBus address for the TC1322 is 1001000. The 7-bit address transmitted in the serial bit stream must match for the TC1322 to respond with an Acknowledge (indicating the TC1322 is on the bus and ready to accept data). The eighth bit in the Address Byte is a Read-Write bit. This bit is a 1 for a read operation or 0 for a write operation. During the first phase of any transfer, this bit will be set = 0 to indicate that the command byte is being written.

### 4.3 Acknowledge (ACK)

Acknowledge (ACK) provides a positive handshake between the host and the TC1322. The host releases SDA after transmitting eight bits, then generates a ninth clock cycle to allow the TC1322 to pull the SDA line LOW to acknowledge that it successfully received the previous eight bits of data or address.

### 4.4 Data Byte

After a successful ACK of the address byte, the host must transmit the data byte to be written or clock out the data to be read. (See the appropriate timing diagrams.) ACK will be generated after a successful write of a data byte into the TC1322.

## 4.5 STOP Condition (STOP)

Communications must be terminated by a STOP condition (a LOW to HIGH transition of SDA while SCL is HIGH). The STOP Condition must be communicated by the transmitter to the TC1322. Refer to Figure 4-1, Timing Diagrams for serial bus timing.

DS21388B-page 8

### 4.6 Register Set and Programmer's Model

# TABLE 4-2:TC1322 COMMAND SET<br/>(SMBus READ\_BYTE AND<br/>WRITE\_BYTE)

| Command Byte Description |      |                                   |  |  |  |  |  |  |

|--------------------------|------|-----------------------------------|--|--|--|--|--|--|

| Command                  | Code | Function                          |  |  |  |  |  |  |

| RWD                      | 00h  | Read/Write Data (DATA)            |  |  |  |  |  |  |

| RWCR                     | 01h  | Read/Write Configuration (CONFIG) |  |  |  |  |  |  |

# TABLE 4-3:CONFIGURATION REGISTER<br/>(CONFIG), 8-BIT, READ/WRITE

|             | Configuration Register (CONFIG) |                                 |         |        |                |      |                   |  |  |  |  |

|-------------|---------------------------------|---------------------------------|---------|--------|----------------|------|-------------------|--|--|--|--|

| D[7]        | D[6]                            | D[5]                            | D[4]    | D[3]   | D[2]           | D[1] | D[0]              |  |  |  |  |

|             | Reserved                        |                                 |         |        |                |      |                   |  |  |  |  |

| В           | it                              | POR                             | Fund    | tion   | Туре           | Оре  | ration            |  |  |  |  |

| DĮ          | D[0]                            |                                 | Standby | Switch | Read/<br>Write |      | Standby<br>Normal |  |  |  |  |

| D[7]-D[1] 0 |                                 | Reserve<br>Always r<br>Zero whe | eturns  | N/A    | ١              | N/A  |                   |  |  |  |  |

# TABLE 4-4:DATA REGISTER (DATA),<br/>12-BIT, READ/WRITE

| Data Register (DATA) for 1st Byte |                                   |      |      |      |      |      |      |  |  |  |  |

|-----------------------------------|-----------------------------------|------|------|------|------|------|------|--|--|--|--|

| D[11]                             | D[0]                              | D[9] | D[8] | D[7] | D[6] | D[5] | D[4] |  |  |  |  |

| MSB                               | Х                                 | Х    | Х    | Х    | Х    | Х    | LSB  |  |  |  |  |

|                                   | Data Register (DATA) for 2nd Byte |      |      |      |      |      |      |  |  |  |  |

| D[3]                              | D[2]                              | D[1] | D[0] | Х    | Х    | Х    | Х    |  |  |  |  |

| Х                                 | Х                                 | Х    | LSB  | Х    | Х    | Х    | Х    |  |  |  |  |

The DAC output voltage is a function of reference voltage and the binary value of the contents of the register DATA. The transfer function is given by the expression:

### **EQUATION 4-1:**

| $V_{OUT} = V_{REF} \times \left[\frac{DATA}{4096}\right]$ |  |

|-----------------------------------------------------------|--|

|-----------------------------------------------------------|--|

### 4.7 Register Set Summary

The TC1322's register set is summarized in Table 4-5 below. All registers are 12-bits wide.

| TABLE 4-5: | TC1322 REGISTER SET |

|------------|---------------------|

|            | SUMMARY             |

| Name   | Description                      | POR State     | Read | Write |

|--------|----------------------------------|---------------|------|-------|

| Data   | Data Register<br>(2-Byte Format) | d00000000000b | Х    | Х     |

| Config | CONFIG Register                  | d0000 0000b   | Х    | Х     |

DS21388B-page 10

# 5.0 PACKAGING INFORMATION

### 5.1 Package Marking Information

Package marking data not available at this time.

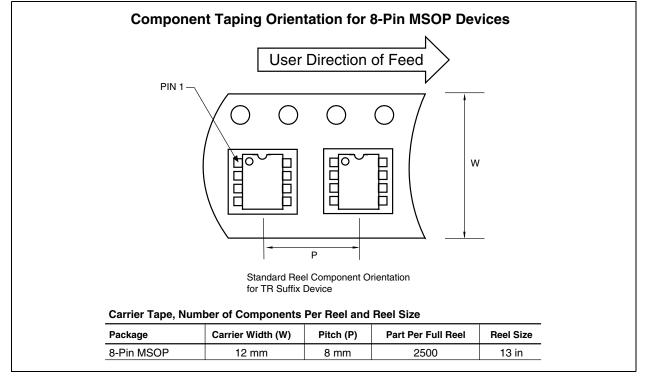

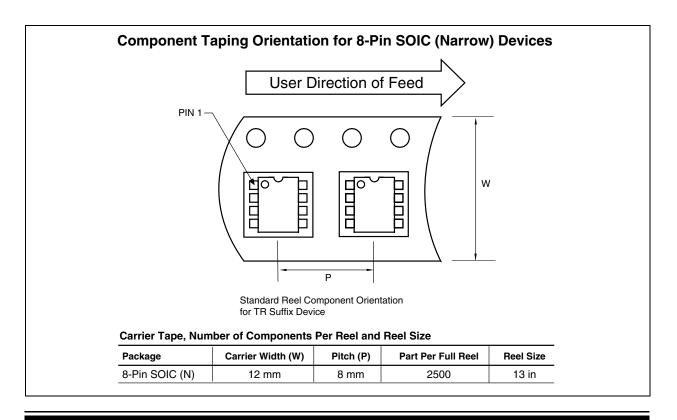

### 5.2 Taping Forms

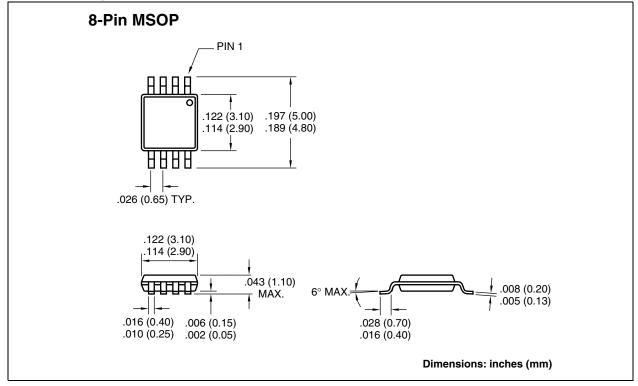

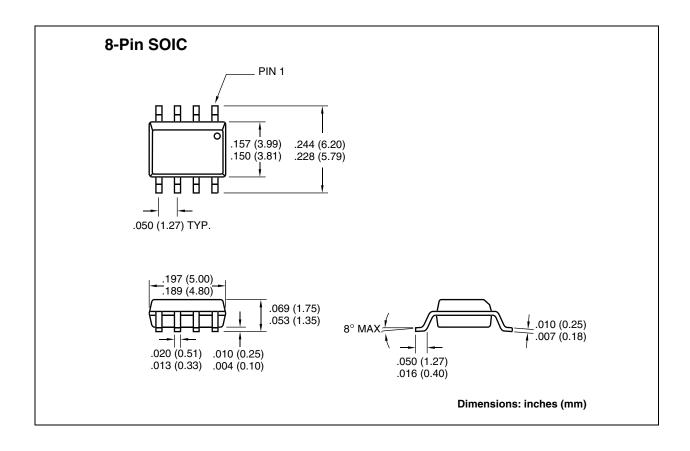

### 5.3 Package Dimensions

DS21388B-page 12

NOTES:

<sup>© 2002</sup> Microchip Technology Inc.

# SALES AND SUPPORT

### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 2. 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PlCmicro® 8-bit MCUs, KEELoo® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

# WORLDWIDE SALES AND SERVICE

### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

Chicago 333 Pierce Road, Suite 180

Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334

Tel: 248-538-2250 Fax: 248-538-2260 Kokomo

2767 S. Albright Road Kokomo, Indiana 46902

Tel: 765-864-8360 Fax: 765-864-8387 Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

**New York**

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

### China - Chengdu

Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599

### China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521 China - Shanghai

Microchip Technology Consulting (Shanghai) Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086 Hong Kong

Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

### India

Microchip Technology Inc. India Liaison Office **Divvasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471-6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-6334-8870 Fax: 65-6334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan

Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

### EUROPE

Denmark

Microchip Technology Nordic ApS **Regus Business Centre** Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910

France

Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Microchip Technology GmbH

Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy

Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

### **United Kinadom**

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

03/01/02