Order this document by DSP56156/D REV 1

MOTOROLA SEMICONDUCTOR TECHNICAL DATA

# DSP56156 DSP56156ROM

## Advance Information 16-bit Digital Signal Processor

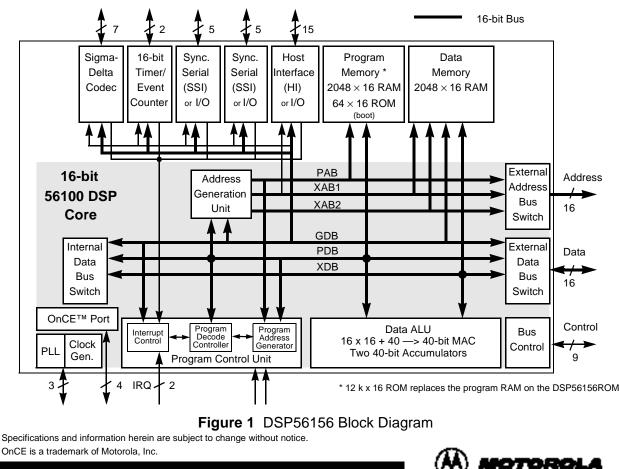

The DSP56156 is a general-purpose MPU-style Digital Signal Processor (DSP). On a single semiconductor chip, the DSP56156 comprises a very efficient 16-bit digital signal processing core, program and data memories, a number of peripherals, and system support circuitry. Unique features of the DSP56156 include a built-in sigma-delta ( $^2$ ý) codec and phase-locked loop (PLL). This combination of features makes the DSP56156 a cost-effective, high-performance solution for many DSP applications, especially speech coding, digital communications, and cellular base stations.

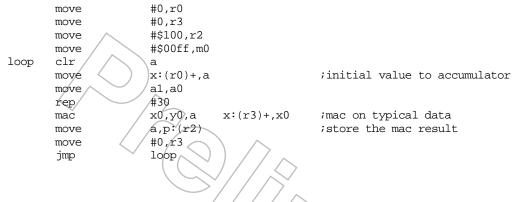

The central processing unit of the DSP56156 is the DSP56100 core processor. Like all DSP56100based DSPs, the DSP56156 consists of three execution units operating in parallel, allowing up to six operations to be performed during each instruction cycle. This parallelism greatly increases the effective processing speed of the DSP56156. The MPU-style programming model and instruction set allow straightforward generation of efficient, compact code. The basic architectures and development tools of Motorola's 16-bit, 24-bit, and 32-bit DSPs are so similar that understanding how to design and program one greatly reduces the time needed to learn the others.

On-Chip Emulation (OnCE<sup>™</sup> port) circuitry provides convenient and inexpensive debug facilities normally available only through expensive external hardware. Development costs are reduced and in-field testing is greatly simplified using the OnCE<sup>™</sup> port. Figure 1 illustrates the DSP56156 in detail.

© MOTOROLA INC., 1994

## **DSP56156 Features**

### **Digital Signal Processing Core**

- Efficient, object code compatible, 16-bit 56100-Family DSP engine

- Up to 30 Million Instructions Per Second (MIPS) 33 ns instruction cycle at 60 MHz

Freescale Semiconductor, Inc.

- Up to 180 Million Operations Per Second (MOPS) at 60 MHz

- Highly parallel instruction set with unique DSP addressing modes

- Two 40-bit accumulators including extension byte

- Parallel 16 × 16-bit multiply-accumulate in 1 instruction cycle (2 clock cycles)

- Double precision  $32 \times 32$ -bit multiply with 72-bit result in 6 instruction cycles

- Least Mean Square (LMS) adaptive loop filter in 2 instructions

- 40-bit Addition/Subtraction in 1 instruction cycle

- Fractional and integer arithmetic with support for multiprecision arithmetic

- Hardware support for block-floating point FFT

- Hardware-nested DO loops including infinite loops

- Zero-overhead fast interrupts (2 instruction cycles)

- Three 16-bit internal data buses and three 16-bit internal address buses for maximum information transfer on-chip

### Memory

- On-chip Harvard architecture permitting simultaneous accesses to program and memories

- 2048  $\times$  16-bit on-chip program RAM and 64  $\times$  16-bit bootstrap ROM (or 12 k  $\times$  16-bit on-chip program ROM on the DSP56156ROM)

- $2048 \times 16$ -bit on-chip data RAM

- External memory expansion with 16-bit address and data buses

- Bootstrap loading from external data bus, Host Interface, or Synchronous Serial Interface

### Peripheral and Support Circuits

- Byte-wide Host Interface (HI) with Direct Memory Access support

- Two Synchronous Serial Interfaces (SSI) to communicate with codecs and synchronous serial devices

- Built in  $\mu$ -law and A-law compression/expansion

- Up to 32 software-selectable time slots in network mode

- 16-bit Timer/Event Counter also generates and measures digital waveforms

- On-chip sigma-delta voice band Codec:

- Sampling clock rates between 100 kHz and 3 MHz

- Four software-programmable decimation/interpolation ratios

- Internal voltage reference ( $^{2}/_{5}$  of positive power supply)

- No external components required

2

DSP56156 Features Documentation

- On-chip peripheral registers memory mapped in data memory space

- Double buffered peripherals

- Up to 27 general purpose I/O pins

- Two external interrupt request pins

- On-Chip Emulation (OnCE<sup>™</sup>) port for unobtrusive, processor speed-independent debugging

- Software-programmable, Phase-Locked Loop-based (PLL) frequency synthesizer for the core clock

### **Miscellaneous Features**

- Power-saving Wait and Stop modes

- Fully static, HCMOS design for operating frequencies from 40 or 60 MHz down to DC

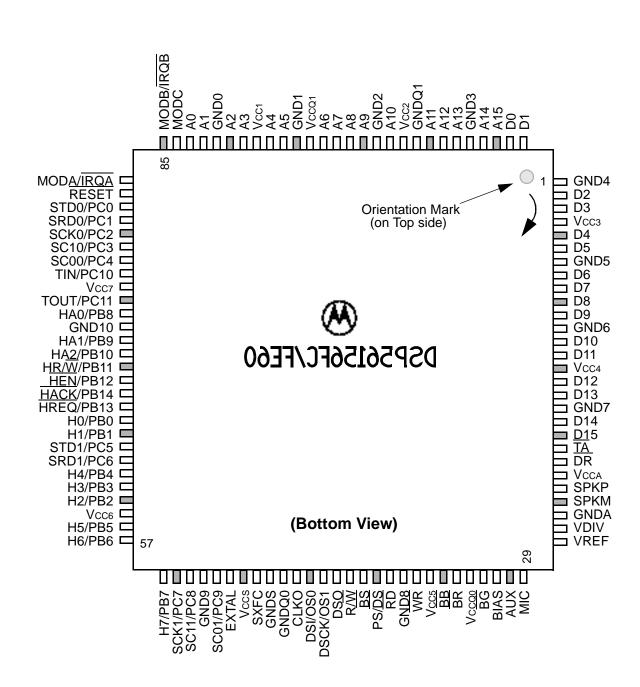

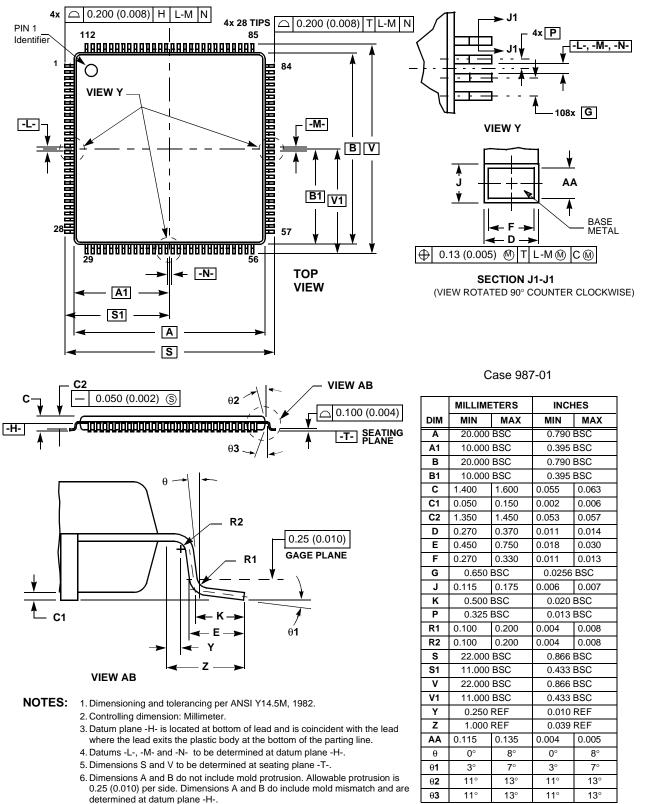

- 112-pin Ceramic Quad Flat Pack (CQFP) surface-mount package;  $20 \times 20 \times 3$  mm

- 112-pin Plastic Thin Quad Flat Pack (TQFP) surface-mount package;  $20 \times 20 \times 1.5$  mm

- 5 V power supply

## **Product Documentation**

This data sheet plus the two manuals listed in Table 1 are required for a complete DSP56156 description and are necessary to properly design with the part. Documentation is available from a local Motorola distributor, a semiconductor sales office, or through a Motorola Literature Distribution Center.

| Торіс                  | Description                                                                                                    | Order Number     |

|------------------------|----------------------------------------------------------------------------------------------------------------|------------------|

| DSP56100 Family Manual | Detailed description of the 56000-<br>family architecture and the 16-bit core<br>processor and instruction set | DSP56100FAMUM/AD |

| DSP56156 User's Manual | Detailed description of memory, peripherals, and interfaces                                                    | DSP56156UM/AD    |

| DSP56156 Data Sheet    | Pin and package descriptions, and electrical and timing specifications                                         | DSP56156/D       |

| Table 1 | DSP56156 | Documentation |

|---------|----------|---------------|

|         |          |               |

### Introduction

Documentation Data Sheet Contents

### **Related Documentation**

Table 2 lists additional documentation relevant to the DSP56156.

| Торіс                             | Description                                                                                             | Order Number   |

|-----------------------------------|---------------------------------------------------------------------------------------------------------|----------------|

| DSP Family Brochure               | Overview of all DSP product families                                                                    | BR1105/D       |

| Development Tools                 | Product Brief. Includes ordering information                                                            | DSPTOOLSP/D    |

| Fractional and Integer Arithmetic | Application Report. Includes code                                                                       | APR3/D         |

| Fast Fourier Transforms (FFTs)    | Application Report. Comprehensive<br>FFT algorithms and code for<br>DSP56001, DSP56156, and<br>DSP96002 | APR4/D         |

| G.722 Audio Processing            | Application Report. Theory and code using SB-ADPCM                                                      | APR404/D       |

| Dr. BuB Bulletin Board            | Flyer. Motorola's electronic bulletin board where free DSP software is available                        | BR297/D        |

| Third Party Compendium            | Brochures from companies selling<br>hardware and software that supports<br>Motorola DSPs                | DSP3RDPTYPAK/D |

| University Support Program        | Flyer. Motorola's program that supports universities in DSP research and education                      | BR382/D        |

| Table 2 Related Motorola Documentatio | n |

|---------------------------------------|---|

|---------------------------------------|---|

### **Data Sheet Contents**

This data sheet contains:

- signal definitions and pin locations

- electrical specifications and timings

- package descriptions

- design considerations

- ordering information

Downloaded from Elcodis.com electronic components distributor

## **Pin Groupings**

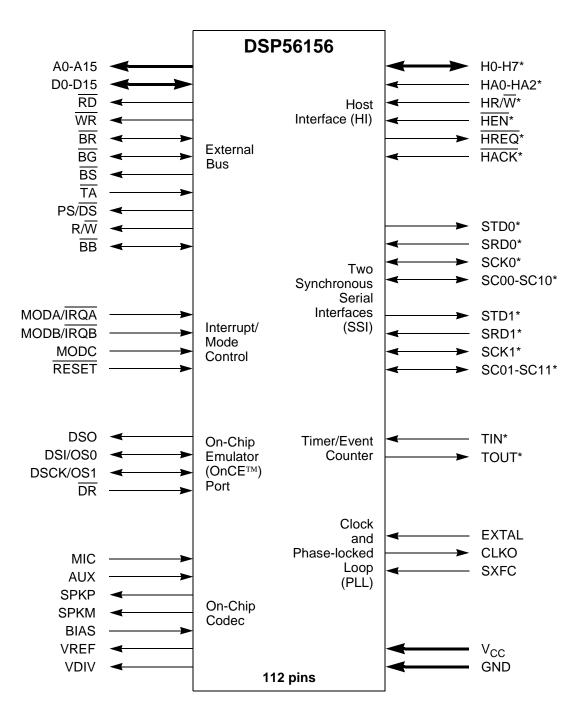

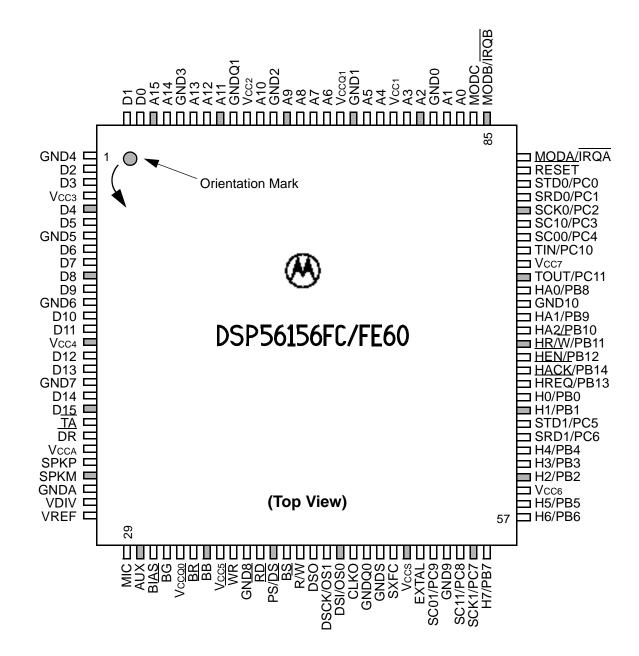

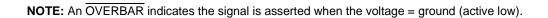

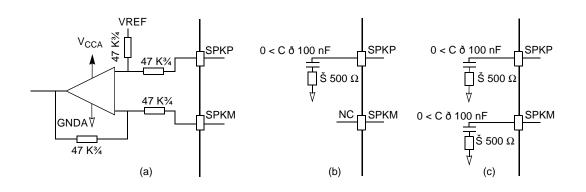

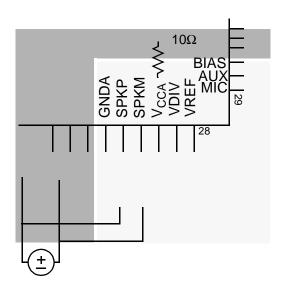

The DSP56156 is available in a 112-pin Ceramic Quad Flat Pack (CQFP) and a 112-pin Plastic Thin Quad Flat Pack (TQFP). The input and output signals are organized into the functional groups indicated in Table 3. Figure 2 illustrates the chip's pin functions.

| Functional Group                            | Number of Pins |

|---------------------------------------------|----------------|

| Address                                     | 16             |

| Data Bus                                    | 16             |

| Bus Control                                 | 9              |

| Host Interface (HI)                         | 15             |

| Synchronous Serial Interfaces (SSI)         | 10             |

| Timer Interface                             | 2              |

| Interrupt and Mode Control                  | 4              |

| Phase-Locked Loop (PLL) and Clock           | 3              |

| On-Chip Emulation (OnCE <sup>TM</sup> Port) | 4              |

| On-Chip Codec                               | 7              |

| Power (V <sub>CC</sub> )                    | 10             |

| Ground (GND)                                | 16             |

| Total                                       | 112            |

| Table 3 | Functional I | Pin Groupings |

|---------|--------------|---------------|

|---------|--------------|---------------|

**NOTE:** OVERBARS are used throughout this document to indicate a signal which is at Ground voltage (typically a TTL logic low  $- V_{IL}$  or  $V_{OL}$ ) when the function is logically true. These signals are, likewise, at  $V_{CC}$  voltage (typically a TTL logic high  $- V_{IH}$  or  $V_{OH}$ ) when the function is logically false.

#### Introduction

**Pin Functions**

\* These pins have an alternate function of general purpose input/output.

Figure 2 DSP56156 Pin Functions

Downloaded from Elcodis.com electronic components distributor

# **Pin Descriptions**

### Address and Data Bus

- A0-A15 (Address Bus) three-state, active high outputs. A0-A15 change in t0 and specify the address for external program and data memory accesses. If there is no external bus activity, A0-A15 remain at their previous values. A0-A15 are three-stated during hardware reset.

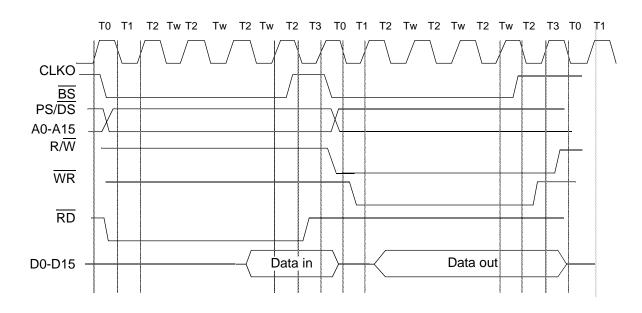

- D0-D15 (Data Bus) - three-state, active high, bidirectional input/outputs. Read data is sampled on the trailing edge of t2, while write data output is enabled by the leading edge of t2 and three-stated at the leading edge of t0. If there is no external bus activity, D0-D15 are three-stated. D0-D15 are also threestated during hardware reset.

## **Bus Control**

- PS/DS (Program/Data Memory Select) three-state, active low output. This output is asserted only when external data memory is referenced.  $PS/\overline{DS}$  timing is the same for the A0-A15 address lines.  $PS/\overline{DS}$  is high for program memory access and is low for data memory access. If the external bus is not used during an instruction cycle (t0, t1, t2, t3),  $PS/\overline{DS}$  goes high in t0.  $PS/\overline{DS}$  is in the high impedance state during hardware reset.

- R/W (Read/Write) three-state, active low output. Timing is the same as the address lines, providing an "early write" signal.  $R/\overline{W}$  (which changes in t0) is high for a read access and is low for a write access. If the external bus is not used during an instruction cycle

Go to: www.freescale.com

(t0, t1, t2, t3),  $R/\overline{W}$  goes high in t0.  $R/\overline{W}$ is three-stated during hardware reset.

- WR (Write Enable) three-state, active low output. This output is asserted during external memory write cycles. When  $\overline{WR}$  is asserted in t1, the data bus pins D0-D15 become outputs and the DSP puts data on the bus during the leading edge of t2. When  $\overline{WR}$  is deasserted in t3, the external data has been latched inside the external device. When  $\overline{WR}$  is asserted, it qualifies the A0-A15 and  $PS/\overline{DS}$ pins.  $\overline{WR}$  can be connected directly to the WE pin of a static RAM. WR is threestated during hardware reset or when the DSP is not bus master.

- RD (Read Enable) three-state, active low output. This output is asserted during external memory read cycles. When  $\overline{\text{RD}}$  is asserted in late t0/early t1, the data bus pins D0-D15 become inputs and an external device is enabled onto the data bus. When  $\overline{RD}$  is deasserted in t3, the external data is latched inside the DSP. When  $\overline{RD}$  is asserted, it qualifies the A0-A15 and  $PS/\overline{DS}$  pins. RD can be connected directly to the  $\overline{OE}$  pin of a static RAM or ROM.  $\overline{RD}$  is three-stated during hardware reset or when the DSP is not bus master.

- BS (Bus Strobe) three-state, active low output. Asserted at the start of a bus cycle (during t0) and deasserted at the end of the bus cycle (during t2). This pin provides an "early bus start" signal which can be used as address latch and as an "early bus end" signal which can be used by an external bus controller. BS is three-stated during hardware reset.

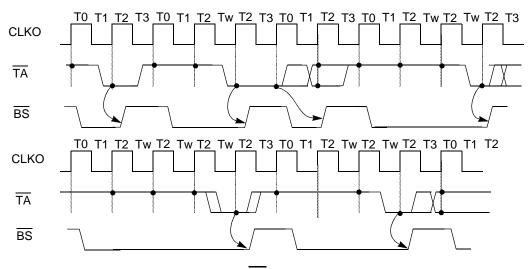

TA (Transfer Acknowledge) — active low input. If there is no external bus activity, the  $\overline{TA}$  input is ignored by the DSP. When there is external bus cycle activity, TA can be used to insert wait states in the external bus cycle.  $\overline{TA}$  is sampled on the leading edge of the clock. Any number of wait states from 1 to infinity may be inserted by using  $\overline{TA}$ . If  $\overline{TA}$  is sampled high on the leading edge of the clock beginning the bus cycle, the bus cycle will end 2T after the TA has been sampled low on a leading edge of the clock; if the Bus Control Register (BCR) value does not program more wait states. The number of wait states is determined by the TA input or by the Bus Control Register (BCR), whichever is longer.  $\overline{TA}$  is still sampled during the leading edge of the clock when wait states are controlled by the BCR value. In that case, TA will have to be sampled low during the leading edge of the last period of the bus cycle programmed by the BCR (2T before the end of the bus cycle programmed by the BCR) in order not to add any wait states. TA should always be deasserted during

t3 to be sampled high by the leading edge of T0. If  $\overline{TA}$  is sampled low (asserted) at the leading edge of the t0 beginning the bus cycle, and if no wait states are specified in the BCR register, zero wait states will be inserted in the external bus cycle, regardless the status of  $\overline{TA}$  during the leading edge of T2.

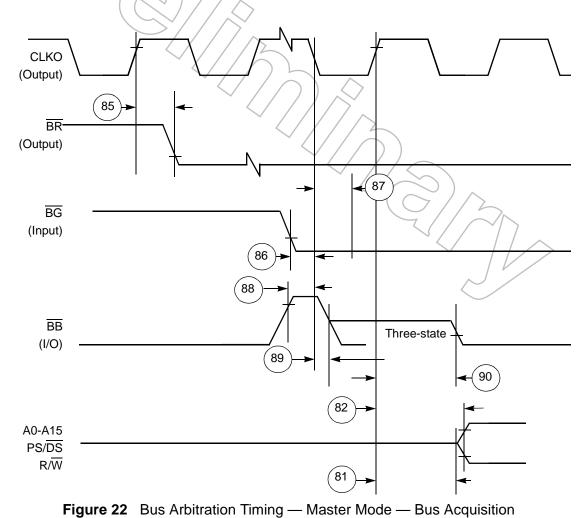

BR (Bus Request) — active low output when in master mode, active low input when in slave mode. After poweron reset, this pin is an input (slave mode). In this mode, the bus request BR allows another device such as a processor or DMA controller to become the master of the DSP external data bus D0-D15 and external address bus A0-A15. The DSP asserts  $\overline{BG}$  a few T states after the  $\overline{BR}$  input is asserted. The DSP bus controller releases control of the external data bus D0-D15, address bus A0-A15 and bus control pins  $PS/\overline{DS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , and  $R/\overline{W}$  at the earliest time possible consistent with proper synchronization. These pins are then placed in the high impedance state and

Figure 3 TA Controlled Accesses

the  $\overline{\text{BB}}$  pin is deasserted. The DSP continues executing instructions only if internal program and data memory resources are accessed. If the DSP requests the external bus while  $\overline{\text{BR}}$  input pin is asserted, the DSP bus controller inserts wait states until the external bus becomes available ( $\overline{\text{BR}}$  and  $\overline{\text{BB}}$  deasserted). Note that interrupts are not serviced when a DSP instruction is waiting for the bus controller. Note also that  $\overline{\text{BR}}$  is prevented from interrupting the execution of a read/ modify/write instruction.

If the master bit in the OMR register is set, this pin becomes an output (Master Mode). In this mode, the DSP is not the external bus master and has to assert  $\overline{BR}$  to request the bus mastership. The DSP bus controller will insert wait states until  $\overline{BG}$  input is asserted and will then begin normal bus accesses after the rising of the clock which sampled  $\overline{BB}$  high. The  $\overline{BR}$  output signal will remain asserted until the DSP no longer needs the bus. In this mode, the Request Hold bit (RH) of the Bus Control Register (BCR) allows  $\overline{BR}$  to be asserted under software control.

During external accesses caused by an instruction executed out of external program memory, BR remains asserted low for consecutive external X memory accesses and continues toggling for consecutive external P memory accesses unless the Request Hold bit (RH) is set inside the Bus Control Register (BCR).

In the master mode,  $\overline{BR}$  can also be used for non arbitration purpose: if  $\overline{BG}$ is always asserted,  $\overline{BR}$  is asserted in t0 of every external bus access. It can then be used as a chip select to turn a external memory device off and on between internal and external bus accesses.  $\overline{BR}$  timing is in that case similar to A0-A15,  $R/\overline{W}$  and  $PS/\overline{DS}$ ; it is asserted and deasserted during t0.

BG (Bus Grant) - active low input when in master mode, active low output when in slave mode. Output after power on reset if the slave is selected, this pin is asserted to acknowledge an external bus request. It indicates that the DSP will release control of the external address bus A0-A15, data bus D0-D15 and bus control pins when  $\overline{BB}$ is deasserted. The  $\overline{BG}$  output is asserted in response to a  $\overline{BR}$  input. When the  $\overline{BG}$  output is asserted and  $\overline{BB}$  is deasserted, the external address bus A0-A15, data bus D0-D15 and bus control pins are in the high impedance state.  $\overline{BG}$  assertion may occur in the middle of an instruction which requires more than one external bus cycle for execution. Note that  $\overline{BG}$  assertion will not occur during indivisible read-modify-write instructions (BFSET, BFCLR, BFCHG). When  $\overline{BR}$  is deasserted, the  $\overline{BG}$  output is deasserted and the DSP regains control of the external address bus, data bus, and bus control pins when the  $\overline{BB}$ pin is sampled high.

> This pin becomes an input if the master bit in the OMR register is set (Master Mode). It is asserted by an external processor when the DSP may become the bus master. The DSP can start normal external memory access after the  $\overline{BB}$  pin has been deasserted by the previous bus master. When  $\overline{BG}$  is deasserted, the DSP will release the bus as soon as the current transfer is completed. The state of  $\overline{BG}$  may be tested by testing the BS bit in the Bus Control Register.  $\overline{BG}$  is ignored during hardware reset.

Bus Control Interrupt and Mode Control

> **BB** (Bus Busy) — active low input when not bus master, active low output when bus master. This pin is asserted by the DSP when it becomes the bus master and it performs an external access. It is deasserted when the DSP releases bus mastership. BB becomes an input when the DSP is no longer the bus master.

## **Interrupt and Mode Control**

MODA/IRQA (Mode Select A/External Interrupt Request A) — input. This input has two functions:

- to select the initial chip operating mode and,

- to allow an external device to request a DSP interrupt after internal synchronization.

MODA is read and internally latched in the DSP when the processor exits the reset state. MODA and MODB select the initial chip operating mode. Several clock cycles after leaving the reset state, the MODA pin changes to the external interrupt request IRQA. The chip operating mode can be changed by software after reset.

The  $\overline{IRQA}$  input is a synchronized external interrupt request which indicates that an external device is requesting service. It may be programmed to be level sensitive or negative edge triggered. If level sensitive triggering is selected, an external pull up resistor is required for wired-OR operation. If the processor is in the stop standby state and  $\overline{IRQA}$  is asserted, the processor will exit the stop state. MODB/IRQB (Mode Select B/External Interrupt Request B) — input. This input has two functions:

- to select the initial chip operating mode and,

- to allow an external device to request a DSP interrupt after internal synchronization.

MODB is read and internally latched in the DSP when the processor exits the reset state. MODA and MODB select the initial chip operating mode. Several clock cycles after leaving the reset state, the MODB pin changes to the external interrupt request IRQB. After reset, the chip operating mode can be changed by software.

The IRQB input is an external interrupt request which indicates that an external device is requesting service. It may be programmed to be level sensitive or negative edge triggered. If level sensitive triggering is selected, an external pull up resistor is required for wired-OR operation.

- **MODC** (Mode Select C) input. This input selects the initial bus operating mode. When tied high, the external bus is programmed in the master mode ( $\overline{BR}$  output and  $\overline{BG}$  input) and when tied low the bus is programmed in the slave mode ( $\overline{BR}$  input and  $\overline{BG}$  output). MODC is read and internally latched in the DSP when the processor exits the reset state. After  $\overline{RESET}$ , the bus operating mode can be changed by software by writing the MC bit of the OMR register.

- **RESET** (Reset) input. This input is a direct hardware reset of the processor. When RESET is asserted, the DSP is initialized and placed in the reset state. A Schmitt

Interrupt and Mode Control Host Interface

trigger input is used for noise immunity. When the reset pin is deasserted, the initial chip operating mode is latched from the MODA and MODB pins, and the initial bus operating mode is latched from the MODC pin. The internal reset signal should be deasserted synchronized with the internal clocks.

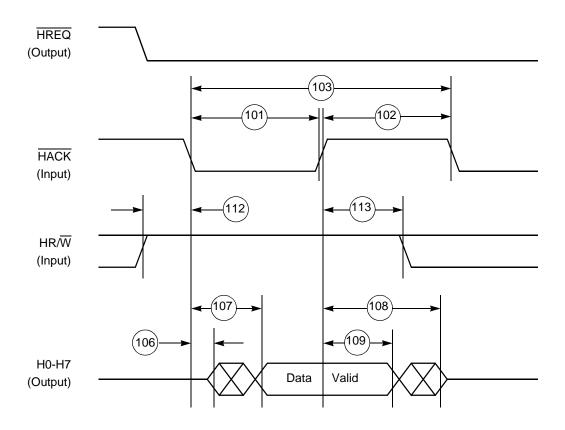

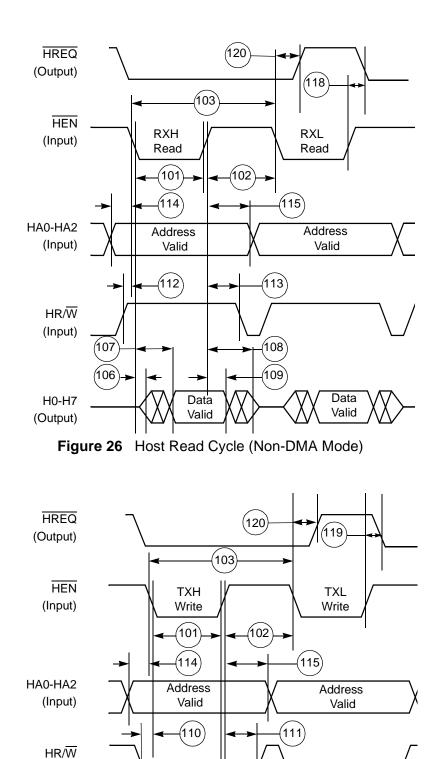

## **Host Interface**

- H0-H7 (Host Data Bus) bidirectional. This bidirectional data bus is used to transfer data between the host processor and the DSP. This bus is an input unless enabled by a host processor read. H0-H7 may be programmed as Port B general purpose parallel I/O pins called PB0-PB7 when the Host Interface (HI) is not being used.

- HA0-HA2 (Host Address 0-2) input\*. These inputs provide the address selection for each HI register and are stable when HEN is asserted. HA0-HA2 may be programmed as Port B general purpose parallel I/O pins called PB8-PB10 when the HI is not being used.

- HR/W (Host Read/Write) input\*. This input selects the direction of data transfer for each host processor access. If HR/W is high and HEN is asserted, H0-H7 are outputs and DSP data is transferred to the host processor. If HR/W is low and HEN is asserted, H0-H7 are inputs and host data is transferred to the DSP. When HEN is asserted, HR/W is stable. HR/W may be programmed as a general purpose I/O pin called PB11 when the HI is not being used.

- **HEN** (Host Enable) input\*. This input enables a data transfer on the host data bus. When HEN is asserted and HR/ $\overline{W}$  is high, H0-H7 becomes an output and DSP data may be latched by the host processor. When HEN is asserted and HR/ $\overline{W}$  is low, H0-H7 is an input and host data is latched inside the DSP when HEN is deasserted. Normally a chip select signal derived from host address decoding and an enable clock is connected to the Host Enable. HEN may be programmed as a general purpose I/O pin called PB12 when the HI is not being used.

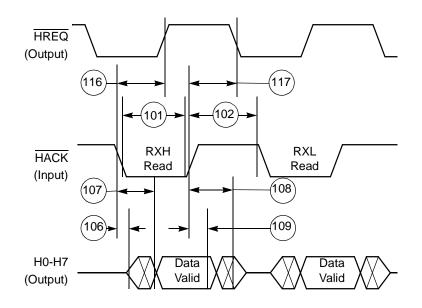

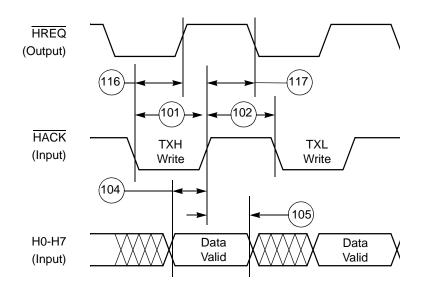

- HREQ (Host Request) output\*. This opendrain output signal is used by the HI to request service from the host processor. HREQ may be connected to an interrupt request pin of a host processor, a transfer request of a DMA controller, or a control input of external circuitry. HREQ is asserted when an enabled request occurs in the HI. HREQ is deasserted when the enabled request is cleared or masked, DMA HACK is asserted, or the DSP is reset. HREQ may be programmed as a general purpose I/O pin (not open-drain) called PB13 when the HI is not being used.

- HACK (Host Acknowledge) input\*. This input has two functions:

- to provide a host acknowledge signal for DMA transfers and,

- to control handshaking and to provide a host interrupt acknowledge compatible with MC68000 family processors.

If programmed as a host acknowledge signal,  $\overline{\text{HACK}}$  may be used as a data strobe for HI DMA data transfers. If programmed as an MC68000 host interrupt

Downloaded from Elcodis.com electronic components distributor

<sup>\*</sup> These pins can be bidirectional when programmed as general purpose I/O.

acknowledge, HACK enables the HI Interrupt Vector Register (IVR) onto the host data bus H0-H7 if the Host Request HREQ output is asserted. In this case, all other HI control pins are ignored and the HI state is not affected. HACK may be programmed as a general purpose I/O pin called PB14 when the HI is not being used.

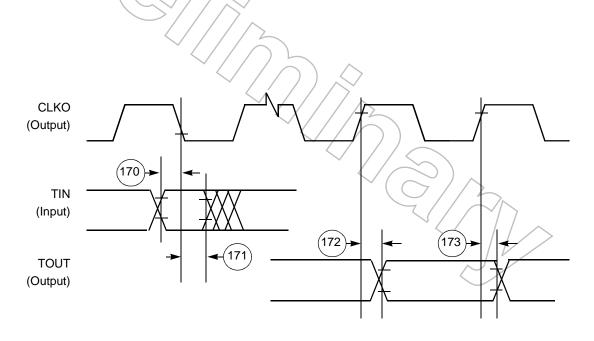

## **16-bit Timer**

- TIN (Timer Input) input\*. This input receives external pulses to be counted by the on-chip 16-bit timer when external clocking is selected. The pulses are internally synchronized to the DSP core internal clock. TIN may be programmed as a general purpose I/O pin called PC10 when the external event function is not being used.

- **TOUT (Timer Output) output\*.** This output generates pulses or toggles on a timer overflow event or a compare event. TOUT may be programmed as a general purpose I/O pin called PC11 when disabled by the timer out enable bits (TO2-TO0).

## Synchronous Serial Interfaces (SSI)

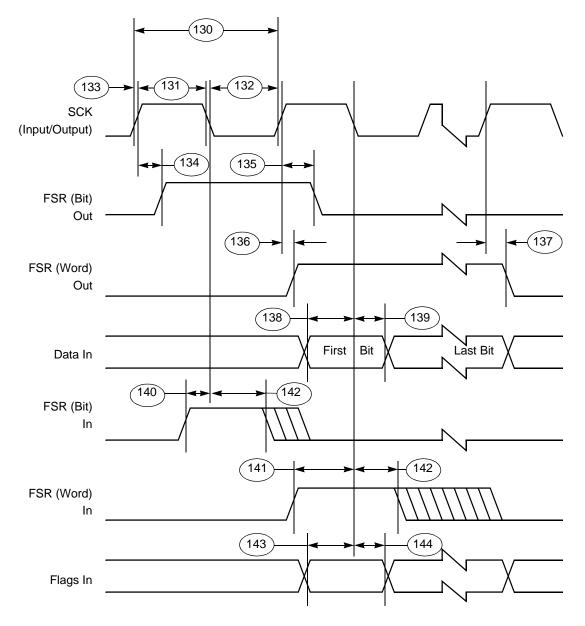

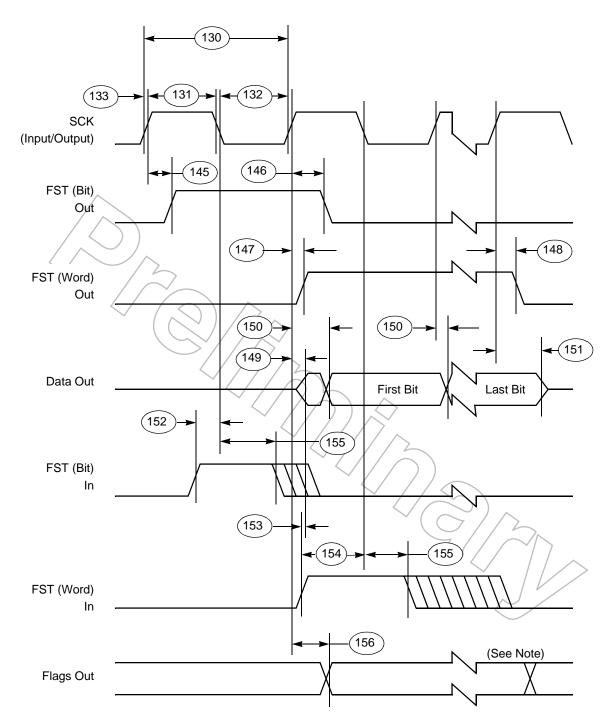

STD0-1 (SSI0-1 Transmit Data) — output\*. These output pins transmit serial data from the SSI0-1 Transmit Shift Register. STD0 and STD1 may be programmed as a general purpose I/O pin called PC0 and PC5, respectively, when the STD function is not being used.

- SRD0-1 (SSI0-1 Receive Data) input\*. These input pins receive serial data and transfer the data to the SSI0-1 Receive Shift Register. SRD0 and SRD1 may be programmed as a general purpose I/O pin called PC1 and PC6, respectively, when the SRD function is not being used.

- SCK0-1 (SSI0-1 Serial Clock) bidirectional. These bidirectional pins provide the serial bit rate clock for the SSI0-1 interface. SCK0 and SCK1 may be programmed as a general purpose I/O pin called PC2 and PC7, respectively, when the SSI0-1 interfaces are not being used.

- SC10-11 (SSI0-1 Serial Control 1) bidirectional. These bidirectional pins are used by the SSI0-1 serial interface as frame sync I/O or flag I/O. SC10 and SC11 may be programmed as a general purpose I/O pin called PC3 and PC8, respectively, when the SSI0-1 are not using these pins.

- SC00-01 (SSI0-1 Serial Control 0) bidirectional. These bidirectional pins are used by the SSI0-1 serial interface as frame sync I/O or flag I/O. SC00 and SC01 may be programmed as a general purpose I/O pin called PC4 and PC9, respectively, when the SSI0-1 are not using these pins.

\* These pins can be bidirectional when programmed as general purpose I/O.

For More Information On This Product.

12

MOTOROLA

## On-Chip Emulation (OnCE<sup>™</sup> Port)

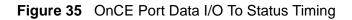

DSI/OS0 (Debug Serial Input/Chip Status 0) bidirectional. The DSI/OS0 pin, when an input, is the pin through which serial data or commands are provided to the OnCE port controller. The data received on the DSI pin will be recognized only when the DSP has entered the debug mode of operation. Data must have valid TTL logic levels before the serial clock falling edge. Data is always shifted into the OnCE serial port most significant bit (MSB) first. When the DSP is not in the debug mode, the DSI/ OS0 pin provides information about the chip status if it is an output and used in conjunction with the OS1 pin.

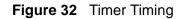

### DSCK/OS1 (Debug Serial Clock/Chip Status 1)

— **bidirectional.** The DSCK/OS1 pin, when an input, is the pin through which the serial clock is supplied to the OnCE port. The serial clock provides pulses required to shift data into and out of the OnCE serial port. Data is clocked into the OnCE port on the falling edge and is clocked out of the OnCE serial port on the rising edge. If the DSCK/OS1 pin is an output and used in conjunction with the OS0 pin, it provides information about the chip status when the DSP is not in the debug mode.

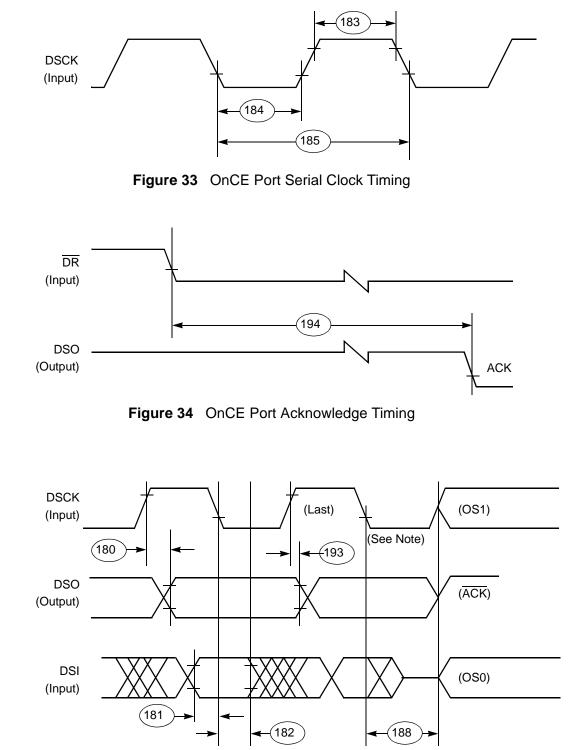

**DSO (Debug Serial)** — **output.** The debug serial output provides the data contained in one of the OnCE port controller registers as specified by the last command received from the command controller. When idle, this pin is high. When the requested data is available, the DSO line will be asserted (negative true logic) for four T cycles (one instruction

> DSP56156 Data Sheet For More Information On This Product,

Go to: www.freescale.com

cycle) to indicate that the serial shift register is ready to receive clocks in order to deliver the data. When the chip enters the debug mode due to an external debug request ( $\overline{DR}$ ), an internal software debug request ( $\overline{DEBUG}$ ), a hardware breakpoint occurrence or a trace/step occurrence, this line will be asserted for three T cycles to indicate that the chip has entered the debug mode and is waiting for commands. Data is always shifted out the OnCE serial port with the most significant bit first.

DR (Debug Request) — input. The debug request input provides a means of entering the debug mode of operation. This pin, when asserted, will cause the DSP to finish the current instruction being executed, enter the debug mode, and wait for commands to be entered from the debug serial input line.

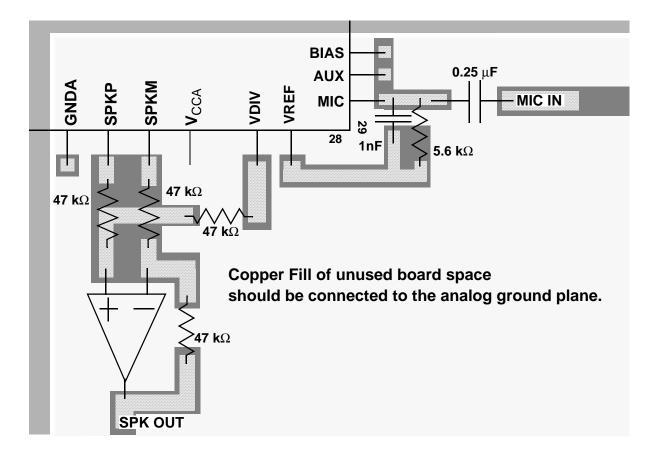

## **On-Chip Codec**

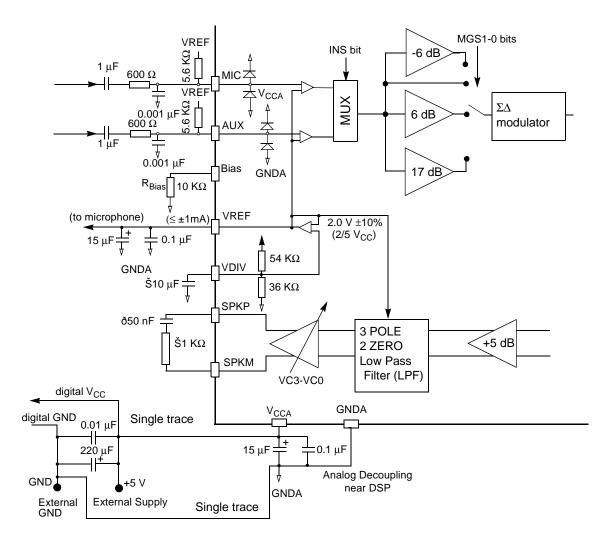

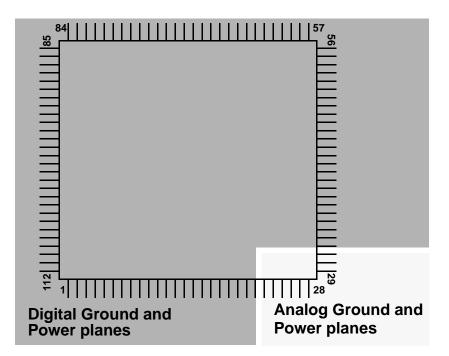

- AUX (Auxiliary) input. This pin is selected as the analog input to the A/D converter when the INS bit is set in the codec control register COCR. This pin should be left floating when the codec is not used.

- BIAS (Bias current) input. This input is used to determine the bias current for the analog circuitry. Connecting a resistor between BIAS and GNDA will program the current bias generator. This pin should be left floating when the codec is not used.

- MIC (Microphone) input. This pin is selected as the analog input to the A/D converter when the INS bit is cleared in

### **Freescale Semiconductor, Inc.**

the codec control register COCR. This pin should be left floating when the codec is not used.

- **SPKP (Speaker Plus) output**. This pin is the positive analog output from the onchip D/A converter. This pin should be left floating when the codec is not used.

- **SPKM (Speaker Minus) output**. This pin is the negative analog output from the on-chip D/A converter. This pin should be left floating when the codec is not used.

- **VREF** (Voltage Reference) output. This pin is the op-amp buffer output in the reference voltage generator. It has a value of  $(^{2}/_{5})V_{CCA}$ . This pin should always be connected to the GNDA through two capacitors, even when the codec is not used.

- **VDIV** (Voltage Division) output. This output pin is also the output to the onchip op-amp buffer in the reference voltage generator. It is connected to a resistor divider network located within the codec block which provides a voltage equal to  $(^2/_5)V_{CCA}$ . This pin should be connected to the GND via a capacitor when the codec is used and should be left floating when the codec is not used.

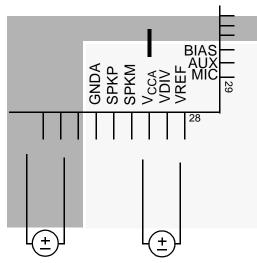

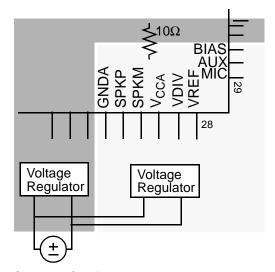

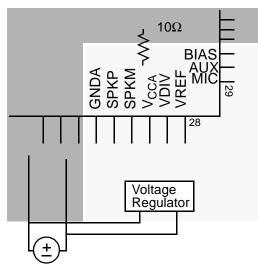

## Power, Ground, and Clock

- V<sub>CC</sub> (Power) Power pins

- **GND** (Ground) Ground pins

- V<sub>CCS</sub> (Synthesizer Power) This pin supplies a quiet power source to the Phase-Locked Loop (PLL) to provide greater frequency stability.

- **GNDS (Synthesizer Ground)** This pin supplies a quiet ground source to the PLL to provide greater frequency stability.

- $V_{CCA}$  (Analog Power) This pin is the positive analog supply input. It should be connected to  $V_{CC}$  when the codec is not used.

- **GNDA** (Analog Ground) This pin is the analog ground return. It should be connected to digital GND when the codec is not used.

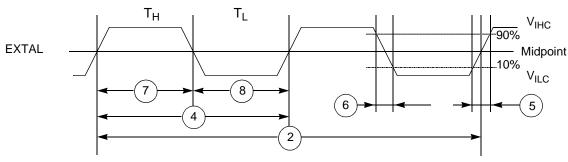

- **EXTAL (External Clock) input.** This input should be driven by an external clock or by an external oscillator. After being squared, the input frequency can be used as the DSP core internal clock. In that case, it is divided by two to produce a four phase instruction cycle clock, the minimum instruction time being two input clock periods. This input frequency is also used, after division, as input clock for the on-chip codec and the onchip PLL.

- CLKO (Clock Output) output. This pin outputs a buffered clock signal. By programming two bits (CS1-CS0) inside the PLL Control Register (PLCR), the user can select between outputting a squared version of the signal applied to EXTAL, a squared version of the signal applied to EXTAL divided by 2, and a delayed version of the DSP core master clock. The clock frequency on this pin can be disabled by setting the Clockout Disable bit (CD; bit 7) of the Operating Mode Register (OMR). When disabled, the pin can be left floating.

- **SXFC (External Filter Capacitor)** This pin adds an external capacitor to the PLL filter circuit. A low leakage capacitor should be connected between and located very close to SXFC and V<sub>CCS</sub>.

Downloaded from Elcodis.com electronic components distributor

14

## **Electrical Characteristics and Timing**

**CAUTION:** Exceeding maximum electrical ratings will permanently damage or disable the chip, or impair the chip's long term reliability.

The DSP56156 is fabricated in high density HCMOS with TTL compatible inputs and CMOS compatible outputs.

| Rating                                           | Symbol           | Value                              | Unit |

|--------------------------------------------------|------------------|------------------------------------|------|

| Supply Voltage                                   | V <sub>CC</sub>  | -0.3 to +7.0                       | V    |

| All Input Voltages                               | V <sub>IN</sub>  | GND - 0.5 to V <sub>CC</sub> + 0.5 | V    |

| Current Drain per Pin excluding $V_{CC}$ and GND | I                | 10                                 | mA   |

| Storage Temperature                              | T <sub>stg</sub> | -55 to +150                        | °C   |

Table 4 Maximum Electrical Ratings (GND = 0 Vdc)

|     | Voltage |     | emperature<br>(°C) |

|-----|---------|-----|--------------------|

| Min | Мах     | Min | Max                |

| 4.5 | 5.5     | -40 | 115                |

|     |         |     |                    |

Table 5 Operating Conditions

**Table 6** Thermal Characteristics of CQFP and TQFP Packages

| Thermal Resistance           | Symbol        | Va   | Rating |        |  |

|------------------------------|---------------|------|--------|--------|--|

| Characteristics              | Symbol        | CQFP | TQFP   | Rating |  |

| Junction to Ambient          | $\Theta_{JA}$ | 40   | 49     | °C/W   |  |

| Junction to Case (estimated) | $\Theta_{JC}$ | 7    | 8      | °C/W   |  |

**NOTE:** This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or V<sub>CC</sub>).

MOTOROLA

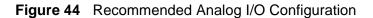

## **Analog I/O Characteristics**

$(V_{CCA} = 5.0 \text{ V dc} \pm 10\%, T_J = -40^{\circ} \text{ to } +125^{\circ}\text{C})$

The analog I/O characteristics of this device are listed in Table 7. For additional information regarding the use of analog signals, see "Design Considerations" at the end of this document.

| Characteristic                                                                                                                                                                                                                        | Min                   | Тур                       | Max                          | Unit                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|------------------------------|------------------------|

| Input Impedance on MIC and AUX (See Note 1)                                                                                                                                                                                           | 46                    | 78                        | 1400                         | kΩ                     |

| Input Capacitance on MIC and AUX                                                                                                                                                                                                      | _                     | _                         | 10                           | pF                     |

| Peak Input Voltage on the MIC/AUX Input for Full Scale           Linearity (0.14 dBm0):         6 dB - MGS1 - 0 = 00           (See Note 2)         0 dB - MGS1 - 0 = 01           6 dB - MGS1 - 0 = 10         17 dB - MGS1 - 0 = 11 | <br>                  |                           | 1.414<br>0.707<br>354<br>100 | Vp<br>Vp<br>mVp<br>mVp |

| Internal Input Gain Variation;<br>G = -6 dB, 0 dB, 6 dB or 17 dB<br>( $\pm 0.83$ dB variation due to 10% variation on V <sub>CC</sub> ):                                                                                              | G - 0.83              | G                         | G + 0.83                     | dB                     |

| VREF Output Voltage                                                                                                                                                                                                                   | 1.8                   | 2                         | 2.2                          | V                      |

| VREF Output Current                                                                                                                                                                                                                   | ////                  | 1                         | ±1                           | mA                     |

| DC Offset Between SPKP and SPKM                                                                                                                                                                                                       | $\overline{\sqrt{4}}$ | 1                         | 100                          | mV                     |

| Allowable Differential Load Capacitance on SPKP and SPKM (with 1 k $\Omega$ in series)                                                                                                                                                | 0                     | $\langle \rangle \leq$    | 0.05                         | μF                     |

| Allowable Single-ended Load Capacitance on SPKP or SPKM (with 0.5 $k\Omega$ in series)                                                                                                                                                | 0<br>(See Note 3)     | $\left( \bigcirc \right)$ | 100<br>0.1                   | μF                     |

| Maximum Single-ended Signal Output Level                                                                                                                                                                                              | —                     | _                         | /1 /                         | Vp                     |

| Maximum Differential Signal Output Level                                                                                                                                                                                              | —                     | _                         | 2                            | Ур                     |

| Single-ended Load Resistance                                                                                                                                                                                                          | 500                   | _                         | $\sum$                       | Ω                      |

| Differential Load Resistance                                                                                                                                                                                                          | 1                     | _                         | _                            | kΩ                     |

| Resistance BIAS                                                                                                                                                                                                                       | _                     | 10<br>(See<br>Note 4)     | —                            | kΩ                     |

| Internal Output Volume Control Variation<br>VC = -20, -15, -10, -5, 0, 6, 12, 18, 24, 30, 35 dB<br>( $\pm$ 0.83 dB variation due to 10% variation on V <sub>CC</sub> )                                                                | VC - 0.83             | VC                        | VC + 0.83                    | dB                     |

Table 7

Analog I/O Characteristics

NOTES: 1. Minimum value reached for a Codec clock of 3 MHz, typical for 2 MHz and maximum for 100 kHz 2. 0 dBm0 corresponds to 3.14 dB below the input saturation level

3. AC coupling is necessary in single-ended mode when the load resistor is not tied to VREF

4. ± 10%

A/D and D/A Performance

## A/D and D/A Performance

$(V_{CCA} = 5.0 \text{ V dc} \pm 10\%, \text{ T}_{J} = -40^{\circ} \text{ to} + 125^{\circ}\text{C})$

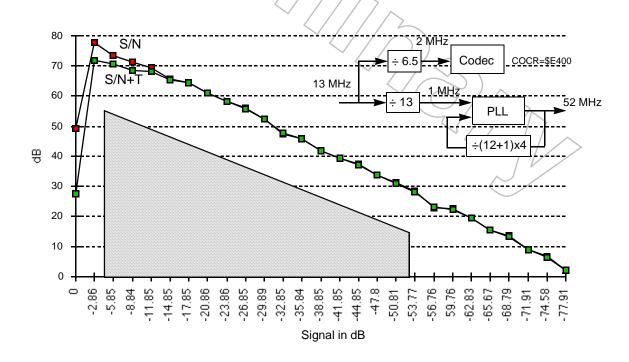

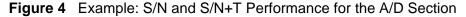

The A/D and D/A performance of the codec section are given in Table 8 with an example presented in Figure 4.

| Characteristic                                                          | Level                  | Min | <b>Typ</b><br>(See Note 1) | Max | Unit |

|-------------------------------------------------------------------------|------------------------|-----|----------------------------|-----|------|

| Analog to Digital Section Signal to Noise plus Distortion Ratio (S/N+T) | 0 dBm0<br>(See Note 2) | 55  | 65                         | —   | dB   |

|                                                                         | -50 dBm0               | 15  | 20                         |     | dB   |

| Digital to Analog Section Signal to Noise                               | 0 dB                   | 55  | 65                         |     | dB   |

| plus Distortion Ratio (S/N+T)                                           | -50 dB                 | 15  | 20                         |     | dB   |

- NOTES: 1. 0 dB gain on the A/D and D/A; Codec clock at 1.538 MHz with 128 decimation/interpolation ratio and tested at 1502 Hz

- 2. 0 dBm0 corresponds to -3.14 dB below the input saturation level

MOTOROLA

Downloaded from Elcodis.com electronic components distributor

Other On-Chip Codec Characteristics

## **Other On-Chip Codec Characteristics**

(V\_{CCA} = 5.0 V dc  $\pm$  10%, T\_J = -40° to +125°C, C\_L = 50 pF + 1 TTL Load)

The analog I/O characteristics of this device are shown in Table 9.

| Characteristic          | Min | Тур   | Max   | Unit |

|-------------------------|-----|-------|-------|------|

| Codec Master Clock      | 0.1 | 2.048 | 3     | MHz  |

| Codec Sampling Rate     | 78  | 16000 | 37000 | Hz   |

| A/D Section Group Delay |     | —     | 0.2   | msec |

| D/A Section Group Delay | —   | —     | 0.2   | msec |

|                         |     |       | 07/   | Z    |

Table 9 Analog I/O Characteristics of On-Chip Codec

18

## **DC Electrical Characteristics**

(GND = 0 V dc)

Semiconductor, Inc.

Freescale

(V<sub>CC</sub> = 5.0 V dc  $\pm$  10%, T<sub>J</sub> = -40° to +125°C, C<sub>L</sub> = 50 pF + 1 TTL Load)

The DC electrical characteristics of this device are shown in Table 10.

| Characteristic                                                                                                                                            | Symbol           | Min                         | Тур           | Max                                          | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------|---------------|----------------------------------------------|----------|

| Input High Voltage<br>except EXTAL, RESET, MODA, MODB, MODC                                                                                               | V <sub>IH</sub>  | 2.0                         | _             | V <sub>CC</sub>                              | V        |

| Input Low Voltage<br>except EXTAL, MODA, MODB, MODC                                                                                                       | V <sub>IL</sub>  | -0.5                        | —             | 0.8                                          | V        |

| Input High Voltage<br>EXTAL DC coupled<br>EXTAL AC coupled (See Note 1)                                                                                   | V <sub>IHC</sub> | 70% of V <sub>CC</sub><br>1 | _             | V <sub>CC</sub><br>V <sub>CC</sub>           | V        |

| Input Low Voltage<br>EXTAL DC coupled<br>EXTAL AC coupled (See Note 1)                                                                                    | VILC             | -0.5<br>-0.5                |               | 20% of V <sub>CC</sub><br>V <sub>CC</sub> -1 | V        |

| Input High Voltage RESET                                                                                                                                  | Vihr             | 2.5                         | _             | V <sub>CC</sub>                              | V        |

| Input High Voltage MODA, MODB, MODC                                                                                                                       | Ville            | 3.5                         | —             | V <sub>CC</sub>                              | V        |

| Input Low Voltage MODA, MODB, MODC                                                                                                                        | VILM             | -0,5                        | _             | 2.0                                          | V        |

| Input Leakage Current<br>RESET, MODA, MODB, MODC, TA, DR, BR                                                                                              | I <sub>IN</sub>  | -100<br>-1                  | $\mathcal{D}$ | 100                                          | μA<br>μA |

| Three-State (Off-State) Input Current<br>(@2.4 V/0.5 V)                                                                                                   | TSI              | -10                         | £/            | 10                                           | μA       |

| Output High Voltage (I <sub>OH</sub> = -10 µA)                                                                                                            | V <sub>OHC</sub> | V <sub>CC</sub> -0.1        | _             |                                              | V        |

| Output High Voltage (I <sub>OH</sub> = -0.4 mA)                                                                                                           | V <sub>OH</sub>  | 2.4                         | _ <           | <u> </u>                                     | V        |

| Output Low Voltage (I <sub>OL</sub> = 10 μA)                                                                                                              | V <sub>OLC</sub> | —                           | —             | 0.1                                          | V        |

| Output Low Voltage ( $I_{OL}$ = 3.2 mA<br><u>R/W</u> I <sub>OL</sub> = 1.6 mA; Open Drain<br>HREQ I <sub>OL</sub> = 6.7 mA, TXD I <sub>OL</sub> = 6.7 mA) | V <sub>OL</sub>  |                             | _             | 0.4                                          | V        |

| Input Capacitance (See Note 2)                                                                                                                            | C <sub>IN</sub>  | _                           | 10            | —                                            | pF       |

Table 10 DC Electrical Characteristics

**NOTES:** 1. When EXTAL is AC coupled,  $V_{IHC} - V_{ILC} \\ \check{S} \\ 1 \\ V \\ must be true.$

2. Input capacitance is periodically sampled and not 100% tested in production.

MOTOROLA

#### DSP56156 Data Sheet For More Information On This Product, Go to: www.freescale.com

**Clock Operation Timing**

# **AC Electrical Characteristics**

(GND = 0 V dc)

The timing waveforms in the **AC Electrical Characteristics** are tested with a  $V_{IL}$  maximum of 0.5 V and a  $V_{IH}$  minimum of 2.4 V for all pins, except EXTAL, RESET, MODA, MODB and MODC. These five pins are tested using the input levels set forth in the **DC Electrical Characteristics**. AC timing specifications which are referenced to a device input signal are measured in production with respect to the 50% point of the respective input signal's transition. The DSP56156 output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at 0.8 V and 2.0 V respectively.

## **Clock Operation Timing**

The system clock to the DSP56156 must be externally supplied to EXTAL as illustrated in Figure 6.

| Num | Characteristics                                              | Sym              | 40 MHz       |      | 50 MHz |       | 60 MHz |     | Unit |

|-----|--------------------------------------------------------------|------------------|--------------|------|--------|-------|--------|-----|------|

| Num | Characteristics                                              |                  | Min          | Max  | Min    | Мах   | Min    | Max | onic |

| 1   | Frequency of Operation (EXTAL)                               | f                | <u>/</u> 0 / | 40   | 0      | 50    | 0      | 60  | MHz  |

| 2   | Instruction Cycle Time = $2T_{C}$                            | I <sub>CYC</sub> | 50           | /× / | 40     | ×     | 33     | ×   | ns   |

| 3   | Wait State Time = $T_C = 2T$                                 | _                | 25           | ×/   | 20     | ×     | 16.6   | ×   | ns   |

| 4   | EXTAL Cycle Period                                           | Т <sub>С</sub>   | 25           | ×    | 20     | / * < | 16.6   | ×   | ns   |

| 5   | EXTAL Rise Time (See Note 1)                                 |                  | —            | 4    | _ <    | 3     | (-C)   | 3   | ns   |

| 6   | EXTAL Fall Time (See Note 1)                                 |                  |              | 4    |        | 3     | '      | 3   | ns   |

| 7   | EXTAL Width High<br>48-52% duty cycle<br>(See Notes 2, 3, 4) | Т <sub>Н</sub>   | 12           | ×    | 9.6    | ×     | 8      | ×   | ns   |

| 8   | EXTAL Width Low<br>48%-52% duty cycle<br>(See Notes 2, 3, 4) | ΤL               | 12           | ×    | 9.6    | ×     | 8      | ×   | ns   |

| / | Table | 11 6 | llock | Operatio | n Ti                                    | mina |

|---|-------|------|-------|----------|-----------------------------------------|------|

| 1 | Idule | n /c | NOUR  | Operatic | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ming |

- **NOTES:** 1. Rise and fall time may be relaxed to 12 ns maximum if the EXTAL input frequency is less than or equal to 20 MHz. If the EXTAL input frequency is between 20 MHz and 40 MHz, rise and fall time should meet the specified values in the 40 MHz column (4 ns maximum).

- 2. The duty cycle may be relaxed to 43-57% if the EXTAL input frequency is less than or equal to 20 MHz. If the EXTAL input frequency is between 20 MHz and 40 MHz, the duty cycle should be such that  $T_H$  and  $T_L$  meet the specified values in the 40 MHz column (12 ns minimum).

- 3. T = I<sub>CYC</sub> / 4 is used in the electrical characteristics. The exact length of each T is affected by the duty cycle of the external clock input.

- 4. Duty cycles and EXTAL widths are measured at the EXTAL input signal midpoint when AC coupled and at  $V_{CC}/2$  when not AC coupled.

Clock Operation Timing PLL

Figure 5 External Clock Timing

## **Other Clock and PLL Operation Timing**

Clock and PLL timings are listed in Table 12 and the clocking configurations are illustrated in Figure 6,

| Table 12 | Clock and | I PLL | Timing |

|----------|-----------|-------|--------|

|----------|-----------|-------|--------|

| Characteristics                          | Min | Мах                      | Unit |

|------------------------------------------|-----|--------------------------|------|

| PLL Output frequency                     | 10  | Max Fosc<br>(See Note 1) | MHz  |

| EXTAL Input Clock Amplitude (See Note 2) | 1   | V <sub>CC</sub>          | Vpp  |

- NOTES: 1. Maximum DSP operating frequency. See Table 11.

- An AC coupling capacitor is required on EXTAL if the levels are out of the normal CMOS level range (V<sub>ILC</sub>>20% of V<sub>CC</sub> or V<sub>IHC</sub><70% of V<sub>CC</sub>).

MOTOROLA

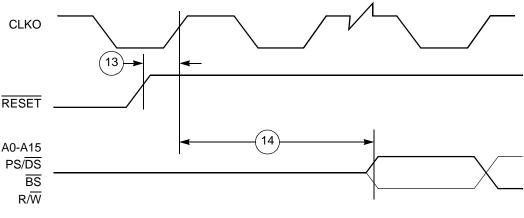

Reset, Stop, Wait, Mode Select, and Interrupt Timing

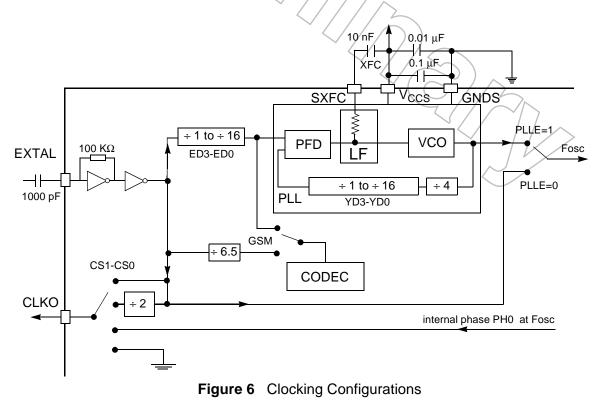

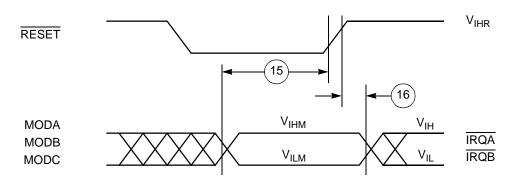

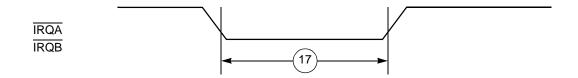

## Reset, Stop, Wait, Mode Select, and Interrupt Timing

$(V_{CC} = 5.0 \text{ V dc} \pm 10\%, T_J = -40^{\circ} \text{ to} + 125^{\circ}\text{C}, C_L = 50 \text{ pF} + 1 \text{ TTL Load})$

$cyc = Clock cycle = \frac{1}{2}$  instruction cycle = 2 T cycles

ws = Number of wait states programmed into external bus access using BCR (WS = 0 - 31)

| Nerrow | Characteristics                                                                                                                                                                                        | 40           | MHz                    | 50           | MHz                    | 60           | MHz                  | 11 *     |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------|--------------|------------------------|--------------|----------------------|----------|

| Num    | Characteristics                                                                                                                                                                                        | Min          | Max                    | Min          | Max                    | Min          | Max                  | Unit     |

| 10     | RESET Assertion to Address, Data and<br>Control Signals High Impedance                                                                                                                                 | _            | 25                     | _            | 23                     | _            | 21                   | ns       |

| 11     | Minimum Stabilization Duration<br>(See Note 1) OMR bit 6=0<br>OMR bit 6=1                                                                                                                              | 600KT<br>60T |                        | 600KT<br>60T | _                      | 600KT<br>60T |                      | ns<br>ns |

| 12     | Asynchronous RESET Deassertion to<br>First External Address Output<br>(See Note 7)                                                                                                                     | 16T          | 18T+20                 | 16T          | 18T+17                 | 16T          | 18T+15               | ns       |

| 13     | Synchronous Reset Setup Time from<br>RESET Deassertion to Rising Edge of<br>CLKO                                                                                                                       | 7            | cyc-4                  | 6            | cyc-3                  | 5            | cyc-2                | ns       |

| 14     | Synchronous Reset Delay Time from<br>CLKO High to the First External Access<br>(See Note 7)                                                                                                            | 16T+3        | 16T+20                 | 16T+ 3       | 16T+18                 | 16T+3        | 16T+16               | ns       |

| 15     | Mode Select Setup Time                                                                                                                                                                                 | 22           | —                      | 20           | ())                    | 18           | —                    | ns       |

| 16     | Mode Select Hold Time                                                                                                                                                                                  | 0            | _                      | 0            | - $E/$                 | 0            | —                    | ns       |

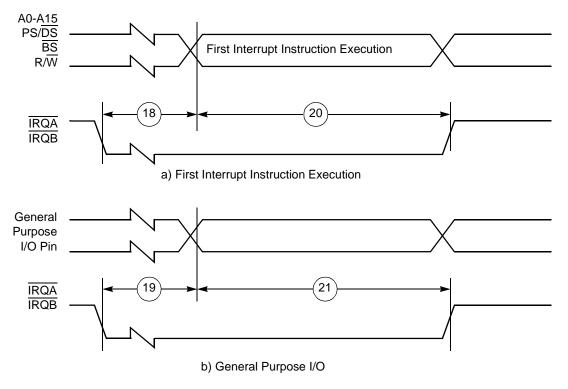

| 17     | Edge-triggered Interrupt Request Width                                                                                                                                                                 | 13           | —                      | 11           | $\geq$ (               | <b>9</b>     | $\wedge$             | ns       |

| 18     | Delay from IRQA, IRQB Assertion to<br>External Data Memory Access Out Valid<br>- Caused by First Interrupt<br>Instruction Fetch                                                                        |              |                        |              |                        |              |                      |          |

|        | - Caused by First Interrupt<br>Instruction Execution                                                                                                                                                   | 11T+4        | —                      | 11T+4        | —                      | 11T+3        | $\sim$               | ns       |

|        |                                                                                                                                                                                                        | 19T+4        | —                      | 19T+4        | —                      | 19T+3        | —                    | ns       |

| 19     | Delay from IRQA, IRQB Assertion to<br>General Purpose Output Valid Caused<br>by the Execution of the First Interrupt<br>Instruction                                                                    | 22T+5        |                        | 22T+4        | _                      | 22T+3        | _                    | ns       |

| 20     | Delay from External Data Memory<br>Address Output Valid Caused by First<br>Interrupt Instruction Execution to Inter-<br>rupt Request Deassertion for Level Sen-<br>sitive Fast Interrupts (See Note 2) | _            | 5T-26<br>+<br>cyc × ws | _            | 5T-24<br>+<br>cyc × ws | _            | 5T-22<br>+<br>cyc×ws | ns       |

| Table 13 Reset, Stop, Wait, Mode Select, and Interrupt Timing | Table 13 | Reset, | Stop, | Wait, | Mode | Select, | and | Interrupt | Timing |

|---------------------------------------------------------------|----------|--------|-------|-------|------|---------|-----|-----------|--------|

|---------------------------------------------------------------|----------|--------|-------|-------|------|---------|-----|-----------|--------|

Downloaded from Elcodis.com electronic components distributor

Reset, Stop, Wait, Mode Select, and Interrupt Timing

(V<sub>CC</sub> = 5.0 V dc  $\pm$  10%, T<sub>J</sub> = -40° to +125°C, C<sub>L</sub> = 50 pF + 1 TTL Load)

|     |                                                                                                                                                                                                                                                                       | 40 N               | 1Hz                    | 50 N               | IHz                    | 60 N               | /Hz                    |          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|--------------------|------------------------|--------------------|------------------------|----------|

| Num | Characteristics                                                                                                                                                                                                                                                       | Min                | Max                    | Min                | Max                    | Min                | Мах                    | Unit     |

| 21  | Delay from General-Purpose<br>Output Valid Caused by the<br>Execution of the First Inter-<br>rupt Instruction to IRQA,<br>IRQB Deassertion for Level<br>Sensitive Fast Interrupts — If<br>2nd Interrupt Instruction is:<br>Single Cycle<br>(See Note 2)<br>Two Cycles |                    | сус - 29<br>3 сус - 29 |                    | сус - 27<br>3 сус - 27 |                    | сус - 26<br>3 сус - 26 | ns       |

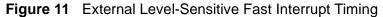

| 22  | Synchronous setup time from<br>IRQA, IRQB assertion to<br>Synchronous falling edge of<br>CLKO (See Notes 5 and 6)                                                                                                                                                     | 14                 | сус-3                  | 13                 | сус-2                  | 12                 | cyc-1                  | ns       |

| 23  | Falling Edge of CLKO to First<br>Interrupt Vector Address Out<br>Valid after Synchronous<br>recovery from Wait State<br>(See Notes 3 and 5)                                                                                                                           | 277+3              | 27T+20                 | 27T+3              | 27T+18                 | 27T+3              | 27T+16                 | ns       |

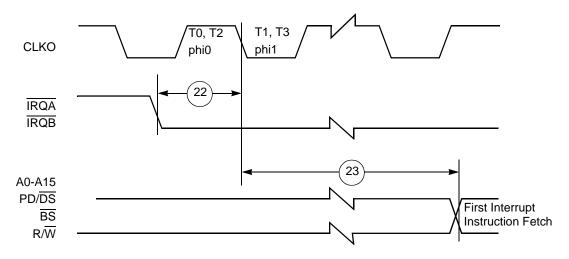

| 24  | IRQA Width Assertion to<br>Recover from Stop State<br>(See Note 4)                                                                                                                                                                                                    | 15                 |                        | 13                 | _                      | 12                 | —                      | ns       |

| 25  | Delay from IRQA Assertion to<br>Fetch of first instruction (exit-<br>ing Stop)<br>(See Notes 1 and 3)<br>OMR bit 6=0<br>OMR bit 6=1                                                                                                                                   | 524303T+4<br>47T+4 |                        | 524303T+3<br>47T+3 |                        | 524303T+3<br>47T+3 | >=                     | ns<br>ns |

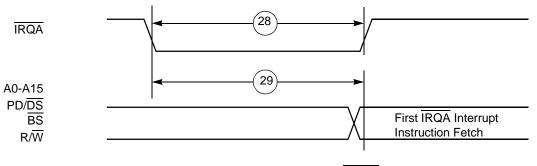

| 28  | Duration for Level Sensitive<br>IRQA Assertion to Cause the<br>Fetch of First IRQA Interrupt<br>Instruction (exiting Stop)<br>(See Notes 1 and 3)<br>OMR bit 6=0<br>OMR bit 6=1                                                                                       | 524303T<br>47T     |                        | 524303T<br>47T     | _                      | 524303T<br>47T     |                        | ns<br>ns |

| 29  | Delay from Level Sensitive<br>IRQA Assertion to First Inter-<br>rupt Vector Address Out<br>Valid (exiting Stop)<br>(See Notes 1 and 3)<br>OMR bit 6=0<br>OMR bit 6=1                                                                                                  | 524303T+4<br>47T+4 |                        | 524303T+3<br>47T+3 |                        | 524303T+3<br>47T+3 |                        | ns<br>ns |

Table 13 Reset, Stop, Wait, Mode Select, and Interrupt Timing (continued)

MOTOROLA

### **Freescale Semiconductor, Inc.**

#### **AC Electrical Characteristics and Timing**

Reset, Stop, Wait, Mode Select, and Interrupt Timing

**NOTES:** 1. Circuit stabilization delay is required during reset when using an external clock in two cases: • after power-on reset

- when recovering from Stop mode

- 2. When using fast interrupts, IRQA or IRQB is defined as level-sensitive, then timings 20 and 21 apply to prevent multiple interrupt service. To avoid these timing restrictions, the negative edge-triggered mode is recommended when using fast interrupts.

- 3. The interrupt instruction fetch is visible on the pins only in Mode 3.

- 4. The minimum is specified for the duration of an edge triggered IRQA interrupt required to recover from the Stop state. This is not the minimum required so that the IRQA interrupt is accepted.

- 5. Timing #22 is for all IRQx interrupts while timing #23 is only when exiting the Wait state.

- 6. Timing #22 triggers off T1 in the normal state and off phi1 when exiting the Wait state.

- 7. The instruction fetch is visible on the pins only in Mode 2 and Mode 3.

Figure 7 Asynchronous Reset Timing

Figure 8 Synchronous Reset Timing

24

**AC Electrical Characteristics and Timing**

Reset, Stop, Wait, Mode Select, and Interrupt Timing

Figure 9 Operating Mode Select Timing

Figure 10 External Interrupt Timing (Negative Edge-Triggered)

MOTOROLA

**Freescale Semiconductor, Inc.**

### **Freescale Semiconductor, Inc.**

#### **AC Electrical Characteristics and Timing**

Reset, Stop, Wait, Mode Select, and Interrupt Timing

Figure 13 Recovery from Stop State Using Asynchronous Interrupt Timing

26

Reset, Stop, Wait, Mode Select, and Interrupt Timing

| Num | Characteristics                                                                                                                                                                                                                                                 | 40                            | MHz     | 50 MHz                        |                  | 60 MHz                        |                  | Unit           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------|-------------------------------|------------------|-------------------------------|------------------|----------------|

| Num | Characteristics                                                                                                                                                                                                                                                 | Min                           | Max     | Min                           | Max              | Min                           | Max              | Onit           |

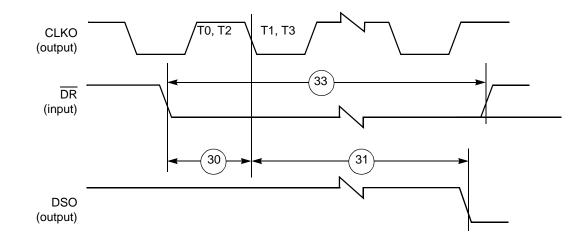

| 30  | DR Asserted to CLK high (Setup<br>Time for Synchronous Recovery<br>from Wait State)                                                                                                                                                                             | 10                            | cyc - 4 | 9                             | cyc - 3          | 8                             | cyc - 2          | ns             |

| 31  | CLK high to DSO (ACK) Valid<br>(Enter Debug Mode) after Syn-<br>chronous Recovery from Wait<br>State                                                                                                                                                            | 18 сус                        |         | 18 сус                        |                  | 18 сус                        |                  | ns             |

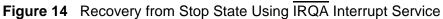

| 32  | DR to DSO (ACK) Valid         (Enter Debug Mode)         - After Asynchronous Recovery from Stop State         - After Asynchronous Recovery from Wait State                                                                                                    | 29 cyc<br>18 cyc              | _       | 29 сус<br>18 сус              | _                | 29 сус<br>18 сус              | _                | ns<br>ns       |

| 33  | <ul> <li>DR Assertion Width</li> <li>to Recover from Wait/Stop<br/>without entering debug mode</li> <li>to Recover from Wait/Stop<br/>short wake-up and enter<br/>debug mode</li> <li>to Recover from Stop<br/>long wake-up and enter<br/>debug mode</li> </ul> | 12<br>29 cyc<br>262157<br>cyc | 10 cyc  | 11<br>29 cyc<br>262157<br>cyc | 10 cyc<br>—<br>— | 10<br>29 cyc<br>262157<br>cyc | 10 cyc<br>—<br>— | ns<br>ns<br>ns |

### Table 14 Wait and Stop Timings

MOTOROLA

### Freescale Semiconductor, Inc.

#### AC Electrical Characteristics and Timing

Reset, Stop, Wait, Mode Select, and Interrupt Timing Capacitance Derating

## **Capacitance Derating**

The DSP56156 External Bus Timing Specifications are designed and tested at the maximum capacitive load of 50 pF, including stray capacitance. Typically, the drive capability of the External Bus pins (A0-A15, D0-D15, PS/ $\overline{DS}$ ,  $\overline{RD}$ ,  $\overline{BS}$ ,  $\overline{WR}$ ,  $R/\overline{W}$ ) derates linearly at 1 ns per 12 pF of additional capacitance from 50 pF to 250 pF of loading. Port B and C pins derate linearly at 1 ns per 5 pF of additional capacitance from 50 pF to 250 pF of loading.

When an internal memory access follows an external memory access, the PS/ $\overline{\text{DS}}$ , R/ $\overline{\text{W}}$ ,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  strobes remain deasserted and A0-A15 do not change from their previous state.

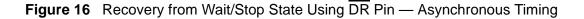

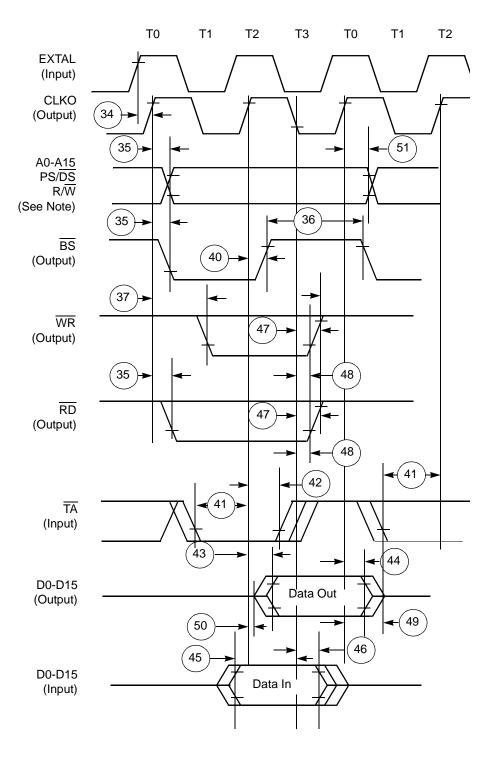

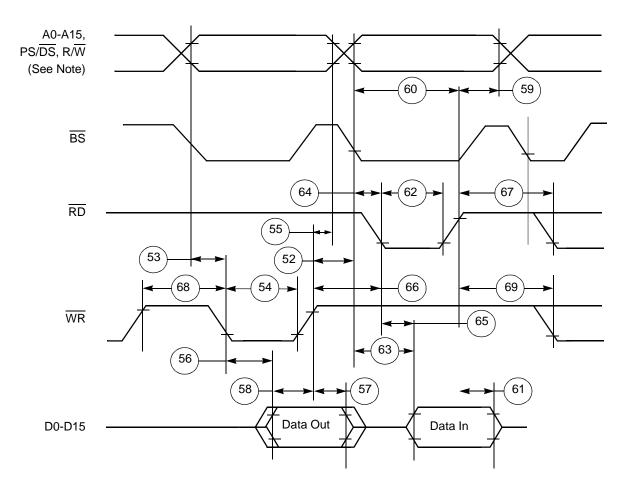

## **External Bus Synchronous Timing**

(V\_{CC} = 5.0 V dc  $\pm$  10%, T\_J = -40° to +125°C, C\_L = 50 pF + 1 TTL Load)

Table 15 lists external bus synchronous timing. Figure 17 and illustrate the bus timings with no wait states and two wait states, respectively.

| Num |                                                                           | 40    | MHz       | 50 MHz |                | 60 MHz |                  | Unit |

|-----|---------------------------------------------------------------------------|-------|-----------|--------|----------------|--------|------------------|------|

| Num | Characteristic                                                            | Min   | Max       | Min    | Max            | Min    | Max              | Unit |

| 34  | EXTAL CLK In High to CLKO High                                            | 2.4   | 9         | 2.4    | 9              | 2.4    | 9                | ns   |

| 35  | CLKO High to<br>a. A0-A15 Valid                                           | 4.7   | 12        | 4.7    | 12             | 4.7    | 12<br>(See Note) | ns   |

|     | b. PS/DS, R/W Valid, BS, RD Asserted                                      | 4.7   | 14        | 4.7    | 14             | 4.7    | 4                | ns   |

| 36  | BS Width Deasserted                                                       | 18.3  | —         | 13.4   | _              | 9.8    | —                | ns   |

| 37  | CLKO High to WR Asserted Low                                              | T+3.1 | T+12.4    | T+3.1  | T+12.4         | T+3.1  | T+12.4           | ns   |

| 38  | WR and RD Deasserted High to BS<br>Asserted Low (2 Successive Bus Cycles) | 14.3  | 45.8      | 11.8   | 13.3           | 10.2   | 11.8             | ns   |

| 39  | <intentionally blank=""></intentionally>                                  |       | $/ \land$ |        |                |        |                  |      |

| 40  | CLKO High to BS Deasserted                                                | 2.6   | 10.3      | 2.6    | 10.3           | 2.6    | 10.3             | ns   |

| 41  | TA Valid to CLKO High (Setup)                                             | 4.5   | /_/       | 4.5    | <u> </u>       | 4.5    |                  | ns   |

| 42  | CLKO High to $\overline{TA}$ Invalid (Hold)                               | 0     |           | 0      |                | 0      |                  | ns   |

| 43  | CLKO High to D0-D15 Out Valid                                             | 1.7   | 7.1       | 1.7    | 7.1            | 1.7    | 7.1              | ns   |

| 44  | CLKO High to D0-D15 Out Invalid                                           | 2.0   | _         | 2.0    | $\langle \neq$ | 2.0    | $\frown$         | ns   |

| 45  | D0-D15 In Valid to CLKO Low (Setup)                                       | 6     | _         | 6      | —              | 6      | _                | ns   |

| 46  | CLKO Low to D0-D15 In Invalid (Hold)                                      | 0     | _         | 0      | $\sim$         | 0      |                  | ns   |

| 47  | CLKO Low to WR, RD Deasserted                                             | _     | 10        | —      | 10             | —      | 10               | ns   |

| 48  | $\overline{\text{WR}}, \overline{\text{RD}}$ Hold Time from CLKO Low      | 2.2   | _         | 2.2    | _              | 2.2    | —                | ns   |

| 49  | CLKO High to D0-D15 Three-state                                           | 0     | 6         | 0      | 6              | 0      | 6                | ns   |

| 50  | CLKO High to D0-D15 Out Active                                            | 1.2   | 4.2       | 1.2    | 4.2            | 1.2    | 4.2              | ns   |

| 51  | CLKO High to A0-A15, PS/DS, R/W Invalid                                   | 2.8   | _         | 2.8    | _              | 2.8    | —                | ns   |

Table 15 External Bus Synchronous Timing

**NOTE:** 10 ns  $C_L = 25 \text{ pF}$

Downloaded from Elcodis.com electronic components distributor

### Freescale Semiconductor, Inc.

#### **AC Electrical Characteristics and Timing**

External Bus Synchronous Timing

Figure 17 External Bus Synchronous Timing — No Wait States

## Freescale Semiconductor, Inc.

**AC Electrical Characteristics and Timing**

External Bus Synchronous Timing

**Freescale Semiconductor, Inc.**

External Bus Asynchronous Timing

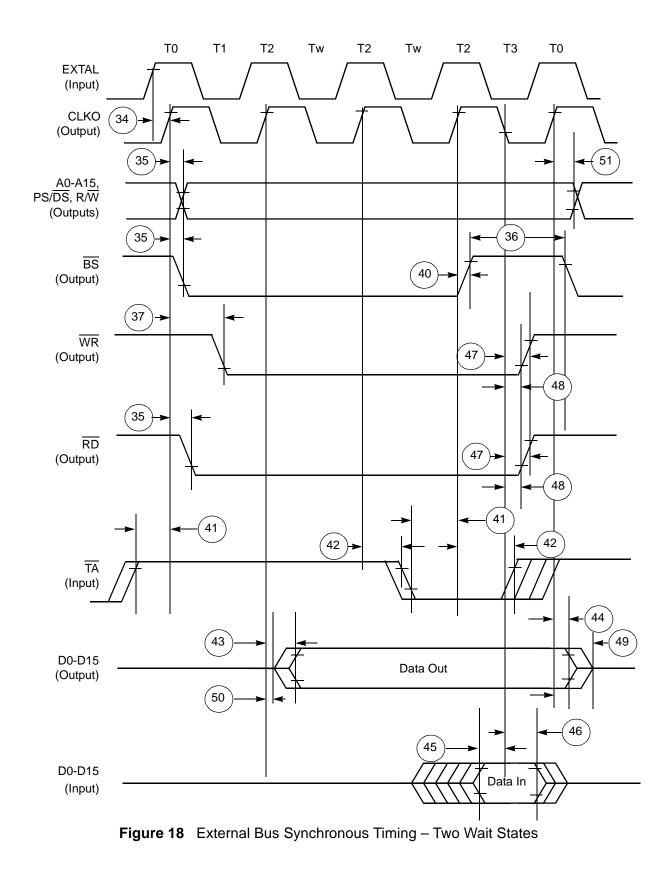

### **External Bus Asynchronous Timing**

$(V_{CC} = 5.0 \text{ V dc} \pm 10\%, T_J = -40^{\circ} \text{ to} + 125^{\circ}\text{C}, C_L = 50 \text{ pF} + 1 \text{ TTL Load})$

- cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles WS = Number of Wait States, Determined by BCR Register (WS = 0 to 31)

- = WS  $\times$  cyc = 2T  $\times$  WS WT

External Bus Asynchronous Timing

NOTE: During Read-Modify-Write instructions and internal instructions, the address lines do not change state.

Figure 19 External Bus Asynchronous Timing

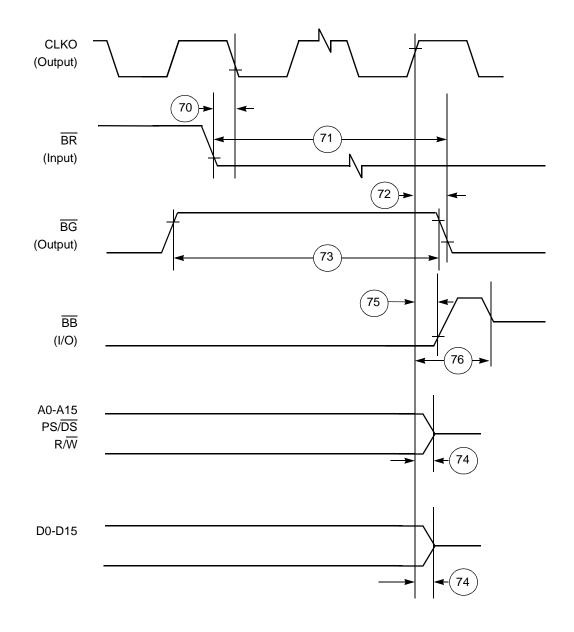

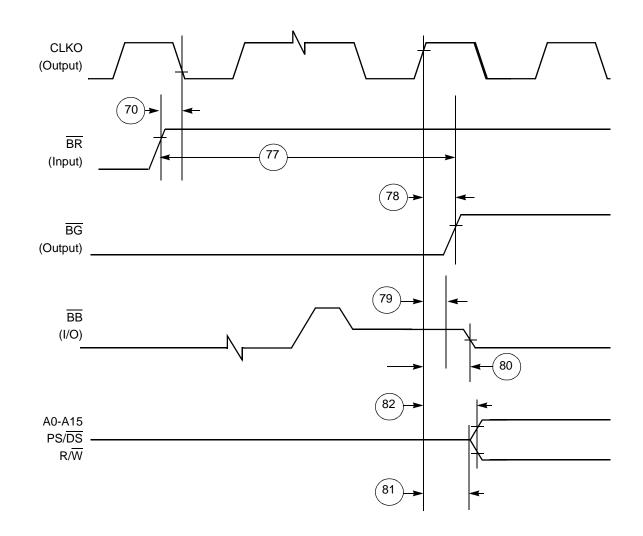

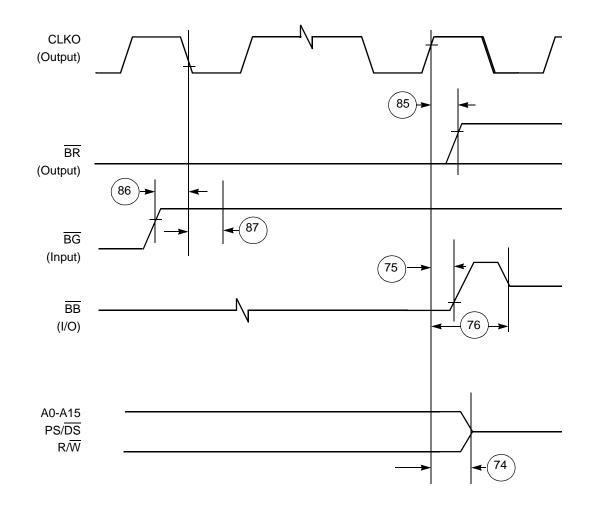

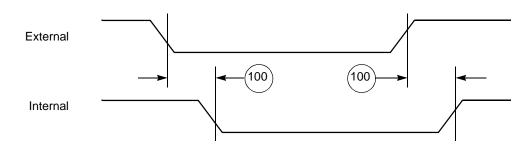

Bus Arbitration Timing — Slave Mode

## **Bus Arbitration Timing — Slave Mode**

(V\_{CC} = 5.0 V dc  $\pm$  10%, T\_J = -40° to +125°C, C\_L = 50 pF + 1 TTL Load)

- cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles

- WS = Number of Wait States for external X or P memory, Determined by BCR Register (WS = 0 to 31)

- WT =  $WS \times cyc = 2T \times WS$

- WX = Number of Wait States for external X memory, Determined by BCR Register (WS = 0 to 31)

- WP = Number of Wait States for external P memory, Determined by BCR Register (WS = 0 to 31)

| Num | Characteristics                                                                                                      | 40/5                       | 0/60 MHz                                           | 11:0:4 |

|-----|----------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------|--------|

| Num | Characteristics                                                                                                      | Min                        | Мах                                                | Unit   |

| 70  | BR Input to CLKO low setup time                                                                                      | 0                          | 1                                                  | ns     |

| 71  | Delay from BR Input Assertion to (See Note 1)<br>BG Output Assertion (See Note 2)<br>(See Note 3)                    | 5T+1.9<br>3T+1.9<br>5T+1.9 | 9T+4.2<br>6T+WT+4.2<br>26T+4T x WX<br>+2T x WP+4.2 | ns     |