# 100V, 2A Peak, Half-Bridge Driver with Tri-Level PWM Input and Adjustable Dead-Time

#### ISL78420

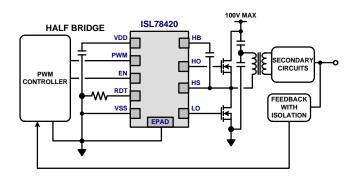

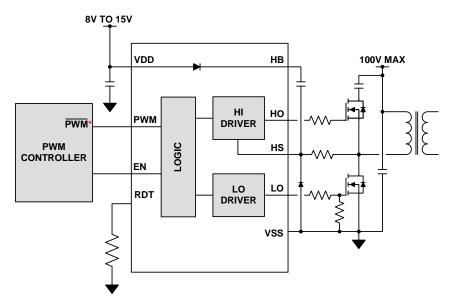

The ISL78420 is a 100V, high frequency, half-bridge MOSFET driver with a tri-level PWM input. This part is a derivative of the HIP2121 half-bridge driver. The non-automotive version of the ISL78420 is the HIP2124.

This driver is designed to work in conjunction with the <a href="ISL78220">ISL78220</a>, "6-Phase Interleaved Boost PWM Controller with Light Load Efficiency Enhancement". Equally, it can be used in most applications where a half-bridge driver is used.

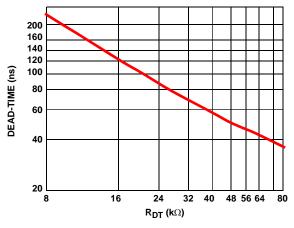

This driver has a programmable dead-time to ensure break-before-make operation between the high-side and low-side drivers. A resistor is used to adjust the dead-time up to 220ns.

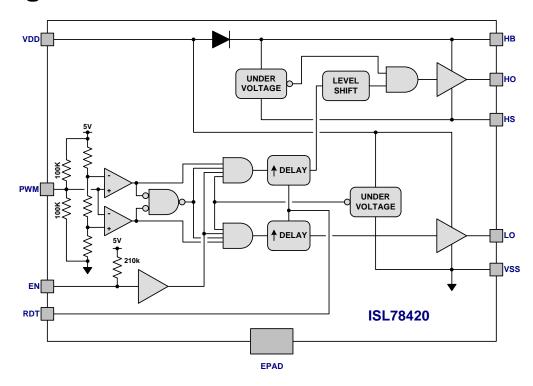

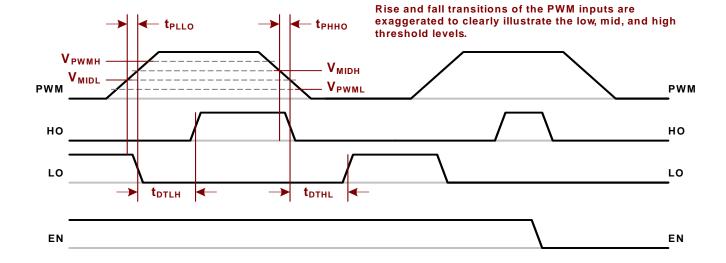

The tri-level input allows the PWM input to also function as a disable input. When the PWM input is a logic high, the high-side bridge FET is turned on and the low-side FET is off. When the input is a logic low, the low-side bridge FET is turned on and the high-side FET is turned off. When the input voltage is midrange, both the high and low-side bridge FETs are turned off.

The enable pin (EN), when low, drives both outputs to a low state. This input is used when the controller does not utilize a tri-state output. All logic inputs are  $V_{DD}$  tolerant.

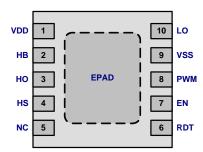

Two package options are provided. The 10 Ld 4x4 DFN package has standard pinouts. The 9 Ld 4x4 DFN package omits pin 2 to comply with 100V conductor spacing per IPC-2221.

#### **Features**

- Programmable break-before-make dead-time prevents shoot-through and is adjustable up to 220ns

- Bootstrap supply maximum voltage to 114VDC

- Wide supply voltage range (8V to 14V)

- · Supply undervoltage protection

- On-chip  $\mathbf{1}\Omega$  bootstrap diode

- Unique tri-level PWM input logic enables phase shedding when using multi-phase PWM controllers (e.g. ISL78220/225)

- 9 Ld TDFN "B" package compliant with 100V conductor spacing guidelines per IPC-2221

- AEC-0100 Qualified

## **Applications**

- · Automotive applications

- Multi-phase boost (ISL78220/225)

- · Half-bridge DC/DC converter

- · Class-D amplifiers

- · Forward converter with active clamp

#### **Related Literature**

- FN7668 HIP2120, HIP2121 "100V, 2A Peak, High Frequency Half-Bridge Drivers with Adjustable Dead Time Control and PWM Input"

- FN8363 HIP2124, "100V, 2A Peak, Half Bridge Driver with Tri-level Input and Adjustable Dead Time" (non-automotive)

- FN7688 ISL78220, "6-Phase Interleaved Boost PWM Controller with Light Load Efficiency Enhancement"

- FN7909 ISL78225, "4-Phase Interleaved Boost PWM Controller with Light Load Efficiency Enhancement"

**FIGURE 1. TYPICAL APPLICATION**

FIGURE 2. DEAD-TIME vs TIMING RESISTOR

## **Block Diagram**

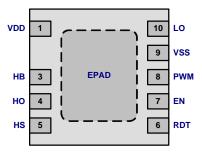

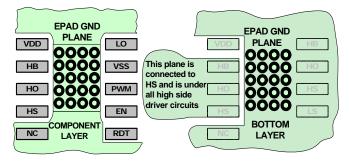

## **Pin Configurations**

ISL78420ARTAZ (10 LD 4X4 TDFN) TOP VIEW

ISL78420ARTBZ (9 LD 4X4 TDFN) TOP VIEW

## **Pin Descriptions**

| 10<br>LD | 9<br>LD | SYMBOL | DESCRIPTION                                                                                                                                                                                  |

|----------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 1       | VDD    | Positive supply voltage for lower gate driver. Decouple this pin to ground with a 4.7µF or larger ceramic capacitor to VSS                                                                   |

| 2        | 3       | НВ     | High-side bootstrap supply voltage referenced to HS. Connect bootstrap capacitor to this pin and HS.                                                                                         |

| 3        | 4       | но     | High-side output connected to gate of high-side FET.                                                                                                                                         |

| 4        | 5       | HS     | High-side source connect to source of high-side FET.<br>Connect bootstrap capacitor to this pin and HB.                                                                                      |

| 8        | 8       | PWM    | PWM input. For PWM = 5V, HO = 1, LO = 0. For PWM = 0V, HO = 0, LO = 1. For PWM = 2.5V, HO = LO = 0.                                                                                          |

| 7        | 7       | EN     | Output enable, when low, HO = LO = 0                                                                                                                                                         |

| 9        | 9       | VSS    | Negative voltage supply, Connected to ground.                                                                                                                                                |

| 10       | 10      | LO     | Low-side output. Connect to gate of low-side FET.                                                                                                                                            |

| 5        | -       | NC     | No Connect. This pin is isolated from all other pins. May optionally be connected to VSS. Note that on the 9 Ld package, there is no pin present at the location normally occupied by pin 2. |

| 6        | 6       | RDT    | A resistor connected between this pin and VSS adds dead time by adding delay time to the falling and rising edges of the PWM input.                                                          |

| -        | -       | EPAD   | The epad is electrically isolated. It is recommended that the epad be connected to the VSS plane for heat removal.                                                                           |

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | INPUT        | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|--------------------------------|-----------------|--------------|---------------------|----------------------|----------------|

| ISL78420ART <b>A</b> Z         | 78420 AZ        | 5V Tri-level | -40 +125            | 10 Ld 4x4 TDFN       | L10.4x4        |

| ISL78420ARTBZ (Note 4)         | 78420 BZ        | 5V Tri-level | -40 +125            | 9 Ld 4x4 TDFN        | L9.4x4         |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL78420. For more information on MSL please see tech brief TB363. and TB477.

- 4. "B" package option has alternate pin assignments for compliance with 100V Conductor Spacing Guidelines per IPC-2221. Note that Pin 2 is omitted for additional spacing between pins 1 and 3.

#### **Absolute Maximum Ratings (Note 6)**

| Supply Voltage, V <sub>DD</sub> , V <sub>HB</sub> - V <sub>HS</sub> (Notes 5) | 0.3V to 18V                    |

|-------------------------------------------------------------------------------|--------------------------------|

| PWM and EN Input Voltage                                                      | 0.3V to V <sub>DD</sub> + 0.3V |

| Voltage on LO                                                                 | 0.3V to V <sub>DD</sub> + 0.3V |

| Voltage on HO                                                                 | . VHS - 0.3V to VHB + 0.3V     |

| Voltage on HS (Continuous)                                                    | 1V to 110V                     |

| Voltage on HB                                                                 | 118V                           |

| Average Current in V <sub>DD</sub> to HB Diode                                | 100mA                          |

## Maximum Recommended Operating Conditions (Note 6)

| Supply Voltage, V <sub>DD</sub> | 8V to 14V                                              |

|---------------------------------|--------------------------------------------------------|

| Voltage on HS                   | 1V to 100V                                             |

| Voltage on HS                   | (Repetitive Transient) -5V to 105V                     |

| Voltage on HB                   | V <sub>HS</sub> + 8V to V <sub>HS</sub> + 14V and      |

|                                 | $\dots$ V <sub>DD</sub> - 1V to V <sub>DD</sub> + 100V |

| HS Slew Rate                    | <50V/ns                                                |

| Temperature                     | 40°C to +125°C                                         |

#### **Thermal Information**

| Thermal Resistance (Typical)  10 Ld TDFN (Notes 7, 8)                                                                          | θ <sub>JA</sub> (°C/W)<br>42<br>42 | θ <sub>JC</sub> (°C/W)<br>4<br>4  |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------|

| Max Power Dissipation at +25°C in Free Air 10 Ld TDFN                                                                          |                                    | 3.1W                              |

| Storage Temperature Range                                                                                                      | 5                                  | 5°C to +150°C<br>see <u>TB487</u> |

| ESD Ratings Human Body Model Class 2 (Tested per JESD Machine Model Class B (Tested per JESD22-/ Charged Device Model Class IV | <b>A115-A</b> )                    | 300V                              |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

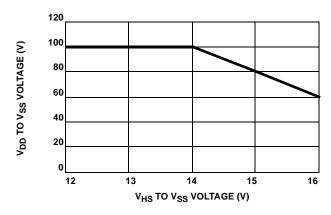

- 5. The ISL78420 is capable of derated operation at supply voltages exceeding 14V. Figure 17 shows the high-side voltage derating curve for this mode of operation.

- 6. All voltages referenced to V<sub>SS</sub> unless otherwise specified.

- 7. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 8. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications**  $V_{DD} = V_{HB} = 12V$ ,  $V_{SS} = V_{HS} = 0V$ ,  $R_{DT} = 0_K$ , PWM = 0V, No Load on LO or HO, Unless Otherwise Specified. Boldface limits apply over the operating temperature range, -40°C to +125°C.

|                                          |                     |                                                        | т,  | <b>4 =</b> +25 | °C  | T <sub>A</sub> = -40°0 |                 |       |

|------------------------------------------|---------------------|--------------------------------------------------------|-----|----------------|-----|------------------------|-----------------|-------|

| PARAMETERS                               | SYMBOL              | TEST CONDITIONS                                        | MIN | ТҮР            | MAX | MIN<br>(Note 9)        | MAX<br>(Note 9) | UNITS |

| SUPPLY CURRENTS                          |                     |                                                        |     |                |     |                        |                 |       |

| V <sub>DD</sub> Quiescent Current        | I <sub>DD8k</sub>   | R <sub>DT</sub> = 8k                                   | -   | 650            | 950 | -                      | 1000            | μΑ    |

|                                          | I <sub>DD80k</sub>  | R <sub>DT</sub> = 80k                                  | -   | 1.0            | 2.1 | -                      | 2.2             | mA    |

| V <sub>DD</sub> Operating Current        | I <sub>DD08k</sub>  | f = 500kHz, R <sub>DT</sub> = 8k                       | -   | 2.5            | 3   | -                      | 3               | mA    |

|                                          | I <sub>DD080k</sub> | f = 500kHz, R <sub>DT</sub> = 80k                      | -   | 3.4            | 4   | -                      | 4               | mA    |

| Total HB Quiescent Current               | I <sub>HB</sub>     | LI = HI = OV                                           | -   | 65             | 115 | -                      | 150             | μA    |

| Total HB Operating Current               | Інво                | f = 500kHz                                             | -   | 2.0            | 2.5 | -                      | 3               | mA    |

| HB to V <sub>SS</sub> Current, Quiescent | I <sub>HBS</sub>    | LI = HI = 0V; V <sub>HB</sub> = V <sub>HS</sub> = 114V | -   | 0.05           | 1.5 | -                      | 10              | μA    |

| HB to V <sub>SS</sub> Current, Operating | I <sub>HBSO</sub>   | f = 500kHz; V <sub>HB</sub> = V <sub>HS</sub> = 114V   | -   | 1.2            | 1.5 | -                      | 1.6             | mA    |

| Tri-Level PWM Input                      |                     |                                                        |     |                |     |                        |                 |       |

| High Level Threshold                     | V <sub>PWMH</sub>   |                                                        | -   | 3.6            | 4.0 | -                      | 4.3             | ٧     |

| High Middle Level Threshold              | V <sub>MIDH</sub>   |                                                        | 3.0 | 3.4            | -   | 2.9                    | -               | ٧     |

| Low Middle Level Threshold               | V <sub>MIDL</sub>   |                                                        | -   | 1.6            | 2.1 | -                      | 2.2             | V     |

| Low Level Threshold                      | V <sub>PWML</sub>   |                                                        | 0.8 | 1.1            | -   | 0.7                    | -               | V     |

| PWM Mid level Pull-up Resistors          | R <sub>mid</sub>    |                                                        | -   | 160            | -   | -                      | -               | kΩ    |

### ISL78420

**Electrical Specifications**  $V_{DD} = V_{HB} = 12V$ ,  $V_{SS} = V_{HS} = 0V$ ,  $R_{DT} = 0_K$ , PWM = 0V, No Load on LO or HO, Unless Otherwise Specified. Boldface limits apply over the operating temperature range, -40 °C to +125 °C. (Continued)

|                                      |                  |                                                                                | T,  | <b>, =</b> +25 | °C  | T <sub>A</sub> = -40°C |                 |       |

|--------------------------------------|------------------|--------------------------------------------------------------------------------|-----|----------------|-----|------------------------|-----------------|-------|

| PARAMETERS                           | SYMBOL           | TEST CONDITIONS                                                                | MIN | TYP            | MAX | MIN<br>(Note 9)        | MAX<br>(Note 9) | UNITS |

| EN Input                             |                  |                                                                                |     |                |     |                        |                 |       |

| Low Level Input Threshold            | V <sub>ENL</sub> |                                                                                | 1.4 | 1.8            | -   | 1.2                    | -               | ٧     |

| High Level Input Threshold           | V <sub>ENH</sub> |                                                                                | -   | 1.8            | 2.2 | -                      | 2.4             | ٧     |

| EN Pull-up Resistance                | R <sub>pu</sub>  |                                                                                | -   | 210            | -   | 100                    | 320             | kΩ    |

| UNDERVOLTAGE PROTECTION              | -                |                                                                                |     |                | '   |                        |                 | *     |

| V <sub>DD</sub> Rising Threshold     | V <sub>DDR</sub> |                                                                                | 6.8 | 7.3            | 7.8 | 6.5                    | 8.1             | V     |

| V <sub>DD</sub> Threshold Hysteresis | $V_{DDH}$        |                                                                                | -   | 0.6            | -   | -                      | -               | V     |

| HB Rising Threshold                  | V <sub>HBR</sub> |                                                                                | 6.2 | 6.9            | 7.5 | 5.9                    | 7.8             | ٧     |

| HB Threshold Hysteresis              | V <sub>HBH</sub> |                                                                                | -   | 0.6            | -   | -                      | -               | ٧     |

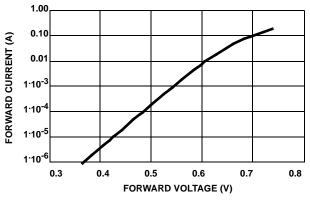

| BOOTSTRAP DIODE                      | -                | ,                                                                              | ,   |                |     |                        |                 |       |

| Low Current Forward Voltage          | V <sub>DL</sub>  | I <sub>VDD-HB</sub> = 100mA                                                    | -   | 0.6            | 0.7 | -                      | 0.8             | V     |

| High Current Forward Voltage         | V <sub>DH</sub>  | I <sub>VDD-HB</sub> = 100mA                                                    | -   | 0.7            | 0.9 | -                      | 1               | V     |

| Dynamic Resistance                   | R <sub>D</sub>   | I <sub>VDD-HB</sub> = 100mA                                                    | -   | 0.8            | 1   | -                      | 1.5             | Ω     |

| LO GATE DRIVER                       |                  |                                                                                |     |                |     |                        |                 |       |

| Low Level Output Voltage             | V <sub>OLL</sub> | I <sub>LO</sub> = 100mA                                                        | -   | 0.25           | 0.4 | -                      | 0.5             | V     |

| High Level Output Voltage            | V <sub>OHL</sub> | I <sub>LO</sub> = -100mA, V <sub>OHL</sub> = V <sub>DD</sub> - V <sub>LO</sub> | -   | 0.25           | 0.4 | -                      | 0.5             | V     |

| Peak Pull-Up Current                 | I <sub>OHL</sub> | V <sub>LO</sub> = 0V                                                           | -   | 2              | -   | -                      | -               | Α     |

| Peak Pull-Down Current               | l <sub>OLL</sub> | V <sub>LO</sub> = 12V                                                          | -   | 2              | -   | -                      | -               | Α     |

| HO GATE DRIVER                       | -                | ,                                                                              | •   | 1              |     |                        |                 |       |

| Low Level Output Voltage             | V <sub>OLH</sub> | I <sub>HO</sub> = 100mA                                                        | -   | 0.25           | 0.4 | -                      | 0.5             | V     |

| High Level Output Voltage            | V <sub>OHH</sub> | I <sub>HO</sub> = -100mA, V <sub>OHH</sub> = V <sub>HB</sub> - V <sub>HO</sub> | -   | 0.25           | 0.4 | -                      | 0.5             | V     |

| Peak Pull-Up Current                 | Іонн             | V <sub>HO</sub> = 0V                                                           | -   | 2              | -   | -                      | -               | Α     |

| Peak Pull-Down Current               | l <sub>OLH</sub> | V <sub>HO</sub> = 12V                                                          | -   | 2              | -   | -                      | -               | Α     |

**Switching Specifications**  $V_{DD} = V_{HB} = 12V$ ,  $V_{SS} = V_{HS} = 0V$ ,  $R_{DT} = 0k\Omega$ , No Load on LO or HO, Unless Otherwise Specified. **Boldface** limits apply over the operating temperature range, -40 °C to +125 °C.

|                                                              |                      |                                      | T <sub>J</sub> = +25°C |      |     | T <sub>J</sub> = -40°C to +125°C |                 |       |

|--------------------------------------------------------------|----------------------|--------------------------------------|------------------------|------|-----|----------------------------------|-----------------|-------|

| PARAMETERS                                                   | SYMBOL               | TEST<br>CONDITIONS                   | MIN                    | TYPE | MAX | MIN<br>(Note 9)                  | MAX<br>(Note 9) | UNITS |

| HO Turn-Off Propagation Delay<br>PWM Falling to HO Falling   | t <sub>PLHO</sub>    |                                      | -                      | 32   | 50  | -                                | 60              | ns    |

| LO Turn-Off Propagation Delay<br>PWM Rising to LO Falling    | t <sub>PLLO</sub>    |                                      | -                      | 32   | 50  | -                                | 60              | ns    |

| Minimum Dead-Time Delay (Note 10)<br>HO Falling to LO Rising | t <sub>DTHLmin</sub> | R <sub>DT</sub> = 80k,<br>PWM 1 to 0 | 15                     | 35   | 50  | 10                               | 60              | ns    |

| Minimum Dead-Time Delay (Note 10)<br>LO Falling to HO Rising | t <sub>DTLHmin</sub> | R <sub>DT</sub> = 80k<br>PWM 0 to 1  | 15                     | 25   | 50  | 10                               | 60              | ns    |

| Maximum Dead-Time Delay (Note 10)<br>HO Falling to LO Rising | t <sub>DTHLmax</sub> | R <sub>DT</sub> = 8k,<br>PWM 1 to 0  | 150                    | 220  | 300 | -                                | -               | ns    |

**Switching Specifications**  $V_{DD} = V_{HB} = 12V$ ,  $V_{SS} = V_{HS} = 0V$ ,  $R_{DT} = 0k\Omega$ , No Load on LO or HO, Unless Otherwise Specified. **Boldface** limits apply over the operating temperature range, -40 °C to +125 °C. (Continued)

|                                                              |                                  |                                     | T <sub>J</sub> = +25°C |      |     | T <sub>J</sub> = -40°C |                 |       |

|--------------------------------------------------------------|----------------------------------|-------------------------------------|------------------------|------|-----|------------------------|-----------------|-------|

| PARAMETERS                                                   | SYMBOL                           | TEST<br>CONDITIONS                  | MIN                    | TYPE | MAX | MIN<br>(Note 9)        | MAX<br>(Note 9) | UNITS |

| Maximum Dead-Time Delay (Note 10)<br>LO Falling to HO Rising | t <sub>DTLHmax</sub>             | R <sub>DT</sub> = 8k,<br>PWM 0 to 1 | 150                    | 220  | 300 | -                      | -               | ns    |

| Either Output Rise/Fall Time (10% to 90%/90% to 10%)         | t <sub>RC,</sub> t <sub>FC</sub> | C <sub>L</sub> = 1nF                | -                      | 10   | -   | -                      | -               | ns    |

| Bootstrap Diode Turn-On or Turn-Off Time                     | t <sub>BS</sub>                  |                                     | -                      | 10   | -   | -                      | -               | ns    |

#### NOTES:

- 9. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits are established by characterization and are not production tested.

- 10. Dead-Time is defined as the period of time between the LO falling and HO rising or between HO falling and LO rising.

## **Timing Diagram**

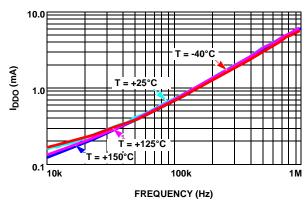

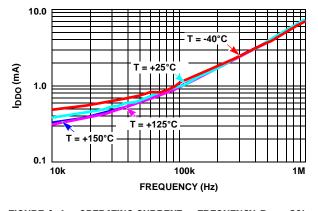

## **Typical Performance Curves**

FIGURE 3.  $I_{DD}$  OPERATING CURRENT vs FREQUENCY,  $R_{DT} = 8K$

FIGURE 4.  $I_{DD}$  OPERATING CURRENT vs FREQUENCY,  $R_{DT} = 80k$

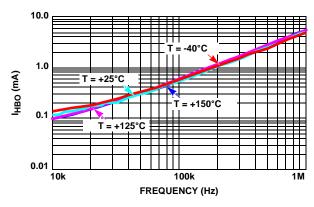

FIGURE 5.  $I_{HB}$  OPERATING CURRENT vs FREQUENCY,  $R_{DT} = 8k$

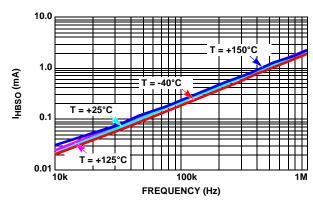

FIGURE 6.  $I_{HBS}$  OPERATING CURRENT vs FREQUENCY  $R_{DT} = 80 k$

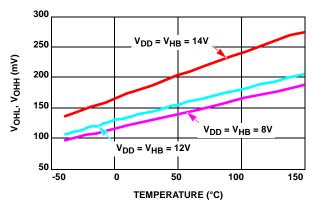

FIGURE 7. HIGH LEVEL OUTPUT VOLTAGE vs TEMPERATURE

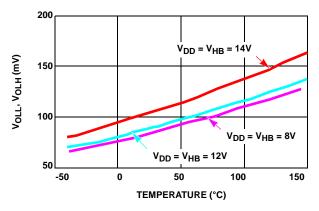

FIGURE 8. LOW LEVEL OUTPUT VOLTAGE vs TEMPERATURE

## **Typical Performance Curves** (Continued)

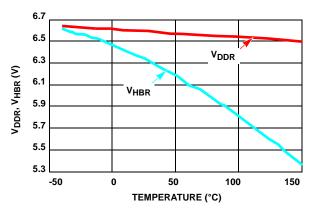

FIGURE 9. UNDERVOLTAGE LOCKOUT THRESHOLD vs TEMPERATURE

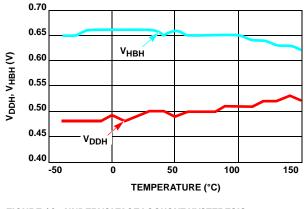

FIGURE 10. UNDERVOLTAGE LOCKOUT HYSTERESIS vs TEMPERATURE

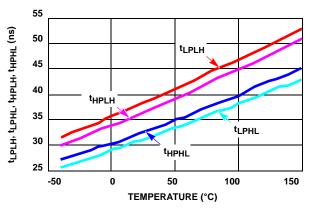

FIGURE 11. PROPAGATION DELAYS vs TEMPERATURE

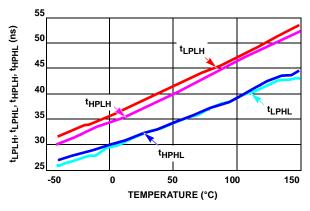

FIGURE 12. DELAY MATCHING vs TEMPERATURE

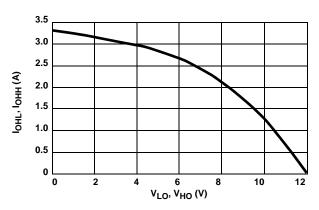

FIGURE 13. PEAK PULL-UP CURRENT vs OUTPUT VOLTAGE

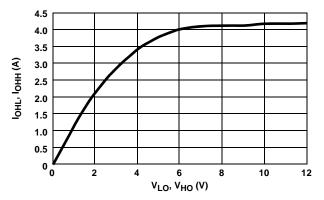

FIGURE 14. PEAK PULL-DOWN CURRENT vs OUTPUT VOLTAGE

## **Typical Performance Curves (Continued)**

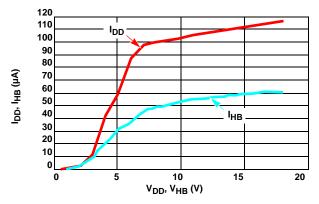

FIGURE 15. QUIESCENT CURRENT vs VOLTAGE

FIGURE 16. BOOTSTRAP DIODE I-V CHARACTERISTICS

FIGURE 17.  $V_{HS}$  VOLTAGE vs  $V_{DD}$  VOLTAGE

## **Functional Description**

#### **Functional Overview**

When connected to a half bridge, the output of the bridge on the HS node follows the PWM input. In other words, when the PWM input is high, the high-side bridge FET is turned on and the low-side FET is off. When the PWM input is low, the low-side bridge FET is turned on and the high-side is turned off. The enable pin (EN), when low, drives both outputs to a low state.

A unique feature of the ISL78420 is the tri-level logic of the PWM input. The logic thresholds of the PWM input is divided into 3 levels. A logic low ensures that the output of the low-side bridge FET is on and the high-side FET is off. A logic high ensures that the high-side bridge FET is on and the low-side FET is off. When the logic input is midrange (2.5V), both the high and low side FETs are off. This driver is designed to work in conjunction with the ISL78220, "6-Phase Interleaved Boost PWM Controller with Light Load Efficiency Enhancement".

When the PWM input transitions high or low, it is necessary to ensure that both bridge FETS are not on at the same time to prevent shoot-through currents (break before make). The internal programmable timers delay the rising edge of either output resulting with both outputs being off before either of the bridge FETs are driven on. An  $8k\Omega$  resistor connected between  $R_{DT}$  and

VSS results in a nominal dead time of 220ns. An  $80 k\Omega$  results with a minimum nominal dead time of 25ns. Resistors values less than 8k and greater than 80k are not recommended.

While the voltage of the input signal to the PWM is within the boundaries of the mid-level logic, the outputs are in a dead time state because both outputs are off. The actual delay time, as programed by the  $R_{DT}$  value, begins when the high or low logic levels are transitioned. The period while the input logic in the mid-level range, is consequently added to the programmed dead time period. This may be a consideration when selecting the  $R_{DT}$  value.

The high-side driver bias is established by the boot capacitor connected between HB and HS. The charge on the boot capacitor is provided by the internal boot diode that is connected to VDD. The current path to charge the boot capacitor occurs when the low-side bridge FET is on. This charge current is limited in amplitude by the inherent resistance of the boot diode and by the drain-source voltage of the low-side FET. Assuming that the on time of the low-side FET is sufficiently long to fully charge the boot capacitor, the boot voltage will charge very close to VDD (less the boot diode drop and the on-voltage of the low-side bridge FET).

When the PWM input transitions high, the high-side bridge FET is driven on after the dead time. Because the HS node is connected

to the source of the high-side FET, the HS node will rise almost to the level of the bridge voltage (less the conduction voltage across the bridge FET). Because the boot capacitor voltage is referenced to the source voltage of the high-side FET, the HB node is  $V_{\mbox{\scriptsize DD}}$  volts above the HS node and the boot diode is reversed biased. Because the high-side driver circuit is referenced to the HS node, the HO output is now approximately VHB + VBRIDGE above ground.

During the low to high transition of the HS node, the boot capacitor sources the necessary gate charge to fully enhance the high-side bridge FET gate. After the gate is fully charged, the boot capacitor no longer sources the charge to the gate but continues to provide bias current to the high-side driver. It is clear that the charge of the boot capacitor must be substantially larger than the required charge of the high-side FET and high-side driver otherwise the boot voltage will sag excessively. If the boot capacitor value is too small for the required maximum of on-time of the high-side FET, the high-side UV lockout may engage resulting with an unexpected operation.

## **Application Information**

#### **Selecting the Boot Capacitor Value**

The boot capacitor value is chosen not only to supply the internal bias current of the high-side driver but also, and more significantly, to provide the gate charge of the driven FET without causing the boot voltage to sag excessively. In practice, the boot capacitor should have a total charge that is approximately 20x the gate charge of the driven power FET for a 5% drop in voltage after the charge has been transferred from the boot capacitor to the gate capacitance.

The following parameters are required to calculate the value of the boot capacitor for a specific amount of voltage droop. In this example, the values used are arbitrary. They should be changed to comply with the actual application.

$V_{DD}$  = 10V  $V_{DD}$  can be any value between 7 and 14VDC

$V_{HB} = V_{DD} - 0.6V = V_{HO}$  High side driver bias voltage ( $V_{DD}$  - boot diode

voltage) referenced to V<sub>HS</sub>

Period = 1ms This is the longest expected switching period

I<sub>HB</sub> = 100μA Worst case high side driver current when

xHO = high (this value is specified for  $V_{DD}$  =

12V but the error is not significant)

$R_{GS} = 100k\Omega$  Gate-source resistor (usually not needed)

Ripple= 5% Desired ripple voltage on the boot cap (larger

ripple is not recommended)

Igate leak = 100nA From the FET vendor's datasheet

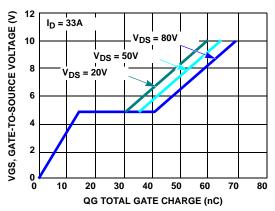

Qgate80V = 64nC From Figure 18

FIGURE 18. TYPICAL GATE CHARGE OF A POWER FET

The following equations calculate the total charge required for the Period. These equations assume that all of the parameters are constant during the period duration. The error is insignificant if the ripple is small.

$$\mathbf{Q_{C}} = \mathbf{Q_{gate80V}} + \mathbf{Period} \times \mathbf{I_{HB}} + \mathbf{V_{HO}}/(\mathbf{R_{GS}} + \mathbf{I_{gate\_leak}}) \qquad \textbf{(EQ. 1)}$$

$$C_{boot} = Q_{C}/(Ripple*VDD)$$

(EQ. 2)

$C_{boot} = 0.52 \mu F$

If the gate to source resistor is removed ( $R_{GS}$  is usually not needed or recommended), then:

$C_{boot} = 0.33 \mu F$

FIGURE 19. TYPICAL ACTIVE CLAMP FORWARD APPLICATION

## **Typical Application Circuit**

Figure 19 is an example of how the ISL78420 can be configured for an active clamp forward power supply application. Note that the PWM signal from the controller must be inverted for this active clamp forward topology.

Depending on the application, the switching speed of the bridge FETs can be reduced by adding series connected resistors between the xHO outputs and the FET gates. Gate-Source resistors are recommended on the low-side FETs to prevent unexpected turn-on of the bridge should the bridge voltage be applied before VDD. Gate-source resistors on the high-side FETs are not usually required if low-side gate-source resistors are used. If relatively low value gate-source resistors are used on the high-side FETs, be aware that a larger value for the boot capacitor may be required.

#### **Transients on HS Node**

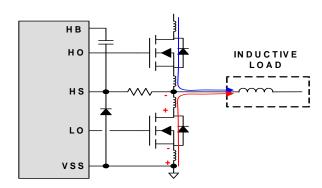

An important operating condition that is frequently overlooked by designers is the negative transient on the xHS pins that occurs when the high-side bridge FET turns off. The Absolute Maximum transient allowed on the xHS pin is -6V but it is wise to minimize the amplitude to lower levels. This transient is the result of the parasitic inductance of the low-side drain-source conductor on the PCB. Even the parasitic inductance of the low-side FET contributes to this transient.

When the high-side bridge FET turns off (see Figure 20), because of the inductive characteristics the load, the current that was flowing in the high-side FET (blue) must rapidly commutate to flow through the low-side FET (red). The amplitude of the negative transient impressed on the xHS node is  $(di/dt \times L)$  where L is the total parasitic inductance of the low-side FET drain-source path and di/dt is the rate at which the high-side FET is turned off. With the increasing power levels of power supplies and motors, clamping this transient become more and more significant for the proper operation of the ISL78420.

FIGURE 20. PARASITIC INDUCTANCE CAUSES TRANSIENTS ON HS NODE

There are several ways of reducing the amplitude of this transient. If the bridge FETs are turned off more slowly to reduce di/dt, the amplitude will be reduced but at the expense of more switching losses in the FETs. Careful PCB design will also reduce the value of the parasitic inductance. However, these two solutions by themselves may not be sufficient. Figure 20 illustrates a simple method for clamping the negative transient. A fast PN junction, 1A diode is connected between xHS and VSS as shown. It is important that this diode be placed as close as possible to the xHS and VSS pins to minimize the parasitic inductance of this current path. Because this clamping diode is essentially in parallel with the body diode of the low-side FET, a small value resistor is necessary to limit current when the body diode of the low-side bridge FET is conducting during the dead time. The resistor in series with HS, can be used instead of the gate resistor of the high-side FET.

Please note that a similar transient with a positive polarity occurs when the low-side FET turns off. This is less frequently a problem because xHS node is floating up toward the bridge bias voltage. The Absolute Max voltage rating for the xHS node does need to be observed when the positive transient occurs.

#### **Power Dissipation**

The dissipation of the ISL78420 is dominated by the gate charge required by the driven bridge FETs and the switching frequency. The internal bias and boot diode also contribute to the total dissipation but these losses are usually insignificant compared to the gate charge losses.

The calculation of the power dissipation of the ISL78420 is very simple.

#### **GATE POWER (FOR THE HO AND LO OUTPUTS)**

$$P_{gate} = 4 \times Q_{gate} \times Freq \times VDD$$

(EQ. 3)

where

$\mathbf{Q}_{\mbox{\scriptsize gate}}$  is the charge of the driven bridge FET at VDD, and

Freq is the switching frequency.

#### **BOOT DIODE DISSIPATION**

$$I_{diode\_avg} = Q_{gate} \times Freq$$

(EQ. 4)

$$P_{diode} = I_{diode\_avg} \times 0.6V$$

(EQ. 5)

where 0.6V is the diode conduction voltage

#### **BIAS CURRENT**

$$P_{hias} = I_{hias} \times VDD$$

(EQ. 6)

where I<sub>bias</sub> is the internal bias current of the ISL78420 at the switching frequency

#### **TOTAL POWER DISSIPATION**

#### **OPERATING TEMPERATURES**

$$T_j = P_{total} \times \theta_{JA} + T_{amb}$$

where  $T_j$  is the junction temperature at the operating air temperature,  $T_{amb}$ , in the vicinity of the part.

$$T_i = P_{total} \times \theta_{JC} + T_{PCB}$$

where  $T_j$  is the junction temperature with the operating temperature of the PCB,  $T_{PCB}$ , as measured where the EPAD is soldered.

### **PC Board Layout**

The AC performance of the ISL78420 depends significantly on the design of the PC board. The following layout design guidelines are recommended to achieve optimum performance from the ISL78420:

- Understand well how power currents flow. The high amplitude di/dt currents of the bridge FETs will induce significant voltage transients on the associated traces.

- Keep power loops as short as possible by paralleling the source and return traces.

- Use planes where practical; they're usually more effective than parallel traces.

- · Planes can also be non-grounded nodes.

- Avoid paralleling high di/dt traces with low level signal lines.

High di/dt will induce currents in the low level signal lines.

- When practical, minimize impedances in low level signal circuits; the noise, magnetically induced on a 10k resistor, is 10x larger than the noise on a 1k resistor.

- Be aware of magnetic fields emanating from transformers and inductors. Core gaps in these structures are especially bad for emitting flux.

- If you must have traces close to magnetic devices, align the traces so that they are parallel to the flux lines.

- The use of low inductance components such as chip resistors and chip capacitors is recommended.

- Use decoupling capacitors to reduce the influence of parasitic inductors. To be effective, these capacitors must also have the shortest possible lead lengths. If vias are used, connect several paralleled vias to reduce the inductance of the vias.

- It may be necessary to add resistance to dampen resonating parasitic circuits. In PCB designs with long leads on the LO and HO outputs, it may be necessary to add series gate resistors on the bridge FETs to dampen the oscillations.

- Keep high dv/dt nodes away from low level circuits. Guard banding can be used to shunt away dv/dt injected currents from sensitive circuits. This is especially true for the PWM control circuits.

- Avoid having a signal ground plane under a high dv/dt circuit.

This will inject high di/dt currents into the signal ground paths.

- Do power dissipation and voltage drop calculations of the power traces. Most PCB/CAD programs have built in tools for calculation of trace resistance.

- Large power components (Power FETs, Electrolytic capacitors, power resistors, etc.) will have internal parasitic inductance, which cannot be eliminated. This must be accounted for in the PCB layout and circuit design.

- If you simulate your circuits, consider including parasitic components.

## **EPAD Design Considerations**

The thermal pad of the ISL78420 is electrically isolated. It's primary function is to provide heat sinking for the IC. It is recommended to tie the EPAD to  $V_{SS}$  (GND).

Figure 21 is an example of how to use vias to remove heat from the IC substrate. Depending on the amount of power dissipated by the ISL78420, it may be necessary, to connect the EPAD to one or more ground plane layers. A via array, within the area of the EPAD, will conduct heat from the EPAD to the ground plane on the bottom layer. If inner PCB layers are available, it is also be desirable to connect these additional layers with the plated-through vias.

The number of vias and the size of the GND planes required for adequate heatsinking is determined by the power dissipated by the ISL78420, the air flow, and the maximum temperature of the air around the IC.

It is important that the vias have a low thermal resistance for efficient heat transfer. Do not use "thermal relief" patterns to connect the vias.

FIGURE 21. RECOMENDED PCB HEATSINK

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE               | REVISION | CHANGE          |

|--------------------|----------|-----------------|

| September 24, 2012 | FN8296.1 | Initial Release |

#### **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.

For a complete listing of Applications, Related Documentation and Related Parts, please see the respective product information page. Also, please check the product information page to ensure that you have the most updated datasheet: <a href="ISL78420">ISL78420</a>

To report errors or suggestions for this datasheet, please go to: www.intersil.com/askourstaff

FITs are available from our website at: http://rel.intersil.com/reports/search.php

For additional products, see <a href="www.intersil.com/product-tree">www.intersil.com/product-tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

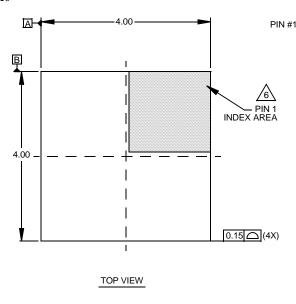

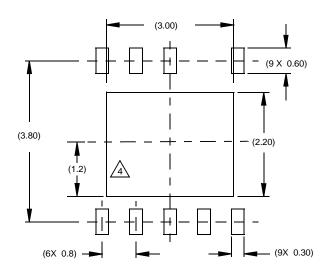

## **Package Outline Drawing**

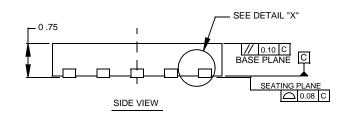

## L9.4x4 9 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE Rev 1, 1/10

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

4. E-Pad is offset from center.

- 5. Tiebar (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

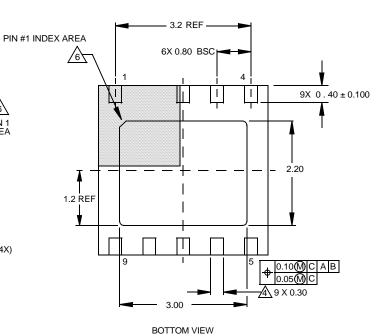

## **Package Outline Drawing**

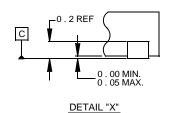

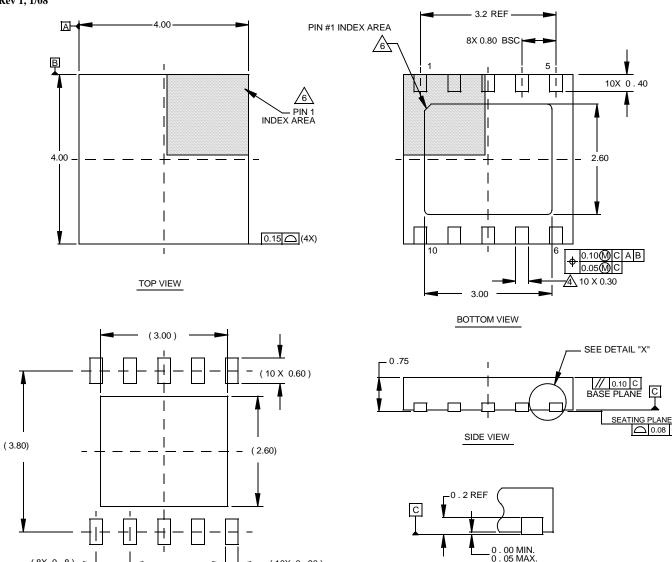

#### L10.4x4 10 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE Rev 1, 1/08

#### NOTES:

(10X 0.30)

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

DETAIL "X"

- Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

TYPICAL RECOMMENDED LAND PATTERN

(8X 0.8)