# PCM61P

# Serial Input 18-Bit Monolithic Audio DIGITAL-TO-ANALOG CONVERTER

### **FEATURES**

- 18-BIT MONOLITHIC AUDIO D/A CONVERTER

- LOW MAX THD + N: -92dB Without External Adjust

- 100% PIN COMPATIBLE WITH INDUSTRY STD 16-BIT PCM56P

- LOW GLITCH OUTPUT OF ±3V OR ±1mA

- CAPABLE OF 8X OVERSAMPLING RATE IN V<sub>OUT</sub> MODE

- COMPLETE WITH INTERNAL REFERENCE AND OUTPUT OP AMP

- RELIABLE PLASTIC 16-PIN DIP PACKAGE

### DESCRIPTION

The PCM61P is an 18-bit totally pin compatible performance replacement for the popular 16-bit PCM56P. With the addition of two extra bits, lower max THD+N (–92dB; PCM61P-K) can be achieved in audio applications already using the PCM56P. The PCM61P is complete with internal reference and output op amp and requires no external parts to function as an 18-bit DAC. The PCM61P is capable of an 8-times oversampling rate (single channel) and meets all of its specifications without an external output deglitcher.

The PCM61P comes in a small, reliable 16-pin plastic DIP package that has passed operating life tests under simultaneous high temperature, high humidity and high pressure testing.

## SPECIFICATIONS

#### ELECTRICAL

All specifications at 25°C, and +V  $_{CC}$  = +5V, unless otherwise noted.

|                                                        |                                                        | PC                        | CM61P-P, J-F   | , к        | UNITS                  |

|--------------------------------------------------------|--------------------------------------------------------|---------------------------|----------------|------------|------------------------|

| PARAMETER                                              | CONDITIONS                                             | MIN                       | TYP            | MAX        |                        |

| RESOLUTION                                             |                                                        |                           |                | 18         | Bits                   |

| DYNAMIC RANGE                                          |                                                        |                           | 108            |            | dB                     |

| DIGITAL INPUT                                          |                                                        |                           |                |            |                        |

| Logic Family                                           |                                                        |                           | CMOS Comp      | atible     |                        |

| Logic Level: V <sub>IH</sub>                           |                                                        | +2.4                      |                | +VL        | V                      |

| VIL                                                    |                                                        | 0                         |                | +0.8       | V                      |

| Iн                                                     | $V_{\rm IH} = +2.7V$                                   |                           |                | +1         | μΑ                     |

| I <sub>IL</sub><br>Data Format                         | $V_{IL} = +0.4V$                                       | Serial BTC <sup>(1)</sup> |                | -50        | μΑ                     |

| Input Clock Frequency                                  |                                                        | Senar Brow                |                | 16.9       | MHz                    |

| DYNAMIC CHARACTERISTICS                                |                                                        |                           |                |            |                        |

| Total Harmonic Distortion + N <sup>(2)</sup><br>PCM61P | Without MSB Adjustments                                |                           |                |            |                        |

| f = 991Hz (0dB) <sup>(3)</sup>                         | $f_{S} = 176.4 \text{kHz}^{(4)}$                       |                           | -88            | -82        | dB                     |

| f = 991Hz (-20dB)                                      | f <sub>S</sub> = 176.4kHz                              |                           | -74            | -68        | dB                     |

| f = 991Hz (-60dB)                                      | f <sub>S</sub> = 176.4kHz                              |                           | -34            | -28        | dB                     |

| PCM61P-J                                               |                                                        |                           | 0.4            |            |                        |

| f = 991Hz (0dB)                                        | $f_s = 176.4$ kHz                                      |                           | -94<br>-76     | 88<br>74   | dB<br>dB               |

| f = 991Hz (-20dB)<br>f = 991Hz (-60dB)                 | f <sub>S</sub> = 176.4kHz<br>f <sub>S</sub> = 176.4kHz |                           | -76<br>-36     | -74<br>-34 | dB                     |

| PCM61P-K                                               | IS = 170.4KΠZ                                          |                           | -30            | -34        | u D                    |

| f = 991Hz (0dB)                                        | f <sub>S</sub> = 176.4kHz                              |                           | -98            | -92        | dB                     |

| f = 991Hz (-20dB)                                      | $f_{\rm S} = 176.4$ kHz                                |                           | -80            | -74        | dB                     |

| f = 991Hz (-60dB)                                      | f <sub>s</sub> = 176.4kHz                              |                           | -40            | -34        | dB                     |

| IDLE CHANNEL SNR                                       | 20Hz to 20kHz at BPZ <sup>(5)</sup>                    |                           | 112            |            | dB                     |

| TRANSFER CHARACTERISTICS                               |                                                        |                           |                |            |                        |

| ACCURACY                                               |                                                        |                           |                |            |                        |

| Gain Error                                             |                                                        |                           | ±2             |            | %FSR                   |

| Bipolar Zero Error                                     |                                                        |                           | ±30            |            | mV                     |

| Differential Linearity Error                           |                                                        |                           | ±0.001         |            | %FSR                   |

| Total Drift <sup>(6)</sup>                             | 0°C to 70°C                                            |                           | ±25            |            | ppm of FSR/°           |

| Bipolar Zero Drift<br>Warm-up Time                     | 0°C to 70°C                                            | 1                         | ±4             |            | ppm of FSR/°<br>Minute |

| MONOTONICITY                                           |                                                        |                           | 16             |            | Bits                   |

| ANALOG OUTPUT                                          |                                                        |                           | 10             |            | DIIS                   |

| Voltage: Output Range                                  |                                                        |                           | ±3             |            | v                      |

| Output Current                                         |                                                        | ±2                        | <u>1</u> 3     |            | mA                     |

| Output Impedance                                       |                                                        | <u>+</u> 2                | 0.1            |            | Ω                      |

| Current: Output Range                                  | ±30%                                                   |                           | ±1             |            | mA                     |

| Output Impedance                                       | ±30%                                                   |                           | 1.2            |            | kΩ                     |

| SETTLING TIME                                          | To ±0.006% of FSR                                      |                           |                |            |                        |

| Voltage: 6V Step                                       |                                                        |                           | 1.5            |            | μs                     |

| 1 LSB                                                  |                                                        |                           | 1.0            |            | μs                     |

| Slew Rate                                              |                                                        |                           | 12             |            | V/µs                   |

| Current: 1mA Step                                      | 10 $\Omega$ to 100 $\Omega$ Load                       |                           | 250            |            | ns                     |

| 1mA Step                                               | 1kΩ Load                                               |                           | 350            |            | ns                     |

| Glitch Energy                                          | Meets all THD-                                         | N specs without           | external degli | tcning     | 1                      |

| POWER SUPPLY REQUIREMENTS <sup>(7)</sup>               |                                                        |                           |                |            |                        |

| ±V <sub>CC</sub> Supply Voltage                        |                                                        | ±4.75                     | ±5             | ±13.2      | V                      |

| Supply Current: +I <sub>CC</sub>                       | $+V_{CC} = +5V$                                        |                           | +10            | +17        | mA<br>mA               |

| +I <sub>CC</sub>                                       | +V <sub>CC</sub> = +12V<br>-V <sub>CC</sub> = -5V      |                           | +12<br>-25     | -35        | mA<br>mA               |

| I <sub>CC</sub>                                        | $-V_{CC} = -3V$<br>$-V_{CC} = -12V$                    |                           | -25<br>-27     | 55         | mA                     |

| Power Dissipation                                      | $\pm V_{CC} = \pm 5V$                                  |                           | 175            | 260        | mW                     |

|                                                        | $\pm V_{CC} = \pm 12V$                                 |                           | 475            |            | mW                     |

| TEMPERATURE RANGE                                      |                                                        |                           |                |            |                        |

| Specification                                          |                                                        | 0                         |                | +70        | °C                     |

| Operating                                              |                                                        | -30                       |                | +70        | °C                     |

| Storage                                                |                                                        | -60                       |                | +100       | °C                     |

NOTES: (1) Binary Two's Complement coding. (2) Ratio of (Distortion<sub>RMS</sub> + Noise<sub>RMS</sub>)/Signal<sub>RMS</sub>. (3) D/A converter output frequency/signal level. (4) D/A converter sample frequency (4 x 44.1kHz; 4 times oversampling). (5) Bipolar zero, using A-weighted filter. (6) This is the combined drift error due to gain, offset, and linearity over temperature. (7) All positive and all negative supply pins must be tied together respectively.

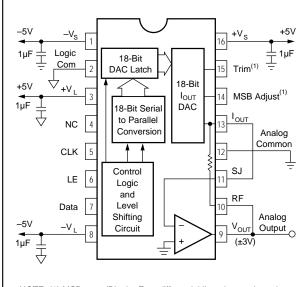

#### **PIN ASSIGNMENTS**

| PIN | FUNCTION         | DESCRIPTION             |

|-----|------------------|-------------------------|

| 1   | -V <sub>S</sub>  | Analog Negative Supply  |

| 2   | LOG COM          | Logic Common            |

| 3   | +VL              | Logic Positive Supply   |

| 4   | NC               | No Connection           |

| 5   | CLK              | Clock Input             |

| 6   | LE               | Latch Enable Input      |

| 7   | DATA             | Serial Data Input       |

| 8   | -V <sub>L</sub>  | Logic Negative Supply   |

| 9   | V <sub>OUT</sub> | Voltage Output          |

| 10  | RF               | Feedback Resistance     |

| 11  | SJ               | Summing Junction        |

| 12  | ANA COM          | Analog Common           |

| 13  | I <sub>OUT</sub> | Current Output          |

| 14  | MSB ADJ          | MSB Adjustment Terminal |

| 15  | TRIM             | MSB Trim-pot Terminal   |

| 16  | +V <sub>S</sub>  | Analog Positive Supply  |

#### **ABSOLUTE MAXIMUM RATINGS**

| DC Supply Voltages±16VDC                                 |

|----------------------------------------------------------|

| Input Logic Voltage1V to V <sub>S</sub> /+V <sub>1</sub> |

| Power Dissipation                                        |

| Operating Temperature Range –25°C to +70°C               |

| Storage Temperature Range60°C to +100°C                  |

| Lead Temperature (soldering, 10s) +300°C                 |

#### PACKAGE INFORMATION

| PRODUCT  | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|--------------------|------------------------------------------|

| PCM61P-P | 16-Pin Plastic DIP | 180                                      |

| PCM61P-J | 16-Pin Plastic DIP | 180                                      |

| PCM61P-K | 16-Pin Plastic DIP | 180                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

### ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

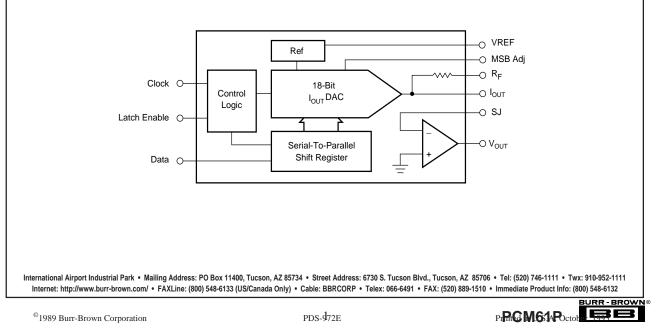

#### CONNECTION DIAGRAM

NOTE: (1) MSB error (Bipolar Zero differential linearity error) can be adjusted to zero using the external circuit shown in Figure 4.

| DIGITAL INPUT    | ANALOG OUTPUT |                       |                       |  |

|------------------|---------------|-----------------------|-----------------------|--|

| Binary Two's     | DAC Output    | Voltage (V)           | Current (mA)          |  |

| Complement (BTC) |               | V <sub>OUT</sub> Mode | I <sub>OUT</sub> Mode |  |

| 1FFFF Hex        | +FS           | -0.99999237           | +2.99997711           |  |

| 00000 Hex        | BPZ           | 0.00000000            | 0.00000000            |  |

| 3FFFF Hex        | BPZ – 1LSB    | +0.00000763           | -0.00002289           |  |

| 20000 Hex        | –FS           | +1.00000000           | -3.00000000           |  |

TABLE I. PCM61P Input/Output Relationships.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

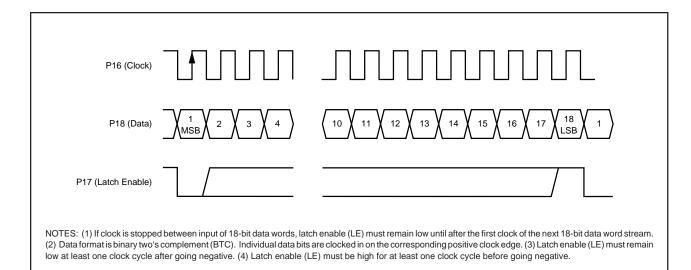

FIGURE 1. PCM61P Timing Diagram.

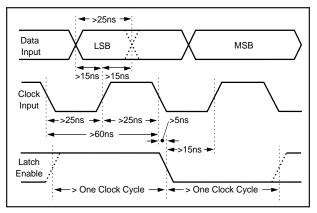

FIGURE 2. PCM61P Setup and Hold Timing Diagram.

#### MAXIMUM CLOCK RATE

The maximum clock rate of 16.9MHz for the PCM61P is derived by multiplying the standard audio sample rate of 44.1kHz times sixteen (16 x oversampling) times the standard audio word bit length of 24 (44.1kHz x 16 x 24 = 16.9MHz). Note that this clock rate accommodates a 24-bit word length, even though only 18 bits are actually being used.

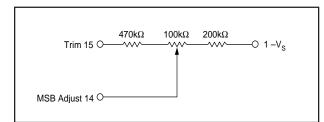

FIGURE 3. MSB Adjust Circuit.

#### MSB ERROR ADJUSTMENT PROCEDURE (OPTIONAL)

The MSB error of the PCM61P can be adjusted to make the differential linearity error (DLE) at BPZ essentially zero. This is important when the signal output levels are very low, because zero crossing noise (DLE at BPZ) becomes very significant when compared to the small code changes occurring in the LSB portion of the converter.

To statically adjust DLE at BPZ, refer to the circuit shown in Figure 3 or the PCM61P connection diagram.

Differential linearity error at bipolar zero and THD are guaranteed to meet data sheet specifications without any external adjustment. However, a provision has been made for an optional adjustment of the MSB linearity point, which makes it possible to eliminate DLE error at BPZ. Two procedures are given to allow either static or dynamic adjustment. The dynamic procedure is preferred because of the difficulty associated with the static method (accurately measuring 16bit LSB steps).

After allowing ample warm-up time (5-10 minutes) to assure stable operation of the PCM61P, select input code 3FFFF hexadecimal (all bits on except the MSB). Measure the output voltage using a 6-1/2 digit voltmeter and record it. Change the digital input code to 00000 hexadecimal (all bits off except the MSB). Adjust the 100k $\Omega$  potentiometer to make the output read 22.9µV more than the voltage reading of the previous code (a 1LSB step = 22.9µV). A much simpler method is to dynamically adjust the DLE at BPZ. Assuming the device has been installed in a digital audio application circuit, send the appropriate digital input to produce a –60dB level sinusoidal output, then adjust the 100k $\Omega$  potentiometer until a minimum level of distortion is observed.