## ANALOG DEVICES

# Precision Sample-and-Hold with 16-Channel Multiplexer

#### FEATURES

16 Single-Ended or 8 Differential Channels with Switchable Mode Control

True 12-Bit Precision: Nonlinearity ≤±0.005% High Speed: 10μs Acquisition Time to 0.01% Complete and Calibrated: No Additional Parts Required Small, Reliable: 32 Pin Hermetic Metal DIP

Versatile: Simple Interface to Popular Analog to Digital Converters

High Differential Input Impedance ( $10^{10}\Omega$ ) and Common Mode Rejection (80dB)

Fully Protected Multiplexer Inputs

### PRODUCT DESCRIPTION

The AD362 is a complete, precision 16-channel data acquisition system analog input section in hybrid integrated circuit form. Large-scale linear integrated circuitry, thick- and thinfilm technology and active laser trimming gives the AD362 extensive applications versatility along with full 12-bit accuracy.

The AD362 contains two 9-channel multiplexers, a differential amplifier, a sample-and-hold with high-speed output amplifier, a channel address latch and control logic. The multiplexers may be connected to the differential amplifier in either an 8-channel differential or 16-channel single-ended configuration. A unique feature of the AD362 is an internal user-controllable analog switch that connects the multiplexers in either a singleended or differential mode. This allows a single device to perform in either mode without hard-wire programming and permits a mixture of single-ended and differential sources to be interfaced by dynamically switching the input mode control.

The sample-and-hold mode control is designed to connect directly to the "Status" output of an analog to digital converter so that a convert command to the ADC will automatically put the sample-and-hold into the "Hold" mode. A precision hold capacitor is included with each AD362. The AD362 output amplifier is capable of driving the unbuffered analog input of most high-speed, 12-bit successive-approximation ADCs. Interface is thereby reduced to two simple connections with no additional components required.

When used with a 12-bit, 25-microsecond ADC such as the AD572, AD574 or AD ADC80, system throughput rate is as high as 30kHz at full rated accuracy. The AD362KD is specified for operation over a 0 to  $+70^{\circ}$ C temperature range while the

AD342SD operates to specification from -55°C to +125°C. Processing to MIL-STD-883, Class B is available for the AD162SD. Both grades are packaged in a hermetic, electrostatically shielded 32-pin metal dual-in-line package.

PRODUCT HIGHLIGHTS

- The AD362, when used with a precision analog to digital converter, forms a complete, accurate, high-speed data acquisition system.

- The 16-input channels may be configured in single ended, differential or a mixture of both modes. Mode switching is provided by a user-controllable internal analog switch.

- 3. Multiplexers, differential amplifier, sample-and-hold and high-speed output buffer provide complete analog interfacing capabilities.

- 4. Internal channel address latches are provided to facilitate interfacing the AD362 to data, address or control buses.

- All grades of the AD362 are hermetically sealed in rugged metal DIP packages.

- 6. A precision hold capacitor is provided with each AD362.

- 7. The AD362SD is specified over the entire military temperature range, -55°C to +125°C. Processing to MIL-STD-883, Class B is available.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Route 1 Industrial Park; P.O. Box 280; Norwood, Mass. 02062

Tel: 617/329-4700

TWX: 710/394-6577

West Coast

Mid-West

Texas

714/842-1717

312/894-3300

214/231-5094

**SPECIFICATIONS** (typical @ +25°C, ±15V and +5V with 2000pF hold capacitor as provided unless otherwise noted)

| MODEL                                                                                                 | AD362KD                                               | AD362SD/AD362SD-883B <sup>1</sup> |     |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------|-----|

| ANALOG INPUTS                                                                                         |                                                       |                                   |     |

| Number of Inputs                                                                                      | 16 Single-Ended or 8 Differential                     |                                   |     |

|                                                                                                       | (Electronically Selectable)                           | *                                 |     |

| Input Voltage Range, Linear                                                                           |                                                       |                                   |     |

| T <sub>min</sub> to T <sub>max</sub>                                                                  | ±10V min                                              | *                                 |     |

| Input (Bias) Current, Per Channel                                                                     | ±50nA max                                             |                                   |     |

| Input Impedance                                                                                       | 1010 0 100-E                                          |                                   |     |

| On Channel                                                                                            | 10 <sup>10</sup> Ω, 100pF<br>10 <sup>10</sup> Ω, 10pF | *                                 |     |

| Off Channel                                                                                           | 20mA, max, Internally Limited                         |                                   |     |

| Input Fault Current (Power Off or On)                                                                 | 20mA, max, internativ Emitted                         |                                   |     |

| Common Mode Rejection<br>Differential Mode                                                            | 70dB min (80dB typ) @ 1kHz, 20V p-p                   | •                                 |     |

| Mux Crosstalk (Interchannel,                                                                          | youb min (ooub typ) o min, oo y p p                   |                                   |     |

| Any Off Channel to Any On Channel                                                                     | ) -80dB max (-90dB typ) @ 1kHz, 20V p-p               | *                                 |     |

| Offset, Channel to Channel                                                                            | ±2.5mV max                                            | *                                 |     |

| ACCUBACY                                                                                              |                                                       |                                   |     |

|                                                                                                       | ±0.02% FSR, max                                       | *                                 |     |

| Gain Error, T <sub>min</sub> o T <sub>max</sub><br>Offset Error, T <sub>min</sub> to T <sub>max</sub> | ±4mV                                                  | •                                 |     |

| Linearity Error                                                                                       | <u>±0.005</u> % max                                   | *                                 |     |

| T <sub>min</sub> to T <sub>max</sub>                                                                  | ±0.01% max                                            | *                                 |     |

| Noise Error                                                                                           | InV pp, 0.1 to 1MHz, max                              | •                                 |     |

| Tmb to Tmax                                                                                           | 2mV p-p, 0.1 to 1MHz max                              | *                                 |     |

| TEMPERATURE COEFFICIENTS                                                                              | $ \setminus / / ) / / $                               | * _                               |     |

| Gain, $T_{min}$ to $T_{max}$                                                                          | t4ppm/°C max                                          | ±2ppm/°C max                      |     |

| Offset, ±10V Range, T <sub>min</sub> to T <sub>max</sub>                                              | ±2ppm °C max                                          | ±1.5ppm/°Gmax                     |     |

| SAMPLE AND HOLD DYNAMICS                                                                              |                                                       |                                   | 7 ~ |

| Aperture Delay                                                                                        | 100ns max (50ns typ)                                  |                                   |     |

| Aperture Uncertainty                                                                                  | 500ps max (100ps typ)                                 |                                   |     |

| Acquisition Time, for 20V Step to                                                                     |                                                       |                                   |     |

| ±0.01% of Final Value                                                                                 | 18μs max (10μs typ)                                   | * 7 //                            |     |

| Feedthrough                                                                                           | -70dB max (-80dB typ) @ 1kHz                          | * 1 []                            |     |

| Droop Rate                                                                                            | 2mV/ms max (1mV/ms typ)                               | *                                 |     |

| DIGITAL INPUT SIGNALS <sup>2</sup>                                                                    |                                                       |                                   |     |

| Input Channel Select (Pins 28-31)                                                                     | 4-Bit Binary, Channel Address                         | *                                 |     |

|                                                                                                       | 1LS TTL Load                                          | •                                 |     |

| Channel Select Latch (Pin 32)                                                                         | "1": Latch Transparent                                | •                                 |     |

|                                                                                                       | "0": Latched                                          | *                                 |     |

|                                                                                                       | 8LS TTL Loads                                         | *                                 |     |

| Single Ended/Differential                                                                             | "0": Single-Ended Mode                                | *                                 |     |

| Mode Select (Pin 1)                                                                                   | "1": Differential Mode                                | •                                 |     |

|                                                                                                       | 3TTL Loads                                            | *                                 |     |

| Sample and Hold Command (Pin 13)                                                                      | "0": Sample Mode                                      |                                   |     |

| cample and fiold command (fin 15)                                                                     | "1": Hold Mode                                        |                                   |     |

|                                                                                                       | 1TTL Load                                             | *                                 |     |

| POWER REQUIREMENTS                                                                                    |                                                       |                                   |     |

| Supply Voltages/Currents                                                                              | +15V, ±5% @ 30mA max                                  |                                   |     |

| Supply voltages/Guitents                                                                              | $-15V, \pm 5\%$ @ 30mA max                            | *                                 |     |

|                                                                                                       | +5V, ±5% @ 40mA max                                   |                                   |     |

| Total Bower Dissingtion                                                                               |                                                       | *                                 |     |

| Total Power Dissipation                                                                               | 1.1 Watts max                                         | -                                 |     |

| TEMPERATURE RANGE                                                                                     | 9 -                                                   | 0 - 0                             |     |

| Specification                                                                                         | $0 \text{ to } +70^{\circ}\text{C}$                   | -55°C to +125°C                   |     |

| Storage                                                                                               | $-55^{\circ}C$ to $+85^{\circ}C^{3}$                  | -55°C to +150°C                   |     |

NOTES: <sup>1</sup> The AD362 is available full; processed and screened to the requirements of MIL-STD-883, Class B. A complete list of tests is given on page 3. When ordering, specify "AD362SD/883B". <sup>2</sup> One TTL Load is defined as  $I_{IL} = -1.6mA$  max @  $V_{IL} = 0.4V$ ,  $I_{IH} = 40\muA$  max @  $V_{IH} = 2.4V$ . One LS TTL Load is defined as  $I_{IL} = -0.36mA$  max @  $V_{IL} = 0.4V$ ,  $I_{IH} = 20\muA$  max @  $V_{IH} = 2.7V$ . <sup>3</sup> AD362KD External Hold Capacitor is limited to +85°C; AD362 device itself may be stored at up to +150°C.

Specifications subject to change without notice.

| ABSOLUTE                                                                                                 | MAXIMUM RATINGS                                         |                     | AD362 PIN FUNCTION DESCRIPTION                                                             |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------|

| (A                                                                                                       | LL MODELS)                                              | Pin                 |                                                                                            |

| +V, Digital Supply                                                                                       | +5.5V                                                   | Number              | Function                                                                                   |

| +V, Analog Supply                                                                                        | +16V                                                    |                     |                                                                                            |

| -V, Analog Supply                                                                                        | -16V                                                    | 1                   | Single-End/Differential Mode Select                                                        |

|                                                                                                          |                                                         |                     | "0": Single-Ended Mode<br>"1": Differential Mode                                           |

| V <sub>IN</sub> , Signal                                                                                 | ±V, Analog Supply                                       | 2                   | Digital Ground                                                                             |

| V <sub>IN</sub> , Digital                                                                                | 0 to +V, Digital Supply                                 | 2 3                 | Positive Digital Power Supply, +5V                                                         |

| AGND to DGND                                                                                             | ±1V                                                     | 4                   | "High" Analog Input, Channel 7                                                             |

| 1 Known arabid (All and an                                           |                                                         | 5                   | "High" Analog Input, Channel 6                                                             |

| PROCESSING I                                                                                             | FOR HIGH RELIABILITY                                    | 6                   | "High" Analog Input, Channel 5                                                             |

|                                                                                                          |                                                         |                     | "High" Analog Input, Channel 4                                                             |

| STAND                                                                                                    | ARD PROCESSING                                          | 7 8                 | "High" Analog Input, Channel 3                                                             |

| $\frown$                                                                                                 |                                                         | 9                   | "High" Analog Input, Channel 2                                                             |

| As part of the standard manufacturing procedure, all models of the AD362 needs the following processing: |                                                         |                     | "High" Analog Input, Channel 1                                                             |

| LD302 Reelve the ronowi                                                                                  | ng processing:                                          | 10<br>11            | "High" Analog Input, Channel 0                                                             |

| PROCESS                                                                                                  | CONDITIONS                                              | 12                  | Hold Capacitor (Provided)                                                                  |

|                                                                                                          | $ \sum ( \cap ) $                                       | 13                  | Sample-Hold Command                                                                        |

| 1) 100% pre-cap Visual<br>Inspection                                                                     | In touse Cliteria                                       |                     | "0": Sample Mode                                                                           |

| $\sim$ $1$ L                                                                                             | 24 hours = 150 %                                        | $\setminus \square$ | "1": Hold Mode                                                                             |

| <ol> <li>Stabilization Bake</li> <li>Seal Test, Gross Leak</li> </ol>                                    | 24 hours @ 150 C<br>Method 1014 Test Condition C        |                     | Normally Connected to ADC Status                                                           |

| <ol> <li>Seal Test, Gross Leak</li> <li>Operating Burn-In</li> </ol>                                     | 24 hours &+125°C                                        | 14/                 | Offset Adjust (See Figure 5)                                                               |

| 4) Operating Burn-In                                                                                     | 24 110013 60 125 0                                      | 15                  | Offset Adjust (See Figure 5)                                                               |

|                                                                                                          |                                                         | 16                  | Analog Output                                                                              |

| PROCESS                                                                                                  | NG TO MIL-STD-883                                       |                     | Normally Connected to ADC                                                                  |

|                                                                                                          |                                                         |                     | "Andlog In"                                                                                |

|                                                                                                          | the requirements of MIL-STD-883.                        | 17<br>18            | Analog Ground                                                                              |

| Method 5008 are identified with a /883B suffix and receive the ollowing processing:                      |                                                         |                     | "High" ("Low") Analog Input, Channel 15 (7)                                                |

|                                                                                                          |                                                         | 19                  | "High" ("Low") Analog Input, Channel 14 (6)                                                |

| ROCESS                                                                                                   | CONDITIONS                                              | 20                  | Negative Analog Power Supply, -15V                                                         |

| ) 100% pre-cap Visual                                                                                    | 2017.1                                                  | 21 22               | Positive Analog Power Supply, +15V                                                         |

| Inspection                                                                                               |                                                         | 22                  | "High" ("Low") Analog Input, Channel 13 (5)<br>"High" ("Low") Analog Input, Channel 12 (4) |

| ) Stabilization Bake                                                                                     | 1008, 24 hours @ +150°C                                 | 23                  | "High" ('Low') Analog Input, Channel 12 (4)<br>"High" ("Low") Analog Input, Channel 11 (3) |

| ) Temperature Cycle                                                                                      | 1010, Test Condition C, 10 cycles,                      | 24                  | "High" ("Low") Analog Input, Channel 11 (5)                                                |

|                                                                                                          | -65°C to +150°C                                         | 26                  | "High" ("Low") Analog Input, Channel 10 (2)                                                |

| ) Constant Acceleration                                                                                  | 2001, Y1 Plane, 1000G                                   | 20                  | "High" ("Low") Analog Input, Channel 8 (0)                                                 |

| ) Visual Inspection                                                                                      | Visable Damage                                          | 28                  | Input Channel Select, Address Bit AE                                                       |

| ) Operating Burn-In                                                                                      | 1015, Test Condition B 160 hours @<br>+125°C            | 29                  | Input Channel Select, Address Bit AD                                                       |

| ) Seal Test: Fine Leak                                                                                   | 1014, Test Condition A, 5 x 10 <sup>-7</sup> std cc/sec | 30                  | Input Channel Select, Address Bit Al                                                       |

| Gross Leak                                                                                               | 1014, Condition C                                       | 31                  | Input Channel Select, Address Bit A2                                                       |

| ) Final Electrical Test                                                                                  | Per Data Sheet                                          | 32                  | Input Channel Select Latch                                                                 |

| ) External Visual Inspection                                                                             | 2009                                                    |                     | "0": Latched                                                                               |

|                                                                                                          |                                                         | 1                   | "1": Latch Transparent                                                                     |

#### AD362 ORDERING GUIDE

|          | Specification                       | Max Gain | Prices   |          |          |  |  |

|----------|-------------------------------------|----------|----------|----------|----------|--|--|

| Model    | Temp Range                          | TC       | (1-24)   | (25-99)  | (100+)   |  |  |

| AD362KD  | $0 \text{ to } +70^{\circ}\text{C}$ | ±4ppm/°C | \$160.00 | \$139.50 | \$119.50 |  |  |

| AD362SD  | -55°C to +125°C                     | ±2ppm/°C | \$295.00 | \$270.00 | \$230.00 |  |  |

| AD362SD/ | $-55^{\circ}$ C to $+125^{\circ}$ C | ±2ppm/°C | \$365.00 | \$330.00 | \$280.00 |  |  |

| 883B     |                                     |          |          |          |          |  |  |

NOTE: D Suffix = Dual-In-Line package designator.

#### AD362 DESIGN

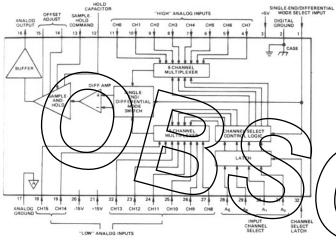

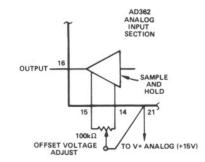

The AD362 consists of two 8-channel multiplexers, a differenial amplifier, a sample-and-hold with high-speed output bufier, channel address latches and control logic as shown in Figure 1. The multiplexers can be connected to the differential implifier in either an 8-channel differential or 16-channel single-ended configuration. A unique feature of the AD362 is in internal analog switch controlled by a digital input that performs switching between single-ended and differential nodes. This feature allows a single AD362 to perform in either mode without external hard-wire interconnections. Of more significance is the ability to serve a mixture of both single-ended and differential sources with a single AD362 by dynamically switching the input mode control.

Figure 1. AD362 Analog Input Section Functional Block Diagram and Pinout

Multiplexer channel address inputs are interfaced through a level-triggered ("transparent") input register. With a Logic "1" at the Channel Select Latch input, the address signals feed through the register to directly select the appropriate input channel. This address information can be held in the register by placing a Logic "0" on the Channel Select Latch input. Internal logic monitors the status of the Single-Ended/Differential 10de input and addresses the multiplexers accordingly.

. differential amplifier buffers the multiplexer outputs while roviding high input impedance in both differential and singlended modes. Amplifier gain and common mode rejection are etively laser-trimmed.

The sample-and-hold is a high speed monolithic device that can also function as a gated operational amplifier. Its uncommitted differential inputs allow it to serve a second role as the output subtractor in the differential amplifier. This eliminates one amplifier and decreases drift, settling time and power consumption. A Logic "1" on the Sample-and-Hold Command input will cause the sample-and-hold to "freeze" the analog signal while the ADC performs the conversion. Normally the Sampleand-Hold Command is connected to the ADC Status output which is at Logic "1" during conversion and Logic "0" between conversions. For slowly-changing inputs, throughput speed may be increased by grounding the Sample-and-Hold Command input instead of connecting it to the ADC status.

A Polystyrene hold capacitor is provided with each commercial temperature range device (AD362KD) while a Teflon capacitor is provided with units intended for operation at temperatures up to  $125^{\circ}$ C (AD362SD). Use of an external capacitor allows the user to make his own speed/accuracy tradeoff; a smaller capacitor will allow faster sample-and-hold response but will decrease accuracy while a larger capacitor will increase accuracy at slower conversion rates.

The output buffer is a high speed amplifier whose output impedance remains low and constant at high frequencies. Therefore, the AD362 may drive a fast, unbuffered, precision ADC without loss of accuracy.

The AD362 is constructed on a substrate that includes thickfilm resistors for non-critical applications such as input protection and biasing. A separately-mounted laser-trimmed thinfilm resistor network is used to establish accurate gain and high common-mode rejection. The metal package affords electromagnetic and electrostatic shielding and is hermetically welded at low temperatures. Welding eliminates the possibility of contamination from solder particles or flux while low temperature sealing maintains the accuracy of the laser-trimmed thin-film resistors.

#### THEORY OF OPERATION Concept

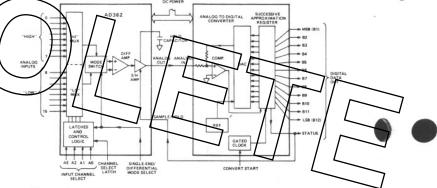

The AD362 is intended to be used in conjunction with a highspeed precision analog-to-digital converter to form a complete data acquisition system (DAS) in microcircuit form. Figure 2 shows a general AD362-with-ADC DAS application.

#### Figure 2. AD362 with ADC as a Complete Data Acquisition System

By dividing the data acquisition task into two sections, several important advantages are realized. Performance of each design is optimized for its specific function. Production yields are increased thus decreasing costs. Furthermore, the standard configuration packages plug into standard sockets and are easier to handle than larger packages with higher pin counts.

#### System Timing

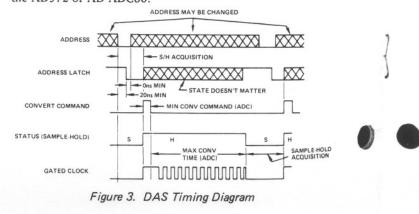

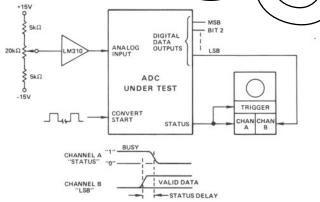

Figure 3 is a timing diagram for the AD362 connected as shown in Figure 2 and operating at maximum conversion rate. The ADC is assumed to be a conventional 12 bit type such as the AD572 or AD ADC80.

## Applying the Automation

The normal sequence of events is as follows:

- 1. The appropriate Channel Select Address is latched into the address register. Time is allowed for the multiplexers to settle.

- A Convert Start command is issued to the ADC which, in response, indicates that it is "busy" by placing a Logic "1" on its Status line.

- 3. The ADC Status controls the sample-and-hold. When the ADC is "busy", the sample-and-hold is in the Hold mode.

- 4. The ADC goes into its conversion routine. Since the sampleand-hold is holding the proper analog value, the address may be updated during conversion. Thus multiplexer settling time can coincide with conversion and need not affect throughput rate.

- The ADC indicates completion of its conversion by returning Status to Logic "0". The sample-and-hold returns to the Sample mode.

6. If the input signal has changed full-scale (different channels may have widely-varying data) the sample-and-hold will spically require 10 microseconds to "acquire" the next input to sufficient accuracy for 12 bit conversion

After allowing a suitable interval for the sample and hold to stabilize at its new value, another Convert Start command may be issued to the ADC.

Figure 4. ADC Status Valid Test

#### NOTE:

#### Valid Output Data

Not all ADCs have all data bits available when Status indicates that the conversion is complete. Successive approximation ADCs based on the 2502/3/4 type of register must have a Status delay built in or the final data bit will lag Status by approximately 50ns. This will result in two problems:

- 1. The sample-and-hold will return to Sample, disturbing the analog input to the ADC as it is attempting to convert the least significant bit. This may result in an error.

- 2. If the falling edge of Status is being used to load the data into a register, the least significant bit will not be valid when loaded.

An external 100ns delay or use of an ADC with a valid Status output is necessary to prevent this problem. The applications shown in this data sheet ensure that all data bits will be valid.

The following test may be made to determine if the ADC Status timing is correct:

1. Connect the ADC under test as shown in Figure 4.

- 2. Trigger the oscilloscope on Status. Delay the display such that Status is mid-screen.

- 3. Observe the LSB data output of the ADC.

- 4. Vary the analog input control to confirm that the LSB transition precedes the Status transition.

#### Single-Ended/Differential Mode Control

The AD362 features an internal analog switch that configures the Analog Input Section in either a 16-channel single-ended or 8-channel differential mode. This switch is controlled by a TTL logic input applied to pin 1 of the Analog Input Section:

"0": Single-Ended (16 channels) "1": Differential (8 channels)

When in the differential mode, a differential source may be applied between corresponding "High" and "Low" analog

It is possible to mix SE and DIFF inputs by using the mode control to command the appropriate mode. In this case, four microseconds must be allowed for the output of the Analog Input Section to settle to within  $\pm 0.01\%$  of its final value, but if the mode is switched concurrent with changing the channel address, no significant additional delay is introduced. The effect of this delay may be eliminated by changing modes while a conversion is in progress (with the sample-and-hold in the 'Hold'' mode). When SE and DIFF signals are being processed concurrently, the DIFF signals must be applied between corresponding "High" and "Low" analog input chanricls. Another application of this feature is the capability of measuring 16 sources individually and or measuring differences between pairs of those sources.

#### Input Channel Addressing

input channels.

Table 1 is the truth table for input channel addressing in both the single-ended and differential modes. The 16 single-ended channels may be addressed by applying the corresponding digital number to the four Input Channel Select address bits, AE, AO, A1, A2 (pins 28-31). In the differential mode, the eight channels are addressed by applying the appropriate digital code to AO, A1 and A2; AE must be enabled with a Logic "1". Internal logic monitors the status of the SE/DIFF Mode input and addresses the multiplexers singularly or in pairs as required.

| ADDRESS |    |    | S  | ON CHANNEL (Pin Number) |      |      |         |       |      |

|---------|----|----|----|-------------------------|------|------|---------|-------|------|

|         |    |    |    | Differer                |      |      | ifferen | ntial |      |

| AE      | A2 | A1 | A0 | Single Ended            |      | "1   | li"     | "Lo"  |      |

| 0       | 0  | 0  | 0  | 0                       | (11) |      | None    |       |      |

| 0       | 0  | 0  | 1  | 1                       | (10) | None |         |       |      |

| 0       | 0  | 1  | 0  | 2                       | (9)  | None |         |       |      |

| 0       | 0  | 1  | 1  | 3                       | (8)  | None |         |       |      |

| 0       | 1  | 0  | 0  | 4                       | (7)  | None |         |       |      |

| 0       | 1  | 0  | 1  | 5                       | (6)  | None |         |       |      |

| 0       | 1  | 1  | 0  | 6                       | (5)  | None |         |       |      |

| 0       | 1  | 1  | 1  | 7                       | (4)  | None |         |       |      |

| 1       | 0  | 0  | 0  | 8                       | (27) | 0    | (11)    | 0     | (27) |

| 1       | 0  | 0  | 1  | 9                       | (26) | 1    | (10)    | 1     | (26) |

| 1       | 0  | 1  | 0  | 10                      | (25) | 2    | (9)     | 2     | (25) |

| 1       | 0  | 1  | 1  | 11                      | (24) | 3    | (8)     | 3     | (24) |

| 1       | 1  | 0  | 0  | 12                      | (23) | 4    | (7)     | 5     | (23) |

| 1       | 1  | 0  | 1  | 13                      | (22) | 5    | (6)     | 5     | (22) |

| 1       | 1  | 1  | 0  | 14                      | (19) | 6    | (5)     | 6     | (19) |

| 1       | 1  | 1  | 1  | 15                      | (18) | 7    | (4)     | 7     | (18) |

Table 1. Input Channel Addressing Truth Table

When the channel address is changed, six microseconds must be allowed for the Analog Input Section to settle to within  $\pm 0.01\%$  of its final output (including settling times of all elements in the signal path). The effect of this delay may be eliminated by performing the address change while a conversion is in progress (with the sample-and-hold in the "Hold" mode).

#### Input Channel Address Latch

The AD362 is equipped with a latch for the Input Channel Select address bits. If the Latch Control pin (pin 32) is at Logic "1", input channel select address information is passed through to the multiplexers. A Logic "0" "freezes" the input channel address present at the inputs at the "1"-to-"0" transition (level-triggered).

This feature is useful when input channel address information is provided from an address, data or control bus that may be required to service many devices. The ability to latch an address is helpful whenever the user has no control of when address information may change.

#### Sample and Hold Mode Control

The Sample-and-Hold Mode Control input (pin 13) is normally connected to the Status output (pin 20) from an analog to digital converter. When a conversion is initiated by applying a Convert Start command to the ADC, Status goet to Dogid "1" putting the sample-and-hold into the "Hold" mode. This "freezes" the information to be digitized for the period of conversion. When the conversion is complete, Statu returns to Logic "0" and the sample-and-hold returns to the "Sample" mode. Eighteen microseconds must be allowed for the sampleand-hold to acquire ("catch up" to) the analog input to within ±0.01% of the final value before a new Convert Start command is issued.

The purpose of a sample-and-hold is to "stop" fast changing input signals long enough to be converted. In this application, it also allows the user to change channels and/or SE/ DIFF mode while a conversion is in progress thus eliminating the effects of multiplexer, analog switch and differential amplifier settling times. If maximum throughput rate is required for slowly changing signals, the Sample-and-Hold Mode Control may be wired to ground (Logic "0") rather than to ADC Status thus leaving the sample-and-hold in a continuous Sample mode.

#### Iold Capacitor

A 2000pF capacitor is provided with each AD362. One side of this capacitor is wired to pin 12, the other to analog ground as close to pin 17 as possible. The capacitor provided with the AD362KD is Polystyrene while the wider operating temperature range of the AD362SD requires a Teflon capacitor (supplied).

Smaller capacitors will allow slightly faster operation, but only with increased noise and decreased precision. 1000pF will typically allow acquisition to 0.1% in four microseconds.

Larger capacitors may be substituted to reduce noise, and sample-to-hold offset, but acquisition time of the sample-andhold will be extended. If less than 12 bits of accuracy is required, a smaller capacitor may be used. This will shorten the S/H acquisition time. In all cases, the proper capacitor dielectric must be used; i.e., Polystyrene (AD326KD only) or Teflon (AD362KD or SD). Other types of capacitors may have higher dielectric absorption (memory) and will cause errors. CAUTION: Polystyrene capacitors will be destroyed if subjected to temperatures above +85° C. No capacitor is required if the sample-and-hold is not used.

#### Analog Input Section Offset Adjust Circuit

Although the offset voltage of the AD362 may be adjusted, that adjustment is normally performed at the ADC. In some special applications, however, it may be helpful to adjust the offset of the Analog Input Section. An example of such a case would be if the input signals were small (<10mV) relative to AD362 voltage offset and gain was to be inserted between the AD362 and the ADC. To adjust the offset of the AD362, the circuit shown in Figure 5 is recommended.

#### Figure 5. AD362 Offset Voltage Adjustment

Under normal conditions, all calibration is performed at the ADC Section.

#### Other Considerations

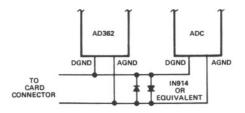

Grounding: Analog and digital signal grounds should be kept separate where possible to prevent digital signals from flowing in the shalog ground circuit and inducing spurious analog signal noise. Analog Ground (pin 17) and Digital Ground (pin 2) are not connected internally these pins must be connected externally for the system to operate properly. Preferably, this connection is made at only one point, as close to the AD\$62 as possible. The case is connected internally to Digital Ground to provide good electrostatic shielding. If the grounds are not tied common on the same card with the AD362, the digital and analog grounds should be connected locally with back-to back general-purpose diodes as shown in Figure 6. This will protect the AD362 from possible damage caused by voltages in excess of  $\pm 1$  volt between the ground systems which could occur if the key grounding card should be removed from the overall system. The device will operate properly with as much as ±200mV between grounds, however this difference will be reflected directly as an input offset voltage.

**Power Supply Bypassing:** The  $\pm 15$ V and  $\pm 5$ V power leads should be capacitively bypassed to Analog Ground and Digital Ground respectively for optimum device performance. 1 $\mu$ F tantalum types are recommended; these capacitors should be located close to the system. It is not necessary to shunt these capacitors with disc capacitors to provide additional high frequency power supply decoupling since each power lead is bypassed internally with a 0.039 $\mu$ F ceramic capacitor.

Interfacing to Popular Analog to Digital Converters Figure 7a shows the AD362 driving an AD ADC80. The The AD362 has been designed to interface directly to most AD ADC80 is a 12-bit, 25-microsecond, low-cost ADC that analog to digital converters; often no additional components meets all of the requirements listed above. Throughput rate are required and only two interconnections must be made. is typically 30kHz with no missing codes over the operating The direct interface requirements for the ADC are as follows: temperature range. Figure 7b shows a 10-bit application based on the AD362 and 1. The ADC Status output must be positive-true Logic ("1" the AD571, a complete low cost 10-bit, 25-microsecond ADC. during conversion). In this case, two of the above requirements are not met: 2. Transition from "0" to "1" must occur at least 200ns 1. DR (DATA READY), as Status, is positive-true but. . . before the most significant bit decision is made (successive approximation ADC) or before input integration starts 2. DR does not indicate that a conversion is in progress until (integrating type ADC). 1.5µs after conversion starts. 3. Status must not return to "0" before the LSB decision is 3. DR does indicate conversion complete after the LSB decimade (see page 5). sion is made, but, . . 4. If Status is being used to latch output data, it must not 4. DR precedes the enabling of the AD571 output 3-state return to Logic "0" until all output data bits are valid and gates by 500ns. available. The gating provided by U1 allows the applied convert comthroughput performance is determined by mand (CC) to initiate input hold at the AD362. CC must last Complete sy tem -case specifications of the AD362 and the for more than 1.5 $\mu$ s so that  $\overline{DR}$  may then assume control combining the worst of Hold. If conversion is continuous (consistent with multiformance is required, the AD C. If guaranteed channel operation), the next convert command can be used to AD363 and AD364 ecommended. The AD363 includes ar -bit, 25-mi oad the previously-converted data into an output register. For AD362 and an AD572 12 crosecond precision an single conversion operation, a  $1\mu$ s delay of the falling edge of ADC. The AD364 consists 2 and an D574 12-bit, an AD1 DR may be used to signify valid data. microprocessor-compatible, low co t ADC. Each pecified as a complete, two-package system; data sheets vailable upon request. DC POWER DC POWER HOLD APACIT £ ANALOG AD362 AD571 ANALOG ANALOG (16) IN DATA BITS OUT (12) SAMPLE/HOLD DR ANALOG INPUTS B&C AD362 AD ADC80 ANALOG ANALOG OUT IN (16) INPUT CHANNEL SAMPLE/HOLD STATUS OUTPUT SELECT SELECT (4) 1/4 74LS32 CONVERT O Л CHANNEL U1 DAT ASTROBE SELECT CONVERT SELEC (TO OUTPUT REGISTER) 1.5µs MIN DATA STROBE (TO OUTPUT REGISTER)

a. 12-Bit DAS Using AD362 and AD ADC80

b. 10-Bit DAS Using AD362 and AD571

Figure 7. Data Acquisition Systems Based on the AD362 and Popular ADC's

#### Interfacing to Special Purpose ADCs

The AD5200 series of ADCs perform a 12-bit conversion in 50 microseconds and feature totally adjustment-free operation, high accuracy, and a small hermetically-sealed 24-pin package.

These ADCs are often used in high-reliability applications and, like the AD362SD (which operates over the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range) are available processed to MIL-STD-883, Class B. The AD5200 series meets all of the interfacing requirements for direct connection to the AD362 as shown in Figure 8a. System throughput rate is typically 16kHz. The HAS series of ultra-fast ADCs are 8-bit (HAS0801), 10bit (HAS1001) and 12-bit (HAS1202) devices that convert in 1.5, 1.7, and 2.8 microseconds (maximum) respectively. These devices are hybrid IC's, packaged in 32-pin DIPs. Since the Data Ready signal from the HAS precedes the LSB decision, DR must be delayed. Figure 8b shows the appropriate circuitry to provide that delay. Throughput rate for the 12-bit system is typically 80kHz.

-8-