EVALUATION KIT

# AVAILABLE High-Voltage, Micropower, Single/Dual **Linear Regulators with Supervisory Functions**

### **General Description**

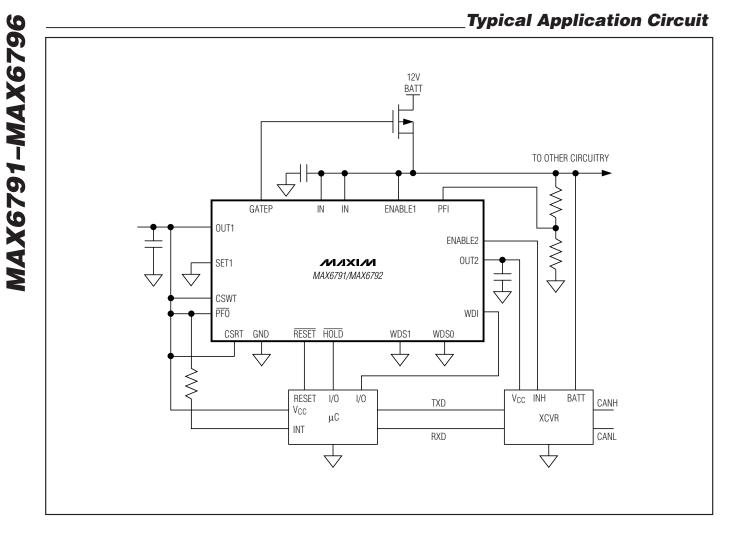

The MAX6791-MAX6796 ultra-low-guiescent-current, single-/dual-output linear regulators are ideal for automotive applications. The devices offer a wide 5V to 72V operating input range, allowing them to withstand automotive load-dump conditions while consuming only 68µA. The MAX6791-MAX6794 are dual-output regulators capable of supplying up to 150mA per output. The MAX6795/MAX6796 offer a single output capable of delivering up to 300mA. These devices offer standard output-voltage options (5V, 3.3V, 2.5V, or 1.8V) and can be adjusted to any voltage from 1.8V to 11V. The MAX6791–MAX6794 also offer a fixed 5V output.

All devices feature a push-pull or open-drain, active-low RESET output with a fixed output reset threshold that is 92.5%/87.5% of the regulator output OUT/OUT1. The reset output asserts low when OUT/OUT1 drops below the reset threshold and remains low for the fixed or capacitor-adjustable reset timeout period after OUT/OUT1 exceeds the reset threshold.

The MAX6791–MAX6796 provide a watchdog input that monitors a pulse train from the microprocessor ( $\mu$ P) and generates reset pulses if the watchdog input remains high or low for a duration longer than the watchdog timeout period. All devices are available with either a fixed watchdog timeout period of 280ms (min) or a period adjustable with an external capacitor. The MAX6791/MAX6792 feature a windowed watchdog timeout period with selectable window ratio. The watchdog feature can be disabled.

The MAX6791–MAX6794 provide dual enable inputs (ENABLE1 and ENABLE2) that control each regulator independently. The single-output MAX6795/MAX6796 feature one enable input (ENABLE).

All devices include a hold input (HOLD) that aids the implementation of a self-holding circuit without requiring external components. Once the regulator is enabled, setting HOLD low forces the regulator to remain on even if ENABLE/ENABLE1 is subsequently set low. Releasing HOLD shuts down the regulator.

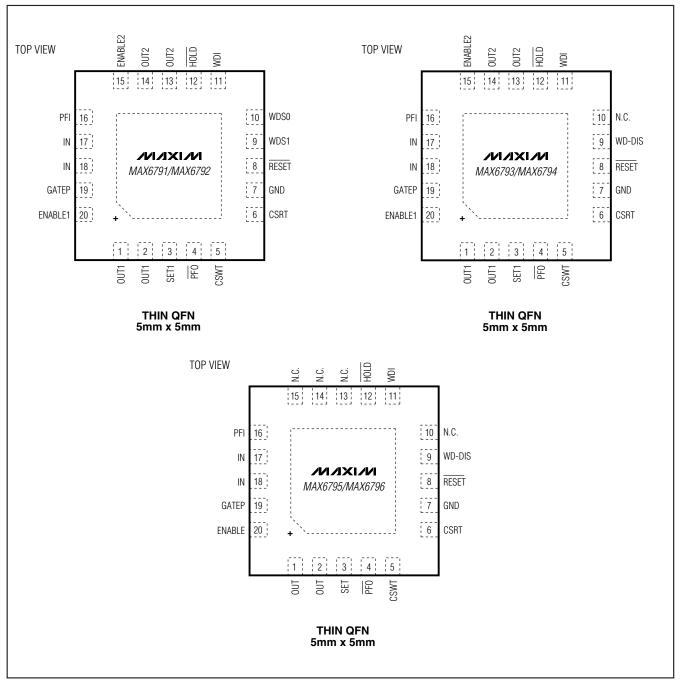

The MAX6791-MAX6796 are available in a small, thermally enhanced TQFN package. The 5mm x 5mm package dissipates up to 2.7W, supporting continuous regulator operation during high ambient temperatures, high battery voltage, and high load-current conditions.

The MAX6791-MAX6796 are specified for a -40°C to +125°C operating temperature range.

Automotive

#### Features

- Low 68µA Quiescent Current

- Wide 5V to 72V Supply Voltage Range

- Output Current Single Output Up to 300mA Dual Outputs Up to 150mA per Output

- Low Dropout Voltage 420mV (typ) at 100mA (Single) 840mV (typ) at 100mA (Dual)

- Fixed Output-Voltage Options: 5V, 3.3V, 2.5V, 1.8V, or Adjustable Output (from 1.8V to 11V)

- ENABLE and HOLD Functionality

- RESET Output: Open Drain or Push-Pull

- Internally Fixed (35µs, 3.125ms, 12.5ms, 50ms, or 200ms) or Capacitor-Ádjustable Reset Timeout Periods

- Internally Fixed or Capacitor-Adjustable Watchdog Timeout Periods

- Windowed (Minimum/Maximum) Watchdog Timer Options (MAX6791/MAX6792)

- Watchdog Disable Feature

- Thermal, Short-Circuit, and Output Overvoltage Protection

- Fully Specified from -40°C to +125°C

- Small, Thermally Enhanced, 5mm x 5mm TQFN

### **Ordering Information**

| PART             | TEMP RANGE      | PIN-PACKAGE |

|------------------|-----------------|-------------|

| MAX6791TP_D _+   | -40°C to +125°C | 20 TQFN-EP* |

| MAX6792TP_D _+   | -40°C to +125°C | 20 TQFN-EP* |

| MAX6793TP_D_+    | -40°C to +125°C | 20 TQFN-EP* |

| MAX6794TP_D_+    | -40°C to +125°C | 20 TQFN-EP* |

| MAX6795TP_D_+    | -40°C to +125°C | 20 TQFN-EP* |

| MAX6795TP_D _/V+ | -40°C to +125°C | 20 TQFN-EP* |

| MAX6795TPSD2/V+  | -40°C to +125°C | 20 TQFN-EP* |

| MAX6796TP_D _+   | -40°C to +125°C | 20 TQFN-EP* |

+Denotes lead-free package.

For tape-and-reel, add a T after the "+." Tape-and-reel are offered in 2.5k increments. The first placeholder "\_" designates preset output-voltage option and preset reset threshold level; see Table 1. The second placeholder "\_ " designates the reset timeout period; see Table 2. For example, the MAX6791TPSD3+ indicates a 3.3V output voltage with a reset threshold of 87.5% at nominal voltage and a 50ms reset timeout period. Samples are generally held in stock. Nonstandard versions require a 2.5k minimum order quantity.

N Denotes an automotive-qualified part. \*EP = Exposed pad.

Typical Application Circuit, Pin Configurations, and Selector Guide appear at end of data sheet.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| (All pins referenced to GND, unless otherwise noted.)<br>IN to GND0.3V to +80V                                | OU<br>Ma   |

|---------------------------------------------------------------------------------------------------------------|------------|

| ENABLE, ENABLE1, ENABLE2, PFI,                                                                                | Coi        |

| GATEP to GND0.3V to (V <sub>IN</sub> + 0.3V)                                                                  | 2          |

| GATEP to IN12V to +0.3V                                                                                       | Ор         |

| OUT, OUT1, OUT2, PFO, RESET (open-drain versions),                                                            | Jur        |

| CSRT, CSWT0.3V to +12V                                                                                        | Sto        |

| HOLD, RESET (push-pull versions), WDI, WDS0, WDS1,<br>WD-DIS, SET, SET10.3V to (V <sub>OUT/OUT1</sub> + 0.3V) | Lea<br>Sol |

|                                                                                                               |            |

OUT, OUT1, OUT2 Short Circuit to GND......Continuous Maximum Current (all pins except IN and OUT\_)......50mA Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) 20-Pin TOEN (derate 33 3mW/°C above +70°C) 20-Pin TOEN (derate 33 3mW/°C above +70°C)

| 20-PIN TQFN (derate 33.3mw/*C above -         | F/U <sup>2</sup> C)2000./IIIW |

|-----------------------------------------------|-------------------------------|

| Operating Temperature Range (T <sub>A</sub> ) | 40°C to +125°C                |

| Junction Temperature (T <sub>J</sub> )        | 150°C                         |

| Storage Temperature Range                     | 65°C to +150°C                |

| Lead Temperature (soldering, 10s)             | +300°C                        |

| Soldering Temperature (reflow)                | +260°C                        |

|                                               |                               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 14V, C_{IN} = 1\mu F, C_{OUT} = 10\mu F, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at T\_A = T\_J = +25°C.) (Note 1)

| PARAMETER               | SYMBOL | (                                           | CONDITIONS                                                                                    | MIN | ТҮР | MAX | UNITS |

|-------------------------|--------|---------------------------------------------|-----------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Supply Voltage Range    | VIN    |                                             |                                                                                               | 5   |     | 72  | V     |

|                         |        | Regulators on (I                            | $_{OAD} = 0$ mA), V <sub>IN</sub> = 8V                                                        |     | 68  | 85  |       |

|                         |        |                                             | V <sub>IN</sub> = 8V, I <sub>LOAD</sub> = 300mA<br>(MAX6795/MAX6796)                          |     | 130 | 220 |       |

|                         |        |                                             | V <sub>IN</sub> = 14V, I <sub>LOAD</sub> = 100mA<br>(MAX6795/MAX6796)                         |     | 100 | 160 |       |

| Supply Current          | lin    | Regulators on,<br>VOUT/OUT1 =<br>VOUT2 = 5V | V <sub>IN</sub> = 8V, I <sub>LOAD1</sub> = I <sub>LOAD2</sub><br>= 150mA<br>(MAX6791–MAX6794) |     | 130 | 220 | μA    |

|                         |        |                                             | $V_{IN} = 14V, I_{LOAD1} = I_{LOAD2} = 50mA$<br>(MAX6791–MAX6794)                             |     | 100 | 160 |       |

|                         |        | Regulators on (I                            | $_{OAD} = 0 mA), V_{IN} = 42V$                                                                |     | 74  | 95  | ]     |

|                         |        |                                             | _OAD = 20mA, total)<br>F = 5V, V <sub>IN</sub> = 42V                                          |     | 100 | 170 |       |

| Shutdown Supply Current | ISHDN  | Regulators off, V                           | ′ <sub>IN</sub> = 14V                                                                         |     | 27  | 45  | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>IN</sub> = 14V, C<sub>IN</sub> = 1 $\mu$ F, C<sub>OUT</sub> = 10 $\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = T<sub>J</sub> = +25°C.) (Note 1)

| PARAMETER                  | SYMBOL           |                                                      | CONDITIONS                                      | MIN   | ТҮР    | MAX   | UNITS |

|----------------------------|------------------|------------------------------------------------------|-------------------------------------------------|-------|--------|-------|-------|

|                            |                  | L/M, I <sub>LOAD</sub> = I                           | LOAD1 = 1mA                                     | 4.858 | 4.974  | 5.090 |       |

|                            |                  | $L/M$ , $I_{LOAD} = 1$<br>$V_{IN} = 8V$              | 150mA (MAX6791–MAX6794),                        | 4.811 | 4.945  | 5.078 |       |

|                            |                  | L/M, I <sub>LOAD</sub> = 3<br>V <sub>IN</sub> = 8V   | 300mA (MAX6795/MAX6796),                        | 4.850 | 5      | 5.150 |       |

|                            |                  | T/S, I <sub>LOAD</sub> = I <sub>L</sub>              | _OAD1 = 1mA                                     | 3.206 | 3.282  | 3.360 |       |

|                            |                  | T/S, I <sub>LOAD</sub> = 1<br>V <sub>IN</sub> = 6V   | 50mA (MAX6791–MAX6794),                         | 3.175 | 3.263  | 3.351 |       |

|                            | Vout/            | T/S, I <sub>LOAD</sub> = 3<br>V <sub>IN</sub> = 6V   | 00mA (MAX6795/MAX6796),                         | 3.201 | 3.3    | 3.399 |       |

| Output Voltage             | VOUT1            | Z/Y, ILOAD = IL                                      | _OAD1 = 1mA                                     | 2.429 | 2.487  | 2.546 | V     |

|                            |                  | Z/Y, I <sub>LOAD</sub> = 1<br>V <sub>IN</sub> = 5.5V | 50mA (MAX6791–MAX6794),                         | 2.405 | 2.472  | 2.539 | 75    |

|                            |                  | Z/Y, I <sub>LOAD</sub> = 3<br>V <sub>IN</sub> = 5.5V | 00mA (MAX6795/MAX6796),                         | 2.425 | 2.5    | 2.575 |       |

|                            |                  | W/V, I <sub>LOAD</sub> = I                           | LOAD1 = 1mA                                     | 1.748 | 1.791  | 1.832 |       |

|                            |                  | W/V, $I_{LOAD} = 1$<br>V <sub>IN</sub> = 5V          | 150mA (MAX6791–MAX6794),                        | 1.731 | 1.780  | 1.828 |       |

|                            |                  | W/V, $I_{LOAD} = 3$<br>V <sub>IN</sub> = 5V          | 300mA (MAX6795/MAX6796),                        | 1.746 | 1.8    | 1.854 |       |

| Output Voltage             |                  | I <sub>LOAD2</sub> = 1mA                             | L.                                              | 4.858 | 4.974  | 5.090 | v     |

| (MAX6791-MAX6794)          | Vout2            | I <sub>LOAD2</sub> = 150r                            | nA                                              | 4.811 | 4.945  | 5.079 |       |

| SET/SET1 Threshold Voltage | VSET             | ILOAD = ILOAD                                        | <sub>01</sub> = 1mA, V <sub>OUT/OUT1</sub> = 5V | 1.207 | 1.2315 | 1.256 | V     |

| Adjustable Output Voltage  | Vout             |                                                      |                                                 | 1.8   |        | 11.0  | V     |

| Dual-Mode™ SET Threshold   |                  | SET/SET1 risir                                       | ng                                              |       | 124    |       | mV    |

|                            |                  | SET/SET1 falli                                       | ng                                              |       | 62     |       |       |

| SET/SET1 Input Current     |                  | SET/SET1 = 1                                         |                                                 | -100  |        | +100  | nA    |

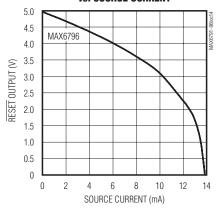

|                            |                  | (MAX6795/                                            | L/M, I <sub>LOAD</sub> = 20mA (Note 2)          |       | 84     | 130   |       |

|                            |                  | (MAX6795)<br>MAX6796)                                | L/M, I <sub>LOAD</sub> = 300mA (Note 2)         |       | 1200   | 1800  | 1     |

| Dropout Voltage            | ΔV <sub>DO</sub> | ,                                                    | T/S, I <sub>LOAD</sub> = 300mA (Note 3)         |       | 1700   | 2400  | mV    |

|                            |                  | (MAX6791-                                            | $L/M$ , $I_{LOAD} = 150mA$ (Note 2)             |       | 1000   | 1800  | _     |

|                            |                  | MAX6794)                                             | L/M, I <sub>LOAD</sub> = 10mA (Note 2)          |       | 84     | 130   |       |

|                            |                  | - /                                                  | T/S, $I_{LOAD} = 150 \text{mA}$ (Note 3)        |       | 1700   | 2400  |       |

| Guaranteed Output Current  |                  |                                                      | (6796, inferred from dropout test               | 300   |        |       | mA    |

| (Note 4)                   |                  | MAX6791-MA                                           | X6794, inferred from dropout test               | 150   |        |       |       |

Dual Mode is a trademark of Maxim Integrated Products, Inc.

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>IN</sub> = 14V, C<sub>IN</sub> = 1 $\mu$ F, C<sub>OUT</sub> = 10 $\mu$ F, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = T<sub>J</sub> = +25°C.) (Note 1)

| PARAMETER                                          | SYMBOL             | CONDITIONS                                                                                             | MIN  | ΤΥΡ                        | MAX                       | UNITS |

|----------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------|------|----------------------------|---------------------------|-------|

| Short-Circuit Output Current Limit                 |                    | MAX6795/MAX6796, output shorted, $V_{IN} = 6V$                                                         | 400  | 480                        |                           | mA    |

| (Note 4)                                           |                    | MAX6791–MAX6794, output shorted,<br>V <sub>IN</sub> = 6V                                               | 200  | 240                        |                           |       |

| Thermal-Shutdown Temperature                       |                    |                                                                                                        |      | +165                       |                           | °C    |

| Thermal-Shutdown Hysteresis                        |                    |                                                                                                        |      | 20                         |                           | °C    |

| Line Regulation                                    |                    | $8V \le V_{IN} \le 72V$ , $I_{LOAD} = 1mA$                                                             |      |                            | 1                         | % of  |

|                                                    |                    | $8V \le V_{IN} \le 72V$ , $I_{LOAD} = 10mA$                                                            |      |                            | 1                         | Vout  |

| Load Regulation (Note 5)                           |                    | I <sub>OUT</sub> = 1mA to 300mA<br>(MAX6795/MAX6796)                                                   |      |                            | 2                         | ~ %   |

| Load Regulation (Note 5)                           |                    | I <sub>OUT</sub> = 1mA to 150mA<br>(MAX6791–MAX6794)                                                   |      |                            | 1.5                       | 70    |

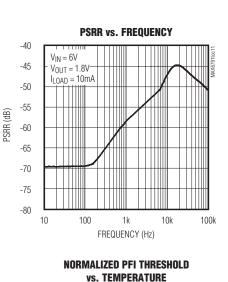

| Power-Supply Rejection Ratio                       | PSRR               | I <sub>LOAD</sub> = 10mA, f = 100Hz, V <sub>IN</sub> = 500mV <sub>P-P</sub>                            |      | 69                         |                           | dB    |

|                                                    |                    | I <sub>LOAD</sub> = 300mA, V <sub>OUT</sub> = 5V,<br>V <sub>OUT</sub> = 90% of its nominal value       |      | 180                        |                           |       |

| Startup Response Time                              | <sup>t</sup> START | I <sub>LOAD</sub> = 150mA, V <sub>OUT</sub> = 5V,<br>V <sub>OUT1/OUT2</sub> = 90% of its nominal value |      | 360                        |                           | μs    |

| Output Overvoltage Protection<br>Threshold         | OV <sub>TH</sub>   | ISINK = 1mA from OUT/OUT1/OUT2                                                                         |      | 1.05 x<br>V <sub>OUT</sub> | 1.1 x<br>V <sub>OUT</sub> | V     |

| Output Overvoltage Protection<br>Sink Current      |                    | V <sub>OUT</sub> = V <sub>OUT</sub> (nominal) x 1.15                                                   | 5    | 10                         |                           | mA    |

| IN to GATEP Clamp Voltage                          |                    | I <sub>GATEP</sub> = -100μA, V <sub>IN</sub> = 20V                                                     | 13.8 | 16.3                       | 18.8                      | V     |

| IN to GATEP Drive Voltage                          |                    | $I_{GATEP} = 0A, V_{IN} = 20V$                                                                         | 8    | 10                         | 12                        | V     |

| ENABLE/ENABLE1/ENABLE2/<br>HOLD Input-Voltage Low  | VIL                |                                                                                                        |      |                            | 0.4                       | V     |

| ENABLE/ENABLE1/ENABLE2/<br>HOLD Input-Voltage High | VIH                |                                                                                                        | 1.4  |                            |                           | V     |

| ENABLE/ENABLE1/ENABLE2<br>Input Pulldown Current   |                    | Enable is internally pulled down to GND                                                                |      | 0.5                        |                           | μA    |

| HOLD Input Pullup Current                          |                    | HOLD is internally pulled to OUT/OUT1                                                                  |      | 2                          |                           | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 14V, C_{IN} = 1\mu$ F,  $C_{OUT} = 10\mu$ F,  $T_A = T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = T_J = +25^{\circ}$ C.) (Note 1)

| PARAMETER                                      | SYMBOL          | CONDITIONS            |       | MIN            | ТҮР                         | MAX            | UNITS |

|------------------------------------------------|-----------------|-----------------------|-------|----------------|-----------------------------|----------------|-------|

| RESET OUTPUT                                   | •               | 1                     |       |                |                             |                |       |

|                                                |                 |                       | L     | 4.500          | 4.625                       | 4.750          |       |

|                                                |                 |                       | М     | 4.250          | 4.375                       | 4.500          | 1     |

|                                                |                 |                       | Т     | 2.970          | 3.053                       | 3.135          |       |

| Reset Threshold (Preset Output                 |                 |                       | S     | 2.805          | 2.888                       | 2.970          |       |

| Voltage)                                       |                 | SET/SET1 = GND        | Z     | 2.250          | 2.313                       | 2.375          |       |

|                                                |                 |                       | Y     | 2.125          | 2.188                       | 2.250          | ]     |

|                                                |                 |                       | W     | 1.620          | 1.665                       | 1.710          | ]     |

|                                                |                 |                       | V     | 1.530          | 1.575                       | 1.620          | ]     |

| Reset Threshold (Adjustable                    |                 | L/T/Z/W               |       | 0.90 x<br>Vout | 0.925 x<br>V <sub>OUT</sub> | 0.95 x<br>Vout |       |

| Output Voltage)                                |                 | M/S/Y/V               |       | 0.85 x<br>Vout | 0.875 x<br>V <sub>OUT</sub> | 0.90 x<br>Vout |       |

| OUT to Reset Delay                             |                 | VOUT1/VOUT falling    |       |                | 35                          |                | μs    |

|                                                |                 |                       | D0    |                | 35                          |                | μs    |

|                                                | t <sub>RP</sub> | VOUT1/VOUT rising     | D1    | 2.187          | 3.125                       | 4.063          | ms    |

| Reset Timeout Period<br>(CSRT = OUT/OUT1)      |                 |                       | D2    | 8.75           | 12.5                        | 16.25          |       |

|                                                |                 |                       | D3    | 35             | 50                          | ms<br>D 65     |       |

|                                                |                 |                       | D4    | 140            | 200                         | 260            | ]     |

| CSRT Ramp Current                              |                 |                       |       | 800            | 1000                        | 1250           | nA    |

| CSRT Ramp Threshold                            |                 |                       |       | 1.185          | 1.218                       | 1.255          | V     |

| WATCHDOG INPUT                                 |                 |                       |       |                |                             |                |       |

| Normal Watchdog Timeout                        | turpo           | CSWT = OUT/OUT1 (fixe | ed)   | 280.0          | 400.0                       | 520.0          | ms    |

| Period                                         | twD2            | CSWT = 1500pF (adjust | able) | 170            | 236.2                       | 290            | 1115  |

| Fast Watchdog Timeout Period                   | twD1            | CSWT = OUT/OUT1 (fixe | ed)   | 37.5           | 50.0                        | 62.5           | ms    |

| SET Ratio = 8                                  | ιννD1           | CSWT = 1500pF (adjust | able) | 21.95          | 29.52                       | 36.90          | 1113  |

| Fast Watchdog Timeout Period                   | twD1            | CSWT = OUT/OUT1 (fixe | ed)   | 18.75          | 25.0                        | 31.25          | ms    |

| SET Ratio = 16                                 | UVD1            | CSWT = 1500pF (adjust | able) | 10.80          | 14.76                       | 18.45          | 1113  |

| Fast Watchdog Timeout Period                   | twD1            | CSWT = OUT/OUT1 (fixe | ed)   | 4.68           | 6.25                        | 7.81           | ms    |

| SET Ratio = 64                                 | ιννD1           | CSWT = 1500pF (adjust | able) | 2.52           | 3.69                        | 4.62           | 1113  |

| Fast Watchdog Minimum Period                   | twpo            |                       |       | 2000           |                             |                | ns    |

| CSWT Ramp Current                              |                 | Adjustable timeout    |       | 800            | 1000                        | 1250           | nA    |

| CSWT Ramp Threshold                            |                 | Adjustable timeout    |       | 1.185          | 1.218                       | 1.255          | V     |

| Undercurrent Threshold for<br>Watchdog Enable  |                 |                       |       | 7.0            | 10                          | 13.8           | mA    |

| Undercurrent Threshold for<br>Watchdog Disable |                 |                       |       | 3              | 5                           | 7              | mA    |

MAX6791-MAX6796

### **ELECTRICAL CHARACTERISTICS (continued)**

(VIN = 14V, CIN = 1µF, C<sub>OUT</sub> = 10µF, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = T<sub>J</sub> = +25°C.) (Note 1)

| PARAMETER                       | SYMBOL          | CONDITIONS                                                              | MIN                       | TYP   | MAX   | UNITS |

|---------------------------------|-----------------|-------------------------------------------------------------------------|---------------------------|-------|-------|-------|

| LOGIC INPUT (WDS0, WDS1, WD     | D-DIS, WDI)     |                                                                         | •                         |       |       | •     |

| Input-Voltage Low               | VIL             |                                                                         |                           |       | 0.4   | V     |

| Input-Voltage High              | VIH             |                                                                         | 1.4                       |       |       | V     |

| Input Current                   |                 | Inputs connected to OUT/OUT1 or GND                                     | -100                      |       | +100  | nA    |

| POWER-FAIL COMPARATOR           |                 |                                                                         |                           |       |       |       |

| PFI Threshold                   | VPFI            |                                                                         | 1.199                     | 1.231 | 1.263 | V     |

| PFI Hysteresis                  |                 |                                                                         |                           | 0.5   |       | %     |

| PFI Input Current               |                 | V <sub>PFI</sub> = 14V                                                  | -100                      |       | +100  | nA    |

| PFI to PFO Delay                |                 | (V <sub>PFI</sub> + 50mV) to (V <sub>PFI</sub> - 50mV)                  |                           | 35    |       | μs    |

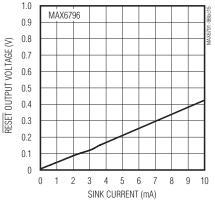

| LOGIC OUTPUT (RESET, PFO)       |                 |                                                                         |                           |       |       |       |

| Output-Voltage Low (Open Drain  | V <sub>OL</sub> | I <sub>SINK</sub> = 50µA (output asserted)                              |                           |       | 0.3   | V     |

| or Push-Pull)                   | VOL             | ISINK = 3.2mA (output asserted)                                         |                           |       | 0.4   | V     |

|                                 |                 | $V_{OUT} \ge 1.0V$ , $I_{SOURCE} = 10\mu A$ (output not asserted)       | 0.8 x<br>Vout             |       |       |       |

| Output-Voltage High (Push-Pull) | V <sub>OH</sub> | $V_{OUT} \ge 1.5V$ , $I_{SOURCE} = 100\mu A$ (output not asserted)      | 0.8 x<br>V <sub>OUT</sub> |       |       | V     |

|                                 |                 | $V_{OUT} \ge 2.2V$ , $I_{SOURCE} = 500\mu A$ (output not asserted)      | 0.8 x<br>V <sub>OUT</sub> |       |       |       |

| Open-Drain Leakage              |                 | $V_{\overline{RESET}} = V_{\overline{PFO}} = 12V$ (output not asserted) |                           |       | 100   | nA    |

Note 1: All devices are 100% production tested at T<sub>J</sub> = +25°C and +125°C. Limits at -40°C are guaranteed by design.

Note 2: Dropout voltage is defined as  $(V_{IN} - V_{OUT})$  when  $V_{OUT}$  is 98% of  $V_{OUT}$  for  $V_{IN} = 8V$ .

**Note 3:** Dropout voltage is defined as  $(V_{IN} - V_{OUT})$  when  $V_{OUT}$  is 98% of  $V_{OUT}$  for  $V_{IN} = 6V$ .

Note 4: Operation beyond the absolute maximum power dissipation is not guaranteed and may damage the part.

Note 5: Test at  $V_{IN} = 8V (L/M)$ ,  $V_{IN} = 6V (T/S)$ ,  $V_{IN} = 5V (Z/Y/W/V)$ .

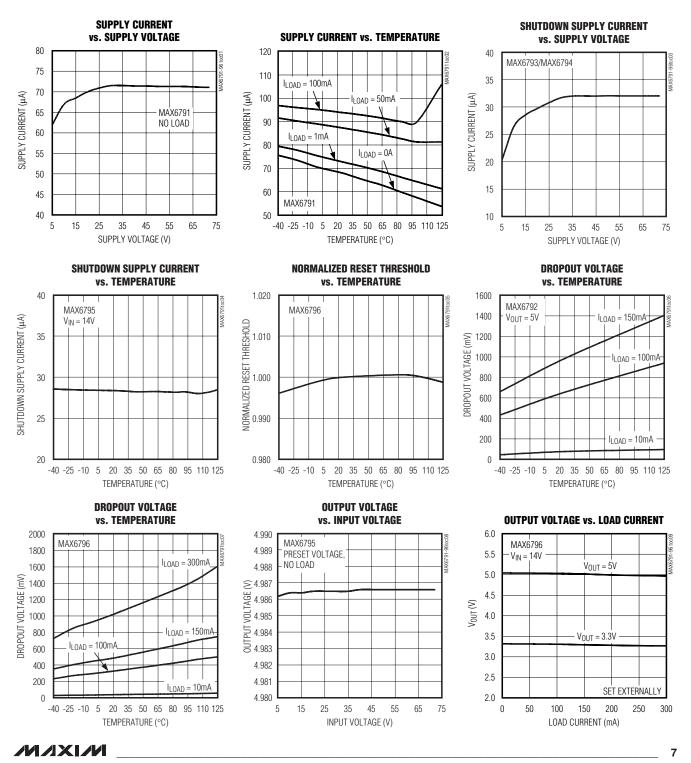

### **Typical Operating Characteristics**

$(V_{IN} = V_{EN} = 14V, C_{IN} = 0.1 \mu F, C_{OUT} = 10 \mu F, T_J = T_A = +25 \degree C$ , unless otherwise noted.)

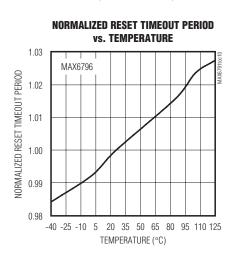

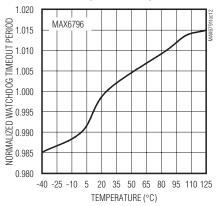

### **Typical Operating Characteristics (continued)**

(VIN = VEN = 14V,  $C_{IN}$  = 0.1µF,  $C_{OUT}$  = 10µF,  $T_J$  =  $T_A$  = +25°C, unless otherwise noted.)

NORMALIZED WATCHDOG TIMEOUT PERIOD vs. temperature

1.001 1.000 1.000 1.000 0.999 0.999 0.995 -40 -25 -10 5 20 35 50 65 80 95 110 125 TEMPERATURE (°C)

#### RESET OUTPUT VOLTAGE vs. SINK CURRENT

### **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = V<sub>EN</sub> = 14V, C<sub>IN</sub> = 0.1 $\mu$ F, C<sub>OUT</sub> = 10 $\mu$ F, T<sub>J</sub> = T<sub>A</sub> = +25°C, unless otherwise noted.)

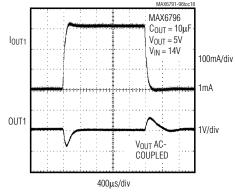

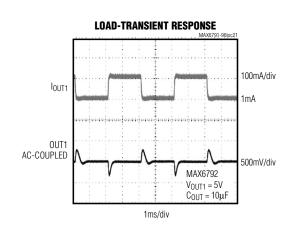

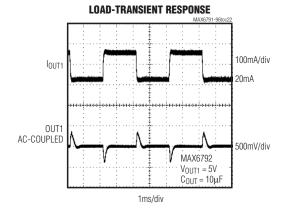

LOAD-TRANSIENT RESPONSE

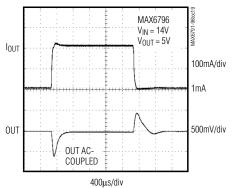

LOAD-TRANSIENT RESPONSE

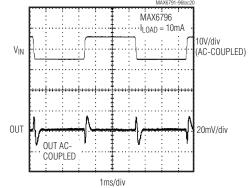

#### LINE-TRANSIENT RESPONSE

MAX6791-MAX6796

### **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = V<sub>EN</sub> = 14V, C<sub>IN</sub> = 0.1 $\mu$ F, C<sub>OUT</sub> = 10 $\mu$ F, T<sub>J</sub> = T<sub>A</sub> = +25°C, unless otherwise noted.)

### **Pin Description**

M/X/M

|                     | PIN                 |                     | PIN   |                                                                                                                                                                                                                                                                           | 1 |  |  |  |

|---------------------|---------------------|---------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

| MAX6791/<br>MAX6792 | MAX6793/<br>MAX6794 | MAX6795/<br>MAX6796 | NAME  | FUNCTION                                                                                                                                                                                                                                                                  |   |  |  |  |

| 1, 2                | 1, 2                | _                   | OUT1  | Regulator 1 Output. Fixed (+1.8V, +2.5V, +3.3V, or +5V) or adjustable (+1.8V to +11V). $V_{OUT1}$ = 150mA (max). Connect a 10µF (min) capacitor from OUT1 to GND.                                                                                                         |   |  |  |  |

| 3                   | 3                   | _                   | SET1  | Feedback Input for Setting the OUT1 Voltage. Connect SET1 to GND to select the preset output voltage. Connect to an external resistive divider for adjustable output operation.                                                                                           |   |  |  |  |

| 4                   | 4                   | 4                   | PFO   | Active-Low, Open-Drain, Power-Fail Comparator Output. PFO asserts low when PFI is below the internal 1.231V threshold. PFO deasserts when PFI is above the internal 1.231V threshold.                                                                                     |   |  |  |  |

| 5                   | 5                   | 5                   | CSWT  | Watchdog Timeout Period Adjust Input. Connect CSWT to OUT1/OUT for the internally fixed watchdog timeout period. For adjustable watchdog timeout period, connect a capacitor from CSWT to GND. See the <i>Selecting Watchdog Timeout Period</i> section for more details. |   |  |  |  |

| 6                   | 6                   | 6                   | CSRT  | Reset Timeout Period Adjust Input. Connect CSRT to OUT1/OUT for the internally fixed timeout period. For adjustable timeout, connect a capacitor from CSRT to GND. See the <i>Reset Output</i> section for more details.                                                  |   |  |  |  |

| 7                   | 7                   | 7                   | GND   | Ground                                                                                                                                                                                                                                                                    |   |  |  |  |

| 8                   | 8                   | 8                   | RESET | Active-Low Reset Output. RESET remains low while OUT1/OUT is below the reset threshold. RESET remains low for the duration of the reset timeout period after the reset conditions end. RESET is available in push-pull and open-drain options.                            |   |  |  |  |

## \_Pin Description (continued)

| PIN                 |                     |                     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|---------------------|---------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6791/<br>MAX6792 | MAX6793/<br>MAX6794 | MAX6795/<br>MAX6796 | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9                   | —                   | _                   | WDS1    | Min/Max Watchdog Logic-Select Input. WDS0 and WDS1 select the watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10                  | _                   | _                   | WDS0    | window ratio or disable the watchdog timer. Drive WDS0 and WDS1 high or low to select the desired ratio, see Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11                  | 11                  | 11                  | WDI     | Watchdog Input.<br>MAX6793–MAX6796: A falling or rising transition must occur on WDI within the selected watchdog timeout period or a reset pulse occurs. The watchdog timer clears when a transition occurs on WDI or whenever RESET is asserted.<br>MAX6791/MAX6792: WDI falling and rising transitions within periods shorter than t <sub>WD1</sub> or longer than t <sub>WD2</sub> force RESET to assert low for the reset timeout period. The watchdog timer begins to count after RESET is deasserted. The watchdog timer clears when a valid transition occurs on WDI or whenever RESET is asserted. Connect WDS0 high and WDS1 low to disable the watchdog timer function. See the <i>Watchdog Timer</i> section. |

| 12                  | 12                  | 12                  | HOLD    | Active-Low Regulator Hold Input. When HOLD is forced low, OUT1/OUT remains ON even if ENABLE1/ENABLE is pulled low. To shut down the output of the regulator (OUT/OUT1), release HOLD after ENABLE1/ENABLE is pulled low. Connect HOLD to OUT1/OUT or leave unconnected if unused. HOLD is internally connected to OUT/OUT1 through a 2µA current source.                                                                                                                                                                                                                                                                                                                                                                 |

| 13, 14              | 13, 14              | _                   | OUT2    | Regulator 2 Output. OUT2 is a fixed +5V output. Connect a 10µF (min) capacitor from OUT2 to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15                  | 15                  |                     | ENABLE2 | Active-High Enable Input 2. Drive ENABLE2 high to turn on OUT2. ENABLE2 is internally connected to ground through a 0.5µA current sink.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16                  | 16                  | 16                  | PFI     | Adjustable Power-Fail Comparator Input. Connect PFI to a resistive-divider to set the desired PFI threshold. The PFI input is referenced to an accurate 1.231V threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17, 18              | 17, 18              | 17, 18              | IN      | Regulator Inputs. Bypass IN with a 1µF capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19                  | 19                  | 19                  | GATEP   | pFET Gate Drive. Connect GATEP to the gate of a p-channel MOSFET to provide low drop reverse-battery voltage protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20                  | 20                  | _                   | ENABLE1 | Active-High Enable Input 1. Drive ENABLE1 high to turn on OUT1. ENABLE1 is internally connected to ground through a 0.5µA current sink.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     | 9                   | 9                   | WD-DIS  | Watchdog Disable Input. Drive WD-DIS low to disable the watchdog timer.<br>Drive WD-DIS high or connect to OUT/OUT1 to enable the watchdog timer.<br>The watchdog timer clears when reset asserts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### Pin Description (continued)

|                     | PIN                 |                     |        |                                                                                                                                                                                                               |

|---------------------|---------------------|---------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6791/<br>MAX6792 | MAX6793/<br>MAX6794 | MAX6795/<br>MAX6796 | NAME   | FUNCTION                                                                                                                                                                                                      |

| _                   | 10                  | 10, 13, 14,<br>15   | N.C.   | Not Internally Connected                                                                                                                                                                                      |

| _                   |                     | 1, 2                | OUT    | Regulator Output. Fixed $+5V$ , $+3.3V$ , $+2.5V$ , $+1.8V$ , or adjustable output (+1.8V to +11V). Connect a $10\mu$ F (min) capacitor from OUT to GND.                                                      |

| _                   | _                   | 3                   | SET    | Feedback Input for Setting the OUT Voltage. Connect SET to GND to select<br>the preset output voltage. Connect to an external resistive-divider for<br>adjustable output operation.                           |

|                     |                     | 20                  | ENABLE | Active-High Enable Input. Drive ENABLE high to turn on the regulator.<br>ENABLE is internally connected to ground through a 0.5µA current sink.                                                               |

| _                   |                     |                     | EP     | Exposed Pad. EP is internally connected to GND. Connect EP to the ground plane to provide a low thermal-resistance path from the IC junction to the PC board. Do not use as the electrical connection to GND. |

### **Detailed Description**

The MAX6791–MAX6796 ultra-low-quiescent-current, single-/dual-output, high-input-voltage linear regulators operate from 5V to 72V. The MAX6791–MAX6794 feature dual regulators that deliver up to 150mA of load current per output. One output is available with preset output-voltage options (+1.8V, +2.5V, +3.3V, and +5.0V) and can be adjusted to any voltage between +1.8V to +11V using an external resistive-divider at SET1. The other output provides a fixed 5V output voltage. The MAX6795/MAX6796 feature a single regulator that delivers up to 300mA of current with preset output-voltage options (+1.8V, +2.5V, +3.3V, and +5.0V) or can be adjusted to any voltage between +1.8V to +11V.

All devices include an integrated µP reset circuit with a fixed/adjustable reset and watchdog timeout period. The MAX6791–MAX6796 monitor OUT/OUT1 and assert a reset output when the output falls below the reset threshold.

#### Regulators

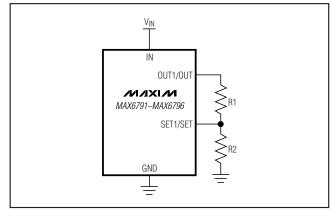

The single and dual regulators accept an input voltage from 5V to 72V. The MAX6791–MAX6796 offer fixed preset output voltages of +1.8V, +2.5V, +3.3V, and +5V, or an adjustable output voltage of +1.8V to +11V, selected using an external resistive-divider network connected between OUT1/OUT, SET1/SET, and GND (see Figure 1). In addition to an adjustable output, the MAX6791–MAX6794 feature a fixed 5V output voltage.

#### **Reset Output**

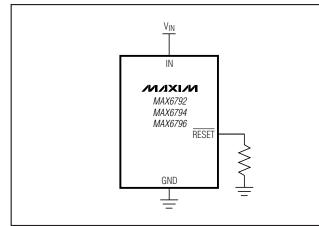

The reset output is typically connected to the reset input of a  $\mu$ P. A  $\mu$ P's reset input starts or restarts the  $\mu$ P in a known state. The MAX6791–MAX6796 supervisory circuits provide the reset logic output to prevent codeexecution errors during power-up, power-down, and brownout conditions (see the *Typical Application Circuit*). RESET changes from high to low whenever the monitored output voltage drops below the reset threshold voltage or the watchdog timeout expires. Once the monitored voltage exceeds its respective reset threshold voltage, RESET remains low for the reset timeout period, then goes high.

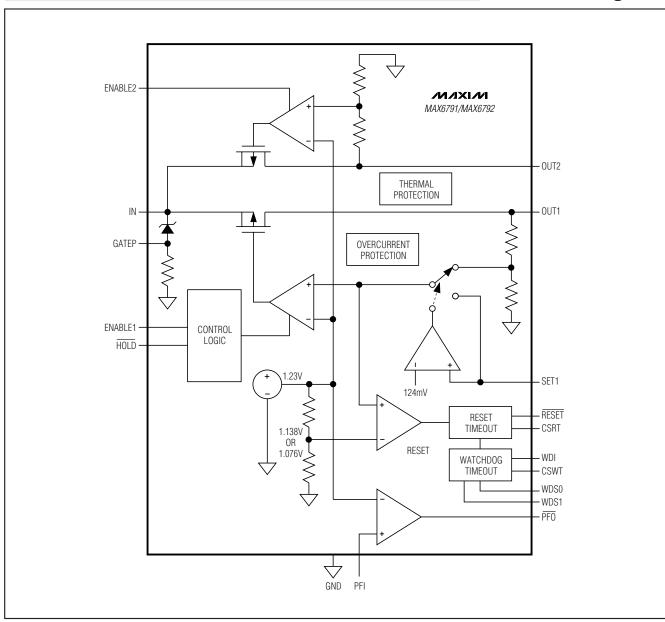

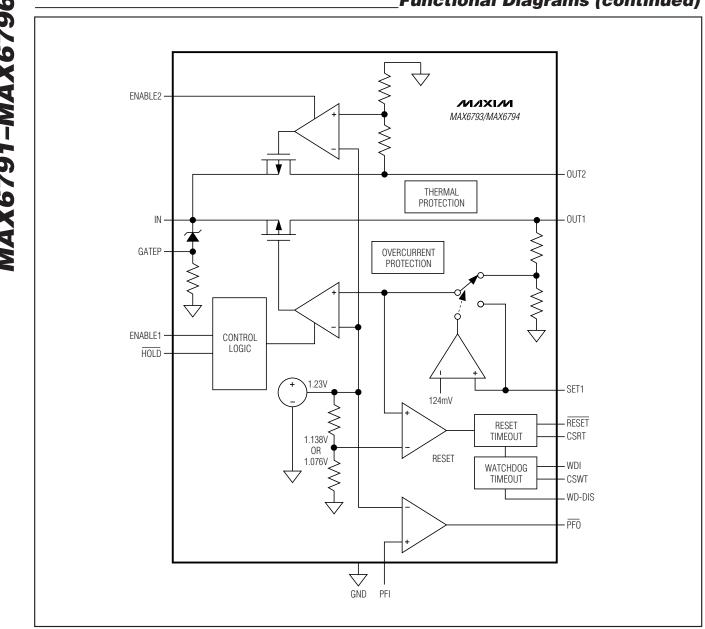

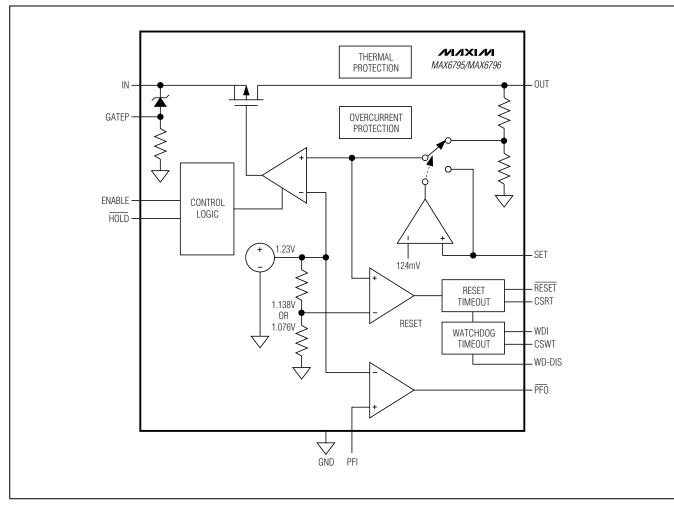

### \_Functional Diagrams

Functional Diagrams (continued)

#### Watchdog Timer

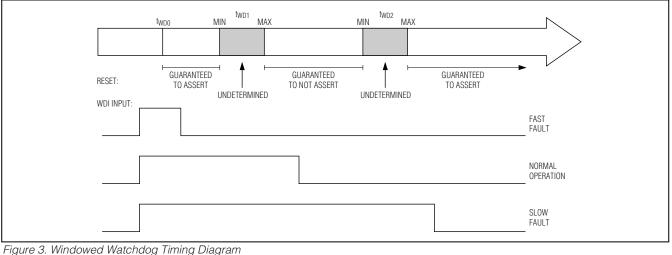

The MAX6791-MAX6796 include a watchdog timer that asserts **RESET** if the watchdog input (WDI) does not toggle high to low or low to high within the watchdog timeout period twp (280ms min or externally adjustable). RESET remains low for the fixed or useradjustable reset timeout period, t<sub>RP</sub>. If the watchdog is not updated for lengthy periods of time, the reset output appears as a pulse train, asserted for t<sub>RP</sub>, deasserted for twp, until WDI is toggled again. Once RESET asserts, it stays low for the entire reset timeout period ignoring any WDI transitions that may occur. To prevent the watchdog from asserting RESET, toggle WDI with a valid rising or falling edge before two from the last edge. The watchdog counter clears when WDI toggles prior to twp from the last edge or when RESET asserts. The watchdog resumes counting after RESET deasserts.

The MAX6791/MAX6792 have a windowed watchdog timer that asserts RESET for the adjusted reset timeout period when the watchdog recognizes a fast watchdog fault ( $t_{WDI} < t_{WD1}$ ), or a slow watchdog fault ( $t_{WDI} > t_{WD2}$ ). The reset timeout period is adjusted independently of the watchdog timeout period.

#### **Enable and Hold Inputs**

The MAX6791–MAX6796 support two logic inputs, ENABLE1/ENABLE and HOLD, making these devices suitable for automotive applications. For example, when the ignition key signal drives ENABLE1/ENABLE high, the regulator turns on and remains on even if ENABLE1/ENABLE goes low, as long as HOLD is forced low and stays low after initial regulator power-up. In this state, releasing HOLD turns the regulator output (OUT/OUT1) off. This feature makes it possible to implement a self-holding circuit without external components. Forcing ENABLE1/ENABLE low and HOLD high or unconnected places the MAX6791–MAX6796 into shutdown mode in which the MAX6791–MAX6796 draw less than 27µA of supply current.

Table 3 shows the state of the regulator output with respect to the voltage level at ENABLE1/ENABLE and HOLD. Connect HOLD to OUT1/OUT or leave it unconnected to allow the ENABLE1/ENABLE input to act as a standard ON/OFF switch for the regulator output (OUT/OUT1).

#### **Power-Fail Comparator**

PFI is the noninverting input to a comparator. If PFI is less than V<sub>PFI</sub> (1.231V), PFO goes low. Common uses for the power-fail comparator include monitoring the

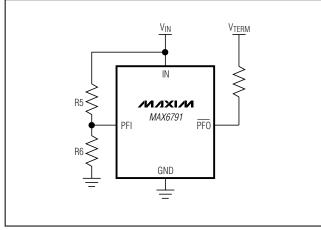

preregulated input of the power supply (such as a battery) or providing an early power-fail warning so software can conduct an orderly system shutdown. Set the power-fail threshold with a resistive-divider, as shown in Figure 5. The typical comparator delay is 35µs from PFI to PFO. Connect PFI to GND or IN if unused.

#### **Reverse-Battery Protection Circuitry**

The MAX6791-MAX6796 include an overvoltage protection circuit that is capable of driving a p-channel MOSFET to protect against reverse-battery conditions. This MOSFET eliminates the need for external diodes, thus minimizing the input voltage drop. See the Typical Application Circuit. The low p-channel MOSFET onresistance of  $30m\Omega$  or less yields a forward-voltage drop of only a few millivolts versus hundreds of millivolts for a diode, thus improving efficiency in batteryoperated devices. Connecting a positive battery voltage to the drain of Q1 (see the Typical Application *Circuit*) forward biases its body diode. When the source voltage exceeds Q1's threshold voltage, Q1 turns on. Once the FET is on, the battery is fully connected to the system and can deliver power to the device and the load. An incorrectly inserted battery reverse-biases the FET's body diode. The gate remains at the ground potential. The FET remains off and disconnects the reversed battery from the system. The internal zener diode and resistor combination at GATEP prevent damage to the p-channel MOSFET during an overvoltage condition. See the Functional Diagrams.

#### **Thermal Protection**

**M/XI/M**

When the junction temperature exceeds  $T_J = +165^{\circ}C$ , the internal protection circuit turns off the internal pass transistor and allows the IC to cool. The thermal sensor turns the pass transistor on again after the junction temperature drops to  $+145^{\circ}C$ , resulting in a cycled output during continuous thermal-overload conditions. Thermal protection protects the MAX6791–MAX6796 in the event of fault conditions. For continuous operation, do not exceed the absolute maximum junction temperature rating of  $+150^{\circ}C$ .

#### **Proper Soldering of Package Heatsink**

The MAX6791–MAX6796 package features an exposed thermal pad on its underside that should be used as a heatsink. This pad lowers the package's thermal resistance by providing a direct heat-conduction path from the die to the PC board. Connect the exposed pad and GND to the system ground using a large pad or ground plane, or multiple vias to the ground plane layer.

#### **Applications Information**

#### **Output Voltage Selection**

The MAX6791–MAX6796 feature dual-mode operation: these devices operate in either a preset voltage mode or an adjustable mode. In preset voltage mode, internal trimmed feedback resistors set the internal linear regulator to +1.8V, +2.5V, +3.3V, or +5V (see the *Selector Guide*). Select preset voltage mode by connecting SET1 (MAX6791–MAX6794)/SET(MAX6795/MAX6796) to GND. In adjustable mode, select an output voltage between +1.8V and +11V using two external resistors connected as a voltage-divider to SET1/SET (see Figure 1). Set the output voltage using the following equation:

$$V_{OUT} = V_{SET} \left(1 + \frac{R1}{R2}\right)$$

where  $V_{SET} = 1.2315V$  and R1, R2  $\leq 200k\Omega$ .

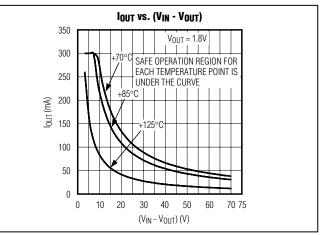

#### **Available Output-Current Calculation**

The MAX6791–MAX6794 provide up to 150mA per output, and the MAX6795/MAX6796 provide up to 300mA of load current. Since the input voltage can be as high as +72V, package power dissipation limits the amount of output current available for a given input/output voltage and ambient temperature. Figure 2 shows the maximum power-dissipation curve for the MAX6791– MAX6796. The graph assumes that the exposed metal pad of the device package is soldered to a solid 1in<sup>2</sup> section of PC board copper. Use Figure 2 to determine the allowable package dissipation for a given ambient temperature. Alternately, use the following formula to calculate the allowable package dissipation:

PD<sub>MAX</sub> = Maximum Power Dissipation

$PD_{MAX} = 2.666W$ , for  $T_A \le +70^{\circ}C$

$\mathsf{PD}_{\mathsf{MAX}}$  = [2.666W - 0.0333W x (TA - 70°C)], for +70°C < TA  $\leq$  +125°C

where 0.0333W is the MAX6791–MAX6796 package thermal derating in W/°C and  $T_{\rm A}$  is the ambient temperature in °C.

After determining the allowable package dissipation, calculate the maximum output current using the following formula:

PD = Power Dissipation

$$\label{eq:pd_max_based} \begin{split} \text{PD} &< \text{PD}_{\text{MAX}} \text{ where } \text{PD} = [(\text{IN} - \text{OUT1}) \times \text{I}_{\text{OUT1}}] + [(\text{IN} - \text{OUT2}) \times \text{I}_{\text{OUT2}}], \text{ for MAX6791-MAX6794}. \end{split}$$

Also, I<sub>OUT1</sub> should be  $\leq$  150mA and I<sub>OUT2</sub> should be  $\leq$  150mA in any case.

$PD < PD_{MAX}$  where  $PD = [(IN - OUT) \times I_{OUT}]$ , for MAX6795/MAX6796.

Also,  $I_{OUT}$  should be  $\leq$  300mA in any case.

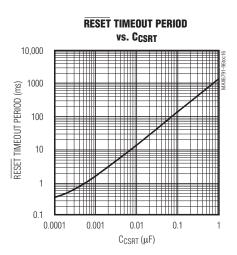

#### **Selecting Reset Timeout Period**

The reset timeout period is adjustable to accommodate a variety of  $\mu$ P applications. Adjust the reset timeout period by connecting a capacitor between CSRT and GND. Use the following formula to set the reset timeout period:

$$t_{\text{RP}} = C_{\text{CSRT}} \left( 1.218 \times 10^6 \frac{\text{V}}{\text{A}} \right)$$

where tRP is in seconds and CCSRT is in Farads.

Connect CSRT to OUT1 (MAX6791–MAX6794) or to OUT (MAX6795/MAX6796) to select an internally fixed timeout period. Connect CSRT to GND to force RESET low. C<sub>CSRT</sub> must be a low-leakage (< 10nA) type capacitor. Ceramic capacitors are recommended; do not use capacitors lower than 100pF to avoid the influence of parasitic capacitances.

Figure 1. Setting the Output Voltage Using a Resistive-Divider

Figure 2. Maximum Power Dissipation for MAX6791–MAX6796

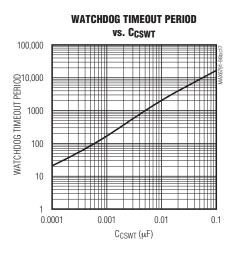

#### Selecting Watchdog Timeout Period

The watchdog timeout period is adjustable to accommodate a variety of µP applications. With this feature, the watchdog timeout can be optimized for software execution. The programmer can determine how often the watchdog timer should be serviced. Adjust the watchdog timeout period (twp) by connecting a capacitor between CSWT and GND. For normal-mode operation, calculate the watchdog timeout capacitor as follows:

$$t_{WD2} = C_{CSWT} \left( 155 \times 10^6 \frac{V}{A} \right)$$

where twp is in seconds and CCSWT is in Farads.

To select the internally fixed watchdog timeout period for the MAX6791-MAX6794, connect CSWT to OUT1. To select the internally fixed watchdog timeout period for the MAX6795/MAX6796, connect CSWT to OUT.

CCSWT must be a low-leakage (< 10nA) type capacitor. Ceramic capacitors are recommended; do not use capacitors lower than 100pF to avoid the influence of parasitic capacitances.

The MAX6791/MAX6792 have a windowed watchdog timer that asserts  $\overline{\text{RESET}}$  for t<sub>RP</sub> when the watchdog recognizes a fast watchdog fault (time between transitions  $< t_{WD1}$ ), or a slow watchdog fault (time between transitions  $> t_{WD2}$ ). The reset timeout period is adjusted independently of the watchdog timeout period. The slow watchdog period, t<sub>WD2</sub>, is calculated as follows:

$$t_{WD2} = C_{CSWT} \left( 155 \times 10^6 \frac{V}{A} \right)$$

where twD2 is in seconds and CCSWT is in Farads.

The fast watchdog period, tWD1, is selectable as a ratio from the slow watchdog fault period (twp2). Select the fast watchdog period by connecting WDS0 and WDS1 to OUT/OUT1 or GND according to Table 4, which illustrates the settings for the 8, 16, and 64 window ratios (tWD2/tWD1). For example, if CCSWT is 2000pF, and WDS0 and WDS1 are low, then twD2 is 318ms (typ) and tWD1 is 40ms (typ). RESET asserts if the watchdog input has two edges too close to each other (faster than twp1); or has edges that are too far apart (slower than  $t_{WD2}$ ).

All WDI inputs are ignored while RESET is asserted. The watchdog timer begins to count after RESET is deasserted. If the time difference between two transitions on WDI is shorter than t<sub>WD1</sub> or longer than t<sub>WD2</sub>, RESET is forced to assert low for the reset timeout period. If the time difference between two transitions on WDI is between twp1 (min) and twp1 (max) or twp2 (min) and twD2 (max), RESET is not guaranteed to assert or deassert; see Figure 3. To guarantee that the window watchdog does not assert RESET, strobe WDI between twp1 (max) and twp2 (min). The watchdog timer is cleared when RESET is asserted. Disable the watchdog timer by connecting WDS0 high and WDS1 low.

There are several options available to disable the watchdog timer (for system development or test purposes or when the  $\mu P$  is in a low-power sleep mode). One way to disable the watchdog timer is to drive WD-DIS low for the MAX6793-MAX6796 and drive WDS0 high and WDS1 low for the MAX6791/MAX6792. This prevents the capacitor from ramping up. Finally, reducing the OUT/OUT1 regulator current below the specified regulator current watchdog-disable threshold (3mA min) also disables the watchdog timer. The

/N/IXI/N

watchdog re-enables immediately when <u>any of</u> these conditions are removed (as long as the RESET is not asserted). Note that the output current threshold limit includes hysteresis so that output current must exceed 13.8mA (max) to reenable the watchdog timer.

#### Capacitor Selection and Regulator Stability

For stable operation over the full temperature range and with load currents up to 150mA, use a 10µF (min) output capacitor with an ESR < 0.5 $\Omega$ . To reduce noise and improve load-transient response and power-supply rejection, use larger output-capacitor values. Some ceramic dielectrics exhibit large capacitance and ESR variation with temperature. For these types of capacitors (such as Z5U and Y5V), much higher-value capacitors are required to maintain stability over the temperaure range. With X7R dielectrics, a 10µF capacitor should be sufficient at all operating temperatures. To improve power-supply rejection and transient response, increase the capacitor between IN and GND.

#### Ensuring a Valid RESET Output Down to VIN = 0V

When V<sub>IN</sub> falls below 1V, RESET current-sinking capabilities decline drastically. High-impedance CMOS-logic inputs connected to RESET can drift to undetermined voltages. This presents no problems in most applications, since most  $\mu$ Ps and other circuitry do not operate with a supply voltage below 1V. In those applications where RESET must be valid down to 0V, adding a pulldown resistor between RESET and GND sinks any stray leakage currents, holding RESET low (Figure 4). The value of the pulldown resistor is not critical; 100k $\Omega$  is large enough not to load RESET and small enough to pull RESET to ground. Open-drain RESET versions are not recommended for applications requiring valid logic for V<sub>IN</sub> down to 0V.

#### Adding Hysteresis to PFI

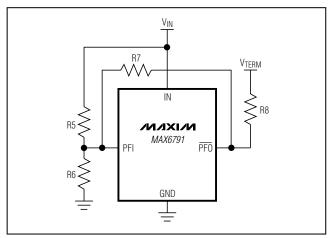

The power-fail comparator has a typical input hysteresis of 0.5% (of V<sub>TH</sub>). This is sufficient for most applications where a power-supply line is being monitored through an external resistive-divider (Figure 5). Figure 6 shows how to add hysteresis to the power-fail comparator. Select the ratio of R5 and R6 so PFI sees 1.23V when V<sub>IN</sub> falls to the desired trip point (V<sub>TRIP</sub>). Since PFO is an open-drain output, resistors R7 and R8 add hysteresis. R7 typically is an order of magnitude greater than R5 or R6. The current through R5 and R6 should be at least 10µA to ensure that the 100nA (max) PFI input current does not shift the trip point. R7 should be larger than 50k $\Omega$  to prevent it from loading down the PFO.

Figure 4. Ensuring  $\overline{\text{RESET}}$  Valid to  $V_{IN} = 0V$

Figure 5. Setting Power-Fail Comparator to Monitor V<sub>IN</sub>

Figure 6. Adding Hysteresis Power-Fail Comparator

| PART<br>SUFFIX (_) | OUTPUT<br>VOLTAGE (V) | RESET THRESHOLD<br>(NOMINAL) |

|--------------------|-----------------------|------------------------------|

| L                  | 5.0                   | 4.625                        |

| М                  | 5.0                   | 4.375                        |

| Т                  | 3.3                   | 3.053                        |

| S                  | 3.3                   | 2.888                        |

| Z                  | 2.5                   | 2.313                        |

| Y                  | 2.5                   | 2.188                        |

| W                  | 1.8                   | 1.665                        |

| V                  | 1.8                   | 1.575                        |

# Table 1. Preset Output Voltage and Reset Threshold

Table 2. Preset Timeout Period

| PART<br>SUFFIX (_) | RESET TIMEOUT PERIOD<br>(NOMINAL) |

|--------------------|-----------------------------------|

| D0                 | 35µs                              |

| D1                 | 3.125ms                           |

| D2                 | 12.5ms                            |

| D3                 | 50ms                              |

| D4                 | 200ms                             |

Use the following formulas to determine the high/low threshold levels and the hysteresis:

$$V_{L-H} = V_{PFI} \times (1 + R5 / R6 + R5 / R7)$$

$V_{H-L} = V_{PFI} \times (1 + R5 / R6) + (V_{PFI} - V_{TERM}) [R5 / (R7 + R8)]$

V<sub>HYS</sub> = V<sub>PFI</sub> x (R5 / R7 ) - (V<sub>PFI</sub> - V<sub>TERM</sub>) [R5 / (R7 + R8)]

where  $V_{L-H}$  is the threshold level for the monitored voltage rising and  $V_{H-L}$  is the threshold level for the monitored voltage falling.

**Chip Information**

PROCESS: BiCMOS

### Table 3. ENABLE/ENABLE1 and HOLD Truth Table/State Table

| OPERATING<br>STATE | ENABLE1/<br>ENABLE | HOLD       | REGULATOR 1<br>OUTPUT | COMMENT                                                                                                                                                                               |

|--------------------|--------------------|------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Initial state      | Low                | Don't care | Off                   | ENABLE/ENABLE1 is pulled to GND through internal pulldown.<br>OUT/OUT1 is disabled.                                                                                                   |

| Turn-on state      | High               | Don't care | On                    | ENABLE/ENABLE1 is externally driven high turning OUT/OUT1 on. HOLD is pulled up to OUT/OUT1.                                                                                          |

| Hold setup state   | High               | Low        | On                    | HOLD is externally pulled low while ENABLE/ENABLE1 remains high, and the regulator latches on.                                                                                        |

| Hold state         | Low                | Low        | On                    | ENABLE/ENABLE1 is driven low (or allowed to float low by an internal pulldown). HOLD remains externally pulled low keeping OUT/OUT1 on.                                               |

| Off state          | Low                | High       | Off                   | HOLD is driven high (or pulled high by the internal pullup) while<br>ENABLE/ENABLE1 is low. OUT/OUT1 is turned off and<br>ENABLE/ENABLE1 and HOLD logic returns to the initial state. |

#### Table 4. MIN/MAX Watchdog Setting

| WDS1 | RATIO                    |

|------|--------------------------|

| 0    | 8                        |

| 1    | 16                       |

| 0    | Watchdog disabled        |

| 1    | 64                       |

|      | WDS1<br>0<br>1<br>0<br>1 |

#### **Table 5. Standard Version Part Number**

| PART NUMBER   | OUTPUT<br>VOLTAGE (V) | RESET TIMEOUT PERIOD (ms)<br>(NOMINAL) | RESET THRESHOLD (V)<br>(NOMINAL) |

|---------------|-----------------------|----------------------------------------|----------------------------------|

| MAX6791TPLD2+ | 5.0                   | 12.5                                   | 4.625                            |

| MAX6791TPSD2+ | 3.3                   | 12.5                                   | 2.888                            |

| MAX6792TPLD2+ | 5.0                   | 12.5                                   | 4.625                            |

| MAX6792TPSD2+ | 3.3                   | 12.5                                   | 2.888                            |

| MAX6793TPLD2+ | 5.0                   | 12.5                                   | 4.625                            |

| MAX6793TPSD2+ | 3.3                   | 12.5                                   | 2.888                            |

| MAX6794TPLD2+ | 5.0                   | 12.5                                   | 4.625                            |

| MAX6794TPSD2+ | 3.3                   | 12.5                                   | 2.888                            |

| MAX6795TPLD2+ | 5.0                   | 12.5                                   | 4.625                            |

| MAX6795TPSD2+ | 3.3                   | 12.5                                   | 2.888                            |

| MAX6796TPLD2+ | 5.0                   | 12.5                                   | 4.625                            |

| MAX6796TPSD2+ | 3.3                   | 12.5                                   | 2.888                            |

+Denotes lead-free package.

### Selector Guide

| PART         | RESET OUTPUT | NUMBER OF<br>OUTPUTS | WINDOWED<br>WATCHDOG TIMEOUT | ENABLE<br>INPUTS | WATCHDOG<br>DISABLE INPUT |

|--------------|--------------|----------------------|------------------------------|------------------|---------------------------|

| MAX6791TP_D_ | Open drain   | 2                    | ✓                            | Dual             | 1                         |

| MAX6792TP_D_ | Push-pull    | 2                    | ✓                            | Dual             | 1                         |

| MAX6793TP_D_ | Open drain   | 2                    | —                            | Dual             | 1                         |

| MAX6794TP_D_ | Push-pull    | 2                    | —                            | Dual             | 1                         |

| MAX6795TP_D_ | Open drain   | 1                    | —                            | Single           | 1                         |

| MAX6796TP_D_ | Push-pull    | 1                    | _                            | Single           | 1                         |

MAX6791-MAX6796

### Package Information

For the latest package outline information and land patterns (footprints), go to <u>www.maxim-ic.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 20 TQFN-EP   | T2055+4      | <u>21-0140</u> | <u>90-009</u>    |

MAX6791-MAX6796

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                      | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------------|------------------|

| 0                  | 10/05            | Initial release                                  |                  |

| 1                  | 8/06             | Correct text in data sheet.                      | 10, 11, 18, 19   |

| 2                  | 10/11            | Added /V automotive-qualified part to data sheet | 1                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

24

\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2011 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.