#

# **IEEE 802.3af-Compliant Power-Over-Ethernet** Interface/PWM Controller for Power Devices

### **General Description**

Features

Powered Device Interface

The MAX5941A/MAX5941B integrate a complete power IC for powered devices (PD) in a power-over-ethernet (PoE) system. The MAX5941A/MAX5941B provide a PD interface and a compact DC-DC PWM controller suitable for flyback and forward converters in either isolated or nonisolated designs.

The MAX5941A/MAX5941B PD interface complies with the IEEE 802.3af standard, providing the PD with a detection signature, a classification signature, and an integrated isolation switch with programmable inrush current control. These devices also feature power-mode undervoltage lockout (UVLO) with wide hysteresis and powergood status outputs.

The MAX5941A/MAX5941B also integrate all the building blocks necessary for implementing DC-DC fixedfrequency isolated power supplies. These devices are a current-mode controller with an integrated high startup circuit suitable for isolated telecom/industrial voltagerange power supplies. A high-voltage startup circuit allows the PWM controller to draw power directly from the 18V to 67V input supply during startup. The switching frequency is internally trimmed to 275kHz ±10%, thus reducing magnetics and filter components. The MAX5941A allows an 85% operating duty cycle and can be used to implement flyback converters. The MAX5941B limits the operating duty cycle to less than 50% and can be used in single-ended forward converters. The MAX5941A/MAX5941B are designed to work with or without an external diode bridge in front of the PD.

The MAX5941A/MAX5941B are available in 16-pin SO packages.

### Applications

**IP** Phones

Wireless Access Nodes

Internet Appliances

Computer Telephony

Security Cameras

Power Devices in Power-Over-Ethernet/ Power-Over-MDI

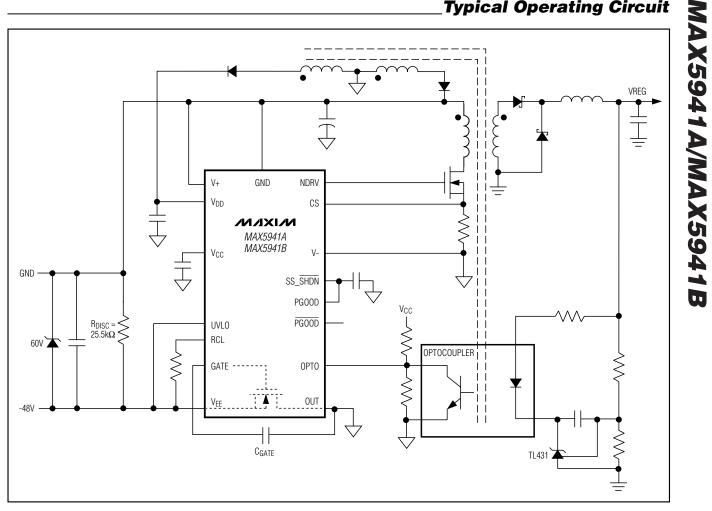

Typical Operating Circuit appears at end of data sheet.

Fully Integrated IEEE 802.3af-Compliant PD Interface

PD Detection and Programmable Classification Signatures

Less than 10µA Leakage Current Offset During Detection

Integrated MOSFET for Isolation and Inrush **Current Limiting**

Gate Output Allows External Control of the Internal Isolation FET

**Programmable Inrush Current Control**

**Programmable Undervoltage Lockout**

PWM Controller

Wide Input Range: 18V to 67V

**Current-Mode Control**

Leading-Edge Blanking

Internally Trimmed 275kHz ±10% Oscillator Soft-Start

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE | MAX DUTY<br>CYCLE (%) |

|-------------|----------------|-----------------|-----------------------|

| MAX5941AESE | -40°C to +85°C | 16 SO           | 85                    |

| MAX5941ACSE | 0°C to +70°C   | 16 SO           | 85                    |

| MAX5941BESE | -40°C to +85°C | 16 SO           | 50                    |

| MAX5941BCSE | 0°C to +70°C   | 16 SO           | 50                    |

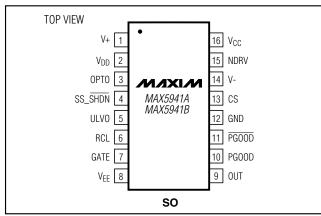

### **Pin Configuration**

### **M X M**

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages are referenced to VFF, unless otherwise noted.)         | UVLO, PGOOD, PGOOD to VEE                             |

|-----------------------------------------------------------------------|-------------------------------------------------------|

| · · · · · · · · · · · · · · · · · · ·                                 |                                                       |

| GND0.3V to +80V                                                       | GATE to V <sub>EE</sub> 80mA                          |

| OUT, PGOOD                                                            | V <sub>DD</sub> , V <sub>CC</sub> 20mA                |

| RCL, GATE0.3V to +12V                                                 | NDRV Continuous                                       |

| UVLO0.3V to +8V                                                       | NDRV (Pulsed for less than 1µs)                       |

| PGOOD to OUT0.3V to (GND + 0.3V)                                      | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| V+ to V0.3V to +80V                                                   | 16-Pin SO (derate 9.1mW/°C above +70°C)727mW          |

| V <sub>DD</sub> to V0.3V to +40V                                      | Operating Temperature Range                           |

| V <sub>CC</sub> to V0.3V to +12.5V                                    | MAX5941_CSE0°C to +70°C                               |

| OPTO, NDRV, SS_ <u>SHDN</u> , CS to V0.3V to (V <sub>CC</sub> + 0.3V) | MAX5941_ESE40°C to +85°C                              |

| Maximum Input/Output Current (Continuous)                             | Storage Temperature Range65°C to +150°C               |

| OUT to V <sub>FF</sub>                                                | Junction Temperature+150°C                            |

| GND, RCL to VFF70mA                                                   | Lead Temperature (soldering, 10s)+300°C               |

|                                                                       |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = (GND - V_{EE}) = 48V, GATE = \overline{PGOOD} = PGOOD = OPEN, V- tied to OUT, V+ tied to GND, UVLO = V_{EE}, T_A = T_{MIN}$  to +T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C. All voltages are referenced to V<sub>EE</sub>, unless otherwise noted.) (Note 1)

| PARAMETER                                    | SYMBOL             | CONDITIONS                                         |                                                       | MIN   | ТҮР   | MAX   | UNITS |

|----------------------------------------------|--------------------|----------------------------------------------------|-------------------------------------------------------|-------|-------|-------|-------|

| PD INTERFACE                                 |                    |                                                    |                                                       |       |       |       |       |

| DETECTION MODE                               |                    |                                                    |                                                       |       |       |       |       |

| Input Offset Current                         | IOFFSET            | V <sub>IN</sub> = 1.4V to 1<br>(Note 2)            | 0.1V, GND = V- = OUT = V+                             |       |       | 10    | μA    |

| Effective Differential Input<br>Resistance   | dR                 |                                                    | to 10.1V with 1V step, OUT =<br>D = OUT = V+ (Note 3) | 550   |       |       | kΩ    |

| CLASSIFICATION MODE                          |                    |                                                    |                                                       |       |       |       |       |

| Classification Current Turn-Off<br>Threshold | VTH,CLSS           | V <sub>IN</sub> rising (Not                        | e 4)                                                  | 20.8  | 21.8  | 22.5  | V     |

|                                              |                    |                                                    | Class 0, $R_{CL}$ = 10k $\Omega$                      | 0     |       | 2     |       |

| Classification Current (Notes 5, 6)          |                    | V <sub>IN</sub> = 12.6V                            | Class 1, $R_{CL} = 732\Omega$                         | 9.17  |       | 11.83 | mA    |

|                                              | ICLASS             | to 20V, RDISC                                      | Class 2, $R_{CL} = 392\Omega$                         | 17.29 |       | 19.71 |       |

|                                              |                    | = 25.5kΩ                                           | Class 3, $R_{CL}$ = 255 $\Omega$                      | 26.45 |       | 29.55 |       |

|                                              |                    |                                                    | Class 4, $R_{CL}$ = 178 $\Omega$                      | 36.6  |       | 41.4  |       |

| POWER MODE                                   |                    |                                                    |                                                       |       |       |       |       |

| Operating Supply Voltage                     | VIN                | $V_{IN} = (GND - V_{IN})$                          | VEE)                                                  |       |       | 67    | V     |

| Operating Supply Current                     | lin                | Measure at GN                                      | ND, not including RDISC                               |       | 0.4   | 1     | mA    |

| Default Power Turn-On Voltage                | Vuvlo, on          | VIN increasing                                     | , UVLO = V <sub>EE</sub>                              | 37.4  | 38.6  | 40.1  | V     |

| Default Power Turn-Off Voltage               | VUVLO, OFF         | V <sub>IN</sub> decreasing, UVLO = V <sub>EE</sub> |                                                       | 30    |       |       | V     |

| Default Power Turn-On/Off<br>Hysteresis      | Vhyst,<br>uvlo     |                                                    |                                                       | 7.4   |       |       | V     |

| External UVLO Programming<br>Range           | V <sub>IN,EX</sub> | Set UVLO externally (Note 7)                       |                                                       | 12    |       | 67    | V     |

| UVLO External Reference Voltage              | VREF, UVLO         | V <sub>UVLO</sub> increasing                       |                                                       | 2.400 | 2.460 | 2.522 | V     |

2

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = (GND - V_{EE}) = 48V, GATE = \overrightarrow{PGOOD} = PGOOD = OPEN, V- tied to OUT, V+ tied to GND, UVLO = V_{EE}, T_A = T_{MIN}$  to +T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C. All voltages are referenced to V<sub>EE</sub>, unless otherwise noted.) (Note 1)

| PARAMETER                                                        | SYMBOL                                                     | CONDITIC                                                                                                | ONS                                 | MIN  | ТҮР  | МАХ  | UNITS |

|------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------|------|------|------|-------|

| UVLO External Reference Voltage<br>Hysteresis                    | HYST                                                       | Ratio to VREF,UVLO                                                                                      |                                     | 19.2 | 20   | 20.9 | %     |

| UVLO Bias Current                                                | IUVLO                                                      | UVLO = 2.460V                                                                                           |                                     | -1.5 |      | +1.5 | μΑ    |

| UVLO Input Ground Sense<br>Threshold                             | VTH,G,UVLO                                                 | (Note 8)                                                                                                |                                     | 50   |      | 440  | mV    |

| UVLO Input Ground Sense Glitch<br>Rejection                      |                                                            | UVLO = V <sub>EE</sub>                                                                                  |                                     |      | 7    |      | μs    |

| Power Turn-Off Voltage,<br>Undervoltage Lockout Deglitch<br>Time | toff_dly                                                   | V <sub>IN</sub> , V <sub>UVLO</sub> falling (Note                                                       | 9)                                  | 0.32 |      |      | ms    |

| Isolation Switch N-Channel                                       | Pou                                                        |                                                                                                         | T <sub>A</sub> = +25°C<br>(Note 11) |      | 0.6  | 1.1  | - Ω   |

| MOSFET On-Resistance                                             | R <sub>ON</sub>                                            | measured between<br>OUT and V <sub>EE</sub>                                                             | T <sub>A</sub> = +85°C              |      | 0.8  | 1.5  |       |

| Isolation Switch N-Channel<br>MOSFET Off-Threshold Voltage       | VGSTH                                                      | OUT = GND, $V_{GATE} - V_{EE}$ , output current < 1 $\mu$ A                                             |                                     | 0.5  |      |      | V     |

| GATE Pulldown Switch Resistance                                  | RG                                                         | Power-off mode, $V_{IN} = 1$                                                                            | 2V, UVLO = V <sub>EE</sub>          |      | 38   | 80   | Ω     |

| GATE Charging Current                                            | IG                                                         | V <sub>GATE</sub> = 2V                                                                                  |                                     | 5    | 10   | 15   | μA    |

| GATE High Voltage                                                | VGATE                                                      | I <sub>GATE</sub> = 1µA                                                                                 |                                     | 5.58 | 5.76 | 5.93 | V     |

| PGOOD, PGOOD Assertion V <sub>OUT</sub><br>Threshold             | Vouten                                                     | V <sub>OUT</sub> - V <sub>EE</sub> , IV <sub>OUT</sub> - V <sub>EE</sub> I<br>V <sub>GATE</sub> = 5.75V | decreasing,                         | 1.15 | 1.23 | 1.31 | V     |

| Hysteresis                                                       |                                                            | Hysteresis                                                                                              |                                     |      | 70   |      | mV    |

| PGOOD, PGOOD Assertion VGATE                                     | , PGOOD Assertion VGATE (GATE - VEE) increasing, OUT = VEE |                                                                                                         | , OUT = V <sub>EE</sub>             | 4.62 | 4.76 | 4.91 | V     |

| Threshold                                                        | VGSEN                                                      | Hysteresis                                                                                              |                                     |      | 80   |      | mV    |

| PGOOD Output Low Voltage                                         |                                                            | I <sub>SINK</sub> = 2mA (Note 10)                                                                       |                                     |      |      | 0.4  | V     |

| PGOOD Output Low Voltage                                         | VoldCdC                                                    | $I_{SINK}$ = 2mA, OUT $\leq$ (GND - 5V) (Note 10)                                                       |                                     |      |      | 0.2  | V     |

| PGOOD Leakage Current                                            |                                                            | $GATE = high, GND - V_{OUT} = 67V (Note 10)$                                                            |                                     |      |      | 1    | μΑ    |

| PGOOD Leakage Current                                            |                                                            | $GATE = V_{EE}, \overline{PGOOD} - V_{E}$                                                               | E = 67V (Note 10)                   |      |      | 1    | μΑ    |

### **ELECTRICAL CHARACTERISTICS (PWM Controller)**

(All voltages referenced to V-.  $V_{DD}$  = 13V, a 10 $\mu$ F capacitor connects  $V_{CC}$  to V-,  $V_{CS}$  = V-, V+ = 48V, 0.1 $\mu$ F capacitor connected to SS\_SHDN, NDRV = open circuit, OPTO = V-, T<sub>A</sub> = T<sub>MIN</sub> to +T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                       | SYMBOL CONDITIONS |                                                             | MIN | TYP  | MAX | UNITS |

|---------------------------------|-------------------|-------------------------------------------------------------|-----|------|-----|-------|

| SUPPLY CURRENT                  |                   |                                                             |     |      |     |       |

|                                 | IV+(NS)           | $V_{DD} = 0V, V + = 67V, driver not switching$              |     | 0.85 | 1.3 |       |

| V+ Supply Current               | IV+(S)            | $V_{+} = 67V, V_{DD} = 0V, V_{OPTO} = 4V, driver switching$ |     | 1.4  | 2.6 | mA    |

| V+ Supply Current After Startup |                   | $V + = 67V, V_{DD} = 13V, V_{OPTO} = 4V$                    |     | 11   |     | μΑ    |

| V <sub>DD</sub> Supply Current  | IVDD(NS)          | $V_{DD} = 36V$ , driver not switching                       |     | 0.9  | 1.3 | mA    |

|                                 | IVDD(S)           | $V_{DD} = 36V$ , driver switching, $V_{OPTO} = 4V$          |     | 1.9  | 2.7 | ША    |

MAX5941A/MAX5941B

### ELECTRICAL CHARACTERISTICS (PWM Controller) (continued)

(All voltages referenced to V-.  $V_{DD}$  = 13V, a 10 $\mu$ F capacitor connects  $V_{CC}$  to V-,  $V_{CS}$  = V-, V+ = 48V, 0.1 $\mu$ F capacitor connected to SS\_SHDN, NDRV = open circuit, OPTO = V-, T<sub>A</sub> = T<sub>MIN</sub> to +T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                     | SYMBOL          | CONDITIONS                                                        | MIN   | ТҮР   | МАХ   | UNITS |

|-----------------------------------------------|-----------------|-------------------------------------------------------------------|-------|-------|-------|-------|

| V+ Shutdown Current                           |                 | $V_{SS}$ <u>SHDN</u> = 0V, V+ = 67V                               |       | 190   | 290   | μA    |

| V <sub>DD</sub> Shutdown Current              |                 | V <sub>SS_SHDN</sub> = 0V                                         |       | 8     | 20    | μA    |

| PREREGULATORS/STARTUP                         | •               | ·                                                                 |       |       |       | •     |

| V+ Input Voltage                              |                 |                                                                   | 18    |       | 67    | V     |

| V <sub>DD</sub> Supply Voltage                |                 |                                                                   | 13    |       | 36    | V     |

| INTERNAL REGULATORS                           | •               |                                                                   |       |       |       | •     |

|                                               |                 | Powered from V+, $I_{CC} = 7.5 \text{mA}$ , $V_{DD} = 0 \text{V}$ | 7.5   | 9.8   | 12    | V     |

| V <sub>CC</sub> Output Voltage                |                 | Powered from $V_{DD}$ , $I_{CC} = 7.5 \text{mA}$                  | 9.0   | 10.0  | 11.0  | v     |

| V <sub>CC</sub> Undervoltage Lockout          | VCC_UVLO        | V <sub>CC</sub> falling                                           |       | 6.6   |       | V     |

| OUTPUT DRIVER                                 |                 | 1                                                                 |       |       |       |       |

| Peak Source Current                           |                 | V <sub>CC</sub> = 11V (externally forced)                         |       | 570   |       | mA    |

| Peak Sink Current                             |                 | V <sub>CC</sub> = 11V (externally forced)                         |       | 1000  |       | mA    |

| NDRV High-Side Driver<br>Resistance           | R <sub>OH</sub> | V <sub>CC</sub> = 11V, externally forced, NDRV<br>sourcing 50mA   |       | 4     | 12    | Ω     |

| NDRV Low-Side Driver<br>Resistance            | R <sub>OL</sub> | V <sub>CC</sub> = 11V, externally forced, NDRV sinking 50mA       |       | 1.6   | 4     | Ω     |

| PWM COMPARATOR                                | 1               |                                                                   |       |       |       |       |

| OPTO Input Bias Current                       |                 | VOPTO = VSS_SHDN                                                  | -1.00 |       | +1.00 | μA    |

| OPTO Control Range                            |                 |                                                                   | 2     |       | 3     | V     |

| Slope Compensation                            | VSCOMP          | MAX5941A                                                          |       | 26    |       | mV/µs |

| THERMAL SHUTDOWN                              |                 |                                                                   |       |       |       | · ·   |

| Thermal Shutdown Temperature                  |                 |                                                                   |       | 150   |       | °C    |

| Thermal Hysteresis                            |                 |                                                                   |       | 25    |       | °C    |

| CURRENT LIMIT                                 |                 |                                                                   |       |       |       |       |

| CS Threshold Voltage                          | VILIM           | V <sub>OPTO</sub> = 4V                                            | 419   | 465   | 510   | mV    |

| CS Input Bias Current                         |                 | $0V \le V_{CS} \le 2V, V_{OPTO} = 4V$                             | -1    |       | +1    | μA    |

| Current-Limit Comparator<br>Propagation Delay |                 | 25mV overdrive on CS, V <sub>OPTO</sub> = 4V                      |       | 180   |       | ns    |

| CS Blanking Time                              |                 | V <sub>OPTO</sub> = 4V                                            |       | 70    |       | ns    |

| OSCILLATOR                                    |                 |                                                                   | I     |       |       | 1     |

| Clock Frequency Range                         |                 | V <sub>OPTO</sub> = 4V                                            | 235   | 275   | 314   | kHz   |

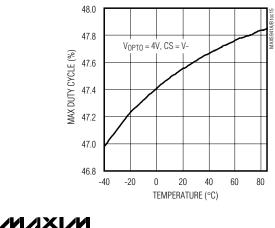

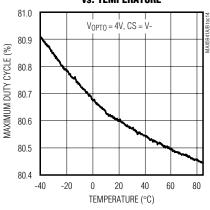

|                                               | 1               | MAX5941A, $V_{OPTO} = 4V$                                         | 75    |       | 85    |       |

| Max Duty Cycle                                |                 | MAX5941B, $V_{OPTO} = 4V$                                         | 44    |       | 50    | %     |

| SOFT-START                                    | 1               |                                                                   | I     |       |       | 1     |

| SS Source Current                             | Isso            | $V_{SS(\overline{SHDN})} = 0V$                                    | 2.0   | 4.6   | 6.5   | μA    |

| SS Sink Current                               |                 |                                                                   | 1     |       |       | mA    |

| Peak Soft-Start Voltage Clamp                 | 1               | No external load                                                  | 2.331 | 2.420 | 2.500 | V     |

| · · ·                                         |                 | Vss SHDN falling (Note 11)                                        | 0.25  | 0.37  | 0.41  |       |

| Shutdown Threshold                            | 1               |                                                                   | 5.20  | 0.01  | 0.11  | V     |

\_\_\_\_\_

- **Note 1:** All min/max limits for the PD interface are production tested at +85°C (extended grade)/+70°C (commercial grade). Limits at +25°C and -40°C are guaranteed by design. All PWM controller min/max limits are 100% production tested at +25°C and +85°C (extended grade)/+70°C (commercial grade). Limits at -40°C are guaranteed by design, unless otherwise noted.

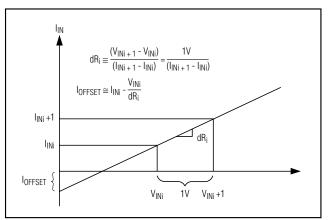

- Note 2: The input offset current is illustrated in Figure 1.

- **Note 3:** Effective differential input resistance is defined as the differential resistance between GND and V<sub>EE</sub> without any external resistance.

- Note 4: Classification current is turned off whenever the IC is in power mode.

- Note 5: See Table 2 in the PD Classification Mode section. RDISC and RCL must be 100ppm or better.

- Note 6: See Thermal Dissipation section for details.

- **Note 7:** When UVLO is connected to the midpoint of an external resistor-divider with a series resistance of  $25.5k\Omega$  (±1%), the turnon threshold set point for the power mode is defined by the external resistor-divider. Make sure the voltage on the UVLO pin does not exceed its maximum rating of 8V when V<sub>IN</sub> is at the maximum voltage.

- Note 8: When the VUVLO is below VTH, G, UVLO, the MAX5941 sets the turn-on voltage threshold internally (VUVLO,ON).

- Note 9: An input voltage or V<sub>UVLO</sub> glitch below their respective thresholds shorter than or equal to t<sub>OFF\_DLY</sub> does not cause the MAX5941A/MAX5941B to exit power-on mode (as long as the input voltage remains above an operable voltage level of 12V).

- Note 10: PGOOD references to OUT while PGOOD references to VEE.

- Note 11: Guaranteed by design.

Figure 1. Effective Differential Input Resistance/Offset Current

voltages are referenced to V- (for graphs 12-30 in the Typical Operating Characteristics), unless otherwise noted.)

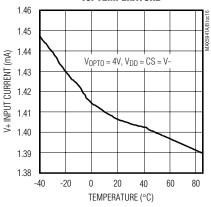

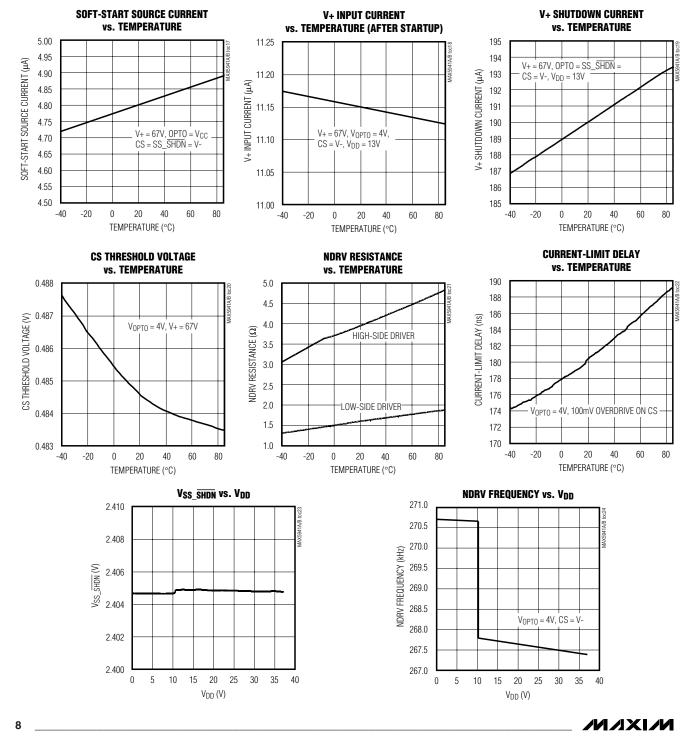

# Typical Operating Characteristics $(V_{IN} = (GND - V_{EE}) = 48V, GATE = \overline{PGOOD} = PGOOD = OUT = OPEN, UVLO = V_{EE}, V_{DD} = 13V, NDRV floating, T_A = T_{MIN} to T_{MAX}.$ Typical values are at T\_A = +25°C. All voltages are referenced to V\_{EE} (for graphs 1–11 in the *Typical Operating Characteristics*), all

**CLASSIFICATION CURRENT EFFECTIVE DIFFERENTIAL INPUT** vs. INPUT VOLTAGE **DETECTION CURRENT vs. INPUT VOLTAGE RESISTANCE vs. INPUT VOLTAGE** 40 RESISTANCE (MQ) 3.5 0.45  $R_{DISC} = 25.5 k\Omega$ **ĊLASS** 4 0.40 35 3.0 GND = V + = V - = OUTCLASSIFICATION CURRENT (mA) 0.35 30 2.5 0.30 DETECTION CURRENT ĊLASS 3 25 EFFECTIVE DIFFERENTIAL INPUT 2.0 0.25 20 0.20 1.5 ĊLASS 2 15 0.15 1.0 10 0.10 . CLASS 1 0.5 5 0.05 . CLASS 0 0 0 0 10 15 25 30 20 0 10 15 0 2 4 8 10 5 6 INPUT VOLTAGE (V) INPUT VOLTAGE (V) INPUT VOLTAGE (V) PGOOD OUTPUT LOW VOLTAGE **OFFSET CURRENT** NORMALIZED UVLO vs. INPUT VOLTAGE vs. TEMPERATURE vs. CURRENT 0 1.010 200  $UVLO = V_{EE}$ 1 008 180 -0.5 1.006 160 001.004 1.002 1.000 0.998 0.996 OFFSET CURRENT (µA) -1.0 140 (Jm) 120 -1.5 VPG00D ( 100 -2.0 80 0.996 60 -2.5 0 994 40 -3.0 0 992 20 -3.5 0.990 0 1 2 3 4 5 6 7 8 9 10 11 -40 -15 10 35 60 85 0 4 8 12 16 20 INPUT VOLTAGE (V) TEMPERATURE (°C) I<sub>SINK</sub> (mA) **PGOOD OUTPUT LOW VOLTAGE OUT LEAKAGE CURRENT INRUSH CURRENT CONTROL** vs. CURRENT vs. TEMPERATURE  $(V_{IN} = 12V)$ 400 20  $V_{OUT} = 67V$ 350 VGATE 5V/div 16 OUT LEAKAGE CURRENT (nA) 300 250 VPG00D (mV) INRUSH 12 100mA/div 200 8 150 VOUT 10V/div 100 4 50 PGOOD 10V/div 0 0 0 4 8 12 16 20 1ms/div -15 85 -40 10 35 60 I<sub>SINK</sub> (mA) INPUT VOLTAGE (V) MIXIM 6

# \_ . . . . . . . . . . .

#### (VIN = (GND - VEF) = 48V, GATE = PGOOD = PGOOD = OUT = OPEN, UVLO = VEF, VDD = 13V, NDRV floating, TA = TMIN to TMAX. Typical values are at $T_A = +25^{\circ}$ C. All voltages are referenced to $V_{EE}$ (for graphs 1–11 in the *Typical Operating Characteristics*), all voltages are referenced to V- (for graphs 12-30 in the Typical Operating Characteristics), unless otherwise noted.) VSS SHDN VS. TEMPERATURE **INRUSH CURRENT CONTROL INRUSH CURRENT CONTROL** (AT THE END OF SOFT-START) $(V_{IN} = 48V)$ $(V_{IN} = 67V)$ MAX5941toc10 1.003 <sup>-</sup> SHDN (V) (NORMALIZED TO V<sub>REF</sub> = 2.4V) .0001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - .001 - OPTO = CS = VVGATE 5V/div VGATE 5V/div IINRUSH 100mA/div INRUSH 1.001 100mA/div VOUT 50V/div νουτ 50V/div /ss PGOOD 50V/div PGOOD 50V/div 0.999 2ms/div -40 -20 0 20 40 60 80 2ms/div TEMPERATURE (°C)

### **Typical Operating Characteristics (continued)**

#### NDRV FREQUENCY vs. TEMPERATURE 278 277 NDRV FREQUENCY (kHz) $V_{OPTO} = 4V, CS = V$ 276 275 274 273 -40 -20 0 20 40 60 80 TEMPERATURE (°C)

#### MAXIMUM DUTY CYCLE vs. temperature

MAXIMUM DUTY CYCLE vs. TEMPERATURE

#### V+ SUPPLY CURRENT vs. TEMPERATURE

MAX5941A/MAX5941B

$(V_{IN} = (GND - V_{EE}) = 48V, GATE = \overrightarrow{PGOOD} = PGOOD = OUT = OPEN, UVLO = V_{EE}, V_{DD} = 13V, NDRV floating, T_A = T_{MIN}$  to T<sub>MAX</sub>. Typical values are at T\_A = +25°C. All voltages are referenced to V<sub>EE</sub> (for graphs 1–11 in the *Typical Operating Characteristics*), all voltages are referenced to V- (for graphs 12–30 in the *Typical Operating Characteristics*), unless otherwise noted.)

$(V_{IN} = (GND - V_{EE}) = 48V, GATE = \overrightarrow{PGOOD} = PGOOD = OUT = OPEN, UVLO = V_{EE}, V_{DD} = 13V, NDRV floating, T_A = T_{MIN}$  to T<sub>MAX</sub>. Typical values are at T\_A = +25°C. All voltages are referenced to V\_{EE} (for graphs 1–11 in the *Typical Operating Characteristics*), all

voltages are referenced to V- (for graphs 12-30 in the Typical Operating Characteristics), unless otherwise noted.)

Typical Operating Characteristics (continued)

#### MAXIMUM DUTY CYCLE vs. VDD V<sub>CC</sub> vs. V<sub>DD</sub> 48.0 10.2 47.9 101 DEVICE POWERED FROM VDD 47.8 $V_{OPTO} = 4V, CS = V$ MAXIMUM DUTY CYCLE (%) 10.0 47.7 47.6 V<sub>CC</sub> (V) 9.9 47.5 DRIVER POWERED 9.8 FROM V<sub>DD</sub> 47.4 47.3 9.7 47.2 DRIVER POWERED 96 DEVICE POWERED FROM V+ 47.1 FROM V+ 47.0 9.5 0 5 10 15 20 25 30 35 0 5 10 15 20 25 30 35 40 40 V<sub>DD</sub> (V) V<sub>DD</sub> (V) **V+ SUPPLY CURRENT V+ INPUT CURRENT vs. VOLTAGE** (AFTER STARTUP) vs. V+ VOLTAGE 12 1.40 1.39 1.38 1.37 1.36 1.35 1.3 1.3 1.3 1.3 10 V+ INPUT CURRENT (µA) V<sub>OPTO</sub> = 4V, CS = V-, V<sub>DD</sub> = 13V 8 6 $V_{OPTO} = 4V, CS = V_{DD} = V-$ 4 1.33 2 1.32 1.31 0 0 10 20 30 40 50 60 70 80 90 100 110 0 20 100 40 60 80 V+ VOLTAGE (V) V+ VOLTAGE (V) VCC VOLTAGE vs. VCC CURRENT V<sub>CC</sub> VOLTAGE vs. V<sub>CC</sub> CURRENT 10.0 10.4 $V_{DD} = OPTO = CS = V$ V+ = 67V, 0PT0 = CS = V 9.9 10.2 9.8 $V_{DD} = 36V$ 10.0 9.7 V+=67V /<sub>CC</sub> VOLTAGE (V) V<sub>CC</sub> VOLTAGE (V) 9.6 = 48V 9.8 9.5 $V_{DD} = 13V$ •V+ = 36V9.6 9.4 $V_{+} = 24V$ 9.3 9.4 9.2 9.2 9.1 9.0 9.0 0 10 15 0 5 10 15 5 20 20 V<sub>CC</sub> CURRENT (mA) V<sub>CC</sub> CURRENT (mA)

Downloaded from Elcodis.com electronic components distributor

/N/XI/N

### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V+              | High-Voltage Startup Input. Referenced to V Connect directly to an input voltage range between 18V to 67V. Connects internally to a high-voltage linear regulator that generates V <sub>CC</sub> during startup. Tie V+ to GND.                                                                                                                                                                                                                                                                                                                                          |

| 2   | V <sub>DD</sub> | Line Regulator Input. Referenced to V V <sub>DD</sub> is the input to the linear regulator that generates V <sub>CC</sub> . For supply voltages less than 36V, connect V <sub>DD</sub> and V+ to the supply. For supply voltages greater than 36V, V <sub>DD</sub> receives its power from the tertiary winding of the transformer and accepts voltages from 13V to 36V. Bypass V <sub>DD</sub> to V- with a 4.7 $\mu$ F capacitor.                                                                                                                                      |

| 3   | OPTO            | Optocoupler Input. Referenced to V The control voltage range on this input is 2V to 3V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | SS_SHDN         | Soft-Start Timing Capacitor Connection. Referenced to V Ramp time to full current limit is approximately 0.45ms/nF. Bypass with a minimum 10nF capacitor to V A 2.4V reference voltage appears across the capacitor. Disable the PWM controller by pulling SS_SHDN below 0.25V. Tie to PGOOD to enable PWM controller automatically from the PD interface.                                                                                                                                                                                                               |

| 5   | UVLO            | Undervoltage Lockout Programming Input for Power Mode. Referenced to V <sub>EE</sub> . When UVLO is above its threshold, the device enters the power mode. Connect UVLO to V <sub>EE</sub> to use the default undervoltage lockout threshold. Connect UVLO to an external resistor-divider to define a threshold externally. The series resistance value of the external resistors must add to $25.5k\Omega$ (±1%) and replaces the detection resistor. To keep the device in undervoltage lockout, pull UVLO between V <sub>TH,G,UVLO</sub> and V <sub>REF,UVLO</sub> . |

| 6   | RCL             | Classification Setting. Referenced to VEE. Add a resistor from RCL to VEE to set a PD class (see Tables 1 and 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7   | GATE            | Gate of Internal N-Channel Power MOSFET. Referenced to V <sub>EE</sub> . GATE sources 10µA when the device enters the power mode. Connect an external 100V ceramic capacitor from GATE to V <sub>OUT</sub> to program the inrush current. Pull GATE to V <sub>EE</sub> to turn off the internal MOSFET. The detection and classification functions operate normally when GATE is pulled to V <sub>EE</sub> .                                                                                                                                                             |

| 8   | VEE             | Negative Input Power. Source of the integrated isolation N-channel power MOSFET. Connect VEE to -48V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9   | OUT             | Output Voltage. Referenced to $V_{EE}$ . Drain of the integrated isolation N-channel power MOSFET. Connect OUT to V                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10  | PGOOD           | Power-Good Indicator Output, Active High, Open Drain. PGOOD is referenced to OUT. PGOOD goes high impedance when $V_{OUT}$ is within 1.2V of $V_{EE}$ and when GATE is 5V above $V_{EE}$ . Otherwise, PGOOD is pulled to OUT (given that $V_{OUT}$ is at least 5V below GND). Connect PGOOD directly (no external pullup required) to SS_SHDN to enable/disable the PWM controller.                                                                                                                                                                                      |

| 11  | PGOOD           | Power-Good Indicator Output, Active Low, Open Drain. $\overrightarrow{PGOOD}$ is referenced to V <sub>EE</sub> . $\overrightarrow{PGOOD}$ is pulled to V <sub>EE</sub> when V <sub>OUT</sub> is within 1.2V of V <sub>EE</sub> and when GATE is 5V above V <sub>EE</sub> . Otherwise, $\overrightarrow{PGOOD}$ goes high impedance.                                                                                                                                                                                                                                      |

| 12  | GND             | Ground. Referenced to VEE. GND is the positive input power. Connect to V+.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13  | CS              | Current-Sense Input. Referenced to V Turns power switch off if V <sub>CS</sub> rises above 465mV for cycle-by-cycle current limiting. CS is also the feedback for the current-mode controller. CS connects to the PWM controller through a leading-edge blanking circuit.                                                                                                                                                                                                                                                                                                |

| 14  | V-              | V- is the ground terminal of the PWM Controller. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15  | NDRV            | Gate Drive. Referenced to V Drives a high-voltage external N-channel power MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16  | V <sub>CC</sub> | Regulated IC Supply. Referenced to V Provides power for MAX5941 V <sub>CC</sub> is regulated from V <sub>DD</sub> during normal operation and from V+ during startup. Bypass V <sub>CC</sub> with a 10 $\mu$ F tantalum capacitor in parallel with a 0.1 $\mu$ F ceramic capacitor to V                                                                                                                                                                                                                                                                                  |

| CLASS | USAGE       | <b>R<sub>CL</sub> (Ω)</b> | MAXIMUM POWER USED BY PD (W) |

|-------|-------------|---------------------------|------------------------------|

| 0     | Default     | 10k                       | 0.44 to 12.95                |

| 1     | Optional    | 732                       | 0.44 to 3.84                 |

| 2     | Optional    | 392                       | 3.84 to 6.49                 |

| 3     | Optional    | 255                       | 6.49 to 12.95                |

| 4     | Not allowed | 178                       | Reserved*                    |

### Table 1. PD Power Classification/RCL Selection

\*Class 4 reserved for future use.

### **Detailed Description**

The MAX5941A/MAX5941B integrate a complete power IC for powered devices (PDs) in a power-over-ethernet (PoE) system. The MAX5941A/MAX5941B provide PD interface and a compact DC-DC PWM controller suitable for flyback and forward converters in either isolated or nonisolated designs.

The MAX5941A/MAX5941B powered device (PD) interface complies with the IEEE 802.3af standard, providing the PD with a detection signature, a classification signature, and an integrated isolation switch with programmable inrush current control. These devices also feature power-mode undervoltage lockout (UVLO) with wide hysteresis, and power-good status outputs.

An integrated MOSFET provides PD isolation during detection and classification. The MAX5941A/MAX5941B guarantee a leakage current offset of less than 10µA during the detection phase. A programmable current limit prevents high inrush current during power-on. The devices feature power-mode UVLO with wide hysteresis and long deglitch time to compensate for twisted-pair cable resistive drop and to ensure glitch-free transition between detection, classification, and power-on/off phases. The MAX5941A/MAX5941B provide both active-high (PGOOD) and active-low (PGOOD) outputs. Both devices offer an adjustable UVLO threshold with a default value compliant to the IEEE 802.3af standard. The MAX5941A/MAX5941B are designed to work with or without an external diode bridge in front of the PD.

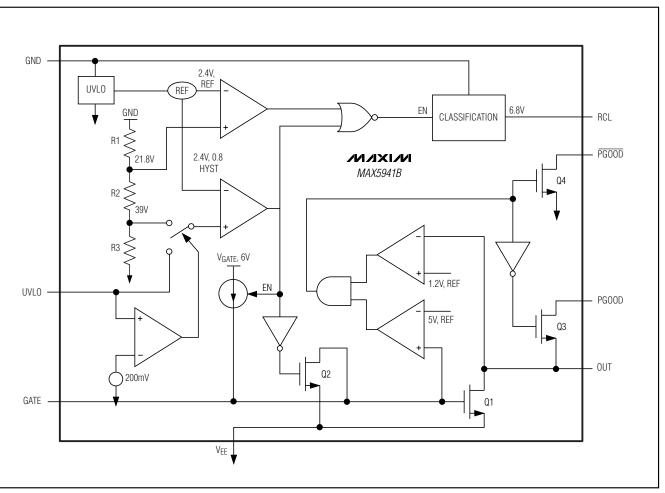

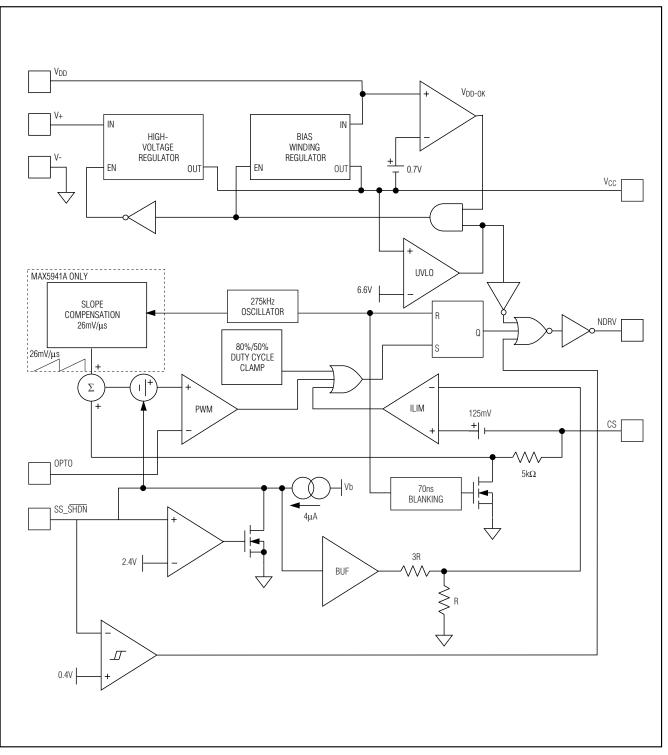

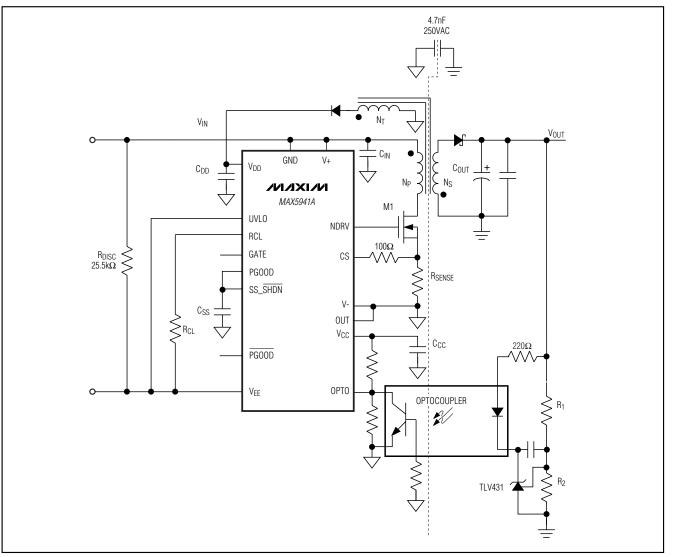

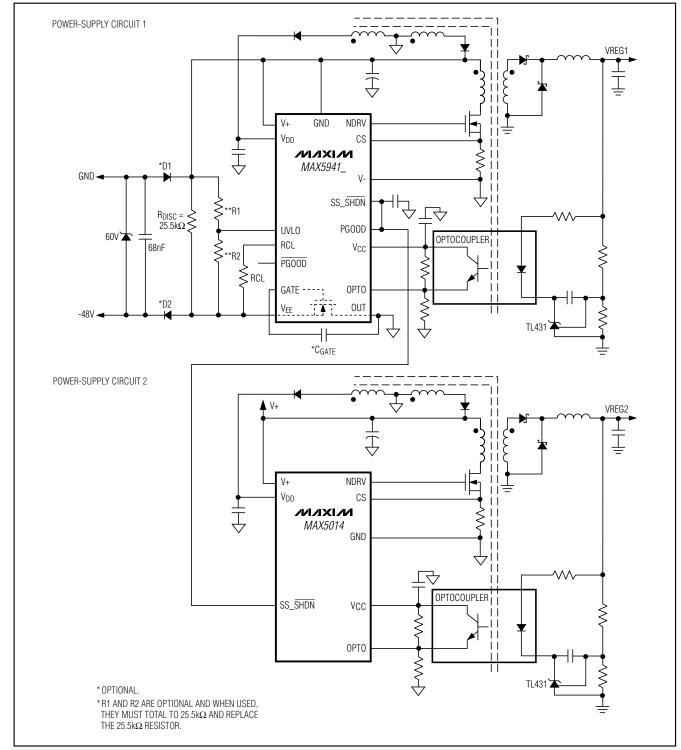

Use the MAX5941A/MAX5941B PWM current-mode controllers to design flyback- or forward-mode power supplies. Current-mode operation simplifies control-loop design while enhancing loop stability. An internal highvoltage startup regulator allows the device to connect directly to the input supply without an external startup resistor. Current from the internal regulator starts the controller. Once the tertiary winding voltage is established, the internal regulator is switched off and bias current for running the PWM controller is derived from the tertiary winding. The internal oscillator is set to 275kHz and trimmed to  $\pm 10\%$ . This permits the use of small magnetic components to minimize board space. Both the MAX5941A and MAX5941B can be used in power supplies providing multiple output voltages. A functional diagram of the PWM controller is shown in Figure 4. Typical applications circuits for forward and flyback topologies are shown in Figure 5 and Figure 6, respectively.

### **Powered Device Interface**

### **Operating Modes**

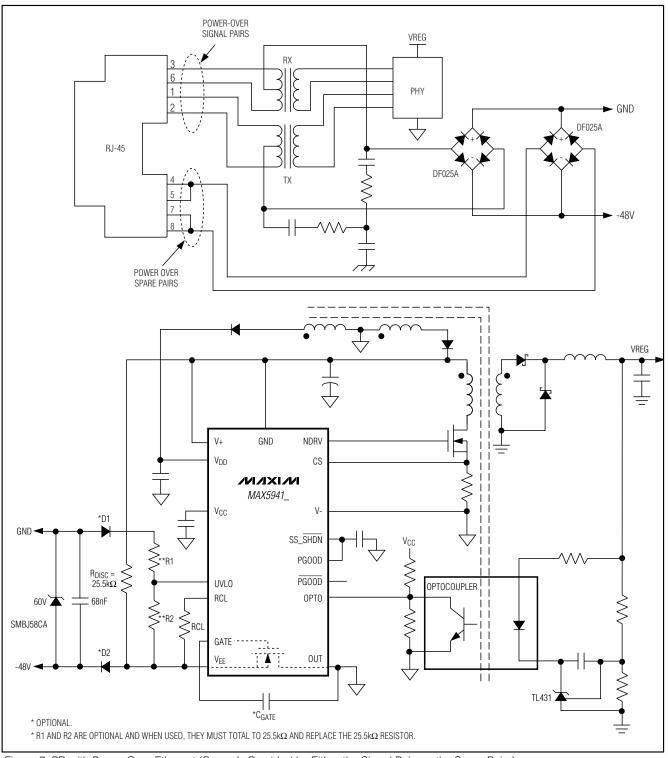

The powered device (PD) front-end section of the MAX5941A/MAX5941B operates in three different modes: PD detection signature, PD classification, and PD power, depending on its input voltage ( $V_{IN} = GND - V_{EE}$ ). All voltage thresholds are designed to operate with or without the optional diode bridge while still complying with the IEEE 802.3af standard (see Application Circuit 1).

### Detection Mode ( $1.4V \le V_{IN} \le 10.1V$ )

In detection mode, the power source equipment (PSE) applies two voltages on V<sub>IN</sub> in the range of 1.4V to 10.1V (1V step minimum), and then records the current measurements at the two points. The PSE then computes  $\Delta V/\Delta I$  to ensure the presence of the 25.5k $\Omega$  signature resistor. In this mode, most of the MAX5941A/MAX5941B internal circuitry is off and the offset current is less than 10µA.

If the voltage applied to the PD is reversed, install protection diodes on the input terminal to prevent internal damage to the MAX5941A/MAX5941B (see Figure 7). Since the PSE uses a slope technique ( $\Delta V/\Delta I$ ) to calculate the signature resistance, the DC offset due to the protection diodes is subtracted and does not affect the detection process.

### Classification Mode (12.6V $\leq$ V<sub>IN</sub> $\leq$ 20V)

In the classification mode, the PSE classifies the PD based on the power consumption required by the PD. This allows the PSE to efficiently manage power distribution. The IEEE 802.3af standard defines five different classes as shown in Table 1. An external resistor (R<sub>CL</sub>) connected from RCL to V<sub>EE</sub> sets the classification current.

| CLASS | <b>R<sub>CL</sub> (Ω)</b> | V <sub>IN</sub> * (V) | CLASS CURRENT SEEN AT V <sub>IN</sub> (mA) |     | IEEE 802.3af PD (<br>CURRENT SPEC | CLASSIFICATION<br>CIFICATION (mA) |

|-------|---------------------------|-----------------------|--------------------------------------------|-----|-----------------------------------|-----------------------------------|

|       |                           |                       | MIN                                        | MAX | MIN                               | MAX                               |

| 0     | 10k                       | 12.6 to 20            | 0                                          | 4   | 0                                 | 4                                 |

| 1     | 732                       | 12.6 to 20            | 9                                          | 12  | 9                                 | 12                                |

| 2     | 392                       | 12.6 to 20            | 17                                         | 20  | 17                                | 20                                |

| 3     | 255                       | 12.6 to 20            | 26                                         | 30  | 26                                | 30                                |

| 4     | 178                       | 12.6 to 20            | 36                                         | 42  | 36                                | 44                                |

### **Table 2. Setting Classification Current**

\*VIN is measured across the MAX5941 input pins (VEE and GND), which does not include the diode bridge voltage drop.

Figure 2. Powered Device Interface Block Diagram

The PSE determines the class of a PD by applying a voltage at the PD input and measures the current sourced out of the PSE. When the PSE applies a voltage between 12.6V and 20V, the MAX5941A/MAX5941B exhibit a current characteristic with values indicated in Table 2. The PSE uses the classification current information to classify the power requirement of the PD. The classification current includes the current drawn by the 25.5k $\Omega$  detection signature resistor and the supply current of the MAX5941A/MAX5941B so that the total current drawn by the PD is within the IEEE 802.3af standard figures. The classification current is turned off whenever the device is in power mode.

#### Power Mode

During power mode, when V<sub>IN</sub> rises above the undervoltage lockout threshold (V<sub>UVLO,ON</sub>), the MAX5941A/ MAX5941B gradually turn on the internal N-channel MOSFET Q1 (see Figure 2). The MAX5941A/ MAX5941B charge the gate of Q1 with a constant current source (10µA, typ). The drain-to-gate capacitance of Q1 limits the voltage rise rate at the drain of MOSFET, thereby limiting the inrush current. To reduce the inrush current, add external drain-to-gate capacitance (see the *Inrush Current* section). When the drain of Q1 is within 1.2V of its source voltage and its gate-to-source voltage is above 5V, the MAX5941A/MAX5941B assert the PGOOD/PGOOD outputs. The MAX5941A/MAX5941B have a wide UVLO hysteresis and turn-off deglitch time to compensate for the high impedance of the twisted-pair cable.

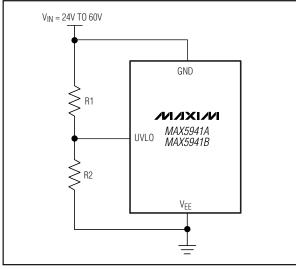

#### **Undervoltage Lockout**

The MAX5941A/MAX5941B operate up to a 67V supply voltage with a default UVLO turn-on set at 39V and a UVLO turn-off set at 30V. Adjust the UVLO threshold using a resistor-divider connected to UVLO (see Figure 3). When the input voltage is above the UVLO threshold (VUVLO,ON), the IC is in power mode and the MOSFET is on. When the input voltage goes below the UVLO threshold (VUVLO,OFF) for more than tOFF\_DLY, the MOSFET turns off.

To adjust the UVLO threshold, connect an external resistor-divider from GND to UVLO and from UVLO to VEE. Use the following equations to calculate R1 and R2 for a desired UVLO threshold:

$$R2 = 25.5k\Omega \times \frac{V_{REF, UVLO}}{V_{IN, EX}}$$

$$R1 = 25.5k\Omega - R2$$

where V<sub>IN, EX</sub> is the desired UVLO threshold. Since the resistor-divider replaces the  $25.5k\Omega$  PD detection resistor, ensure that the sum of R1 and R2 equals  $25.5k\Omega \pm 1\%$ . When using the external resistor-divider, the

Figure 3. Setting Undervoltage Lockout with an External Resistor-Divider

MAX5941 has an external reference voltage hysteresis of 20% (typ). In other words, when UVLO is programmed externally, the turn-off threshold is 80% (typ) of the new UVLO turn-on threshold.

#### **Inrush Current Limit**

The MAX5941A/MAX5941B charge the gate of the internal MOSFET with a constant current source ( $10\mu$ A, typ). The drain-to-gate capacitance of the MOSFET limits the voltage rise rate at the drain, thereby limiting the inrush current. Add an external capacitor from GATE to OUT to further reduce the inrush current. Use the following equation to calculate the inrush current:

$$I_{\text{INRUSH}} = I_{\text{G}} \times \frac{C_{\text{OUT}}}{C_{\text{GATE}}}$$

The recommended inrush current for a PoE application is 100mA.

#### PGOOD/PGOOD Outputs

PGOOD is an open-drain, active-high logic output. PGOOD goes high impedance when V<sub>OUT</sub> is within 1.2V of V<sub>EE</sub> and when GATE is 5V above V<sub>EE</sub>. Otherwise, PGOOD is pulled to V<sub>OUT</sub> (given that V<sub>OUT</sub> is at least 5V below GND). Connect PGOOD to SS\_SHDN to enable the PWM controller. No external pullup resistor is required.

PGOOD is an open-drain, active-low logic output. PGOOD is pulled to VEE when VOUT is within 1.2V of VEE and when GATE is 5V above VEE. Otherwise, PGOOD goes high impedance.

#### **Thermal Dissipation**

During classification mode, if the PSE applies the maximum DC voltage, the maximum voltage drop from GND to V<sub>RCL</sub> will be 13V. If the maximum classification current of 42mA flows through the MAX5941A/MAX5941B, then the maximum DC power dissipation will be close to 546mW, which is slightly higher than the maximum DC power dissipation of the IC at maximum operating temperature. However, according to the IEEE 802.3af standard, the duration of the classification mode is limited to 75ms (max). The MAX5941A/MAX5941B handles the maximum classification power dissipation for the maximum duration time without sustaining any internal damage. If the PSE violates the IEEE 802.3af standard by exceeding the 75ms maximum classification duration, it may cause internal damage to the IC.

#### **PWM Controller**

#### Current-Mode Control

The MAX5941A/MAX5941B offer current-mode control operation with added features such as leading-edge blanking with dual internal path that only blanks the sensed current signal applied to the input of the PWM comparator. The current-limit comparator monitors the CS pin at all times and provides cycle-by-cycle current limit without being blanked. The leading-edge blanking of the CS signal prevents the PWM comparator from prematurely terminating the on cycle. The CS signal contains a leading-edge spike that is the result of the MOSFET gate charge current, capacitive and diode reverse recovery current of the power circuit. Since this leading-edge spike is normally lower than the current limit comparator threshold, current limiting is not blanked and cycle-by-cycle current limiting is provided under all conditions.

Use the MAX5941A in discontinuous flyback applications where wide line voltage and load current variation is expected. Use the MAX5941B for single transistor forward converters where the maximum duty cycle must be limited to less than 50%.

Under certain conditions, it may be advantageous to use a forward converter with greater than 50% duty cycle. For those cases, use the MAX5941A. The large duty cycle results in much lower operating primary RMS currents through the MOSFET switch and in most cases a smaller output filter inductor. The major disadvantage to this is that the MOSFET voltage rating must be higher and that slope compensation must be provided to stabilize the inner current loop. The MAX5941A provides internal slope compensation.

#### **Optocoupled Feedback**

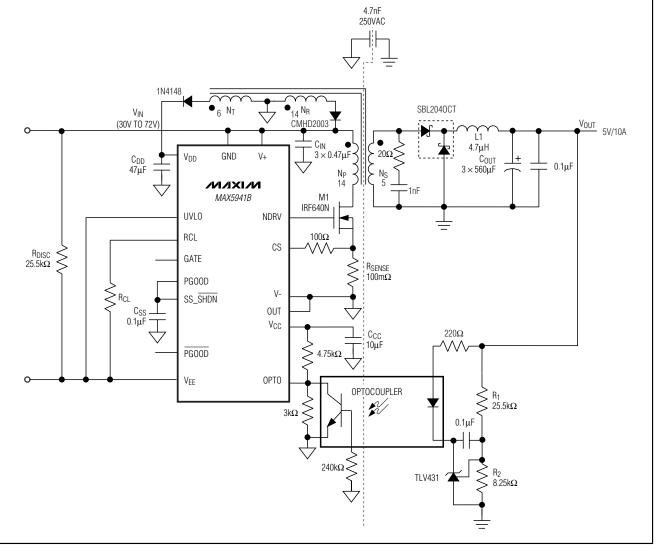

Isolated voltage feedback is achieved by using an optocoupler and a shunt regulator as shown in Figure 5. The output voltage set-point accuracy is a function of the accuracy of the shunt regulator and feedback resistordivider tolerance.

#### **Internal Regulators**

The internal regulators of the MAX5941A/MAX5941B enable initial startup without a lossy startup resistor and regulate the voltage at the output of a tertiary (bias) winding to provide power for the IC. At startup, V+ is regulated down to V<sub>CC</sub> to provide bias for the device. The V<sub>DD</sub> regulator then regulates from the output of the tertiary winding to V<sub>CC</sub>. This architecture allows the tertiary winding to have only a small filter capacitor at its output thus eliminating the additional cost of a filter inductor.

When designing the tertiary winding, calculate the number of turns so the minimum reflected voltage is always higher than 12.7V. The maximum reflected voltage must be less than 36V.

To reduce power dissipation, the high-voltage regulator is disabled when the V<sub>DD</sub> voltage reaches 12.7V. This greatly reduces power dissipation and improves efficiency. If V<sub>CC</sub> falls below the undervoltage lockout threshold (V<sub>CC</sub> = 6.6V), the low-voltage regulator is disabled, and soft-start is reinitiated. In undervoltage lockout the MOSFET driver output (NDRV) is held low.

If the input voltage range is between 13V and 36V, V+ and V<sub>DD</sub> may be connected to the line voltage provided that the maximum power dissipation is not exceeded. This eliminates the need for a tertiary winding.

#### PWM Controller Undervoltage Lockout, Soft-Start, and Shutdown

The soft-start feature of the MAX5941A/MAX5941B allows the load voltage to ramp up in a controlled manner, thus eliminating output voltage overshoot.

While the controller is in undervoltage lockout, the capacitor connected to the SS\_SHDN pin is discharged. Upon coming out of undervoltage lockout, an internal current source starts charging the capacitor to initiate the soft-start cycle. Use the following equation to calculate total soft-start time:

$$t_{startup} = 0.45 \frac{ms}{nF} \times C_{ss}$$

where Css is the soft-start capacitor as shown in Figure 5.

Operation begins when  $V_{SS}$ <u>SHDN</u> ramps above 0.6V. When soft-start has completed,  $V_{SS}$ <u>SHDN</u> is regulated

Figure 4. MAX5941A/MAX5941B PWM Controller Functional Diagram

Downloaded from Elcodis.com electronic components distributor

15

MAX5941A/MAX5941B

MAX5941A/MAX5941B

Figure 5. Forward Converter

to 2.4V, the internal voltage reference. Pull Vss\_ $\underline{SHDN}$  below 0.25V to disable the controller.

Undervoltage lockout shuts down the controller when  $V_{CC}$  is less than 6.6V. The regulators for V+ and the reference remain on during shutdown.

### **Current-Sense Comparator**

The current-sense (CS) comparator and its associated logic limit the peak current through the MOSFET. Current is sensed at CS as a voltage across a sense resistor between the source of the MOSFET and GND. To reduce switching noise, connect CS to the external

MOSFET source through a  $100\Omega$  resistor or an RC lowpass filter (Figures 5, 6). Select the current-sense resistor, RSENSE, according to the following equation:

$$R_{SENSE} = 0.465 V / I_{LimPrimary}$$

where  $\ensuremath{\mathsf{I}_{\mathsf{Lim}\mathsf{Primary}}}$  is the maximum peak primary-side current.

When  $V_{CS} > 465 \text{mV}$ , the power MOSFET switches off. The propagation delay from the time the switch current reaches the trip level to the driver turn-off time is 170ns.

Figure 6. Flyback Converter

### **PWM Comparator and Slope Compensation**

An internal 275kHz oscillator determines the switching frequency of the controller. At the beginning of each cycle, NDRV switches the N-channel MOSFET on. NDRV switches the external MOSFET off after the maximum duty cycle has been reached, regardless of the feedback.

The MAX5941B uses an internal ramp generator for slope compensation. The internal ramp signal is reset at the beginning of each cycle and slews at 26mV/µs.

The PWM comparator uses the instantaneous current, the error voltage, the internal reference, and the slope

compensation (MAX5941A only) to determine when to switch the N-channel MOSFET off. In normal operation, the N-channel MOSFET turns off when:

IPRIMARY × RSENSE > VOPTO - VREF - VSCOMP

where IPRIMARY is the current through the N-channel MOSFET, VREF is the 2.4V internal reference, and V<sub>SCOMP</sub> is a ramp function starting at zero and slewing at 26mV/ $\mu$ s (MAX5941A only). When using the MAX5941A in a forward-converter configuration, the following condition must be met to avoid control-loop subharmonic oscillations:

$\frac{N_{S}}{N_{P}} \times \frac{k \times R_{SENSE} \times V_{OUT}}{L} = 26 \text{mV}/\mu\text{s}$

where k = 0.75 to 1, and Ns and Np are the number of turns on the secondary and primary side of the transformer, respectively. L is the output filter inductor. This makes the output inductor current downslope as referenced across R<sub>SENSE</sub> equal to the slope compensation. The controller responds to transients within one cycle when this condition is met.

#### **N-Channel MOSFET Gate Driver**

NDRV drives an N-channel MOSFET. NDRV sources and sinks large transient currents to charge and discharge the MOSFET gate. To support such switching transients, bypass  $V_{CC}$  with a ceramic capacitor. The average current as a result of switching the MOSFET is the product of the total gate charge and the operating frequency. It is this current plus the DC quiescent current that determines the total operating current.

### **Applications Information**

#### Design Example

The following is a general procedure for designing a forward converter (Figure 5) using the MAX5941B:

- 1) Determine the requirements.

- 2) Set the output voltage.

- 3) Calculate the transformer primary to secondary winding turns ratio.

- 4) Calculate the reset to primary winding turns ratio.

- 5) Calculate the tertiary to primary winding turns ratio.

- 6) Calculate the current-sense resistor value.

- 7) Calculate the output inductor value.

- 8) Select the output capacitor.

- The circuit in Figure 5 was designed as follows:

- 1)  $30V \le V_{IN} \le 67V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 10A$ ,  $V_{RIPPLE} \le 50mV$ . Turn-on threshold is set at 38.6V.

- 2) To set the output voltage, calculate the values of resistors R1 and R2 according to the following equation:

$$\frac{V_{\text{REF}}}{V_{\text{OUT}}} = \frac{R_2}{R_1 + R_2}$$

where  $V_{\text{REF}}$  is the reference voltage of the shunt regulator, and  $\text{R}_1$  and  $\text{R}_2$  are the resistors shown in Figures 5 and 6.

3) The turns ratio of the transformer is calculated based on the minimum input voltage and the lower limit of the maximum duty cycle for the MAX5941B (44%). To enable the use of MOSFETs with drain-source breakdown voltages of less than 200V, use the MAX5941B with the 50% maximum duty cycle. Calculate the turns ratio according to the following equation:

$$\frac{N_{S}}{N_{P}} \ge \frac{V_{OUT} + (V_{D1} \times D_{MAX})}{D_{MAX} \times V_{IN MIN}}$$

where:

$N_S/N_P$  = Turns ratio ( $N_S$  is the number of secondary turns and  $N_P$  is the number of primary turns).

VOUT = Output voltage (5V).

$V_{D1}$  = Voltage drop across D1 (typically 0.5V for power Schottky diodes).

D<sub>MAX</sub> = Minimum value of maximum operating duty cycle (44%).

VIN MIN = Minimum Input voltage (30V).

In this example:

$$\frac{N_{S}}{N_{P}} \ge \frac{5V + (0.5V \times 0.44)}{0.44 \times 30V} = 0.395$$

Choose NP based on core losses and DC resistance. Use the turns ratio to calculate NS, rounding up to the nearest integer. In this example, NP = 14 and NS = 6.

For a forward converter, choose a transformer with a magnetizing inductance in the neighborhood of  $200\mu$ H. Energy stored in the magnetizing inductance of a forward converter is not delivered to the load and must be returned back to the input; this is accomplished with the reset winding.

The transformer primary to secondary leakage inductance should be less than  $1\mu$ H. Note that all leakage energy will be dissipated across the MOS-FET. Snubber circuits may be used to direct some or all of the leakage energy to be dissipated across a resistor.

To calculate the minimum duty cycle ( $D_{MIN}$ ), use the following equation:

$$D_{MIN} = \frac{V_{OUT}}{V_{IN}MAX} \times \frac{N_S}{N_P} - V_{D1} = 17.7$$

where VIN\_MAX is the maximum input voltage (67V).

4) The reset winding turns ratio (NR/NP) needs to be low enough to guarantee that the entire energy in the transformer is returned to V+ within the off cycle at the maximum duty cycle. Use the following equation to determine the reset winding turns ratio:

$$N_{R} \leq N_{P} \times \frac{1 - D_{MAX}'}{D_{MAX}'}$$

where:

N<sub>R</sub>/N<sub>P</sub> = Reset winding turns ratio.

D<sub>MAX</sub>' = Maximum value of maximum duty cycle:

$$N_{\rm R} \le 14 \times \frac{1-0.5}{0.5} = 14$$

Round N<sub>R</sub> to the nearest smallest integer.

The turns ratio of the reset winding (NR/NP) determines the peak voltage across the N-channel MOS-FET.

Use the following equation to determine the maximum drain-source voltage across the N-channel MOSFET:

$$V_{DSMAX} \ge V_{IN\_MAX} \times \left(1 + \frac{N_P}{N_R}\right)$$

V<sub>DSMAX</sub> = Maximum MOSFET drain-source voltage. V<sub>IN MAX</sub> = Maximum input voltage:

$$V_{\text{DSMAX}} \ge 67V \times \left(1 + \frac{14}{14}\right) = 134V$$

Choose MOSFETs with appropriate avalanche power ratings to absorb any leakage energy.

Choose the tertiary winding turns ratio (NT/NP) so that the minimum input voltage provides the minimum operating voltage at VDD (13V). Use the following equation to calculate the tertiary winding turns ratio:

$$\label{eq:linear_state} \begin{split} & \frac{V_{DDMIN} + 0.7}{V_{IN\_MIN}} \times N_P \leq N_T \leq \\ & \frac{V_{DDMAX} + 0.7}{V_{IN\_MAX}} \times N_P \end{split}$$

where:

V<sub>DDMIN</sub> is the minimum V<sub>DD</sub> supply voltage (13V). V<sub>DDMAX</sub> is the maximum V<sub>DD</sub> supply voltage (30V).

M/IXI/M

VIN\_MIN is the minimum input voltage (30V).

$V_{\text{IN\_MAX}}$  is the maximum input voltage (67V in this design example).

Np is the number of turns of the primary winding. NT is the number of turns of the tertiary winding:

$$\frac{13.7}{30} \times 14 \le N_T \le \frac{36.7}{67} \times 14$$

$$6.39 \le N_T \le 7.67$$

Choose  $N_T = 7$ .

6) Choose RSENSE according to the following equation:

$$R_{SENSE} \le \frac{V_{ILIM}}{\frac{N_S}{N_P} \times 1.2 \times I_{OUTMAX}}$$

where:

VILIM is the current-sense comparator trip threshold voltage (0.465V).

NS/NP is the secondary side turns ratio (5/14 in this example).

I<sub>OUTMAX</sub> is the maximum DC output current (10A in this example):

$$R_{SENSE} \le \frac{0.465V}{\frac{6}{14} \times 1.2 \times 10} = 90.4 m\Omega$$

Choose the inductor value so that the peak ripple current (LIR) in the inductor is between 10% and 20% of the maximum output current:

$$L \ge \frac{(V_{OUT} + V_D) \times (1 - D_{MIN})}{2 \times LIR \times 275 \text{kHz} \times I_{OUTMAX}}$$

where  $V_D$  is the output Schottky diode forward voltage drop (0.5V) and LIR is the ratio of inductor ripple current to DC output current:

$$L \ge \frac{(5.5) \times (1-0.198)}{0.4 \times 275 \text{kHz} \times 10A} = 4.01 \mu\text{H}$$

8) The size and ESR of the output filter capacitor determine the output ripple. Choose a capacitor with a low ESR to yield the required ripple voltage.

Use the following equations to calculate the peak-topeak output ripple:

$$V_{\text{RIPPLE}} = \sqrt{V_{\text{RIPPLE,ESR}}^2 + V_{\text{RIPPLE,C}}^2}$$

### **Table 3. Component Suppliers**

| COMPONENT               | SUPPLIERS               | WEBSITE                                   |

|-------------------------|-------------------------|-------------------------------------------|

|                         | International Rectifier | www.irf.com                               |

| Power FETS              | Fairchild               | www.fairchildsemi.com                     |

|                         | Vishay-Siliconix        | www.vishay.com/brands/siliconix/main.html |

| Current-Sense Resistors | Dale-Vishay             | www.vishay.com/brands/dale/main.html      |

| Current-Sense Resistors | IRC                     | www.irctt.com/pages/index.cfm             |

|                         | ON Semi                 | www.onsemi.com                            |

| Diodes                  | General Semiconductor   | www.gensemi.com                           |

|                         | Central Semiconductor   | www.centralsemi.com                       |

|                         | Sanyo                   | www.sanyo.com                             |

| Capacitors              | Taiyo Yuden             | www.t-yuden.com                           |

|                         | AVX                     | www.avxcorp.com                           |

|                         | Coiltronics             | www.cooperet.com                          |

| Magnetics               | Coilcraft               | www.coilcraft.com                         |

|                         | Pulse Engineering       | www.pulseeng.com                          |

where:

VRIPPLE is the combined RMS output ripple due to VRIPPLE,ESR, the ESR ripple, and VRIPPLE,C, the capacitive ripple. Calculate the ESR ripple and capacitive ripple as follows:

$V_{RIPPLE,ESR} = I_{RIPPLE} \times ESR$

$V_{RIPPLE,C} = I_{RIPPLE}/(2 \times \pi \times 275 \text{kHz} \times C_{OUT})$

### Layout Recommendations

All connections carrying pulsed currents must be very short, be as wide as possible, and have a ground plane as a return path. The inductance of these connections must be kept to a minimum due to the high di/dt of the currents in high-frequency switching power converters.

Current loops must be analyzed in any layout proposed, and the internal area kept to a minimum to reduce radiated EMI. Ground planes must be kept as intact as possible.

MAX5941A/MAX5941B

Figure 8. Power-Supply Circuit 1 Enabling PWM Controller of a Second Power Circuit

MAX5941A/MAX5941B

**Chip Information**

TRANSISTOR COUNT: 4232 **PROCESS: BICMOS**

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <u>www.maxim-ic.com/packages</u>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2003 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.