# 12-Bit, 100 MSPS D/A Converters

# AD9712/AD9713

#### **FEATURES**

100 MSPS Update Rate ECL/TTL Compatibility

Low Glitch Impulse: 100 pV-s Fast Settling: 30 ns to  $\pm 1$  LSB

Low Power: 700 mW

#### **APPLICATIONS**

ATE

Signal Reconstruction

**Arbitrary Waveform Generators**

Digital Synthesizers

Signal Generators

GENERAL DESCRIPTION

The AD9712 and AD9713 are 12-bit high speed digitato-analog converters constructed in an advanced oxide isolated bipolar process. The AD9712 is an ECL-competible device featuring update rates of 100 MSPS minimum; the UTL compatible AD9713 will update at 80 MSPS minimum.

Designed for direct digital synthesis, waveform reconstruction, and high resolution imaging applications, both devices feature low glitch impulse of 100 pV-s; and fast settling times of 30 ns to  $\pm 1 \text{ LSB}$ . Both units are characterized for dynamic performance, and have excellent harmonic suppression.

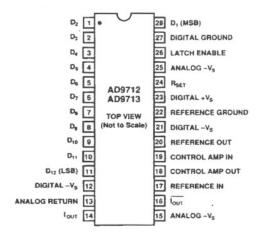

Plastic DIP Pinout Designations (Top View)

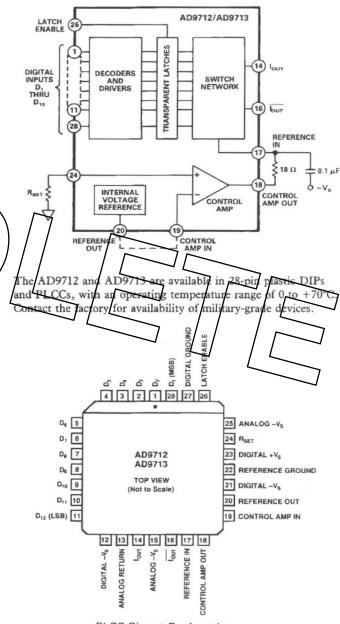

#### FUNCTIONAL BLOCK DIAGRAM

PLCC Pinout Designations

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106

Tel: 617/329-4700 Fax: 617/326-8703 Twx: 710/394-6577

West Coast Central Atlantic

714/641-9391

214/231-5094

Atlantic 215/643-7790

# AD9712/AD9713—SPECIFICATIONS

| Positive Supply Voltage $(+V_S)$ (AD9713 Only) +6 V Negative Supply Voltage $(-V_S)$ (AD9712 and AD9713) | REFERENCE IN Voltage Range3.7 V to $-V_S$ Analog Output Current ( $I_{OUT}$ or $\overline{I_{OUT}}$ )30 mA Operating Temperature Range AD9712JN/JP 0 to $+70^{\circ}\text{C}$ AD9713JN/JP 0 to $+70^{\circ}\text{C}$ Maximum Junction Temperature <sup>2</sup> $+150^{\circ}\text{C}$ Lead Temperature (Soldering, 10 seconds) $+300^{\circ}\text{C}$ Storage Temperature Range $-65^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# ELECTRICAL CHARACTERISTICS ( $-V_s = -5.2 \text{ V}; +V_s = +5 \text{ V}$ (AD9713 Only); CONTROL AMP IN = -1.2 V (external); $R_{SET} = 7.5 \text{ k}\Omega$ , unless otherwise noted)

|                                                                     |                        | Test    | AD971          |       |                   |                         | 3JN/JP |                      |                   |   |

|---------------------------------------------------------------------|------------------------|---------|----------------|-------|-------------------|-------------------------|--------|----------------------|-------------------|---|

| Parameter (Conditions)                                              | Temp                   | Level   | Min            | Тур   | Max               | Min                     | Тур    | Max                  | Units             |   |

| RESOLUTION                                                          |                        |         | 12             |       |                   | 12                      |        |                      | Bits              |   |

| DC ACCURACY Differential Norlinearity (J) Integral Nonlinearity (I) | +25°C<br>Full<br>+25°C |         |                | 1.2   | 2.0<br>4.0<br>3.0 |                         | 1.2    | 2.0<br>4.0<br>3.0    | LSB<br>LSB<br>LSB |   |

| ("Best Fit" Straight Line)                                          | Full                   | VI) /   |                | - ) ) | 4.0               | /                       | _      | 4.0                  | LSB               |   |

| INITIAL OFFSET ERROR<br>Zero-Scale Offset Error                     | +25°C<br>Full          | VI      |                | 9.5   | 1.5               |                         | 0.5    |                      | p.A.              | 7 |

| Full-Scale Gain Error <sup>3</sup>                                  | +25°C<br>Full          | I<br>VI |                | 4.0   | 8.5<br>11.0       | L / ,                   | 4.0    | 5.0<br>7 8.5<br>11.0 | 7 %               |   |

| Offset Drift Coefficient                                            | +25°C                  | V       |                | 0.03  |                   | $H \subset \mathcal{L}$ | 0.03   | /                    | μA/°C             |   |

| REFERENCE/CONTROL AMP<br>Internal Reference Voltage                 | +25°C<br>Full          | I       | -1.13<br>-1.11 | -1.26 | -1.39<br>-1.41    | -1.13<br>-1.11          | -1.26  | -1.59<br>-1.41       |                   |   |

| Internal Reference Voltage Drift                                    | Full                   | V       | -1.11          | 300   | -1.41             | -1.11                   | 300    | -1.41                | μV/°C             |   |

| Amplifier Input Impedance                                           | +25°C                  | v       |                | 50    |                   |                         | 50     |                      | kΩ                |   |

| Amplifier Bandwidth                                                 | +25°C                  | v       |                | 300   |                   |                         | 300    |                      | kHz               |   |

| REFERENCE INPUT <sup>4</sup>                                        |                        |         |                |       |                   |                         |        |                      |                   |   |

| Reference Input Impedance                                           | +25°C                  | v       |                | 3     |                   |                         | 3      |                      | kΩ                |   |

| Reference Multiplying Bandwidth <sup>5</sup>                        | +25°C                  | V       |                | 40    |                   |                         | 40     |                      | MHz               |   |

| OUTPUT PERFORMANCE                                                  |                        |         |                |       |                   |                         |        |                      |                   |   |

| Full-Scale Output Current <sup>6</sup>                              | +25°C                  | v       |                | 20.48 |                   |                         | 20.48  |                      | mA                |   |

| Output Compliance Range                                             | +25°C                  | IV      | -1.2           |       | +3                | -1.2                    |        | +3                   | V                 |   |

| Output Resistance                                                   | +25°C                  | IV      | 2.0            | 2.5   | 3.0               | 2.0                     | 2.5    | 3.0                  | kΩ                |   |

| Output Capacitance                                                  | +25°C                  | V       |                | 30    |                   |                         | 30     |                      | pF                |   |

| Output Update Rate <sup>7</sup>                                     | +25°C                  | IV      | 100            | 110   |                   | 80                      | 90     |                      | MSPS              |   |

| Output Settling Time (t <sub>ST</sub> ) <sup>8</sup>                |                        |         |                |       |                   |                         |        |                      |                   |   |

| Current Settling                                                    | +25°C                  | V       |                | 30    |                   |                         | 30     |                      | ns                |   |

| Voltage Settling ( $R_L = 50 \Omega$ )                              | +25°C                  | V       |                | 30    |                   |                         | 30     |                      | ns                |   |

| Output Propagation Delay (tpD)9                                     | +25°C                  | V       |                | 8     |                   |                         | 11     |                      | ns                |   |

| Glitch Impulse <sup>10</sup>                                        | +25°C                  | V       |                | 100   |                   |                         | 100    |                      | pV-s              |   |

| Output Slew Rate <sup>11</sup>                                      | +25°C                  | ·V      |                | 400   |                   |                         | 400    |                      | V/µs              |   |

| Output Rise Time <sup>11</sup>                                      | +25°C                  | V       |                | 3     |                   |                         | 3      |                      | ns                |   |

| Output Fall Time11                                                  | +25°C                  | V       |                | 2     |                   |                         | 2      |                      | ns                |   |

| Parameter (Conditions)                           | Temp  | Test<br>Level | AD971<br>Min | 2JN/JP<br>Typ | Max          | AD971<br>Min | 3JN/JP<br>Typ | Max | Units |

|--------------------------------------------------|-------|---------------|--------------|---------------|--------------|--------------|---------------|-----|-------|

| DIGITAL INPUTS                                   |       |               |              |               |              |              |               |     |       |

| Logic "1" Voltage                                | Full  | VI            | -1.0         | -0.8          |              | 2.0          |               |     | v     |

| Logic "0" Voltage                                | Full  | VI            |              | -1.7          | -1.5         |              |               | 0.8 | V     |

| Logic "1" Current                                | Full  | VI            |              |               | 20           |              |               | 20  | μΑ    |

| Logic "0" Current                                | Full  | VI            |              |               | 10           |              |               | 600 | μA    |

| Input Capacitance                                | +25°C | V             |              | 3             |              |              | 3             |     | pF    |

| Input Setup Time (t <sub>S</sub> ) <sup>12</sup> | +25°C | V             |              | 3 3           |              |              | 3             |     | ns    |

| Input Hold Time (t <sub>H</sub> ) <sup>13</sup>  | +25℃  | V             |              | 3             |              |              | 3             |     | ns    |

| Latch Pulse Width (t <sub>LPW</sub> )            |       |               |              | 0.5           |              |              |               |     |       |

| (Transparent)                                    | +25℃  | V             |              | 2.5           |              |              | 4             |     | ns    |

| AC LINEARITY14                                   |       |               |              |               |              |              |               |     |       |

| Spurious-Free Dynamic Range                      | +25°C | v             |              | -60           |              |              | -55           |     | dBc   |

| POWER SUPPLY <sup>15</sup>                       |       |               |              |               |              |              |               |     |       |

| Positive Supply Current (+5.0 V)                 | +25°C | I             |              |               |              |              | 10            | 20  | mA    |

|                                                  | Full  | VI            |              |               |              |              |               | 23  | mA    |

| Negative Supply Current (-5.2 V)                 | +25°C | I             |              | 130           | 160          |              | 135           | 165 | mA    |

|                                                  | Full  | VI            |              |               | 170          |              |               | 175 | mA    |

| Nominal Power Dissipation                        | +25℃  | V             |              | 676           | 10.0011.0001 |              | 726           |     | mW    |

| Power Supply                                     |       |               |              |               |              |              |               |     |       |

| Rejection Ratio (PSRR)16                         | +25°C | I             |              | 50            | 350          |              | 50            | 350 | μA/V  |

individually, and b eyond which the serviceability of the circuit may be impaired.

rating conditions for an extended period of time may affect device reliability.

$\theta_{JA} = 48^{\circ}\text{C/W}; \ \theta_{JC} = 10^{\circ}\text{C/W}.$ 28 pin FLCC 3Measured as error of the ratio of fall-se ominal); ratio is nominally urrent to

through R<sub>SET</sub> (160 ) iving REFERENCE Full-scale variations among devices are N direct

<sup>5</sup>Frequency at which a 3 dB reduction in output of DAC is o 50 dulation at m

<sup>6</sup>Based on  $I_{FS} = 128 (V_{REF}/R_{SET})$  when using internal amplifi

<sup>7</sup>Output settling to 0.1%.

Measured at midscale transition, to ±0.024%.

<sup>9</sup>Measured from falling edge of LATCH ENABLE signal to 50% point of full-scale

<sup>10</sup>Glitch impulse combines the absolute value of positive and negative transitions operating in la

<sup>11</sup>Measured with  $R_L = 50 \Omega$  and DAC operating in latched mode.

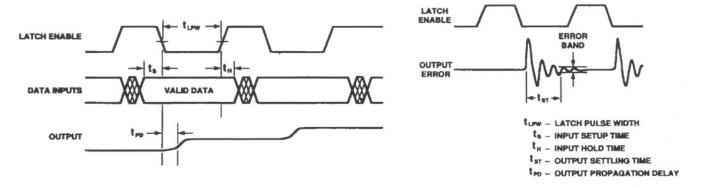

<sup>12</sup>Data must remain stable prior to falling edge of LATCH ENABLE signal for specified time.

<sup>13</sup>Data must remain stable after rising edge of LATCH ENABLE signal for specified time.

14Update rate ≤50 MSPS; output frequency = 5 MHz.

<sup>15</sup>Supply voltages should remain stable within ±5% for normal operation.

<sup>16</sup>Measured at ±5% of +V<sub>s</sub> (AD9713 only) and -V<sub>s</sub> (AD9712 or AD9713) using external reference.

Specifications subject to change without notice.

#### **EXPLANATION OF TEST LEVELS**

#### Level

- I 100% production tested.

- II 100% production tested at +25°C, and sample tested at specified temperatures.

- III Sample tested only.

- IV Parameter is guaranteed by design and characterization testing.

- V Parameter is a typical value only.

- VI All devices are 100% production tested at +25°C. 100% production tested at temperature extremes for extended temperature devices; sample tested at temperature extremes for commercial/industrial devices.

#### **ORDERING GUIDE**

| Model                | Description                                       | Package<br>Option* |  |

|----------------------|---------------------------------------------------|--------------------|--|

| AD9712JN<br>AD9712JP | ECL-Compatible Plastic DIP<br>ECL-Compatible PLCC | N-28<br>P-28A      |  |

| AD9713JN<br>AD9713JP | TTL-Compatible Plastic DIP TTL-Compatible PLCC    | N-28<br>P-28A      |  |

\*N = Plastic DIP; P = Plastic Leaded Chip Carrier.

## AD9713/AD9713

#### AD9712/AD9713 PIN DESCRIPTIONS

| rin<br>No. | Name                            | Function                                                                                                                                                                                                                                                                     |

|------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -10        | D <sub>2</sub> -D <sub>11</sub> | Ten of twelve digital input bits.                                                                                                                                                                                                                                            |

| 1          | D <sub>12</sub> (LSB)           | Least Significant Bit (LSB) of digital input word.                                                                                                                                                                                                                           |

| 2          | DIGITAL -Vs                     | One of two negative digital supply pins; nominally -5.2 V.                                                                                                                                                                                                                   |

| 3          | ANALOG RETURN                   | Analog ground return. This point and the reference side of the DAC load resistors should be connected to the same potential (nominally ground).                                                                                                                              |

| 4          | I <sub>OUT</sub>                | Analog current output; full-scale output occurs with digital inputs at all "1."                                                                                                                                                                                              |

| 5          | ANALOG -Vs                      | One of two negative analog supply pins; nominally -5.2 V.                                                                                                                                                                                                                    |

| 6          | I <sub>OUT</sub>                | Complementary analog current output; zero scale output occurs with digital inputs at all "1."                                                                                                                                                                                |

| 7          | REFERENCE IN                    | Normally connected to CONTROL AMP OUT (Pin 18). Direct line to DAC current switch network. Voltage changes at this point have a direct effect on the full-scale output. Full-scale current output = 128 (Reference voltage/R <sub>SET</sub> ) when using internal amplifier. |

| 8          | CONTROL AMPOUT                  | Normally connected to BEFERENCE IN (Pin 17). Output of internal control amplifier, which provides a temperature compensated drive level to the current switch network.                                                                                                       |

| 9          | CONTROL AMP IN                  | Normaly connected to REFERENCE OUT (Pin 20) if not connected to external reference. Full-scale current out = 128  (Reference voltage/R <sub>SNT</sub> ) when using internal amplifier.                                                                                       |

| 0          | REFERENCE OUT                   | Normally connected to CONTROL AMP IN (Pin 19). Internal voltage reference, nominally -1.26 V.                                                                                                                                                                                |

| 1          | DIGITAL -V <sub>s</sub>         | One of two negative digital supply pins; nominally -5.2 V.                                                                                                                                                                                                                   |

| !          | REFERENCE GROUND                | Ground return for the internal voltage reference and amplifier.                                                                                                                                                                                                              |

| 3          | DIGITAL +V <sub>s</sub>         | Positive digital supply pin; used only on the AD9713; nominally +5 V.                                                                                                                                                                                                        |

| 4          | R <sub>SET</sub>                | Connection for external resistance reference. Full-scale current out = 128 (Reference voltage/R <sub>SET</sub> ) when using internal amplifier.                                                                                                                              |

| 5          | ANALOG -V <sub>s</sub>          | One of two negative analog supply pins; nominally -5.2 V.                                                                                                                                                                                                                    |

| 5          | LATCH ENABLE                    | Transparent latch control line.                                                                                                                                                                                                                                              |

| 7          | DIGITAL GROUND                  | Digital ground return.                                                                                                                                                                                                                                                       |

| 8          | D <sub>1</sub> (MSB)            | Most Significant Bit (MSB) of digital input word.                                                                                                                                                                                                                            |

AD9712/AD9713 Timing Diagram

### AD9712/AD9713

#### THEORY AND APPLICATIONS

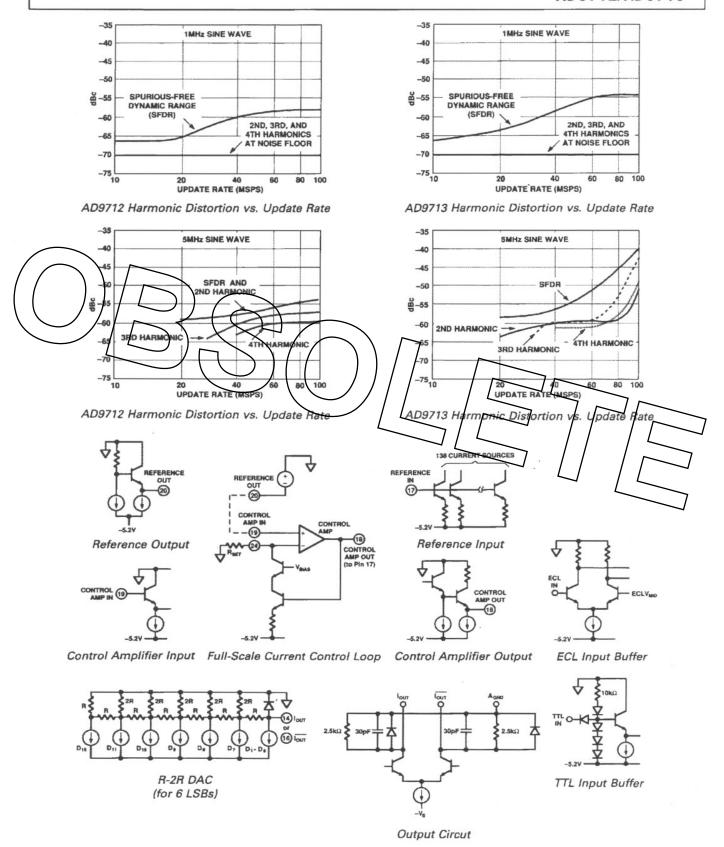

The AD9712 and AD9713 high speed digital-to-analog converters utilize Most Significant Bit (MSB) decoding and segmentation techniques to reduce glitch impulse and maintain linearity without trimming.

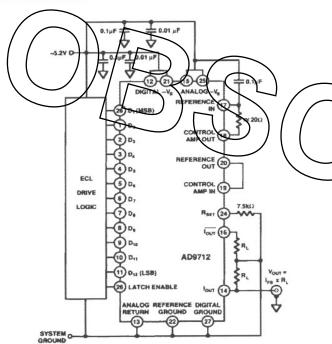

As shown in the functional block diagram, the design is based on four main subsections: the Decoder/Driver circuits, the Transparent Latches, the Switch Network and the Control Amplifier. An internal band-gap reference is also included to allow operation with a minimum of external components.

#### **Digital Inputs**

The AD9712 employs single-ended ECL-compatible inputs for data inputs D<sub>1</sub>-D<sub>12</sub> and LATCH ENABLE. The internal ECL midpoint reference is designed to match 10K ECL device thresholds. On the AD9713, a TTL translator is added at each input; with this exception, the AD9712 and AD9713 are identical

In the Decoder/Driver section, the four MSBs (D<sub>1</sub>-D<sub>4</sub>) are decoded to 13 "thermometer code" lines. An equalizing delay is included for the right Least Significant Bits (LSBs) and LATCH ENABLE. This delay minimizes data skew, and data scup and hald times at the latch inputs this is important when operating the latches in the transparent mode. Without the delay, skew caused by the decoding circuits would degrade glitch impulse.

The latches operate in their transparent mode when LATCH ENABLE (Pin 26) is at logic level "0." The latches can be used to synchronize data to the current switches by applying a narrow LATCH ENABLE pulse with proper data setup and hold times as shown in the timing diagram. With an external transparent latch at each data input clocked out of phase with the DAC, the AD9712/AD9713 operates in a master slave (edge-triggered) mode.

Although the AD9712/AD9713 chip is designed to provide isolation from digital inputs to the outputs, some coupling of digital transitions is inevitable, especially with TTL or CMOS inputs applied to the AD9713. Digital feedthrough can be reduced by forming a low-pass filter using a resistor in series with the capacitance of each digital input.

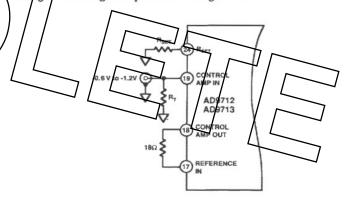

#### References

As shown in the functional block diagram, the internal band-gap reference, control amplifier and reference input are pinned out for maximum user flexibility when setting the reference.

When using the internal reference, REFERENCE OUT (Pin 20) should be connected to CONTROL AMP IN (Pin 19). CONTROL AMP OUT (Pin 18) should be connected to REFERENCE IN (Pin 17) through an 18  $\Omega$  resistor. A 0.1  $\mu$ F ceramic capacitor from Pin 17 to  $-V_S$  (Pin 15) improves settling by decoupling switching noise from the current sink base line. A reference current cell provides feedback to the control amp by sinking current through  $R_{\rm SET}$  (Pin 24).

Full-scale output current is determined by the voltage at CONTROL AMP IN  $(V_{\rm REF})$  and  $R_{\rm SET}$  according to the equation:

$$I_{OUT}(FS) = V_{REF}/R_{SET} \times 128.$$

The internal reference is nominally -1.26 V with a tolerance of  $\pm 10\%$  and typical drift over temperature of 300  $\mu$ V/°C. If

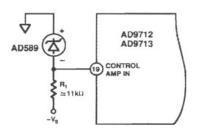

greater accuracy or better temperature stability is required, an external reference can be utilized. The AD589 reference shown in Figure 1 features  $\pm 10$  ppm/°C drift over temperatures from 0 to +70°C.

Figure 1. Use of AD589 as External Reference

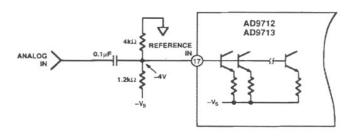

Two modes of multiplying operation are possible with the AD9712/AD9713. Signals with bandwidths up to 400 kHz and input swings from -0.1 V to -1.2 V can be applied to the CONTROL AMP input as shown in Figure 2. Because the control amplifier is internally compensated, the 0.1  $\mu F$  capacitor at Pin 17 can be eliminated to maximize the multiplying bandwidth. However, it should be noted that settling time for changes to the digital inputs will be degraded.

Figure 2. Low Frequency Multiplying Circuit

The REFERENCE IN pin can also be driven directly for wider bandwidth multiplying operation. The analog signal for this mode of operation must have a signal swing in the range of -4 V to -5.2 V. This can be implemented by capacitively coupling into REFERENCE IN an ac signal and establishing a dc bias of -4.0 V to -5.2 V, as shown in Figure 3; or by driving REFERENCE IN with a low impedance op amp whose signal swing is limited to the stated range.

Figure 3. Wideband Multiplying Circuit

## AD9712/AD9713

Outputs

The Switch Network controls complementary current outputs  $I_{OUT}$  and  $\overline{I}_{OUT}$ . As indicated earlier,  $D_1$ – $D_4$  are decoded into 15 "thermometer code" lines which drive matched current sources.  $D_5$  and  $D_6$  control weighted current sources; and  $D_7$ – $D_{12}$  are applied to the R-2R network.

This segmentation reduces frequency domain errors due to glitch impulse. Current is steered to either  $I_{OUT}$  or  $\overline{I}_{OUT}$  in proportion to the digital input code. The sum of the two currents is always equal to the full-scale output current minus one LSB.

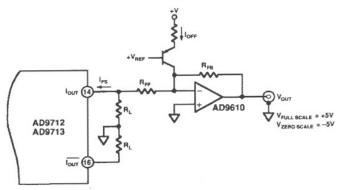

The current output can be converted to a voltage by resistive loading as shown in Figure 4. Both  $I_{\rm OUT}$  and  $\overline{I_{\rm OUT}}$  should be loaded equally for best overall performance. The voltage which is developed is the product of the output current and the value of the load resistor.

Figure 4. Typical Resistive Load Connection

When operating at the nominal full-scale current of 20.48 mA, the voltage swing will be from 0 to -1.024 V across 50  $\Omega$  resistors. Bipolar outputs are possible by sourcing a current equal to half the DAC full-scale current into the load resistor.

An alternate method of converting the current output to voltage is by driving the summing node of an operational amplifier directly with a feedback resistor selected according to the equation:

$$R_{FB} = V_{OUT}(FS) / I_{OUT}(FS)$$

A current feedback amplifier such as the AD9610 offers significantly faster settling and greater bandwidth than a conventional voltage feedback op amp. The feedback resistor for the AD9610 must be 1.5 k $\Omega$  or greater to maintain stability. This value for  $R_{\rm FB}$ , along with the 20.48 mA full-scale output current, results in a full-scale output of 30 V, which exceeds the output range of the AD9610.

Full-scale output voltage can be reduced by either reducing the DAC's full-scale output current, or by using a current divider at

the DAC output as shown in Figure 5. Reducing DAC full-scale output current degrades both linearity and settling time; therefore, the current divider method is preferable.

Figure 5. I/V Conversion Using Current Feedback Amp

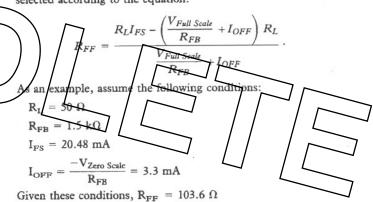

The DAC output is not clamped at virtual ground in this configuration because of the series resistance  $R_{\rm FF}$ . The value of  $R_{\rm FF}$  is selected according to the equation:

Power and Grounding

Maintaining low noise on power supplies and ground is critical for obtaining optimum results with the AD9712 or AD9713. DACs are most often used in circuits which are predominantly digital. To preserve 12-bit performance, especially at conversion speeds up to 100 MSPS, special precautions are necessary for power supplies and grounding.

Ideally, the DAC should have a separate analog ground plane. All ground pins of the DAC, as well as reference and analog output components, should be tied directly to this analog ground plane. The DAC's ground plane should be connected to the system ground plane at a single point.

Ferrite beads, along with high frequency, low inductance decoupling capacitors, should be used for the supply connections to isolate digital switching currents from the DAC supply pins. Separate isolation networks for the digital and analog supply connections will further reduce supply noise coupling to the output.

Molded socket assemblies should be avoided even when prototyping circuits with the AD9712 or AD9713. When the DAC cannot be directly soldered into the board, individual pin sockets such as AMP #6-330808-0 (knock-out end), or #60330808-3 (open end) should be used. These have much less effect on interlead capacitance than do molded assemblies.

## AD9712/AD9713

AD9712/AD9713 Equivalent Circuits

0.085/0.110 (2.16/2.79)