TRI-STATE® is a registered trademark of National Semiconductor Corporation.

©1997,1998 National Semiconductor Corporation

http://www.national.com

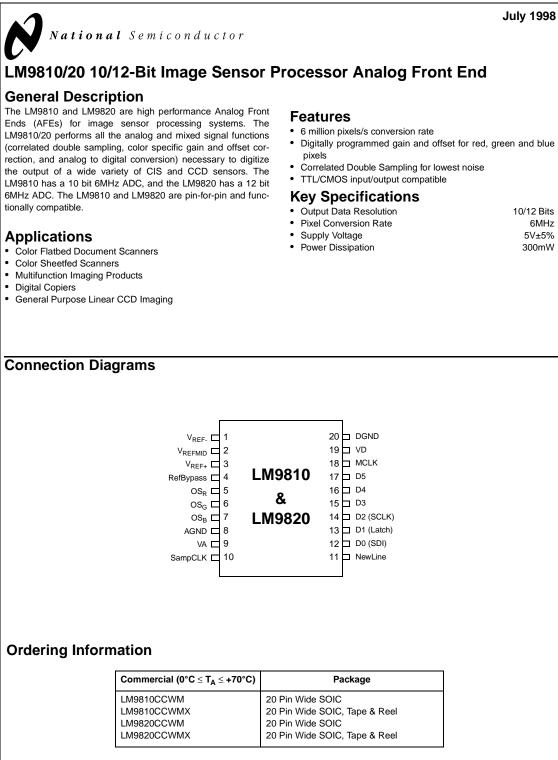

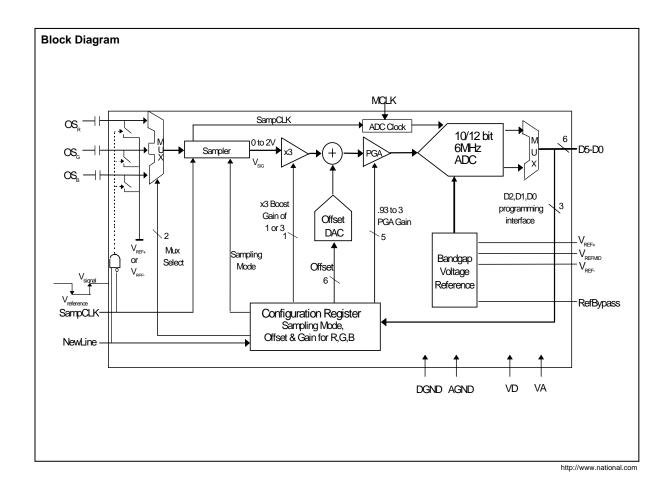

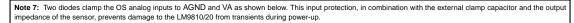

LM9810/20 10/12-Bit Image Sensor Processor Analog Front End

# Absolute Maximum Ratings (Notes 1 & 2)

| Positive Supply Voltage (V+=VA=VD)         |                  |

|--------------------------------------------|------------------|

| With Respect to GND=AGND=DGND              | 6.5V             |

| Voltage On Any Input or Output Pin         | -0.3V to V++0.3V |

| Input Current at any pin (Note 3)          | ±25mA            |

| Package Input Current (Note 3)             | ±50mA            |

| Package Dissipation at $T_A = 25^{\circ}C$ | (Note 4)         |

| ESD Susceptibility (Note 5)                |                  |

| Human Body Model                           | 2000V            |

| Soldering Information                      |                  |

| Infrared, 10 seconds (Note 6)              | 300°C            |

| Storage Temperature                        | -65°C to +150°C  |

# **Operating Ratings** (Notes 1 & 2)

# **Electrical Characteristics**

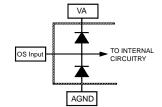

The following specifications apply for AGND=DGND=0V, VA=VD=+5.0V<sub>DC</sub>,  $f_{MCLK}$ =24MHz,  $R_s$ =25 $\Omega$ . Boldface limits apply for  $T_A=T_J=T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A=T_J=25^{\circ}C$ . (Notes 7, 8, & 12)

| Symbol               | Parameter                                                               | Conditions                                                        | Typical<br>(Note 9) | Limits<br>(Note 10) | Units<br>(Limits)      |  |

|----------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------|---------------------|------------------------|--|

| CCD/CIS S            | ource Requirements for Full Specified A                                 | ccuracy and Dynamic Range (Note                                   | 12)                 |                     |                        |  |

| V <sub>OS PEAK</sub> | Sensor's Maximum Peak Differential Signal Range                         | Gain = 0.933<br>Gain = 3.0<br>Gain = 9.0                          | 2.1<br>0.65<br>0.21 |                     | V<br>V<br>V            |  |

| Analog Inp           | but Characteristics                                                     |                                                                   |                     |                     |                        |  |

|                      | OS <sub>R</sub> , OS <sub>G</sub> , OS <sub>B</sub> Input Capacitance   |                                                                   | 5                   |                     | pF                     |  |

|                      |                                                                         | Measured with $OS = 3.5V_{DC}$<br>CDS disabled, selected OS input | 20                  | 25                  | μA (max)               |  |

|                      | $OS_R$ , $OS_G$ , $OS_B$ Input Leakage Current                          | CDS disabled, unselected OS input                                 | 10                  |                     | nA                     |  |

| Coarse Co            | Ior Balance PGA Characteristics                                         |                                                                   |                     | •                   |                        |  |

|                      | Monotonicity                                                            |                                                                   |                     | 5                   | bits (min)             |  |

|                      | G <sub>0</sub> (Minimum PGA Gain)                                       | PGA Setting = 0                                                   | 0.93                | .90<br>.96          | V/V (min)<br>V/V (max) |  |

|                      | G <sub>31</sub> (Maximum PGA Gain)                                      | PGA Setting = 31                                                  | 3.0                 | 2.96<br>3.15        | V/V (min)<br>V/V (max) |  |

|                      | x3 Boost Gain                                                           | x3 Boost Setting On<br>(bit B5 of Gain Register is set)           | 3.0                 | 2.93<br>3.05        | V/V (min)<br>V/V (max) |  |

|                      | Gain Error at any gain (Note 13)                                        |                                                                   | ±0.4                | 1.67                | % (max)                |  |

| Internal Re          | eference Characteristics                                                |                                                                   |                     |                     |                        |  |

| V <sub>REFMID</sub>  | Mid Supply Output Voltage                                               |                                                                   | 2.5                 |                     | V                      |  |

| V <sub>REF+</sub>    | Positive Reference Output Voltage                                       |                                                                   | 3.5                 |                     | V                      |  |

| V <sub>REF-</sub>    | Negative Reference Output Voltage                                       |                                                                   | 1.5                 |                     | V                      |  |

| $\Delta V_{REF}$     | Differential Reference Voltage<br>V <sub>REF+</sub> - V <sub>REF-</sub> |                                                                   | 2.0                 |                     | V                      |  |

| Symbol                                                           | Parameter                                                                                                                                           | Conditions                                                                                          | Typical<br>(Note 9)                 | Limits<br>(Note 10)                        | Units<br>(Limits)     |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------|-----------------------|

| ADC Chara                                                        | acteristics                                                                                                                                         |                                                                                                     | (Note 5)                            | (1010-10)                                  | (2                    |

|                                                                  | Resolution with No Missing Codes                                                                                                                    |                                                                                                     |                                     | 10                                         | bits (min             |

| INL                                                              | Integral Non-Linearity Error (Note 11)                                                                                                              |                                                                                                     | ±0.35                               | ±1.5                                       | LSB (max              |

| DNL                                                              | Differential Non-Linearity                                                                                                                          |                                                                                                     | ±0.35                               | ±1.0                                       | LSB (max              |

|                                                                  | nel Linearity (Note 14)                                                                                                                             |                                                                                                     | 10.25                               | 11.0                                       | LOD (IIIa)            |

| INL                                                              | Integral Non-Linearity Error (Note 11)                                                                                                              |                                                                                                     | +0.0                                |                                            | LSB                   |

|                                                                  |                                                                                                                                                     |                                                                                                     | ±0.9                                |                                            |                       |

| DNL                                                              | Differential Non-Linearity                                                                                                                          |                                                                                                     | ±0.40                               |                                            | LSB                   |

| Static Offs                                                      | et DAC Characteristics                                                                                                                              | 1                                                                                                   |                                     |                                            |                       |

|                                                                  | Monotonicity                                                                                                                                        |                                                                                                     |                                     | 6                                          | bits (min             |

|                                                                  | Offset DAC LSB size                                                                                                                                 | PGA gain = 1                                                                                        | 5                                   | 3.4<br>6.4                                 | LSB (mir<br>LSB (ma   |

|                                                                  | Offset DAC Adjustment Range                                                                                                                         | PGA gain = 1                                                                                        | ±150                                | ±140                                       | LSB (mir              |

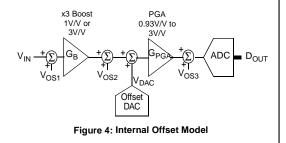

| System Ch                                                        | haracteristics (see section 1.7.1, Internal                                                                                                         | Offsets)                                                                                            | •                                   |                                            |                       |

| С                                                                | Analog Channel Gain Constant<br>(ADC Codes/V)                                                                                                       | Includes voltage reference<br>variation, gain setting = 1                                           | 502                                 | 468<br>532                                 | LSB (mir<br>LSB (ma   |

| V <sub>OS1</sub>                                                 | Pre-Boost Analog Channel Offset Error,<br>CCD Mode                                                                                                  |                                                                                                     | 4.4                                 | -7.2<br>+15.7                              | LSB (mir<br>LSB (ma   |

| V <sub>OS1</sub>                                                 | Pre-Boost Analog Channel Offset Error,<br>CIS Mode                                                                                                  |                                                                                                     | 4.5                                 | -6.5<br>+15.2                              | LSB (mir<br>LSB (ma   |

| V <sub>OS2</sub>                                                 | Pre-PGA Analog Channel Offset Error                                                                                                                 |                                                                                                     | -10                                 | -28<br>+5.3                                | LSB (miı<br>LSB (ma   |

| V <sub>OS3</sub>                                                 | Post-PGA Analog Channel Offset Error                                                                                                                |                                                                                                     | -11                                 | -30.6<br>+7.3                              | LSB (mir<br>LSB (ma   |

| The followin<br>T <sub>A</sub> =T <sub>J</sub> =T <sub>MIN</sub> | <b>D Electrical Characteristics</b><br>ag specifications apply for AGND=DGND=0V,<br>to $T_{MAX}$ ; all other limits $T_A=T_J=25^{\circ}C$ . All LSI | VA=VD=+5.0V <sub>DC</sub> , f <sub>MCLK</sub> =24MHz, R<br>B limits are in units of the LM9820<br>I | s=25Ω. Boldfac<br>'s 12 bit ADC. (N | ce limits app<br>otes 7, 8, & <sup>2</sup> | ly for<br>2)<br>Units |

| Symbol                                                           | Parameter                                                                                                                                           | Conditions                                                                                          | (Note 9)                            | (Note 10)                                  | (Limits               |

| ADC Chara                                                        | acteristics                                                                                                                                         |                                                                                                     |                                     |                                            |                       |

|                                                                  | Resolution with No Missing Codes                                                                                                                    |                                                                                                     |                                     | 12                                         | bits (min             |

| INL                                                              | Integral Non-Linearity Error (Note 11)                                                                                                              |                                                                                                     | ±1.1                                | ±4.0                                       | LSB (ma               |

| DNL                                                              | Differential Non-Linearity                                                                                                                          |                                                                                                     | ±0.6                                | +1.75<br>-1.0                              | LSB (ma               |

| Full Chann                                                       | l<br>nel Linearity (Note 14)                                                                                                                        | I                                                                                                   | <b>ļ</b>                            | 1                                          | L                     |

| INL                                                              | Integral Non-Linearity Error (Note 11)                                                                                                              |                                                                                                     | ±3.4                                |                                            | LSB                   |

|                                                                  | 1                                                                                                                                                   |                                                                                                     |                                     | 1                                          |                       |

| Symbol                                                                                                                                                              | Parameter                                                                                                                                                                                                                                                                                                                                                                                             | Conditions                                                                                                                                                                                                                                                                                                 | Typical<br>(Note 9)                                               | Limits<br>(Note 10)                             | Units<br>(Limits)                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Static Offs                                                                                                                                                         | et DAC Characteristics                                                                                                                                                                                                                                                                                                                                                                                | ļ                                                                                                                                                                                                                                                                                                          |                                                                   |                                                 |                                                                                                          |

|                                                                                                                                                                     | Monotonicity                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |                                                                   | 6                                               | bits (min                                                                                                |

|                                                                                                                                                                     | Offset DAC LSB size                                                                                                                                                                                                                                                                                                                                                                                   | PGA gain = 1                                                                                                                                                                                                                                                                                               | 20                                                                | 14<br>26                                        | LSB (mir<br>LSB (max                                                                                     |

|                                                                                                                                                                     | Offset DAC Adjustment Range                                                                                                                                                                                                                                                                                                                                                                           | PGA gain = 1                                                                                                                                                                                                                                                                                               | ±590                                                              | ±575                                            | LSB (mir                                                                                                 |

| System Ch                                                                                                                                                           | aracteristics (see section 1.7.1, Internal                                                                                                                                                                                                                                                                                                                                                            | Offsets)                                                                                                                                                                                                                                                                                                   |                                                                   | 1                                               |                                                                                                          |

| С                                                                                                                                                                   | Analog Channel Gain Constant<br>(ADC Codes/V)                                                                                                                                                                                                                                                                                                                                                         | Includes voltage reference<br>variation, gain setting = 1                                                                                                                                                                                                                                                  | 2008                                                              | 1873<br>2129                                    | LSB (mir<br>LSB (ma                                                                                      |

| V <sub>OS1</sub>                                                                                                                                                    | Pre-Boost Analog Channel Offset Error,<br>CCD Mode                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                            | 17.6                                                              | -32.1<br>+68.9                                  | LSB (mir<br>LSB (ma                                                                                      |

| V <sub>OS1</sub>                                                                                                                                                    | Pre-Boost Analog Channel Offset Error,<br>CIS Mode                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                            | 18                                                                | -22.2<br>+57                                    | LSB (mir<br>LSB (ma                                                                                      |

| V <sub>OS2</sub>                                                                                                                                                    | Pre-PGA Analog Channel Offset Error                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                            | -40                                                               | -94.3<br>+16.4                                  | LSB (mir<br>LSB (ma                                                                                      |

| V <sub>OS3</sub>                                                                                                                                                    | Post-PGA Analog Channel Offset Error                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                            | -44                                                               | -121<br>+28                                     | LSB (mir<br>LSB (ma                                                                                      |

| The followin                                                                                                                                                        | Logic Electrical Characte                                                                                                                                                                                                                                                                                                                                                                             | eristics                                                                                                                                                                                                                                                                                                   |                                                                   |                                                 |                                                                                                          |

|                                                                                                                                                                     | g specifications apply for AGND=DGND=0V,<br>to $T_{MAX}$ ; all other limits $T_A=T_J=25^{\circ}C$ . (Notes                                                                                                                                                                                                                                                                                            | VA=VD=+5.0V <sub>DC</sub> , f <sub>MCLK</sub> =24MHz, R <sub>s</sub> =25<br>5 7 & 8)                                                                                                                                                                                                                       | Ω. Boldfac                                                        | e limits appl                                   | y for                                                                                                    |

| Symbol                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                            | <ul> <li>Ω. Boldfac</li> <li>Typical</li> <li>(Note 9)</li> </ul> | e limits appl<br>Limits<br>(Note 10)            | y for<br>Units<br>(Limits)                                                                               |

| Symbol                                                                                                                                                              | to $T_{MAX}$ ; all other limits $T_A = T_J = 25^{\circ}C$ . (Note:                                                                                                                                                                                                                                                                                                                                    | Conditions                                                                                                                                                                                                                                                                                                 | Typical                                                           | Limits                                          | Units                                                                                                    |

| Symbol                                                                                                                                                              | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter                                                                                                                                                                                                                                                                                                      | Conditions                                                                                                                                                                                                                                                                                                 | Typical                                                           | Limits                                          | Units<br>(Limits)                                                                                        |

| Symbol<br>D0-D2, MC                                                                                                                                                 | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha                                                                                                                                                                                                                                                            | Conditions                                                                                                                                                                                                                                                                                                 | Typical                                                           | Limits<br>(Note 10)                             | Units<br>(Limits)<br>V (max)                                                                             |

| Symbol<br>D0-D2, MC<br>V <sub>IN(1)</sub>                                                                                                                           | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha<br>Logical "1" Input Voltage                                                                                                                                                                                                                               | Conditions aracteristics VD=5.25V                                                                                                                                                                                                                                                                          | Typical                                                           | Limits<br>(Note 10)<br>2.0                      | Units                                                                                                    |

| Symbol<br>D0-D2, MC<br>V <sub>IN(1)</sub><br>V <sub>IN(0)</sub>                                                                                                     | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha<br>Logical "1" Input Voltage<br>Logical "0" Input Voltage                                                                                                                                                                                                  | Conditions       aracteristics       VD=5.25V       VD=4.75V       VIN=VD                                                                                                                                                                                                                                  | Typical<br>(Note 9)                                               | Limits<br>(Note 10)<br>2.0                      | Units<br>(Limits)<br>V (max)<br>V (min)<br>µA(max                                                        |

| Symbol<br>D0-D2, MC<br>V <sub>IN(1)</sub><br>V <sub>IN(0)</sub><br>I <sub>IN</sub><br>C <sub>IN</sub>                                                               | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha<br>Logical "1" Input Voltage<br>Logical "0" Input Voltage<br>Input Leakage Current                                                                                                                                                                         | Conditions       aracteristics       VD=5.25V       VD=4.75V       VIN=VD                                                                                                                                                                                                                                  | Typical<br>(Note 9)                                               | Limits<br>(Note 10)<br>2.0                      | Units<br>(Limits)<br>V (max<br>V (min)<br>µA(max                                                         |

| Symbol<br>D0-D2, MC<br>V <sub>IN(1)</sub><br>V <sub>IN(0)</sub><br>I <sub>IN</sub><br>C <sub>IN</sub>                                                               | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha<br>Logical "1" Input Voltage<br>Logical "0" Input Voltage<br>Input Leakage Current<br>Input Capacitance                                                                                                                                                    | Conditions       aracteristics       VD=5.25V       VD=4.75V       VIN=VD                                                                                                                                                                                                                                  | Typical<br>(Note 9)                                               | Limits<br>(Note 10)<br>2.0                      | Units<br>(Limits)<br>V (max)<br>V (min)<br>µA(max                                                        |

| Symbol           D0-D2, MC           V <sub>IN(1)</sub> V <sub>IN(0)</sub> I <sub>IN</sub> C <sub>IN</sub> D0-D5 Digit                                              | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha<br>Logical "1" Input Voltage<br>Logical "0" Input Voltage<br>Input Leakage Current<br>Input Capacitance<br>tal Output Characteristics                                                                                                                      | s 7 & 8)<br>Conditions<br>aracteristics<br>VD=5.25V<br>VD=4.75V<br>V <sub>IN</sub> =VD<br>V <sub>IN</sub> =DGND<br>VD=4.75V, I <sub>OUT</sub> =-360µА                                                                                                                                                      | Typical<br>(Note 9)                                               | Limits<br>(Note 10)<br>2.0<br>0.8<br>2.4        | Units<br>(Limits)<br>V (max)<br>V (min)<br>µA(max<br>µA(max<br>pF                                        |

| Symbol           D0-D2, MC           V <sub>IN(1)</sub> V <sub>IN(0)</sub> I <sub>IN</sub> C <sub>IN</sub> D0-D5 Digit           V <sub>OUT(1)</sub>                | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha<br>Logical "1" Input Voltage<br>Logical "0" Input Voltage<br>Input Leakage Current<br>Input Capacitance<br>tal Output Characteristics<br>Logical "1" Output Voltage                                                                                        | Conditions         aracteristics         VD=5.25V         VD=4.75V         V <sub>IN</sub> =VD         V <sub>IN</sub> =DGND         VD=4.75V, I <sub>OUT</sub> =-360µA         VD=4.75V, I <sub>OUT</sub> =-10µA                                                                                          | Typical<br>(Note 9)                                               | Limits<br>(Note 10)<br>2.0<br>0.8<br>2.4<br>4.4 | Units<br>(Limits<br>V (max)<br>V (min)<br>μA(max)<br>μA(max)<br>pF                                       |

| Symbol           D0-D2, MC           VIN(1)           VIN(0)           IIN           CIN           D0-D5 Digi           VOUT(1)           VOUT(0)           IOUT    | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha<br>Logical "1" Input Voltage<br>Logical "0" Input Voltage<br>Input Leakage Current<br>Input Capacitance<br>tal Output Characteristics<br>Logical "1" Output Voltage<br>Logical "0" Output Voltage<br>TRI-STATE® Output Current                             | Conditions         aracteristics         VD=5.25V         VD=4.75V         VIN=VD         VIN=DGND         VD=4.75V, I <sub>OUT</sub> =-360µA         VD=4.75V, I <sub>OUT</sub> =-10µA         VD=5.25V, I <sub>OUT</sub> =-10µA         VD=5.25V, I <sub>OUT</sub> =1.6mA         V <sub>OUT</sub> =DGND | Typical<br>(Note 9)                                               | Limits<br>(Note 10)<br>2.0<br>0.8<br>2.4<br>4.4 | Units<br>(Limits<br>V (max<br>μA(max<br>μA(max<br>μA(max<br>μA(max<br>V (min)<br>V (min)<br>V (max<br>μA |

| Symbol           D0-D2, MC           VIN(1)           VIN(0)           I <sub>IN</sub> CIN           D0-D5 Digit           VOUT(1)           VOUT(0)           IOUT | to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub> =25°C. (Notes<br>Parameter<br>LK, NewLine, SampCLK Digital Input Cha<br>Logical "1" Input Voltage<br>Logical "0" Input Voltage<br>Input Leakage Current<br>Input Capacitance<br>tal Output Characteristics<br>Logical "1" Output Voltage<br>Logical "0" Output Voltage<br>TRI-STATE <sup>®</sup> Output Current<br>(D0-D5 only) | Conditions         aracteristics         VD=5.25V         VD=4.75V         VIN=VD         VIN=DGND         VD=4.75V, I <sub>OUT</sub> =-360µA         VD=4.75V, I <sub>OUT</sub> =-10µA         VD=5.25V, I <sub>OUT</sub> =-10µA         VD=5.25V, I <sub>OUT</sub> =1.6mA         V <sub>OUT</sub> =DGND | Typical<br>(Note 9)                                               | Limits<br>(Note 10)<br>2.0<br>0.8<br>2.4<br>4.4 | Units<br>(Limit<br>V (mar<br>µA(ma<br>µA(ma<br>pF<br>V (mir<br>V (mir<br>V (ma<br>V (ma<br>µA            |

220 320 Standby with input clocks stopped Standby with input clocks running 110 200 220

5

Operating

Digital Supply Current (Note 15)

µA (max)

µA (max)

μA

$\mathsf{I}_\mathsf{D}$

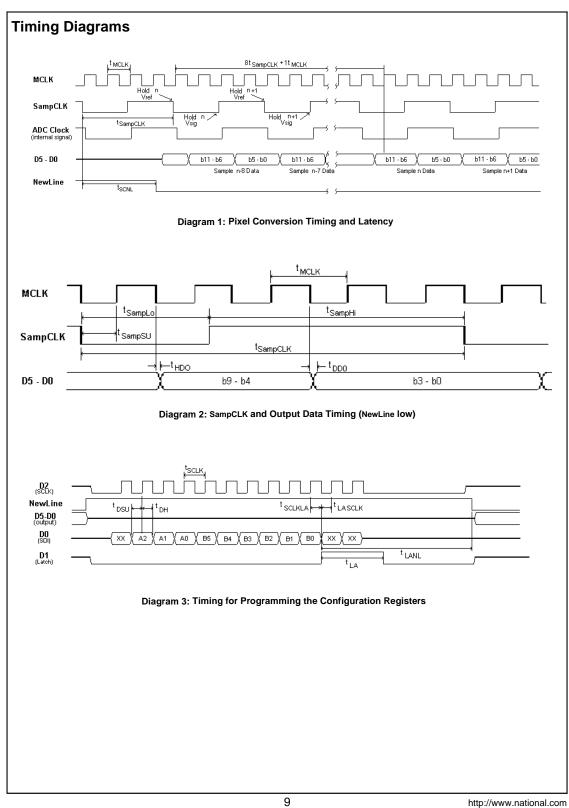

# **AC Electrical Characteristics**

The following specifications apply for AGND=DGND=0V, VA=VD=+5.0V<sub>DC</sub>,  $f_{MCLK}$ =24MHz,  $t_{MCLK}$ =1/ $f_{MCLK}$ ,  $t_r$ = $t_r$ =5ns, R<sub>s</sub>=25 $\Omega$ . Boldface limits apply for T<sub>A</sub>=T<sub>J</sub>=T<sub>MIN</sub> to T<sub>MAX</sub>; all other limits T<sub>A</sub>=T<sub>J</sub>=25°C. (Notes 7 & 8)

| Symbol               | Parameter                                                         | Conditions | Typical<br>(Note 9) | Limits<br>(Note 10) | Units<br>(Limits)             |

|----------------------|-------------------------------------------------------------------|------------|---------------------|---------------------|-------------------------------|

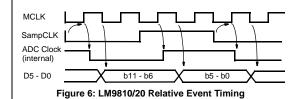

| f <sub>MCLK</sub>    | Maximum MCLK Frequency                                            |            |                     | 24                  | MHz (min)                     |

|                      | MCLK Duty Cycle                                                   |            |                     | 40<br>60            | % (min)<br>% (max)            |

| t <sub>MCLK</sub>    | MCLK period                                                       |            | 41                  |                     | ns (min)                      |

| t <sub>SCNL</sub>    | SampCLK falling edge before NewLine falling edge                  |            |                     | 3                   | t <sub>MCLK</sub> (min)       |

| t <sub>SampCLK</sub> | SampCLK period                                                    |            |                     | 4                   | t <sub>MCLK</sub> (min)       |

| t <sub>SampLo</sub>  | Low time for SampCLK                                              |            | 50                  |                     | ns (min)                      |

| t <sub>SampHi</sub>  | High time for SampCLK                                             |            | 50                  |                     | ns (min)                      |

| t <sub>SampSU</sub>  | SampCLK falling edge before rising<br>edge of MCLK                |            |                     | 4                   | ns (min)                      |

| t <sub>DDO</sub>     | falling edge of MCLK before new valid data                        |            |                     | 40                  | ns (max)                      |

| t <sub>HDO</sub>     | hold time of current data from falling edge of MCLK               |            |                     | 15                  | ns (min)                      |

| t <sub>SCLK</sub>    | D2(SCLK) Serial Clock Period                                      |            | 1                   |                     | t <sub>MCLK</sub> (min)       |

| t <sub>DSU</sub>     | Input data setup time before<br>D2(SCLK) rising edge              |            |                     | 0                   | ns (min)                      |

| t <sub>DH</sub>      | Input data hold time after D2(SCLK) rising edge                   |            |                     | 3                   | ns (min)                      |

| t <sub>SCLKLA</sub>  | D2(SCLK) rising edge after bit B0<br>before D1(Latch) rising edge |            |                     | 3                   | ns (min)                      |

| t <sub>LASCLK</sub>  | D1(Latch) rising edge before next<br>D2(SCLK) rising edge         |            |                     | 3                   | ns (min)                      |

| t <sub>LA</sub>      | High time for D1(Latch)                                           |            |                     | 3                   | t <sub>MCLK</sub> (min        |

| t <sub>LANL</sub>    | D1(Latch) rising edge before NewLine falling edge                 |            |                     | 3                   | t <sub>SampCLK</sub><br>(min) |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND=AGND=DGND=0V, unless otherwise specified.

Note 3: When the input voltage (V<sub>1N</sub>) at any pin exceeds the power supplies (V<sub>1N</sub><GND or V<sub>1N</sub>>VA or VD), the current at that pin should be limited to 25mA. The 50mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25mA to two.

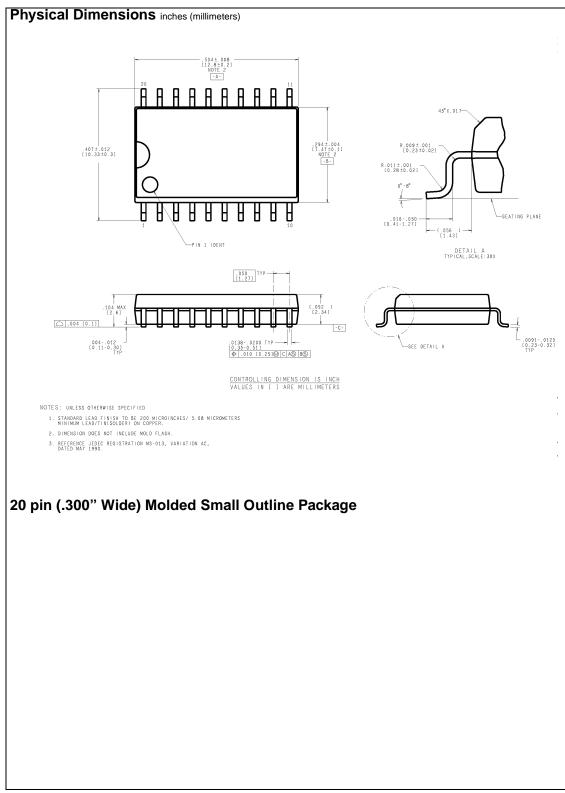

**Note 4:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_Jmax$ ,  $\Theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_Jmax - T_A) / \Theta_{JA}$ .  $T_Jmax = 150^{\circ}C$  for this device. The typical thermal resistance ( $\Theta_{JA}$ ) of this part when board mounted is 84°C/W for the M20B SOIC package.

Note 5: Human body model, 100pF capacitor discharged through a  $1.5 k\Omega$  resistor.

Note 6: See AN450 "Surface Mounting Methods and Their Effect on Product Reliability" or the section titled "Surface Mount" found in any National Semiconductor Linear Data Book for other methods of soldering surface mount devices.

6

Note 8: To guarantee accuracy, it is required that VA and VD be connected together to the same power supply with separate bypass capacitors at each supply pin.

**Note 9:** Typicals are at  $T_1 = T_A = 25^{\circ}$ C,  $f_{MCLK} = 24$ MHz, and represent most likely parametric norm.

Note 10: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 11: Integral non-linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that best fits the actual transfer function of the ADC.

Note 12:  $V_{REF}$  is defined as the CCD OS voltage for the reference period following the reset feedthrough pulse.  $V_{WHITE}$  is defined as the peak CCD pixel output voltage for a white (full scale) image with respect to the reference level,  $V_{REF}$ .  $V_{RFT}$  is defined as the peak positive deviation above  $V_{REF}$  of the reset feedthrough pulse. The maximum correctable range of pixel-to-pixel  $V_{WHITE}$  variation is defined as the maximum variation in  $V_{WHITE}$  (due to PRNU, light source intensity variation, optics, etc.) that the LM9810/20 can correct for using its internal PGA.

Note 13: PGA Gain Error is the maximum difference between the measured gain for any PGA code and the ideal gain calculated by using the formula  $Gain_{PGA}\left(\frac{V}{V}\right) = G_0 + X \frac{PGA \text{ code}}{32}$  where  $X = (G_{31} - G_0)\frac{32}{31}$ .

Note 14: Full Channel INL and DNL are tested with CDS disabled, negative signal polarity, and a single OS input with a gain register setting of 1 (000001b) and an offset register setting of 0 (000000b).

Note 15: The digital supply current (ID) does not include the load, data and switching frequency dependent current required to drive the digital output bus on pins (D5 - D0). The current required to switch the digital data bus can be calculated from: Isw = 2\*Nd\*Psw\*CL\*VD/tSampCLK where Nd is total number of data pins, Psw is the probability of each data bit switching, CL is the capacitive loading on each data pin, VD is the digital supply voltage and tSampCLK is the period of the SampCLK signal. Since Nd is 6, Psw should be .5, and VD is nominally 5V, the switching current can usually be calculated from: Isw = 30\*CL/tSampCLK. For example, if the capacitive load on each digital output pin (D5 - D0) is 20pF and the period of tts SampCLK is 1/6MHz or 167ns, then the digital switching current would be 7.2mA. The calculated digital switching current will be drawn through the VD pin and should be considered as part of the total power budget for he LM9810/20.

7

| Pin Descri                                            | Analog Power                                                                               |  |  |  |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| VA                                                    | -                                                                                          |  |  |  |  |  |  |  |

| VA .                                                  | This is the positive supply pin for the analog supply. It should be connected to a voltage |  |  |  |  |  |  |  |

|                                                       | source of +5V and bypassed to AGND with a                                                  |  |  |  |  |  |  |  |

|                                                       | 0.1µF monolithic capacitor in parallel with a                                              |  |  |  |  |  |  |  |

|                                                       | 10µF tantalum capacitor.                                                                   |  |  |  |  |  |  |  |

| AGND                                                  | This is the ground return for the analog sup                                               |  |  |  |  |  |  |  |

|                                                       | ply.                                                                                       |  |  |  |  |  |  |  |

|                                                       | Analog I/O                                                                                 |  |  |  |  |  |  |  |

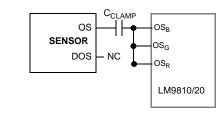

| OS <sub>R</sub> , OS <sub>G</sub> , OS <sub>B</sub> , | Analog Inputs. These inputs (for Red,                                                      |  |  |  |  |  |  |  |

| R,G,B,                                                | Green, and Blue) should be tied to the sen-                                                |  |  |  |  |  |  |  |

|                                                       | sor's OS (Output Signal) through DC block-                                                 |  |  |  |  |  |  |  |

|                                                       | ing capacitors.                                                                            |  |  |  |  |  |  |  |

| RefBypass                                             | Internally generated reference voltage                                                     |  |  |  |  |  |  |  |

|                                                       | bypass pin. It should be bypassed to AGND                                                  |  |  |  |  |  |  |  |

|                                                       | through a .05uF monolithic capacitor.                                                      |  |  |  |  |  |  |  |

| V <sub>REF+,</sub> V <sub>REFMID,</sub>               | Voltage reference bypass pins. They should                                                 |  |  |  |  |  |  |  |

| V <sub>REF-</sub>                                     | each be bypassed to AGND through a .05uF                                                   |  |  |  |  |  |  |  |

|                                                       | monolithic capacitor.                                                                      |  |  |  |  |  |  |  |

|                                                       | Input & Timing Control                                                                     |  |  |  |  |  |  |  |

| MCLK                                                  | Master Clock. The ADC conversion rate will                                                 |  |  |  |  |  |  |  |

|                                                       | be a maximum of ¼ of MCLK. Nominally                                                       |  |  |  |  |  |  |  |

|                                                       | 24MHz.                                                                                     |  |  |  |  |  |  |  |

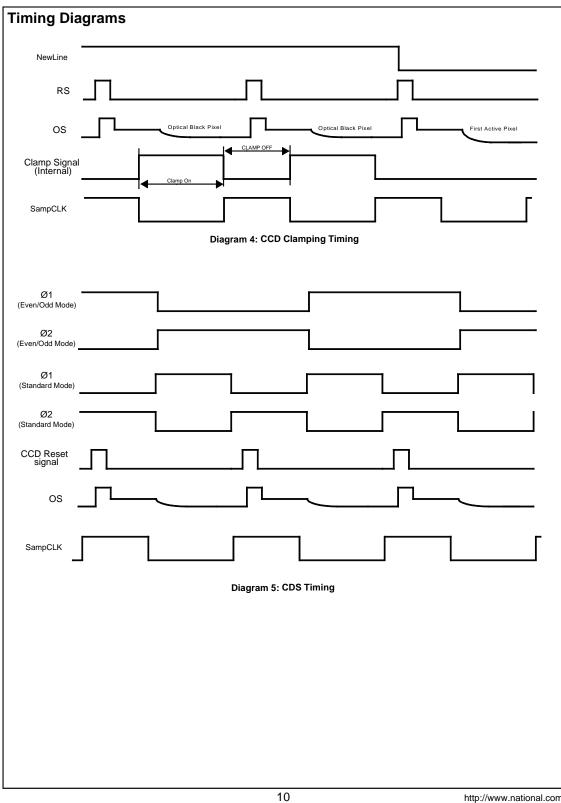

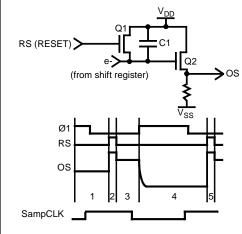

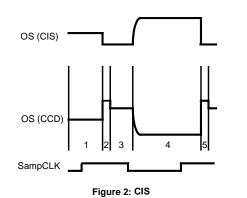

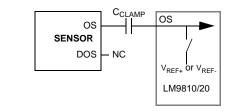

| SampCLK                                               | Sample Clock. SampCLK controls the con-                                                    |  |  |  |  |  |  |  |

|                                                       | version rate of the ADC (up to 1/4 of the                                                  |  |  |  |  |  |  |  |

|                                                       | MCLK rate) and sample timing. The signal                                                   |  |  |  |  |  |  |  |

|                                                       | level is sampled while SampCLK is low and                                                  |  |  |  |  |  |  |  |

|                                                       | held on the rising edge of SampCLK. When                                                   |  |  |  |  |  |  |  |

|                                                       | CDS is enabled, the falling edge of SampCLK                                                |  |  |  |  |  |  |  |

|                                                       | causes the CCD reference level to be held.                                                 |  |  |  |  |  |  |  |

|                                                       | If CDS is not enabled, $V_{REF+}$ or $V_{REF-}$ is held                                    |  |  |  |  |  |  |  |

|                                                       | on the falling edge of SampCLK, depending                                                  |  |  |  |  |  |  |  |

|                                                       | on the programmed signal polarity. SampCLK                                                 |  |  |  |  |  |  |  |

|                                                       | is also used with NewLine to clamp the exter<br>nal coupling capacitors.                   |  |  |  |  |  |  |  |

| NewLine                                               | New Line signal. Used to indicate the start                                                |  |  |  |  |  |  |  |

|                                                       | of active pixels on a new line, to allow                                                   |  |  |  |  |  |  |  |

|                                                       | clamping of the AC coupling caps, and to                                                   |  |  |  |  |  |  |  |

|                                                       | allow programming of the configuration reg-                                                |  |  |  |  |  |  |  |

|                                                       | ister. When NewLine is high and SampCLK is                                                 |  |  |  |  |  |  |  |

|                                                       | low, the OS inputs will be connected to                                                    |  |  |  |  |  |  |  |

|                                                       | either $V_{REF+}$ or $V_{REF-}$ . On the first rising edge                                 |  |  |  |  |  |  |  |

|                                                       | of MCLK after NewLine goes low, the internal                                               |  |  |  |  |  |  |  |

|                                                       | mux and the offset and gain settings will be                                               |  |  |  |  |  |  |  |

|                                                       | set to the appropriate values for the first                                                |  |  |  |  |  |  |  |

|                                                       | color of the next line set in the color mode                                               |  |  |  |  |  |  |  |

|                                                       | setting in the Sampler and Color Mode Reg                                                  |  |  |  |  |  |  |  |

|                                                       | ister. When NewLine is low, D[5-0] transmit                                                |  |  |  |  |  |  |  |

|                                                       | the pixel conversion data from the ADC.                                                    |  |  |  |  |  |  |  |

|                                                       | When NewLine is high, D[5-0] enter TRI-                                                    |  |  |  |  |  |  |  |

|                                                       | STATE and D2, D1 and D0 act as a serial                                                    |  |  |  |  |  |  |  |

|                                                       | interface for programming the configuration registers.                                     |  |  |  |  |  |  |  |

|                                                       | registers.                                                                                 |  |  |  |  |  |  |  |

|                                        | [                                                                                                                                                                       | Digital Po                                                                                                                                                                                                                                                                                                                                             | wer         |                   |  |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|--|--|--|--|

| VD                                     | This is the positive supply pin for the digita<br>supply. It should be connected to a voltage<br>source of +5V and bypassed to DGND with<br>0.1µF monolithic capacitor. |                                                                                                                                                                                                                                                                                                                                                        |             |                   |  |  |  |  |

| DGND                                   | This is ply.                                                                                                                                                            | the grour                                                                                                                                                                                                                                                                                                                                              | nd return f | or the digital su |  |  |  |  |

|                                        |                                                                                                                                                                         | Digital I/                                                                                                                                                                                                                                                                                                                                             | 0           |                   |  |  |  |  |

| D5-D0                                  | low, th<br>the AD<br>NewLin<br>STATE                                                                                                                                    | Data Input/Output pins. When NewLine is<br>low, the 10 or 12 bit conversion results of<br>the ADC are multiplexed to D5-D0. When<br>NewLine is high, the output drivers enter TF<br>STATE and D2, D1 & D0 act as a serial inte<br>face for writing to the configuration regis-                                                                         |             |                   |  |  |  |  |

| LM9810<br>Output Mode<br>(NewLine Low) | MCLK                                                                                                                                                                    | 0, MCLK1                                                                                                                                                                                                                                                                                                                                               | , MCLK2,    | MCLK3             |  |  |  |  |

| D5                                     | b9,                                                                                                                                                                     | b9,                                                                                                                                                                                                                                                                                                                                                    | b3,         | b3                |  |  |  |  |

| D4                                     | b8,                                                                                                                                                                     | b8,                                                                                                                                                                                                                                                                                                                                                    | b2,         | b2                |  |  |  |  |

| D3                                     | b7,                                                                                                                                                                     | b7,                                                                                                                                                                                                                                                                                                                                                    | b1,         | b1                |  |  |  |  |

| D2                                     | b6,                                                                                                                                                                     | b6,                                                                                                                                                                                                                                                                                                                                                    | b0,         | b0                |  |  |  |  |

| D1                                     | b5,                                                                                                                                                                     | b5,                                                                                                                                                                                                                                                                                                                                                    | 0,          | 0                 |  |  |  |  |

| D0                                     | b4,                                                                                                                                                                     | b4,                                                                                                                                                                                                                                                                                                                                                    | 0,          | 0                 |  |  |  |  |

| LM9820<br>Output Mode<br>(NewLine Low) | MCLK                                                                                                                                                                    | 0, MCLK1                                                                                                                                                                                                                                                                                                                                               | , MCLK2,    | MCLK3             |  |  |  |  |

| D5                                     | b11,                                                                                                                                                                    | b11,                                                                                                                                                                                                                                                                                                                                                   | b5,         | b5                |  |  |  |  |

| D4                                     | b10,                                                                                                                                                                    | b10,                                                                                                                                                                                                                                                                                                                                                   | b4,         | b4                |  |  |  |  |

| D3                                     | b9,                                                                                                                                                                     | b9,                                                                                                                                                                                                                                                                                                                                                    | b3,         | b3                |  |  |  |  |

| D2                                     | b8,                                                                                                                                                                     | b8,                                                                                                                                                                                                                                                                                                                                                    | b2,         | b2                |  |  |  |  |

| D1                                     | b7,                                                                                                                                                                     | b7,                                                                                                                                                                                                                                                                                                                                                    | b1,         | b1                |  |  |  |  |

| D0                                     | b6,                                                                                                                                                                     | b6,                                                                                                                                                                                                                                                                                                                                                    | b0,         | b0                |  |  |  |  |

| Input Mode<br>(NewLine High)           |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                        |             |                   |  |  |  |  |

| D5-D3                                  | Don't (                                                                                                                                                                 | Care                                                                                                                                                                                                                                                                                                                                                   |             |                   |  |  |  |  |

| D2 (SCLK)                              | Serial                                                                                                                                                                  | Data Cloc                                                                                                                                                                                                                                                                                                                                              | k.          |                   |  |  |  |  |

| D1 (Latch)                             | D1(Lat<br>When<br>shifted<br>the ad<br>avoid e<br>registe                                                                                                               | Latch and shift enable signal. When<br>D1(Latch) is low, data is shifted into D0(SDI)<br>When D1(Latch) goes high, the last nine bit:<br>shifted into D0(SDI) will be used to program<br>the addressed configuration register. To<br>avoid erroneous writes to the configuration<br>registers, D1(Latch) should be pulled low<br>when NewLine is high. |             |                   |  |  |  |  |