NOT RECOMMENDED FOR NEW DESIGNS

**Digital Filter**

August 1999

#### Features

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- 0MHz to 25.6MHz Sample Rate

- Four Filter Cells

- · 8-Bit Coefficients and Signal Data

- Low Power CMOS Operation

- I<sub>CCSB</sub> = 500μA Maximum

- I<sub>CCOP</sub> = 110μA Maximum at 20MHz

- · 26-Bit Accumulator Per Stage

- Filter Lengths Up To 1032 Taps

- Expandable Coefficient Size, Data Size and Filter Length

- · Decimation by 2, 3 or 4

## **Applications**

- 1-D and 2-D FIR Filters

- Radar/Sonar

- Adaptive Filters

- Echo Cancellation

- Complex Multiply-Add

- Sample Rate Converters

# Ordering Information

| PART NUMBER       | TEMPERA-<br>TURE RANGE | PACKAGE     |

|-------------------|------------------------|-------------|

| HSP43481GM-20/883 | -55°C to +125°C        | 68 Lead PGA |

| HSP43481GM-25/883 | -55°C to +125°C        | 68 Lead PGA |

## Description

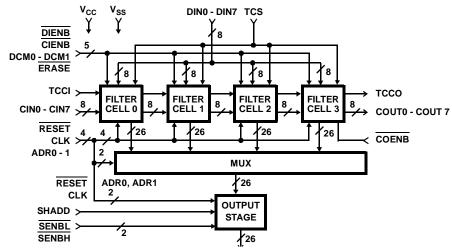

The HSP43481/883 is a video-speed Digital Filter (DF) designed to efficiently implement vector operations such as FIR digital filters. It is comprised of four filter cells cascaded internally and a shift-and- add output stage, all in a single integrated circuit. Each filter cell contains an 8 x 8 multiplier, three decimation registers and a 26-bit accumulator which can add the contents of any filter cell accumulator to the output stage accumulator shifted right by eight-bits. The HSP43481/883 has a maximum sample rate of 25.6MHz. The effective multiply-accumulate (MAC) rate is 102MHz.

The HSP43481/883 can be configured to process expanded coefficient and word sizes. Multiple devices can be cascaded for larger filter lengths without degrading the sample rate or a single device can process larger filter lengths at less than 25.6MHz with multiple passes. The architecture permits processing filter lengths of over 1000 taps with the guarantee of no overflows. In practice, most filter coefficients are less than 1.0, making even larger filter lengths possible. The HSP43481/883 provides for unsigned or two's complement arithmetic, independently selectable for coefficients and signal data.

Each DF filter cell contains three resampling or decimation registers which permit output sample rate reduction at rates of  $\frac{1}{2}$ ,  $\frac{1}{3}$  or  $\frac{1}{4}$  the input sample rate. These registers also provide the capability to perform 2-D operations such as N x N spatial correlations/convolutions for image processing applications.

## Block Diagram

#### HSP43481/883

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries. For information regarding Intersil Corporation and its products, see www.intersil.com Sales Office Headquarters

**NORTH AMERICA**

Intersil Corporation 7585 Irvine Center Drive Suite 100 Irvine, CA 92618 TEL: (949) 341-7000 FAX: (949) 341-7123 Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7946 EUROPE Intersil Europe Sarl Ave. C - F Ramuz 43 CH-1009 Pully Switzerland TEL: +41 21 7293637 FAX: +41 21 7293684 ASIA

Intersil Corporation

Unit 1804 18/F Guangdong Water Building

83 Austin Road

TST, Kowloon Hong Kong

TEL: +852 2723 6339

FAX: +852 2730 1433