# INTEGRATED CIRCUITS

# DATA SHEET

# **TSA5522**1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

Product specification Supersedes data of 1995 Mar 22 File under Integrated Circuits, IC02

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

# **TSA5522**

# **FEATURES**

- Complete 1.4 GHz single chip system

- Three PNP band switch buffers (20 mA)

- Four bus-controlled bidirectional ports (NPN open-collector outputs); only one port in 16-pin version

- 33 V tuning voltage output

- In-lock detector

- 5-step ADC

- Mixer-Oscillator (M/O) band switch output

- 15-bit programmable divider

- Programmable reference divider ratio (512, 640 or 1024)

- Programmable charge-pump current (50 or 250 μA)

- Varicap drive disable

- I2C-bus format

- address plus 4 data bytes transmission (write mode)

- address plus 1 status byte transmission (read mode)

- three independent addresses

- · Low power and low radiation.

# **APPLICATIONS**

- TV tuners and front-ends

- VCR tuners.

# **ORDERING INFORMATION**

| TYPE NUMBER |        | PACKAGE                                                           |          |  |  |  |  |  |

|-------------|--------|-------------------------------------------------------------------|----------|--|--|--|--|--|

| TIPE NOWBER | NAME   | DESCRIPTION                                                       | VERSION  |  |  |  |  |  |

| TSA5522M    | SSOP20 | plastic shrink small outline package; 20 leads; body width 4.4 mm | SOT266-1 |  |  |  |  |  |

| TSA5522T    | SO16   | plastic small outline package; 16 leads; body width 3.9 mm        | SOT109-1 |  |  |  |  |  |

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

### **QUICK REFERENCE DATA**

| SYMBOL              | PARAMETER                              | CONDITIONS                        | MIN.             | TYP. | MAX. | UNIT |

|---------------------|----------------------------------------|-----------------------------------|------------------|------|------|------|

| V <sub>CC1</sub>    | supply voltage (+5 V)                  |                                   | 4.5              | _    | 5.5  | V    |

| V <sub>CC2</sub>    | band switch supply voltage (+12 V)     |                                   | V <sub>CC1</sub> | 12   | 13.5 | V    |

| I <sub>CC1</sub>    | supply current                         |                                   | _                | 22   | 30   | mA   |

| I <sub>CC2</sub>    | band switch supply current             | note 1                            | _                | 27   | 32   | mA   |

| f <sub>RF</sub>     | RF input frequency                     |                                   | 64               | _    | 1400 | MHz  |

| V <sub>i(RF)</sub>  | RF input voltage                       | f <sub>i</sub> = 80 to 150 MHz    | - 25             | _    | 3    | dBm  |

|                     |                                        | f <sub>i</sub> = 150 to 1000 MHz  | - 28             | _    | 3    | dBm  |

|                     |                                        | f <sub>i</sub> = 1000 to 1400 MHz | - 26             | _    | 3    | dBm  |

| f <sub>xtal</sub>   | crystal oscillator input frequency     |                                   | _                | 4    | _    | MHz  |

| I <sub>o(PNP)</sub> | PNP band switch buffers output current |                                   | _                | 20   | 25   | mA   |

| I <sub>o(NPN)</sub> | NPN open-collector output current      |                                   | _                | 20   | 25   | mA   |

| T <sub>amb</sub>    | operating ambient temperature          |                                   | -20              | _    | +85  | °C   |

| T <sub>stg</sub>    | storage temperature (IC)               |                                   | -40              | _    | +150 | °C   |

### Note

1. One band switch buffer ON;  $I_0 = 20$  mA.

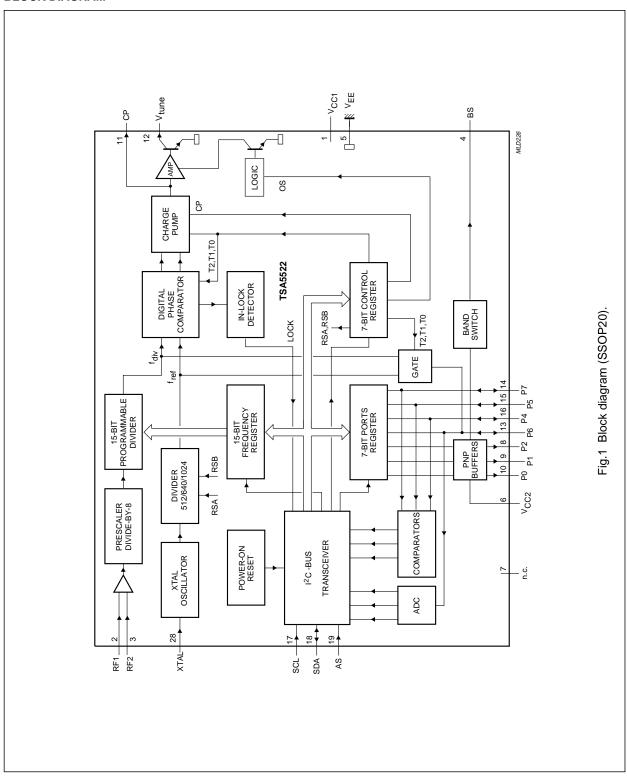

### **GENERAL DESCRIPTION** (see Fig.1)

The device is a single chip PLL frequency synthesizer designed for TV and VCR tuning systems. The circuit consists of a divide-by-eight prescaler with its own preamplifier, a 15-bit programmable divider, a crystal oscillator and its programmable reference divider and a phase/frequency detector combined with a charge-pump which drives the tuning amplifier, including 33 V output. Three high-current PNP band switch buffers are provided for band switching together with four open-collector NPN outputs (only one open-collector output on 16-pin devices). These ports can also be used as input ports [one Analog-to Digital Converter (ADC) and three general purpose I/O ports (not available on 16-pin devices)]. An output is provided to control a Philips mixer/oscillator IC in combination with the PNP buffers state.

Depending on the reference divider ratio (512, 640 or 1024), the phase comparator operates at 3.90625 kHz, 6.25 kHz or 7.8125 kHz with a 4 MHz crystal. The LOCK detector bit FL is set to logic 1 when the loop is locked and is read on the SDA line (status byte) during a read operation.

The ADC is available for digital AFC control. The ADC code is read during a read operation on the  $I^2C$ -bus. The ADC input is combined with the port P6. In the TEST mode, this port is also used as a TEST output for  $f_{ref}$  and  $\frac{1}{2}f_{div}$  (see Table 4).

# I<sup>2</sup>C-bus format

Five serial bytes (including address byte) are required to address the device, select the VCO frequency, program the ports, set the charge-pump current and the reference divider ratio. The device has three independent I<sup>2</sup>C-bus addresses selected by applying a specific voltage on AS input (see Table 3). The general address C2 is always valid.

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

# **BLOCK DIAGRAM**

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

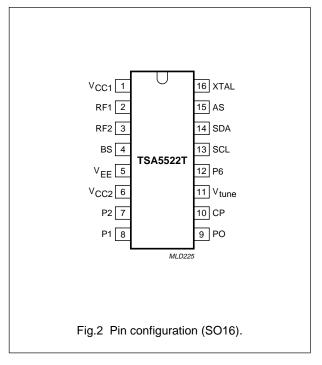

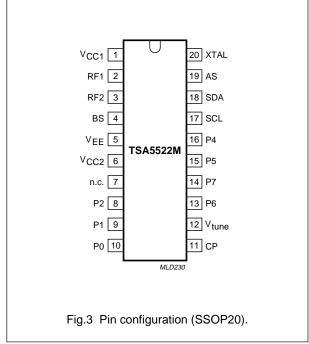

# **PINNING**

| SYMBOL            | SO16 | SSOP20 | DESCRIPTION                                  |

|-------------------|------|--------|----------------------------------------------|

| V <sub>CC1</sub>  | 1    | 1      | voltage supply (+5 V)                        |

| RF1               | 2    | 2      | RF signal input 1                            |

| RF2               | 3    | 3      | RF signal input 2                            |

| BS                | 4    | 4      | band switch output to mixer/oscillator drive |

| V <sub>EE</sub>   | 5    | 5      | ground                                       |

| V <sub>CC2</sub>  | 6    | 6      | voltage supply (+12 V)                       |

| n.c.              | _    | 7      | not connected                                |

| P2                | 7    | 8      | PNP band switch buffer output 2              |

| P1                | 8    | 9      | PNP band switch buffer output 1              |

| P0                | 9    | 10     | PNP band switch buffer output 0              |

| СР                | 10   | 11     | charge-pump output                           |

| V <sub>tune</sub> | 11   | 12     | tuning voltage output                        |

| P6                | 12   | 13     | NPN open-collector output/ADC input          |

| P7                | _    | 14     | NPN open-collector output/comparator input   |

| P5                | _    | 15     | NPN open-collector output/comparator input   |

| P4                | _    | 16     | NPN open-collector output/comparator input   |

| SCL               | 13   | 17     | serial clock input                           |

| SDA               | 14   | 18     | serial data input/output                     |

| AS                | 15   | 19     | address selection input                      |

| XTAL              | 16   | 20     | crystal oscillator input                     |

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

### **FUNCTIONAL DESCRIPTION**

The device is controlled via the two-wire I<sup>2</sup>C-bus. For programming, there is one module address (7 bits) and the R/W bit for selecting the READ or the WRITE mode.

### I<sup>2</sup>C-bus mode

WRITE MODE (R/W = 0); see Table 1

Data bytes can be sent to the device after the address transmission (first byte). Four data bytes are required to fully program the device. The bus transceiver has an auto-increment facility which permits the programming of the device within one single transmission (address + 4 data bytes).

The device can also be partially programmed providing that the first data byte following the address is divider byte 1 (DB1) or control byte (CB). The bits in the data bytes are defined in Table 1. The first bit of the first data

byte transmitted indicates whether frequency data (first bit = 0) or control and ports data (first bit = 1) will follow. Until an  $I^2C$ -bus STOP command is sent by the controller, additional data bytes can be entered without the need to re-address the device. The frequency register is loaded after the 8th clock pulse of the second divider byte (DB2), the control register is loaded after the 8th clock pulse of the ports register is loaded after the 8th clock pulse of the ports byte (PB).

### I<sup>2</sup>C-BUS ADDRESS SELECTION

The module address contains programmable address bits (MA1 and MA0) which offer the possibility of having several synthesizers (up to 3) in one system by applying a specific voltage on the AS input.

The relationship between MA1 and MA0 and the input voltage on the AS input is given in Table 3.

| Table 1 | 12C-hue | data | format |

|---------|---------|------|--------|

|         |         |      |        |

| BYTE                 | MSB               |     | DATA BYTE         |                   |     |     |     |    | COMMAND |

|----------------------|-------------------|-----|-------------------|-------------------|-----|-----|-----|----|---------|

| Address byte (ADB)   | 1                 | 1   | 0                 | 0                 | 0   | MA1 | MA0 | 0  | А       |

| Divider byte 1 (DB1) | 0                 | N14 | N13               | N12               | N11 | N10 | N9  | N8 | Α       |

| Divider byte 2 (DB2) | N7                | N6  | N5                | N4                | N3  | N2  | N1  | N0 | Α       |

| Control byte (CB)    | 1                 | CP  | T2                | T1                | T0  | RSA | RSB | os | A       |

| Ports byte (PB)      | P7 <sup>(1)</sup> | P6  | P5 <sup>(1)</sup> | P4 <sup>(1)</sup> | Х   | P2  | P1  | P0 | Α       |

### Note

1. Not available on 16-pin devices.

Table 2

Description of Table 1

| SYMBOL    | DESCRIPTION                                                                                                                            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| MA1, MA0  | programmable address bits (see Table 3)                                                                                                |

| N14 to N0 | programmable divider bits N = N14 $\times$ 2 <sup>14</sup> + N13 $\times$ 2 <sup>13</sup> + + N1 $\times$ 2 + N0                       |

| СР        | charge-pump current; $CP = 0 = 50 \mu A$ ; $CP = 1 = 250 \mu A$                                                                        |

| T2 to T0  | test bits (see Table 4). For normal operation T2 = 0; T1 = 0; T0 = 1                                                                   |

| RSA, RSB  | reference divider ratio select bits (see Table 5)                                                                                      |

| OS        | tuning amplifier control bit; for normal operation OS = 0 and tuning voltage is ON; when OS = 1 tuning voltage is OFF (high impedance) |

| P2 to P0  | PNP band switch buffers control bits                                                                                                   |

| P7 to P4  | NPN open collector control bits when $P_n = 0$ output n is OFF; when $P_n = 1$ output n is ON                                          |

| Χ         | don't care                                                                                                                             |

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

Table 3 Address selection

| VOLTAGE APPLIED ON AS INPUT                | MA1 | MA2 |

|--------------------------------------------|-----|-----|

| 0 to 0.1V <sub>CC1</sub>                   | 0   | 0   |

| Always valid                               | 0   | 1   |

| 0.4V <sub>CC1</sub> to 0.6V <sub>CC1</sub> | 1   | 0   |

| 0.9V <sub>CC1</sub> to V <sub>CC1</sub>    | 1   | 1   |

Table 4 Test bits

| T2 | T1 | T0 | DEVICE OPERATION                              |

|----|----|----|-----------------------------------------------|

| 0  | 0  | 1  | normal mode                                   |

| 0  | 1  | Х  | charge-pump is OFF                            |

| 1  | 1  | 0  | charge-pump is sinking current                |

| 1  | 1  | 1  | charge-pump is sourcing current               |

| 1  | 0  | 0  | f <sub>ref</sub> is available at LOCK output  |

| 1  | 0  | 1  | ½f <sub>div</sub> is available at LOCK output |

Table 5 Ratio select bits

| RSA | RSB | REFERENCE DIVIDER |

|-----|-----|-------------------|

| Х   | 0   | 640               |

| 0   | 1   | 1024              |

| 1   | 1   | 512               |

Table 6 Band switch output levels

| P2 | P1 | P0 | VOLTAGE<br>ON BS<br>OUTPUT | PHILIPS M/O<br>BAND |

|----|----|----|----------------------------|---------------------|

| 0  | 1  | 0  | 0.25 V                     | band A              |

| 1  | 0  | 0  | 0.4V <sub>CC1</sub>        | band B              |

| 0  | 0  | 1  | 0.8V <sub>CC1</sub>        | band C              |

READ MODE; R/W = 1 (see Table 7)

Data can be read from the device by setting the R/W bit to logic 1. After the slave address has been recognized, the device generates an acknowledge pulse and the first data byte (status byte) is transferred on the SDA line (MSB first). Data is valid on the SDA line during a HIGH level of the SCL clock signal. A second data byte can be read from the device if the microcontroller generates an acknowledge on the SDA line (master acknowledge). End of transmission will occur if no master acknowledge occurs. The device will then release the data line to allow the microcontroller to generate a STOP condition. When ports P4 to P7 are used as inputs, the corresponding bits must be logic 0 (high impedance state). The POR flag is set to logic 1 at power-on. The flag is reset when an end-of-data is detected by the device (end of a read sequence). Control of the loop is made possible with the in-lock flag (FL) which indicates when the loop is locked (FL = 1).

The bits I2, to I0 represent the status of the I/O ports P7, P5 and P4 respectively. A logic 0 indicates a LOW level and a logic 1 indicates a HIGH level (see "Characteristics").

A built-in ADC is available at pin P6. This converter can be used to apply AFC information to the microcontroller from the IF section of the television. The relationship between the bits A2 to A0 is given in Table 8.

Table 7 READ data format

| BYTE               | MSB                | DATA BYTE         |                   |                   |                   |                   |                   | LSB               | COMMAND          |

|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

| Address byte (ADB) | 1                  | 1                 | 0                 | 0                 | 0                 | MA1               | MA0               | 1                 | A <sup>(1)</sup> |

| Status byte (SB)   | POR <sup>(2)</sup> | FL <sup>(3)</sup> | I2 <sup>(4)</sup> | I1 <sup>(4)</sup> | IO <sup>(4)</sup> | A2 <sup>(5)</sup> | A1 <sup>(5)</sup> | A0 <sup>(5)</sup> | -                |

### **Notes**

- A = acknowledge.

- 2. POR = power-on-reset (POR = 1 at power-on).

- 3. FL = in-lock flag (FL = 1 when loop is locked).

- 4. I2 to I0 = digital levels for I/O ports P7, P5 and P4 respectively.

- 5. A2 to A0 = digital outputs of the 5-level ADC.

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

Table 8 ADC levels

| VOLTAGE APPLIED ON PORT P6 <sup>(1)</sup>   | A2 | <b>A</b> 1 | Α0 |

|---------------------------------------------|----|------------|----|

| 0.6V <sub>CC1</sub> to 13.5V                | 1  | 0          | 0  |

| 0.45V <sub>CC1</sub> to 0.6V <sub>CC1</sub> | 0  | 1          | 1  |

| 0.3V <sub>CC1</sub> to 0.45V <sub>CC1</sub> | 0  | 1          | 0  |

| 0.15V <sub>CC1</sub> to 0.3V <sub>CC1</sub> | 0  | 0          | 1  |

| 0 to 0.15V <sub>CC1</sub>                   | 0  | 0          | 0  |

### Note

1. Accuracy is 0.02V<sub>CC1</sub>.

# **LIMITING VALUES**

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL                | PARAMETER                                                | MIN.  | MAX              | UNIT |

|-----------------------|----------------------------------------------------------|-------|------------------|------|

| V <sub>CC1</sub>      | supply voltage +5 V                                      | -0.3  | 6.0              | V    |

| V <sub>CC2</sub>      | supply voltage + 12 V                                    | -0.3  | 16               | V    |

| V <sub>i(RF)</sub>    | prescaler input voltage                                  | -0.3  | V <sub>CC1</sub> | V    |

| V <sub>o(BS)</sub>    | band switch output voltage                               | -0.3  | V <sub>CC1</sub> | V    |

| V <sub>o(PNP)</sub>   | PNP band switch buffer output voltage                    | - 0.3 | V <sub>CC2</sub> | V    |

| I <sub>o(PNP)</sub>   | PNP band switch buffers output current                   | -1    | 25               | mA   |

| V <sub>NPN</sub>      | NPN open-collector output voltage                        | -0.3  | 16               | V    |

| I <sub>NPN</sub>      | NPN open-collector output current                        | -1    | 25               | mA   |

| V <sub>o(CP)</sub>    | charge-pump output voltage                               | -0.3  | V <sub>CC1</sub> | V    |

| V <sub>o(tune)</sub>  | output tuning voltage                                    | -0.3  | 35               | V    |

| V <sub>i(SCL)</sub>   | serial clock input voltage                               | -0.3  | 6.0              | V    |

| V <sub>i/o(SDA)</sub> | serial data input/output voltage                         | -0.3  | 6.0              | V    |

| I <sub>o(SDA)</sub>   | serial data output current                               | -1    | 5                | mA   |

| V <sub>i(AS)</sub>    | address selection input voltage                          | -0.3  | V <sub>CC1</sub> | V    |

| V <sub>i(xtal)</sub>  | crystal oscillator input voltage                         | -0.3  | V <sub>CC1</sub> | V    |

| T <sub>stg</sub>      | storage temperature range (IC)                           | -40   | +150             | °C   |

| T <sub>j</sub>        | maximum junction temperature                             | -     | +150             | °C   |

| t <sub>sc</sub>       | short circuit time; every pin to V <sub>CC1</sub> or GND | -     | 10               | s    |

# **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling bipolar devices. Every pin withstands the ESD test in accordance with MIL-STD-883C category B (2000 V). Every pin withstands the ESD test in accordance with Philips Semiconductors Machine Model 0  $\Omega$ , 200 pF (200 V).

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

# THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                               | MAX | UNIT |

|---------------------|---------------------------------------------------------|-----|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air |     |      |

|                     | SO16                                                    | 110 | K/W  |

|                     | SSOP20                                                  | 120 | K/W  |

# **CHARACTERISTICS**

$V_{CC1} = 4.5$  to 5.5 V;  $V_{CC2} = V_{CC1}$  to 13.2 V;  $T_{amb} = -20$  to 85 °C; unless otherwise specified; see note 1

| SYMBOL              | PARAMETER                                           | CONDITIONS                                                                                           | MIN.             | TYP. | MAX   | UNIT |

|---------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|------|-------|------|

| V <sub>CC1</sub>    | supply voltage (+5 V)                               |                                                                                                      | 4.5              | _    | 5.5   | V    |

| V <sub>CC2</sub>    | supply voltage (+12 V)                              |                                                                                                      | V <sub>CC1</sub> | _    | 13.5  | V    |

| I <sub>CC1</sub>    | supply current                                      |                                                                                                      | _                | 22   | 30    | mA   |

| I <sub>CC2</sub>    | supply current                                      | One band switch buffer is ON;<br>I <sub>source</sub> = 20 mA                                         | _                | 27   | 32    | mA   |

| f <sub>RF</sub>     | RF input frequency                                  |                                                                                                      | 64               | _    | 1400  | MHz  |

| DR                  | divider ratio                                       | 15-bit frequency word                                                                                | 256              | _    | 32767 | MHz  |

| Crystal os          | cillator                                            |                                                                                                      |                  | ·    | •     |      |

| f <sub>xtal</sub>   | crystal oscillator input frequency                  | $R_{xtal} = 25 \text{ to } 300 \Omega$                                                               | 3.2              | 4    | 4.48  | MHz  |

| Z <sub>xtal</sub>   | crystal oscillator input impedance (absolute value) | f <sub>i</sub> = 4 MHz                                                                               | 600              | 1200 | -     | Ω    |

| Prescaler           |                                                     |                                                                                                      | •                |      |       |      |

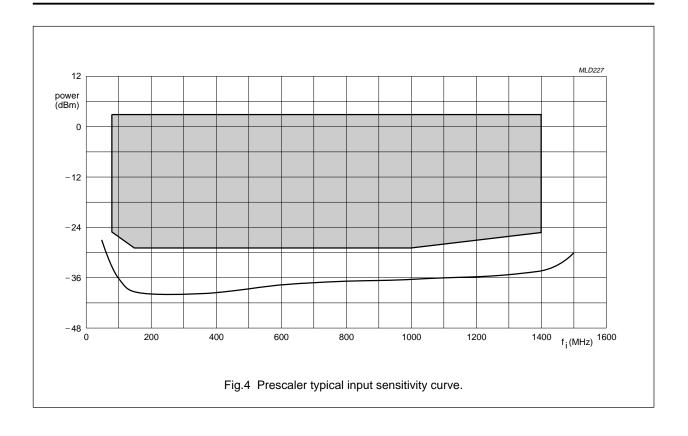

| $V_{i(RF)}$         | RF input level                                      | $V_{CC1} = 4.5 \text{ to } 5.5 \text{ V}; \text{ see Fig.4};$ $f_i = 80 \text{ to } 150 \text{ MHz}$ | -25              | _    | 3     | dB   |

|                     |                                                     | V <sub>CC1</sub> = 4.5 to 5.5 V; see Fig.4;<br>f <sub>i</sub> = 150 to 1000 MHz                      | -28              | -    | 3     | dB   |

|                     |                                                     | $V_{CC1}$ = 4.5 to 5.5 V; see Fig.4; $f_i$ = 1000 to 1400 MHz                                        | -26              | _    | 3     | dB   |

| PNP band            | switch buffers outputs                              |                                                                                                      |                  | ·    | •     | •    |

| I <sub>LO</sub>     | output leakage current                              | $V_{CC2} = 13.5 \text{ V}; V_0 = 0 \text{ V}$                                                        | -10              | _    | _     | μΑ   |

| V <sub>o(sat)</sub> | output saturation voltage                           | I <sub>source</sub> = 20 mA; note 1                                                                  | -                | 0.2  | 0.5   | V    |

| NPN open            | -collector outputs P4, P5, P                        | 6 and P7; see note 2                                                                                 |                  | •    |       | •    |

| I <sub>LO</sub>     | output leakage current                              | V <sub>CC1</sub> = 5.5 V; V <sub>o</sub> = 13.5 V                                                    | _                | _    | 10    | μΑ   |

| V <sub>o(sat)</sub> | output saturation voltage                           | I <sub>sink</sub> = 20 mA; note 3                                                                    | _                | 0.2  | 0.5   | V    |

| C <sub>OL</sub>     | allowed capacitive loading on output pins           | V <sub>OL</sub> = 13.5 V                                                                             |                  |      | 10    | nF   |

| Input port          | s P7, P5 and P4; see note 2                         |                                                                                                      |                  |      |       |      |

| V <sub>IL</sub>     | LOW level input voltage                             |                                                                                                      | _                | _    | 1.5   | V    |

| V <sub>IH</sub>     | HIGH level input voltage                            |                                                                                                      | 3                | _    | _     | V    |

| AS input (          | Address Selection)                                  |                                                                                                      |                  |      |       |      |

| I <sub>IH(AS)</sub> | HIGH level input current                            | V <sub>AS</sub> = V <sub>CC1</sub>                                                                   | _                | _    | 50    | μΑ   |

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

| SYMBOL                   | PARAMETER                                                          | CONDITIONS                                                                                  | MIN.                 | TYP.                | MAX                  | UNIT |

|--------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|---------------------|----------------------|------|

| I <sub>IL(AS)</sub>      | LOW level input current                                            | V <sub>AS</sub> = 0 V                                                                       | -50                  | _                   | _                    | μΑ   |

| SCL and S                | SDA inputs                                                         |                                                                                             |                      |                     |                      | •    |

| V <sub>IL</sub>          | LOW level input voltage                                            |                                                                                             | _                    | _                   | 1.5                  | V    |

| V <sub>IH</sub>          | HIGH level input voltage                                           |                                                                                             | 3.0                  | _                   | 5.5                  | V    |

| I <sub>IH</sub>          | HIGH level input current                                           | V <sub>IH</sub> = 5.5 V; V <sub>CC1</sub> = 0 V                                             | _                    | _                   | 10                   | μΑ   |

|                          |                                                                    | V <sub>IH</sub> = 5.5 V; V <sub>CC1</sub> = 5.5 V                                           | _                    | _                   | 10                   | μΑ   |

| I <sub>IL</sub>          | LOW level input current                                            | V <sub>IL</sub> = 0 V; V <sub>CC1</sub> = 5.5 V                                             | -10                  | _                   | _                    | μΑ   |

| f <sub>clk</sub>         | input clock frequency                                              |                                                                                             | _                    | 100                 | 400                  | kHz  |

| SDA outpo                | ut (I <sup>2</sup> C bus mode)                                     |                                                                                             |                      |                     |                      |      |

| I <sub>ILO</sub>         | output leakage current                                             | V <sub>O</sub> = 5.5 V                                                                      | _                    | _                   | 10                   | μΑ   |

| Vo                       | output voltage                                                     | I <sub>sink</sub> = 3 mA                                                                    | _                    | _                   | 0.4                  | μΑ   |

| BS output                | (M/O band selection)                                               |                                                                                             | 1                    | -                   |                      |      |

| V <sub>o(BS)</sub>       | output voltage                                                     | band A; I <sub>source</sub> = 20 μA                                                         | _                    | 0.25                | 0.5                  | V    |

| , ,                      |                                                                    | band B; I <sub>source</sub> = 20 μA                                                         | 0.36V <sub>CC1</sub> | 0.4V <sub>CC1</sub> | 0.43V <sub>CC1</sub> | V    |

|                          |                                                                    | band C; I <sub>source</sub> = 20 μA                                                         | 0.7V <sub>CC1</sub>  | 0.8V <sub>CC1</sub> | 0.9V <sub>CC1</sub>  | V    |

|                          |                                                                    | band C; I <sub>source</sub> = 50 μA                                                         | 3.1                  | _                   | _                    | V    |

| Charge-pu                | ımp output CP                                                      |                                                                                             |                      |                     | •                    |      |

| I <sub>ICPH</sub>        | HIGH charge pump current (absolute value)                          | CP = 1                                                                                      | _                    | 250                 | _                    | μΑ   |

| I <sub>ICPL</sub>        | LOW charge pump current (absolute value)                           | CP = 0                                                                                      | _                    | 50                  | _                    | μΑ   |

| V <sub>o(CP)</sub>       | output voltage                                                     | in-lock; T <sub>amb</sub> = +25 °C                                                          | _                    | 1.95                | _                    | V    |

| I <sub>LI(off)</sub>     | off-state leakage current                                          | T2 = 0; T1 = 1                                                                              | -5                   | 1                   | 15                   | nA   |

| Tuning vo                | Itage output V <sub>tune</sub>                                     |                                                                                             |                      |                     | •                    |      |

| I <sub>LO(off)</sub>     | leakage current when switched-off                                  | OS = 1; V <sub>tune</sub> = 33 V                                                            | _                    | _                   | 10                   | μΑ   |

| Vo                       | output voltage when the loop is closed                             | OS = 0; T2 = 0; T1 = 0; T0 = 1;<br>$R_L = 27 \text{ k } \Omega$ ; $V_{tune} = 33 \text{ V}$ | 0.4                  | _                   | 32.6                 | V    |

| V <sub>ripple(p-p)</sub> | acceptable ripple voltage on V <sub>CC1</sub> (peak-to-peak value) | f <sub>ripple</sub> = 300 Hz to 300 kHz                                                     | -                    | -                   | 30                   | mV   |

# Notes

- 1. A single PNP band switch buffer is ON.

- 2. P4, P5 and P7 I/O ports are not available in 16-pin package. In 20-pin package, when a port is active, the collector voltage must not exceed 6 V.

- 3. A single NPN open-collector output is ON.

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

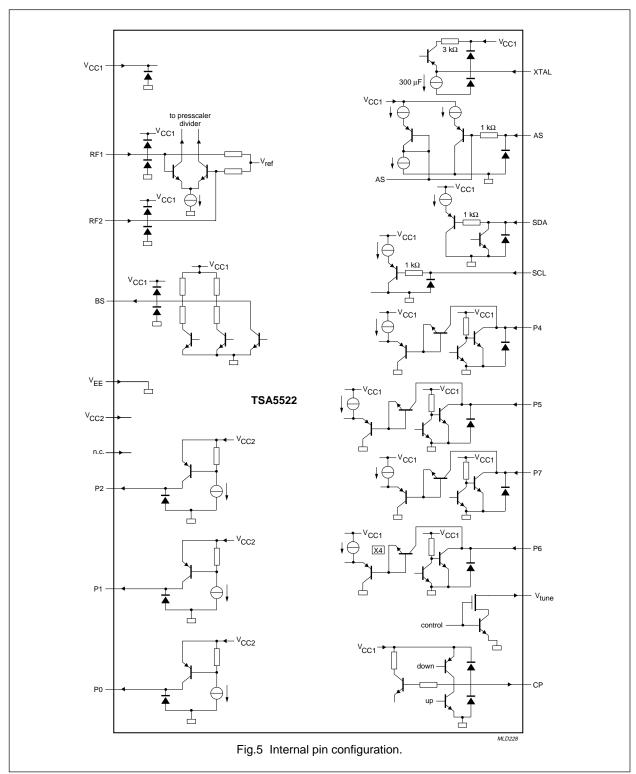

# **INTERNAL PIN CONFIGURATION**

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

# **APPLICATION INFORMATION**

# **Tuning amplifier**

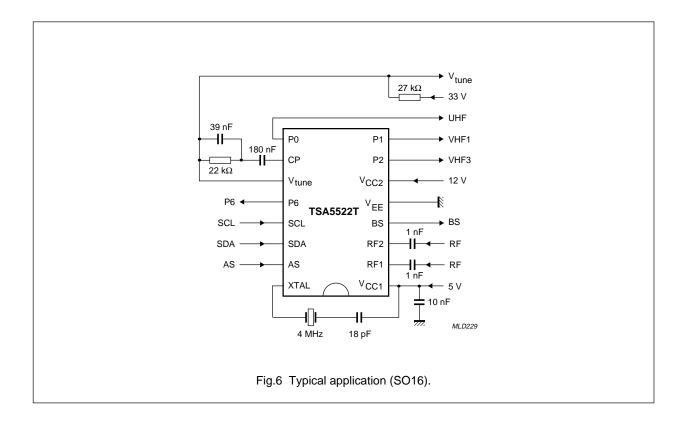

The tuning amplifier is capable of driving the varicap voltage without an external transistor. The tuning voltage output must be connected to an external load of  $27~\text{k}\Omega$  which is connected to the tuning voltage supply rail. Figure 6 shows a possible loop filter. The component values depend on the oscillator characteristics and the selected reference frequency.

# Crystal oscillator

The crystal oscillator uses a 4 MHz crystal connected in series with an 18 pF capacitor thereby operating in the series resonance mode. Connecting the oscillator to the supply voltage is preferred, but it can, however, also be connected to ground.

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

# Flock flag (FL) definition

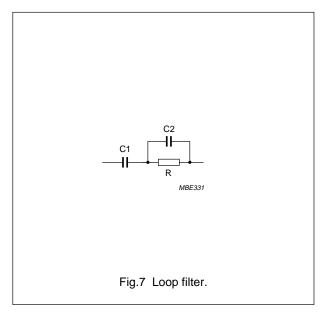

When the LOCK output is LOW the maximum frequency deviation ( $\Delta f$ ) from stable frequency can be expressed as

$$follows: \Delta f \ = \ \pm \frac{K_{VCO}}{K_O} \times I_{CP} \times \frac{(C1+C2)}{(C1\times C2)}$$

where:

$K_{vco}$  = oscillator slope Hz/V

$I_{CP}$  = charge-pump current (A)

$K_0 = 4 \times 10E6$

C1, C2 = loop filter capacitors.

In the application:

K<sub>VCO</sub> = 16 MHz/V (UHF band)

$I_{CP} = 250 \, \mu A$

C1 = 180 nF, C2 = 39 nF

$\Delta f = \pm 31.2$  kHz.

Table 9 LOCK output / FL flag setting

| DESCRIPTION                                                                  | CONDITION        | MIN. | MAX. | UNIT |

|------------------------------------------------------------------------------|------------------|------|------|------|

| Time span between actual phase lock and LOCK bit is LOW                      | RSA = 1; RSB = 1 | 1024 | 1152 | μs   |

| (or FL flag = 1)                                                             | RSA = 1; RSB = 1 | 2048 | 2304 | μs   |

|                                                                              | RSB = 0          | 1280 | 1440 | μs   |

| Time span between the loop losing lock and LOCK bit is HIGH or (FL flag = 0) |                  | 0    | 300  | μs   |

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

# **PACKAGE OUTLINES**

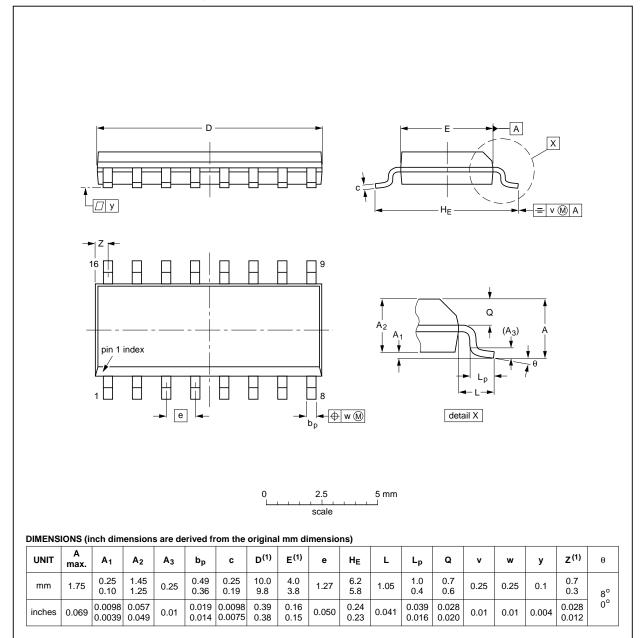

SO16: plastic small outline package; 16 leads; body width 3.9 mm

SOT109-1

# Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  | OUTLINE REFERENCES |          |      |  |            | ISSUE DATE                      |

|----------|--------------------|----------|------|--|------------|---------------------------------|

| VERSION  | IEC                | JEDEC    | EIAJ |  | PROJECTION | ISSUE DATE                      |

| SOT109-1 | 076E07S            | MS-012AC |      |  |            | <del>91-08-13</del><br>95-01-23 |

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

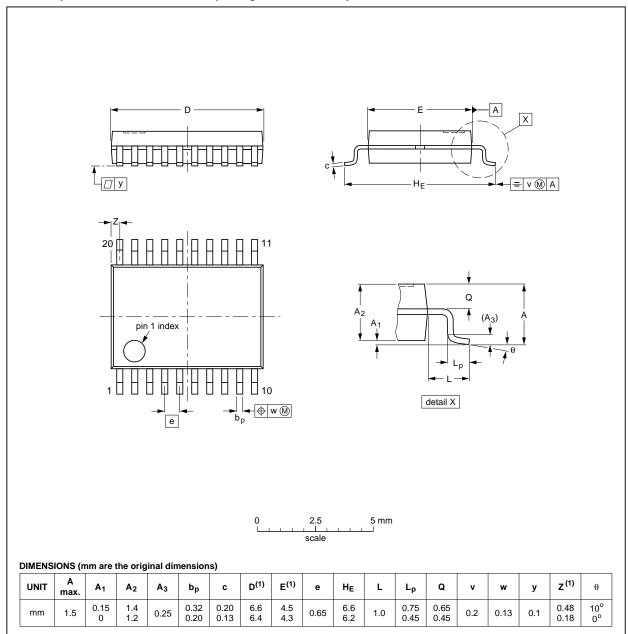

# SSOP20: plastic shrink small outline package; 20 leads; body width 4.4 mm

SOT266-1

### Note

1. Plastic or metal protrusions of 0.20 mm maximum per side are not included.

| OUTLINE  |     | REFERENCES |      |  |  | EUROPEAN   | ISSUE DATE                      |

|----------|-----|------------|------|--|--|------------|---------------------------------|

| VERSION  | IEC | JEDEC      | EIAJ |  |  | PROJECTION |                                 |

| SOT266-1 |     |            |      |  |  |            | <del>90-04-05</del><br>95-02-25 |

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

### **SOLDERING**

### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

### Reflow soldering

Reflow soldering techniques are suitable for all SO and SSOP packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250  $^{\circ}$ C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45  $^{\circ}$ C.

### Wave soldering

SO

Wave soldering techniques can be used for all SO packages if the following conditions are observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow.

- The package footprint must incorporate solder thieves at the downstream end.

### SSOP

Wave soldering is **not** recommended for SSOP packages. This is because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices.

If wave soldering cannot be avoided, the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow and must incorporate solder thieves at the downstream end.

Even with these conditions, only consider wave soldering SSOP packages that have a body width of 4.4 mm, that is SSOP16 (SOT369-1) or SSOP20 (SOT266-1).

METHOD (SO AND SSOP)

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

### Repairing soldered joints

Fix the component by first soldering two diagonally-opposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

# 1.4 GHz I<sup>2</sup>C-bus controlled synthesizer

TSA5522

### **DEFINITIONS**

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

|                           |                                                                                       |

### Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

# LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

### PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips  $I^2C$  components conveys a license under the Philips'  $I^2C$  patent to use the components in the  $I^2C$  system provided the system conforms to the  $I^2C$  specification defined by Philips. This specification can be ordered using the code 9398 393 40011.

# 1.4 GHz $I^2$ C-bus controlled synthesizer

TSA5522

**NOTES**

# Philips Semiconductors – a worldwide company

Argentina: IEROD, Av. Juramento 1992 - 14.b, (1428) BUENOS AIRES, Tel. (541)786 7633, Fax. (541)786 9367

**Australia:** 34 Waterloo Road, NORTH RYDE, NSW 2113, Tel. (02)805 4455, Fax. (02)805 4466

Austria: Triester Str. 64, A-1101 WIEN, P.O. Box 213, Tel. (01)60 101-1236, Fax. (01)60 101-1211

**Belgium:** Postbus 90050, 5600 PB EINDHOVEN, The Netherlands, Tel. (31)40-2783749, Fax. (31)40-2788399

**Brazil:** Rua do Rocio 220 - 5<sup>th</sup> floor, Suite 51, CEP: 04552-903-SÃO PAULO-SP, Brazil, P.O. Box 7383 (01064-970),

Tel. (011)821-2333, Fax. (011)829-1849

Canada: PHILIPS SEMICONDUCTORS/COMPONENTS: Tel. (800) 234-7381, Fax. (708) 296-8556

**Chile:** Av. Santa Maria 0760, SANTIAGO, Tel. (02)773 816, Fax. (02)777 6730

China/Hong Kong: 501 Hong Kong Industrial Technology Centre, 72 Tat Chee Avenue, Kowloon Tong, HONG KONG, Tel. (852)2319 7888, Fax. (852)2319 7700

Colombia: IPRELENSO LTDA, Carrera 21 No. 56-17, 77621 BOGOTA, Tel. (571)249 7624/(571)217 4609, Fax. (571)217 4549

Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S, Tel. (45)32 88 26 36, Fax. (45)31 57 19 49

**Finland:** Sinikalliontie 3, FIN-02630 ESPOO, Tel. (358)0-615 800, Fax. (358)0-61580 920

France: 4 Rue du Port-aux-Vins, BP317, 92156 SURESNES Cedex.

Tel. (01)4099 6161, Fax. (01)4099 6427 **Germany:** P.O. Box 10 51 40, 20035 HAMBURG,

Tel. (040)23 53 60, Fax. (040)23 53 63 00 **Greece:** No. 15, 25th March Street, GR 17778 TAVROS,

Greece: No. 15, 25th March Street, GR 17778 I AVROS Tel. (01)4894 339/4894 911, Fax. (01)4814 240

India: Philips INDIA Ltd, Shivsagar Estate, A Block, Dr. Annie Besant Rd. Worli, Bombay 400 018 Tel. (022)4938 541, Fax. (022)4938 722

Indonesia: Philips House, Jalan H.R. Rasuna Said Kav. 3-4, P.O. Box 4252, JAKARTA 12950, Tel. (021)5201 122, Fax. (021)5205 189

Irel. (021)5201 122, Fax. (021)5205 189 Ireland: Newstead, Clonskeagh, DUBLIN 14, Tel. (01)7640 000, Fax. (01)7640 200

Italy: PHILIPS SEMICONDUCTORS S.r.I., Piazza IV Novembre 3, 20124 MILANO, Tel. (0039)2 6752 2531, Fax. (0039)2 6752 2557

**Japan:** Philips Bldg 13-37, Kohnan2-chome, Minato-ku, TOKYO 108, Tel. (03)3740 5130, Fax. (03)3740 5077

Korea: Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL, Tel. (02)709-1412, Fax. (02)709-1415

Malaysia: No. 76 Jalan Universiti, 46200 PETALING JAYA, SELANGOR, Tel. (03)750 5214, Fax. (03)757 4880

**Mexico:** 5900 Gateway East, Suite 200, EL PASO, TX 79905, Tel. 9-5(800)234-7381, Fax. (708)296-8556

Netherlands: Postbus 90050, 5600 PB EINDHOVEN, Bldg. VB, Tel. (040)2783749, Fax. (040)2788399

New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND, Tel. (09)849-4160, Fax. (09)849-7811

Norway: Box 1, Manglerud 0612, OSLO, Tel. (022)74 8000, Fax. (022)74 8341

Pakistan: Philips Electrical Industries of Pakistan Ltd., Exchange Bldg. ST-2/A, Block 9, KDA Scheme 5, Clifton, KARACHI 75600, Tel. (021)587 4641-49, Fax. (021)577035/5874546 Philippines: PHILIPS SEMICONDUCTORS PHILIPPINES Inc., 106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI, Metro MANILA, Tel. (63) 2 816 6380, Fax. (63) 2 817 3474

Portugal: PHILIPS PORTUGUESA, S.A.,

Rua dr. António Loureiro Borges 5, Árquiparque - Miraflores, Apartado 300, 2795 LINDA-A-VELHA, Tel. (01)4163160/4163333, Fax. (01)4163174/4163366

Singapore: Lorong 1, Toa Payoh, SINGAPORE 1231,

Tel. (65)350 2000, Fax. (65)251 6500 **South Africa:** S.A. PHILIPS Pty Ltd.,

195-215 Main Road Martindale, 2092 JOHANNESBURG, P.O. Box 7430, Johannesburg 2000, Tel. (011)470-5911, Fax. (011)470-5494

Spain: Balmes 22, 08007 BARCELONA, Tel. (03)301 6312, Fax. (03)301 42 43

Sweden: Kottbygatan 7, Akalla. S-164 85 STOCKHOLM, Tel. (0)8-632 2000, Fax. (0)8-632 2745

**Switzerland:** Allmendstrasse 140, CH-8027 ZÜRICH, Tel. (01)488 2211, Fax. (01)481 77 30

Taiwan: PHILIPS TAIWAN Ltd., 23-30F, 66, Chung Hsiao West Road, Sec. 1. Taipeh, Taiwan ROC, P.O. Box 22978, TAIPEI 100, Tel. (886) 2 382 4443, Fax. (886) 2 382 4444

Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd., 209/2 Sanpavuth-Bangna Road Prakanong, Bangkok 10260, THAILAND,

Tel. (66) 2 745-4090, Fax. (66) 2 398-0793

**Turkey:** Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL, Tel. (0212)279 27 70, Fax. (0212)282 67 07

**Ukraine:** Philips UKRAINE, 2A Akademika Koroleva str., Office 165, 252148 KIEV, Tel. 380-44-4760297, Fax. 380-44-4766991

United Kingdom: Philips Semiconductors LTD., 276 Bath Road, Hayes, MIDDLESEX UB3 5BX, Tel. (0181)730-5000, Fax. (0181)754-8421

United States: 811 East Arques Avenue, SUNNYVALE, CA 94088-3409, Tel. (800)234-7381, Fax. (708)296-8556

**Uruguay:** Coronel Mora 433, MONTEVIDEO, Tel. (02)70-4044, Fax. (02)92 0601

Internet: http://www.semiconductors.philips.com/ps/

For all other countries apply to: Philips Semiconductors, International Marketing and Sales, Building BE-p, P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Telex 35000 phtcnl, Fax. +31-40-2724825

SCDS47 © Philips Electronics N.V. 1996

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

Let's make things better.