on the same I<sup>2</sup>C bus.

#

# **Quad-Channel, I<sup>2</sup>C-Margining IDACs with Three Channels of Power-Supply Tracking**

# **General Description**

The DS4426 contains four I<sup>2</sup>C-adjustable current DACs

capable of sinking or sourcing current. External resis-

tors set the full-scale range of each output. Each DAC

output has 127 sink and 127 source steps that are pro-

grammed by the I<sup>2</sup>C interface. Power-supply tracking functionality is provided for three channels using dedi-

cated control inputs. Once power-supply tracking is

accomplished, the current outputs default to zero. Two

address pins allow up to four DS4426 devices to exist

Power-Supply Adjustment

Power-Supply Margining

Power-Supply Tracking

Adjustable Current Sink or Source

**Features**

- Four Current DACs

50µA to 200µA Adjustable Full-Scale Range

127 Settings Each for Sink and Source

- Power-Supply Tracking

Power-Supply Sequencing

Ramp-Up and Ramp-Down Tracking Control

Ratiometric Tracking Support

- +2.7V to +5.5V Operation

- ♦ I<sup>2</sup>C-Compatible Serial Interface

- Two Address Input Pins Allow Up to Four Devices on Same I<sup>2</sup>C Bus

- Lead-Free, 28-Pin TQFN Package (4mm x 4mm) with Exposed Pad

- ♦ Industrial Temperature Range: -40°C to +85°C

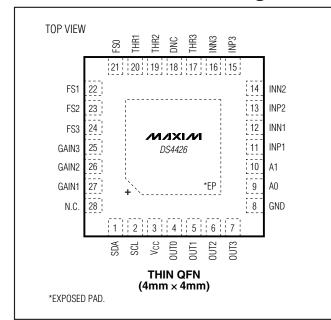

## Pin Configuration

**Applications**

# **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| DS4426T+    | -40°C to +85°C | 28 TQFN-EP* |

| DS4426T+T&R | -40°C to +85°C | 28 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. T&R = Tape and reel.

\*EP = Exposed pad.

Functional Diagram appears at end of data sheet.

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **S4426**

### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on SDA, SCL Relative to GND.....-0.5V to +6.0V Voltage Range on V<sub>CC</sub> Relative to GND .....-0.5V to +6.0V Voltage Range on A0, A1, FS[3:0], GAIN[3:1], INN[3:1], INP[3:1], THR[3:1], and OUT[3:0] Relative to GND .....-0.5V to (V<sub>CC</sub> + 0.5V)\*

| Operating Temperature Range | 40°C to +85°C            |

|-----------------------------|--------------------------|

| Storage Temperature Range   | 55°C to +125°C           |

| Soldering Temperature       |                          |

|                             | J-STD-020 Specification. |

\*Not to exceed +6.0V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                           | SYMBOL   | CONDITIONS | MIN                      | TYP MAX               | UNITS |

|-------------------------------------|----------|------------|--------------------------|-----------------------|-------|

| Supply Voltage                      | Vcc      | (Note 1)   | 2.7                      | 5.5                   | V     |

| Input Logic 1<br>(SDA, SCL, A0, A1) | VIH      |            | 0.7 x<br>V <sub>CC</sub> | V <sub>CC</sub> + 0.3 | V     |

| Input Logic 0<br>(SDA, SCL, A0, A1) | VIL      |            | -0.3                     | 0.3 x<br>VCC          | V     |

| Full-Scale Resistor Values          | RFS[3:0] | (Note 2)   | 40                       | 160                   | kΩ    |

## DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                           | SYMBOL           | CONDITIONS                       | MIN   | ТҮР   | MAX   | UNITS  |

|-------------------------------------|------------------|----------------------------------|-------|-------|-------|--------|

| Supply Current                      | Icc              | V <sub>CC</sub> = +5.5V (Note 3) |       |       | 0.9   | mA     |

| Input Leakage Current<br>(SDA, SCL) | IIL              | V <sub>CC</sub> = +5.5V          | -1    |       | +1    | μA     |

| RFS Voltage                         | V <sub>RFS</sub> | $T_{A} = +25^{\circ}C$           | 0.940 | 0.990 | 1.040 | V      |

| Reference Voltage                   | VREF             |                                  |       | 1.24  |       | V      |

| Temperature Coefficient             |                  |                                  |       | ±100  |       | ppm/°C |

| Output Leakage Current (SDA)        | ١L               |                                  | -1    |       | +1    | μA     |

| Output-Current Low (SDA)            |                  | $V_{OL} = +0.4V$                 | 3     |       |       | m A    |

|                                     | IOL              | $V_{OL} = +0.6V$                 | 6     |       |       | mA     |

| I/O Capacitance                     | CI/O             |                                  |       |       | 10    | pF     |

# DAC OUTPUT CURRENT CHARACTERISTICS

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                       | SYMBOL | L CONDITIONS                                  |  | ТҮР  | МАХ | UNITS |

|---------------------------------|--------|-----------------------------------------------|--|------|-----|-------|

| Output Current Variation Due to |        | DC source, V <sub>OUT</sub> measured at +1.2V |  | 0.33 |     | %N    |

| Power-Supply Change             |        | DC sink, V <sub>OUT</sub> measured at +1.2V   |  | 0.33 |     | /0/V  |

| Output Current Variation Due to |        | DC source, $V_{CC} = +3.6V$                   |  | 0.15 |     | %N    |

| Output-Voltage Change           |        | DC sink, $V_{CC} = +3.6V$                     |  | 0.30 |     | /o/V  |

# DAC OUTPUT CURRENT CHARACTERISTICS (continued)

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                                         | SYMBOL      | CONDITIONS           | MIN  | ТҮР  | MAX                       | UNITS  |

|---------------------------------------------------|-------------|----------------------|------|------|---------------------------|--------|

| Output Voltage for Sinking<br>Current             | Vout:sink   | (Note 4)             | 0.5  |      | 3.5                       | V      |

| Output Voltage for Sourcing<br>Current            | VOUT:SOURCE | (Note 4)             | 0    |      | V <sub>CC</sub> -<br>0.75 | V      |

| Full-Scale Sink Output Current                    | IOUT:SINK   | (Note 4)             | 50   |      | 200                       | μA     |

| Full-Scale Source Output Current                  | IOUT:SOURCE | (Note 4)             | -200 |      | -50                       | μA     |

| Output-Current Full-Scale<br>Accuracy             | IOUT:FS     | $T_A = +25^{\circ}C$ |      |      | ±5                        | %      |

| Output-Current Temperature<br>Coefficient         | IOUT:TC     | (Note 5)             |      | ±130 |                           | ppm/°C |

| Output-Current Power-Supply<br>Rejection Ratio    |             |                      |      | 0.33 |                           | %N     |

| Output-Leakage Current at Zero<br>Current Setting | IZERO       |                      | -1   |      | +1                        | μA     |

| Output-Current Differential<br>Linearity          | DNL         | (Note 6)             |      |      | 0.5                       | LSB    |

| Output-Current Integral Linearity                 | INL         | (Note 7)             |      |      | 1                         | LSB    |

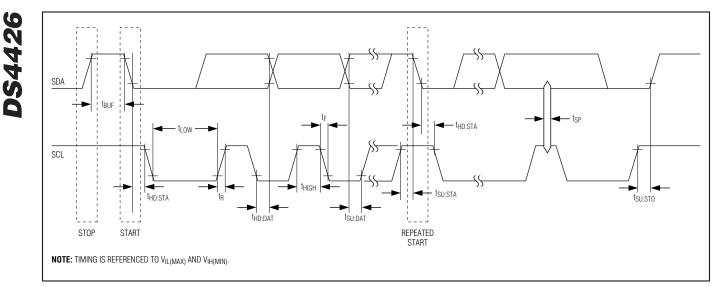

# I<sup>2</sup>C ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +2.7V to +5.5V,  $T_A$  = -40°C to +85°C. Timing referenced to V<sub>IL(MAX)</sub> and V<sub>IH(MIN)</sub>. See Figure 6.)

| PARAMETER                                          | SYMBOL  | CONDITIONS | MIN TYP                   | MAX | UNITS |

|----------------------------------------------------|---------|------------|---------------------------|-----|-------|

| SCL Clock Frequency                                | fSCL    | (Note 8)   | 0                         | 400 | kHz   |

| Bus Free Time Between STOP<br>and START Conditions | tBUF    |            | 1.3                       |     | μs    |

| Hold Time (Repeated) START<br>Condition            | thd:sta |            | 0.6                       |     | μs    |

| Low Period of SCL                                  | tLOW    |            | 1.3                       |     | μs    |

| High Period of SCL                                 | thigh   |            | 0.6                       |     | μs    |

| Data Hold Time                                     | thd:dat |            | 0                         | 0.9 | μs    |

| Data Setup Time                                    | tsu:dat |            | 100                       |     | ns    |

| START Setup Time                                   | tsu:sta |            | 0.6                       |     | μs    |

| SDA and SCL Rise Time                              | tR      | (Note 9)   | 20 +<br>0.1C <sub>B</sub> | 300 | ns    |

| SDA and SCL Fall Time                              | tF      | (Note 9)   | 20 +<br>0.1C <sub>B</sub> | 300 | ns    |

| STOP Setup Time                                    | tsu:sto |            | 0.6                       |     | μs    |

| SDA and SCL Capacitive<br>Loading                  | CB      | (Note 9)   |                           | 400 | pF    |

3

**DS**4426

## **POWER-SUPPLY TRACKING CHARACTERISTICS**

(V<sub>CC</sub> = +2.7V to +5.5V,  $T_A$  = -40°C to +85°C, see Figure 5.)

| PARAMETER                                   | SYMBOL                         | CONDITIONS                                                                                 | MIN | ТҮР  | MAX                      | UNITS  |

|---------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------|-----|------|--------------------------|--------|

| Input Divider Ratio                         | R <sub>DIV</sub>               | R <sub>A</sub> /R <sub>B</sub> and R <sub>C</sub> /R <sub>D</sub>                          | 0.5 |      | 1                        |        |

| Output Load                                 | RL                             | $R_L = (R_F \times R_E)/(R_F + R_E)$                                                       | 1   |      | 20                       | kΩ     |

| Feedback Resistor Ratio                     | R <sub>F</sub> /R <sub>B</sub> |                                                                                            | 0.5 |      | 4.5                      |        |

| Gain Resistor                               | RG                             |                                                                                            | 0.8 |      | 10                       | kΩ     |

| Gain Setting Ratio                          | RL/RG                          |                                                                                            | 1.4 |      | 5                        |        |

| Dower Supply Tracking Cain                  | Ch #                           | $R_L/R_G = 2, R_L = 5k\Omega, V_{CC} = +3.6V,$<br>$T_A = +25^{\circ}C$                     |     | 2.4  |                          |        |

| Power-Supply Tracking Gain                  | Gvi                            | $R_L/R_G = 5, R_L = 5k\Omega, V_{CC} = +3.6V, T_A = +25^{\circ}C$                          | 3.8 | 6.2  | 10                       | - mA/V |

| Power-Supply Tracking Input<br>Bias Current | IB                             |                                                                                            |     |      | 1                        | μA     |

| Power-Supply Tracking Input<br>Voltage      | V <sub>IN</sub>                | INP[3:1] and INN[3:1]                                                                      | 0   |      | V <sub>CC</sub> -<br>1.4 | V      |

| Unity Gain Bandwidth                        | GBW                            | $R_L/R_G = 1.4; R_L = 5k\Omega$                                                            |     | 12   |                          | MHz    |

| Output Voltage While Tracking               | Vout:trk                       | Switch closed, V <sub>CC</sub> = +3.0V, measured at OUT[3:1], R <sub>L</sub> = 5k $\Omega$ | 0   |      | 1.5                      | V      |

| Output Current While Tracking               | IOUT:TRK                       | $R_L/R_G = 1.4, R_G = 1 k\Omega, V_{CC} = +3.0V, V_{FB} = +0.8V$                           |     |      | 1                        | mA     |

| Tracking Accuracy                           |                                |                                                                                            |     |      | ±600                     | mV     |

| Output Leakage                              | IBC                            | Switch open                                                                                |     |      | 0.5                      | μA     |

| Comparator Input Bias Current               | IOFF                           |                                                                                            |     |      | 1                        | μA     |

| Comparator Input Offset                     | Vos                            |                                                                                            |     | ±5   |                          | mV     |

| Switch Delay                                | tDC                            |                                                                                            |     | 5    |                          | μs     |

| Comparator Hysteresis                       | VHYS                           |                                                                                            |     | 12.5 |                          | mV     |

**Note 1:** All voltages are referenced to GND. Current entering the IC is specified positive, and current exiting the IC is negative.

Note 2: Input resistors (R<sub>FS[3:0]</sub>) must be between the specified values to ensure the device meets its accuracy and linearity specifications.

Note 3: Supply current specified with all outputs set to zero current setting and with all inputs at V<sub>CC</sub> or GND. SDA and SCL are connected to V<sub>CC</sub>. Excludes current through R<sub>FS</sub> resistors (I<sub>RFS</sub>). Total current including I<sub>RFS</sub> is I<sub>CC</sub> + (2 x I<sub>RFS</sub>).

**Note 4:** The output-voltage full-scale ranges must be satisfied to ensure the device meets its accuracy and linearity specifications. Only applies to current DAC operation, not power-supply tracking operation.

Note 5: Temperature drift excludes drift caused by external resistors.

**Note 6:** Differential linearity is defined as the difference between the expected incremental current increase with respect to position and the actual increase. The expected incremental increase is the full-scale range divided by 127.

**Note 7:** Integral linearity is defined as the difference between the expected value as a function of the setting and the actual value. The expected value is a straight line between the zero and the full-scale values proportional to the setting.

Note 8: Timing shown is for fast-mode operation (400kHz). This device is also backward-compatible with I<sup>2</sup>C standard-mode timing.

Note 9: CB-Total capacitance of one bus line in pF.

M/IXI/M

4

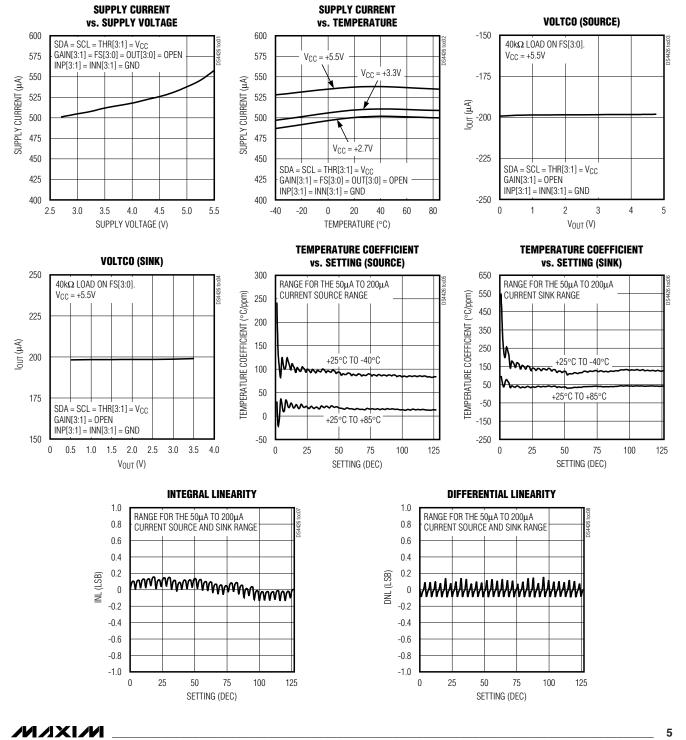

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

**DS4426**

## **Pin Description**

| PIN        | NAME                   | FUNCTION                                                                                                                            |

|------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SDA                    | Serial Data Input/Output. I <sup>2</sup> C data pin.                                                                                |

| 2          | SCL                    | Serial Clock Input. I <sup>2</sup> C clock input.                                                                                   |

| 3          | Vcc                    | Voltage Supply                                                                                                                      |

| 4          | OUT0                   | Current DAC Output                                                                                                                  |

| 5, 6, 7    | OUT1, OUT2, OUT3       | Current DAC and Tracking Control Output                                                                                             |

| 8          | GND                    | Ground                                                                                                                              |

| 9          | AO                     | I <sup>2</sup> C Address Input 0                                                                                                    |

| 10         | A1                     | I <sup>2</sup> C Address Input 1                                                                                                    |

| 11, 13, 15 | INP1, INP2, INP3       | Power-Supply Tracking Positive Input                                                                                                |

| 12, 14, 16 | INN1, INN2, INN3       | Power-Supply Tracking Negative Input                                                                                                |

| 17, 19, 20 | THR3, THR2, THR1       | Threshold Input. Comparator input used to set threshold for tracking enable/disable based on $V_{\text{REF}}/2$ .                   |

| 18         | DNC                    | Do Not Connect                                                                                                                      |

| 21–24      | FS0, FS1, FS2, FS3     | Full-Scale Calibration Input. A resistor-to-ground on this input determines full-<br>scale output current on the associated output. |

| 25, 26, 27 | GAIN3, GAIN2,<br>GAIN1 | Gain Adjustment Pin. Connect a resistor between this pin and $V_{CC}$ .                                                             |

| 28         | N.C.                   | No Connection                                                                                                                       |

| _          | EP                     | Exposed Pad. No connection.                                                                                                         |

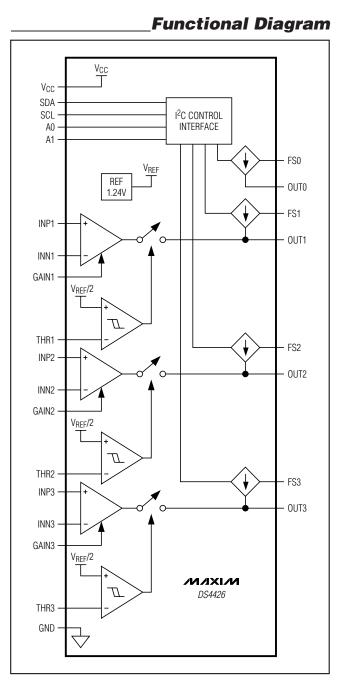

## **Detailed Description**

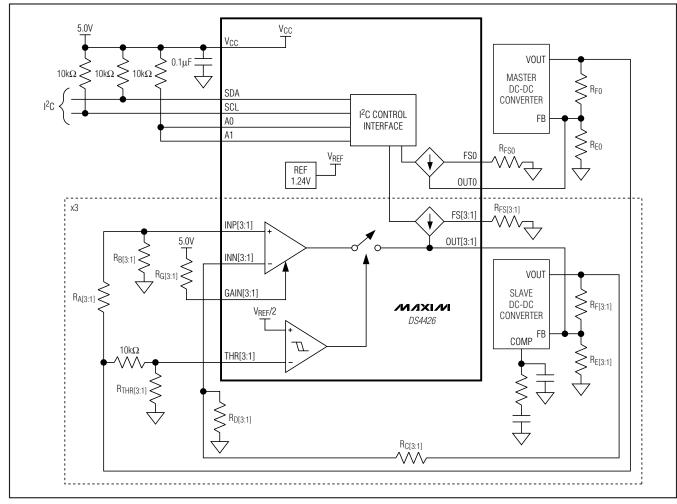

The DS4426 contains four I<sup>2</sup>C-adjustable current sources that are each capable of sinking and sourcing current. Three of the current outputs (OUT[3:1]) also have power-supply tracking circuitry that allows additional current to be sourced during power-up.

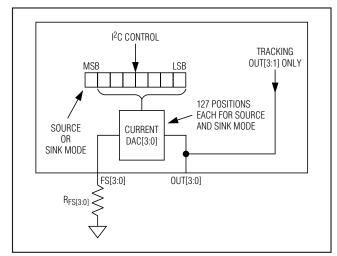

#### **Adjustable Current DACs**

Each output (OUT[3:0]) has 127 sink and 127 source settings that are programmed through the I<sup>2</sup>C interface. The full-scale current ranges (and corresponding step sizes) of the outputs are determined by external resistors connected to the corresponding FS pins (see Figure 1). The formula to determine the external resistor values (RFS) for each output is given by:

$$R_{FS} = \frac{V_{RFS}}{16 \times I_{FS}} \times 127$$

where IFS is the desired full-scale current value, VRFS is the RFS voltage (see the *DC Electrical Characteristics* table), and RFS is the external resistor value. To calculate the output-current value ( $I_{OUT}$ ) based on the corresponding DAC value (see Table 2 for corresponding memory addresses), use the following equation:

$$I_{OUT} = \frac{DACValue(dec)}{127} \times I_{FS}$$

On power-up, the DS4426 current DAC outputs are set to zero current. This is done to prevent the device from sinking or sourcing an incorrect current before the system host controller has a chance to modify its setting. Note, however, that if power-supply tracking is enabled (see the *Power-Supply Tracking Circuit* section), then the DS4426 can still source current at power-up.

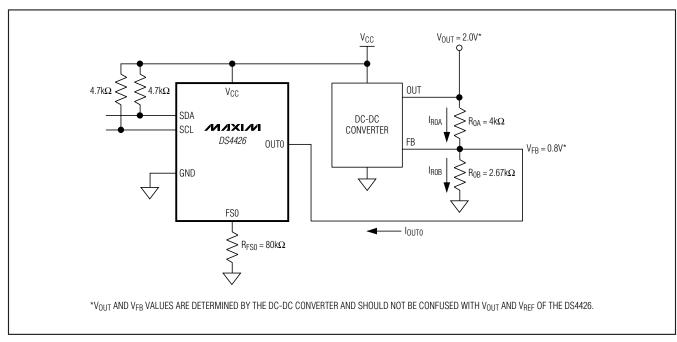

When used in adjustable power-supply applications (see Figure 8), the DS4426 does not affect the initial power-up voltage of the supply because it defaults to providing zero output current on power-up unless power-supply tracking is enabled. As it sources or sinks current into the feedback voltage node, it changes the amount of output voltage required by the regulator to reach its steady-state operating point.

M/XI/N

**S4426**

Figure 1. Current DAC Detail

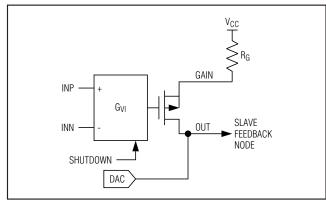

Figure 2. Gain Stage

Figure 3. INP and INN Differential Inputs

M \X | M

Using the external resistors R<sub>FS[3:0]</sub> to set the outputcurrent range, the DS4426 provides some flexibility for adjusting the impedances of the feedback network or the range over which the power supply can be controlled or margined.

As a source for biasing instrumentation or other circuits, the DS4426 provides a simple and inexpensive current source with an I<sup>2</sup>C interface for control. The adjustable, full-scale range allows the application to get the most out of its 7-bit sink or source resolution.

# \_Power-Supply Tracking Circuit

By making use of the power-supply tracking circuitry, the DS4426 has the ability to source current on powerup. This current is additive with the current DAC source/sink currents and is determined by the value of the gain resistor,  $R_G$ , and the supply voltage,  $V_{CC}$ . This current is controlled by the voltages presented to the corresponding INP and INN pins, and the voltages presented to the corresponding threshold (THR) pins.

## **Maximum Source Current**

The maximum current the DS4426 can source at power-up using the power-supply tracking circuitry depends on the value of the supply voltage, V<sub>CC</sub>, and the gain resistor, R<sub>G</sub>, connected from the corresponding GAIN pin to V<sub>CC</sub>. The maximum current (I<sub>MAX</sub>) that can be sourced to the corresponding OUT pin can be estimated using the following equation:

$$I_{MAX} \cong \frac{\left(V_{CC} - V_{OUT}\right)}{R_{G}}$$

The power-supply tracking circuit can be estimated with Figure 2.

#### Inputs for Power-Supply Tracking: INP and INN

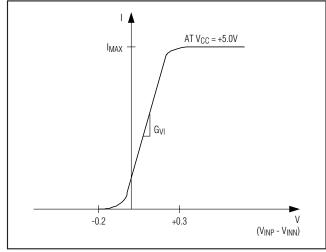

Each pair of power-supply tracking inputs, INP and INN, determines if and how much of the I<sub>MAX</sub> current is sourced when the power-supply tracking circuit is enabled. When the difference between the voltage presented to INP (V<sub>INP</sub>) and INN (V<sub>INN</sub>) is more than approximately +0.3V, then the maximum source current, as determined by the value I<sub>MAX</sub>, is sourced into the OUT pin connection. When the difference between V<sub>INP</sub> and V<sub>INN</sub> is less than approximately -0.2V, then no current is sourced into the corresponding OUT pin. The change in current from no current to I<sub>MAX</sub> can be estimated by the power-supply tracking gain, G<sub>VI</sub> (see the *Power-Supply Tracking Characteristics* table).

Figure 3 shows the typical current behavior of the power-supply tracking circuit with respect to the voltage difference seen at the INP and INN inputs.

Figure 4. Enabling Power-Supply Tracking Using the THR Input

#### THR Inputs for Enabling Power-Supply Tracking

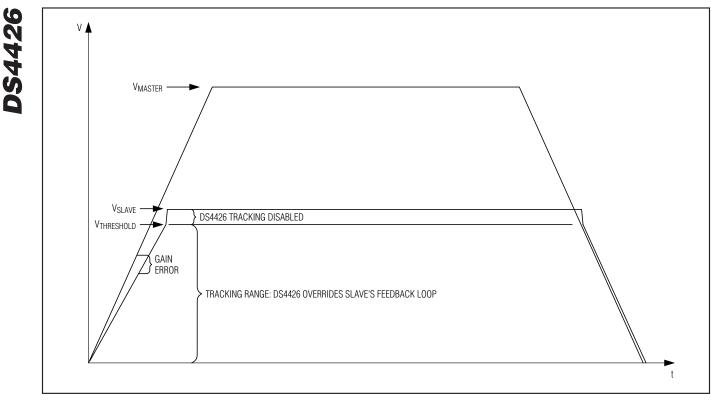

Comparators are used to individually enable/disable power-supply tracking based on the voltage presented to the corresponding THR pin relative to a fixed internal reference (V<sub>REF</sub>/2 = +0.62V). Figure 4 shows a typical startup and shutdown plot based on the voltage presented to the THR pin. Tracking can be disabled by connecting the corresponding THR pin to a voltage greater than V<sub>REF</sub>/2. Below this threshold, the tracking circuit is active.

## Power-Supply Tracking in DC-DC Power Applications

The DS4426 provides several options for power-supply tracking control of DC-DC power supplies. In many cases, it is desirable to prevent certain DC-DC supplies from exceeding the voltage of other supplies. This is often the case with the voltages applied to a digital core and I/O. Each DS4426 supports one master with three slave DC-DCs. See Figure 5 for more information.

#### Loop Bandwidth Consideration

Power-supply tracking is used to override each slave DC-DC's feedback loop during power-up and powerdown. Power-supply tracking is capable of slewing at a much faster rate than most DC-DC converters. Care must be exercised when selecting the loop bandwidth of the master DC-DC, slave DC-DC, and power-supply tracking control loop such that oscillations and overshoot are minimized.

While the slave DC-DC supplies are tracking the master DC-DC supply, there are three time constants of concern:

- 1) Master BW. The master DC-DC control loop bandwidth, power-up ramp rate, and power-down ramp rate.

- 2) Slave BW. The slave DC-DC supplies control loop bandwidths.

- Tracking BW. The DS4426 tracking circuit bandwidth.

To ensure stable operation and minimize peaking, the bandwidths should follow the following rule:

Master BW and Slave BW < (Tracking BW/10)

M/IXI/M

Figure 5. Typical DC-DC Power-Supply Tracking Application

#### **Ratiometric Tracking**

The DS4426 can maintain a defined ratio between a slave voltage and the master voltage where:

KSM = VSLAVE/VMASTER.

In Figure 5, this ratio is given by the following:

$$K_{SM} = [R_{B[3:1]}/(R_{A[3:1]} + R_{B[3:1]})]/[R_{D[3:1]}/(R_{C[3:1]} + R_{D[3:1]})].$$

Nonratiometric tracking is the special case where  $K_{SM} = 1$ .

#### **Power-Supply Tracking Loop Gain Stability**

Slave DC-DC output tracking is controlled by the DS4426 sourcing current into the slave DC-DC's feedback loop. This changes the stability of the loop during tracking. The amount of gain used can be adjusted by

changing the ratio of RL/RG. If oscillations occur, increasing RG reduces gain and increases the system's phase margin. If the slave DC-DC has a compensation pin, the RC network connected to this pin can also be adjusted to improve phase margin. This pin is often labeled COMP or ITH. A larger compensation time constant (increased R and/or increased C) often increases the stability of the system during tracking; however, this also modifies the DC-DC's transient response. In order to prevent modification of the slave DC-DC's transient response after power-supply tracking is complete, RG should first be modified before adjusting the compensation network. The higher the gain, the less the gain error. Reducing the gain increases the gain error during tracking. See Figure 4 for more information.

<sup>9</sup>

## Table 1. Slave Addresses

| A1  | A0  | SLAVE ADDRESS (HEX) |

|-----|-----|---------------------|

| GND | GND | 90h                 |

| GND | Vcc | 92h                 |

| Vcc | GND | 94h                 |

| Vcc | Vcc | 96h                 |

#### Inputs for Tracking in DC-DC Power Applications

When enabling/disabling the power-supply tracking, a resistor-divider connected to the THR input sets the disable threshold (see V<sub>THRESHOLD</sub> in Figure 4). The top of the resistor-divider must be connected to the master DC-DC voltage for correct operation. Below this threshold, the tracking circuit is active.

#### **Power-Supply Sequencing**

The DS4426 can be used to perform power-supply sequencing. This is a subset of power-supply tracking with modifications to the external resistor network. The basic concept is that the DS4426 sources maximum current into the slave power supply's feedback node until a voltage in the system has risen above a specific voltage level. By sourcing the maximum current into the feedback node, the power supply's output is held off. Maximum sourcing current is achieved with two steps:

- Apply the maximum allowed input voltage across INP and INN. Connect INP to V<sub>CC</sub> - 1.4V using a voltage-divider to ground. Connect INN to ground.

- 2) Set the gain to the maximum allowed ( $R_L/R_G = 5$ ).

The slave power supply is allowed to turn on once the voltage on THR is greater than  $V_{REF}/2$ . Use a resistordivider connected to the rising system voltage to scale the trip point to  $V_{REF}/2$ .

# I<sup>2</sup>C Slave Address

The DS4426 responds to one of four I<sup>2</sup>C slave addresses determined by the state of the input on the two address inputs. The two input states are connected to  $V_{CC}$  or connected to ground.

#### **Table 2. Memory Addresses**

| MEMORY ADDRESS (HEX) | CURRENT SOURCE |

|----------------------|----------------|

| F8h                  | OUTO           |

| F9h                  | OUT1           |

| FAh                  | OUT2           |

| FBh                  | OUT3           |

## Memory Organization

The DS4426's current sources are controlled by writing to memory addresses listed in Table 2.

The format of each of the output control registers is given by:

| BIT 7<br>(MSB) | BIT 6          | BIT 5          | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0<br>(LSB) |

|----------------|----------------|----------------|-------|-------|-------|-------|----------------|

| S              | D <sub>6</sub> | D <sub>5</sub> | D4    | D3    | D2    | D1    | D <sub>0</sub> |

where:

| віт | NAME        | DESCRIPTION                                                                                                                     | POWER-ON<br>DEFAULT |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|

| s   | Sign<br>Bit | Determines if DAC sources or<br>sinks current. For sink, $S = 0$ .<br>For source, $S = 1$ .                                     | 0b                  |

| Dx  | Data        | 7-bit data word controlling DAC<br>output. Setting 0000000b<br>outputs zero current regardless<br>of the state of the sign bit. | 000000b             |

For example:

${\sf R}_{FS0}$  = 80k $\Omega$  and register 0xF8h is written to a value of 0xAAh. Use the following formula to calculate the output current:

$$FS = (1.0V/80k\Omega) \times (127/16) = 99.22\mu A$$

The MSB of the output register is 1, so the output is sourcing the value corresponding to position 2Ah (42 decimal). The magnitude of the output current is equal to the following:

99.22µA x (42/127) = 32.8125µA

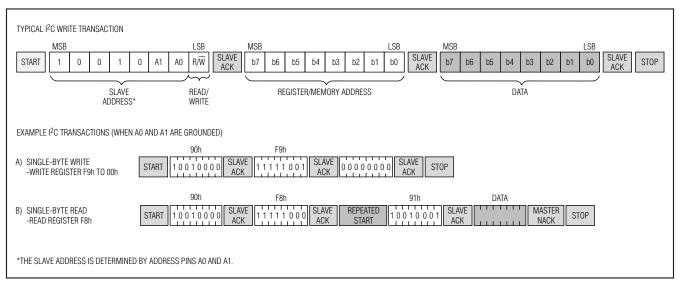

# I<sup>2</sup>C Serial Interface Description

#### **I<sup>2</sup>C Definitions**

The following terminology is commonly used to describe I<sup>2</sup>C data transfers:

**I<sup>2</sup>C Slave Address:** The slave address of the DS4426 is determined by the state of the A0 and A1 pins (see Table 1).

**Master Device:** The master device controls the slave devices on the bus. The master device generates SCL clock pulses and START and STOP conditions.

**Slave Devices:** Slave devices send and receive data at the master's request.

**Bus Idle or Not Busy:** Time between STOP and START conditions when both SDA and SCL are inactive and in their logic-high states. When the bus is idle it often initiates a low-power mode for slave devices.

**START Condition:** A START condition is generated by the master to initiate a new data transfer with a slave. Transitioning SDA from high to low while SCL remains high generates a START condition. See Figure 3 for applicable timing.

**STOP Condition:** A STOP condition is generated by the master to end a data transfer with a slave. Transitioning SDA from low to high while SCL remains high generates a STOP condition. See Figure 3 for applicable timing.

**Repeated START Condition:** The master can use a repeated START condition at the end of one data transfer to indicate that it will immediately initiate a new data transfer following the current one. Repeated STARTs are commonly used during read operations to identify a specific memory address to begin a data transfer. A repeated START condition is issued identically to a normal START condition. See Figure 6 for applicable timing.

**Bit Write:** Transitions of SDA must occur during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL, plus the setup-and-hold time requirements (Figure 6). Data is shifted into the device during the rising edge of the SCL.

**Bit Read:** At the end of a write operation, the master must release the SDA bus line for the proper amount of setup time (Figure 6) before the next rising edge of SCL during a bit read. The device shifts out each bit of data on SDA at the falling edge of the previous SCL pulse, and the data bit is valid at the rising edge of the current SCL pulse. Remember that the master generates all SCL clock pulses, including when it is reading bits from the slave.

Acknowledgement (ACK and NACK): An Acknowledgement (ACK) or Not Acknowledge (NACK) is always the ninth bit transmitted during a byte transfer. The device receiving data (the master during a read or the slave during a write operation) performs an ACK by transmitting a zero during the ninth bit. A device performs a NACK by transmitting a 1 during the ninth bit. Timing for the ACK and NACK is identical to all other bit writes (Figure 6). An ACK is the acknowledgment that the device is properly receiving data. A NACK is used to terminate a read sequence or as an indication that the device is not receiving data.

**Byte Write:** A byte write consists of 8 bits of information transferred from the master to the slave (most significant bit first) plus a 1-bit acknowledgement from the slave to the master. The 8 bits transmitted by the master are done according to the bit-write definition, and the acknowledgement is read using the bit-read definition.

**Byte Read:** A byte read is an 8-bit information transfer from the slave to the master plus a 1-bit ACK or NACK from the master to the slave. The 8 bits of information that are transferred (most significant bit first) from the slave to the master are read by the master using the bit-read definition, and the master transmits an ACK using the bit-write definition to receive additional data bytes. The master must NACK the last byte read to terminate communication so the slave returns control of SDA to the master.

**Slave Address Byte:** Each slave on the I<sup>2</sup>C bus responds to a slave address byte sent immediately following a START condition. The slave address byte contains the slave address in the most significant 7 bits and the  $R/\overline{W}$  bit in the least significant bit. The DS4426's slave address is determined by the state of the A0 and A1 pins (see Table 1). When the  $R/\overline{W}$  bit is 0 (such as in 90h), the master is indicating it will write data to the slave. If  $R/\overline{W} = 1$  (91h in this case), the master is indicating it wants to read from the slave. If an incorrect slave address is written, the DS4426 assumes the master is communicating with another I<sup>2</sup>C device and ignores the communication until the next START condition is sent.

**Memory Address:** During an I<sup>2</sup>C write operation, the master must transmit a memory address to identify the memory location where the slave is to store the data. The memory address is always the second byte transmitted during a write operation following the slave address byte.

Figure 6. I<sup>2</sup>C Timing Diagram

Figure 7. I<sup>2</sup>C Communication Examples

# I<sup>2</sup>C Communication

Writing to a Slave: The master must generate a START condition, write the slave address byte ( $R/\overline{W} = 0$ ), write the memory address, write the byte of data, and generate a STOP condition. Remember that the master must read the slave's acknowledgement during all byte-write operations.

**Reading from a Slave:** To read from the slave, the master generates a START condition, writes the slave address byte with R/W = 1, reads the data byte with a NACK to indicate the end of the transfer, and generates a STOP condition.

M/IXI/N

Downloaded from Elcodis.com electronic components distributor

## **Applications Information**

#### Example Calculations for an Adjustable Power Supply

In this example, the circuit shown in Figure 8 is used to margin a +2.0V supply by ±20%. The margined power supply has a DC-DC converter output voltage, V<sub>OUT</sub>, of +2.0V and a DC-DC converter feedback voltage, V<sub>FB</sub>, of +0.8V. To determine the relationship of R<sub>0A</sub> and R<sub>0B</sub>, start with the equation:

$$V_{FB} = \frac{R_{0B}}{R_{0A} + R_{0B}} \times V_{OUT}$$

Substituting V<sub>FB</sub> = +0.8V and V<sub>OUT</sub> = +2.0V, the relationship between R<sub>0A</sub> and R<sub>0B</sub> is determined to be:

$$R_{0A} = 1.5 \times R_{0B}$$

where:

and

$$I_{ROB} = \frac{V_{FB}}{R_{OB}}$$

$$I_{ROA} = \frac{V_{OUT} - V_{FB}}{R_{OA}}$$

To create a ±20% margin in the supply voltage, the value of V<sub>OUT</sub> is set to +2.4V. With these values in place, R<sub>0B</sub> is calculated to be 2.67k $\Omega$ , and R<sub>0A</sub> is

Figure 8. Example Typical Application Circuit

54426

calculated to be  $4.00k\Omega$ . The current DAC in this configuration allows the output voltage to be moved linearly from +1.6V to +2.4V using 127 settings. This corresponds to a resolution of 6.3mV/step.

## VCC Decoupling

To achieve the best results when using the DS4426, decouple the power supply with a  $0.01\mu$ F (or  $0.1\mu$ F) capacitor. Use a high-quality, ceramic, surface-mount capacitor if possible. Surface-mount components minimize lead inductance, which improves performance. Ceramic capacitors tend to have adequate high-frequency response for decoupling applications.

## **Package Information**

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 28 TQFN      | T2844+1      | <u>21-0139</u> |

# **Revision History**

**DS**4426

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                       | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 4/08             | Initial release.                                                                                                                                                  | _                |

| 1                  | 7/09             | Added OUT[3:0] to the <i>Absolute Maximum Ratings</i> for the following condition: Voltage Range on A0, A1, FS[3:0], GAIN[3:1], INN[3:1], INP[3:1], and THR[3:1]. | 2                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_

© 2009 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.

\_\_\_\_\_ 15