# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC04 January 1995

**Semiconductors**

**Philips**

## HEF4053B MSI

#### DESCRIPTION

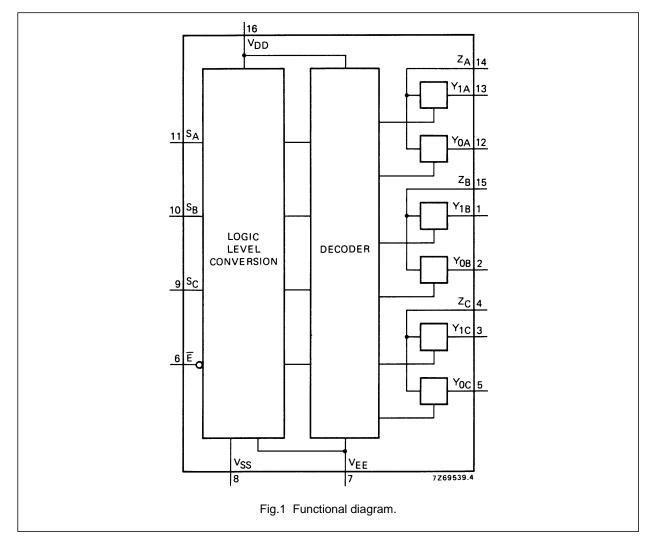

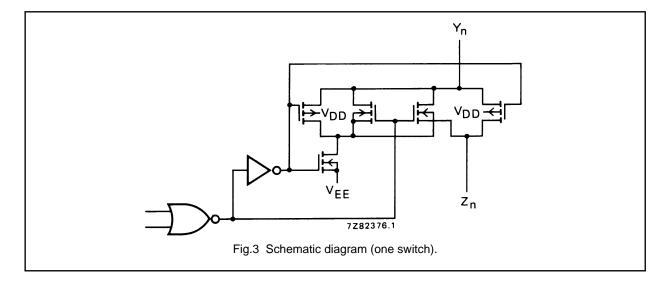

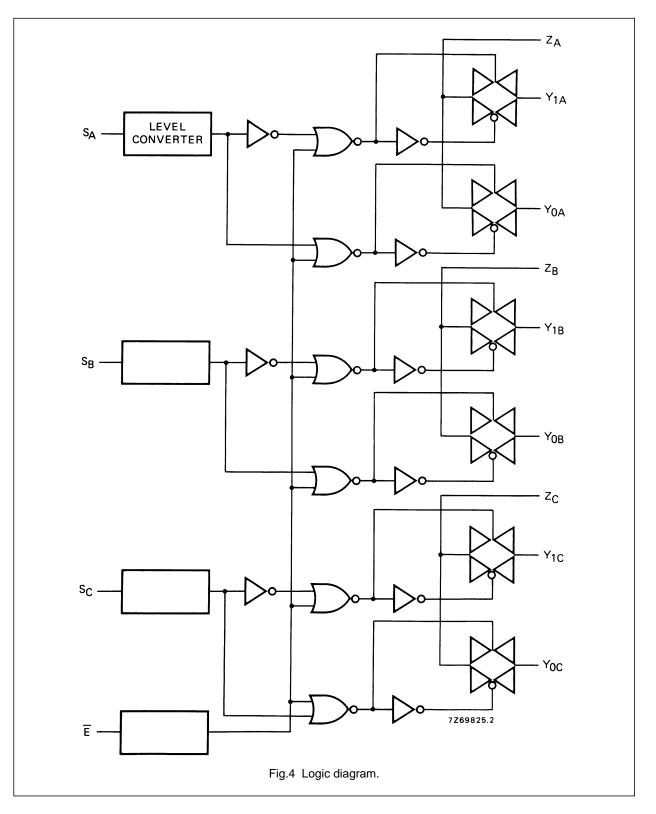

The HEF4053B is a triple 2-channel analogue multiplexer/demultiplexer with a common enable input ( $\overline{E}$ ). Each multiplexer/demultiplexer has two independent inputs/outputs (Y<sub>0</sub> and Y<sub>1</sub>), a common input/output (Z), and select inputs (S<sub>n</sub>). Each also contains two-bidirectional analogue switches, each with one side connected to an independent input/output (Y<sub>0</sub> and Y<sub>1</sub>) and the other side connected to a common input/output (Z).

With  $\overline{E}$  LOW, one of the two switches is selected (low impedance ON-state) by S<sub>n</sub>. With  $\overline{E}$  HIGH, all switches are in the high impedance OFF-state, independent of S<sub>A</sub> to S<sub>C</sub>.

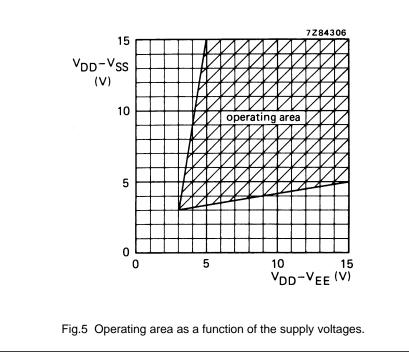

$V_{DD}$  and  $V_{SS}$  are the supply voltage connections for the digital control inputs (S<sub>A</sub> to S<sub>C</sub> and  $\overline{E}$ ). The  $V_{DD}$  to  $V_{SS}$  range is 3 to 15 V. The analogue inputs/outputs (Y<sub>0</sub>, Y<sub>1</sub> and Z) can swing between  $V_{DD}$  as a positive limit and  $V_{EE}$  as a negative limit.  $V_{DD}-V_{EE}$  may not exceed 15 V.

For operation as a digital multiplexer/demultiplexer,  $V_{\text{EE}}$  is connected to  $V_{\text{SS}}$  (typically ground).

### FAMILY DATA, I<sub>DD</sub> LIMITS category MSI

See Family Specifications

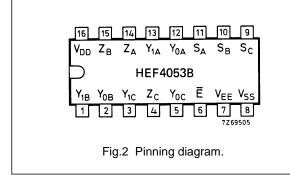

## HEF4053B MSI

| HEF4053BP(N):                        | 16-lead DIL; plastic          |  |  |  |

|--------------------------------------|-------------------------------|--|--|--|

|                                      | (SOT38-1)                     |  |  |  |

| HEF4053BD(F):                        | 16-lead DIL; ceramic (cerdip) |  |  |  |

|                                      | (SOT74)                       |  |  |  |

| HEF4053BT(D):                        | 16-lead SO; plastic           |  |  |  |

|                                      | (SOT109-1)                    |  |  |  |

| (): Package Designator North America |                               |  |  |  |

#### PINNING

| $Y_{0A}$ to $Y_{0C}$ | independent inputs/outputs |

|----------------------|----------------------------|

| $Y_{1A}$ to $Y_{1C}$ | independent inputs/outputs |

| $S_A$ to $S_C$       | select inputs              |

| Ē                    | enable input (active LOW)  |

| $Z_A$ to $Z_C$       | common inputs/outputs      |

### FUNCTION TABLE

| INPU | ITS | CHANNEL                         |

|------|-----|---------------------------------|

| Ē    | Sn  | ON                              |

| L    | L   | Y <sub>0n</sub> –Z <sub>n</sub> |

| L    | Н   | Y <sub>1n</sub> –Z <sub>n</sub> |

| н    | Х   | none                            |

#### Notes

H = HIGH state (the more positive voltage)

L = LOW state (the less positive voltage)

X = state is immaterial

#### RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Supply voltage (with reference to V<sub>DD</sub>)

```

-18 to + 0,5 V

```

$V_{EE}$

Note

To avoid drawing V<sub>DD</sub> current out of terminal Z, when switch current flows into terminals Y, the voltage drop across the bidirectional switch must not exceed 0,4 V. If the switch current flows into terminal Z, no V<sub>DD</sub> current will flow out of terminals Y, in this case there is no limit for the voltage drop across the switch, but the voltages at Y and Z may not exceed V<sub>DD</sub> or V<sub>EE</sub>.

## HEF4053B MSI

HEF4053B

MSI

# Triple 2-channel analogue multiplexer/demultiplexer

## DC CHARACTERISTICS

T<sub>amb</sub> = 25 °C

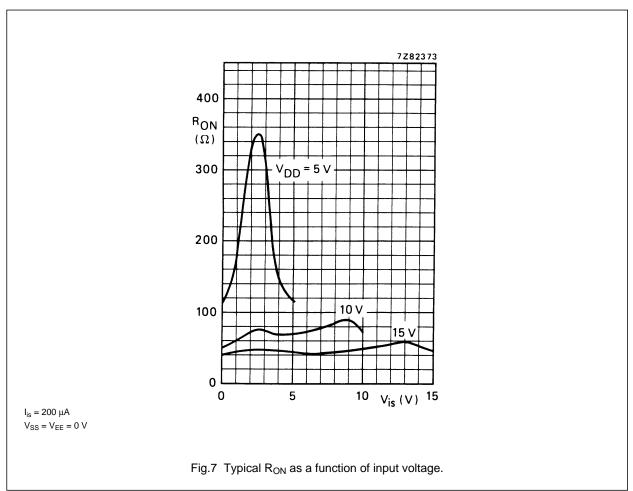

|                   | V <sub>DD</sub> -V <sub>EE</sub><br>V | SYMBOL           | TYP. | MAX. |    | CONDITIONS                                                           |

|-------------------|---------------------------------------|------------------|------|------|----|----------------------------------------------------------------------|

|                   | 5                                     |                  | 350  | 2500 | Ω  |                                                                      |

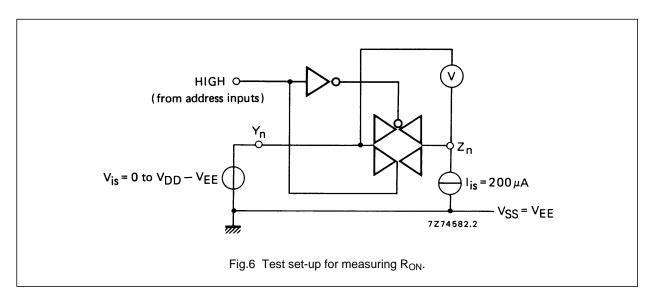

| ON resistance     | 10                                    | R <sub>ON</sub>  | 80   | 245  | Ω  | V <sub>is</sub> = 0 to V <sub>DD</sub> -V <sub>EE</sub><br>see Fig.6 |

|                   | 15                                    |                  | 60   | 175  | Ω  | 366 1 19.0                                                           |

|                   | 5                                     |                  | 115  | 340  | Ω  |                                                                      |

| ON resistance     | 10                                    | R <sub>ON</sub>  | 50   | 160  | Ω  | V <sub>is</sub> = 0<br>see Fig.6                                     |

|                   | 15                                    |                  | 40   | 115  | Ω  | 366 Fig.0                                                            |

|                   | 5                                     |                  | 120  | 365  | Ω  |                                                                      |

| ON resistance     | 10                                    | R <sub>ON</sub>  | 65   | 200  | Ω  | V <sub>is</sub> = V <sub>DD</sub> –V <sub>EE</sub><br>see Fig.6      |

|                   | 15                                    |                  | 50   | 155  | Ω  | 366 Fig.0                                                            |

| 'Δ' ON resistance | 5                                     |                  | 25   | _    | Ω  |                                                                      |

| between any two   | 10                                    | $\Delta R_{ON}$  | 10   | _    | Ω  | V <sub>is</sub> = 0 to V <sub>DD</sub> –V <sub>EE</sub><br>see Fig.6 |

| channels          | 15                                    |                  | 5    | _    | Ω  | 300 1 19.0                                                           |

| OFF-state leakage | 5                                     |                  | -    | _    | nA |                                                                      |

| current, all      | 10                                    | I <sub>OZZ</sub> | -    | _    | nA | Ē at V <sub>DD</sub>                                                 |

| channels OFF      | 15                                    |                  | -    | 1000 | nA |                                                                      |

| OFF-state leakage | 5                                     |                  | _    | _    | nA |                                                                      |

| current, any      | 10                                    | I <sub>OZY</sub> | -    | _    | nA | $\overline{E}$ at V <sub>SS</sub>                                    |

| channel           | 15                                    |                  | _    | 200  | nA |                                                                      |

## HEF4053B MSI

## HEF4053B MSI

### **AC CHARACTERISTICS**

$V_{EE}$  =  $V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C; input transition times  $\leq$  20 ns

|                 | V <sub>DD</sub><br>V | TYPICAL FORMULA FOR P ( $\mu$ W)                                                                 |                                      |

|-----------------|----------------------|--------------------------------------------------------------------------------------------------|--------------------------------------|

| Dynamic power   | 5                    | $2 \ 500 \ f_i + \sum (f_o C_L) \times V_{DD}^2$                                                 | where                                |

| dissipation per | 10                   | 11 500 f <sub>i</sub> + $\Sigma$ (f <sub>o</sub> C <sub>L</sub> ) × V <sub>DD</sub> <sup>2</sup> | f <sub>i</sub> = input freq. (MHz)   |

| package (P)     | 15                   | 29 000 $f_i + \sum (f_o C_L) \times V_{DD}^2$                                                    | f <sub>o</sub> = output freq. (MHz)  |

|                 |                      |                                                                                                  | $C_L = load capacitance (pF)$        |

|                 |                      |                                                                                                  | $\Sigma(f_o C_L) = sum of outputs$   |

|                 |                      |                                                                                                  | V <sub>DD</sub> = supply voltage (V) |

### AC CHARACTERISTICS

$V_{EE}$  =  $V_{SS}$  = 0 V;  $T_{amb}$  = 25 °C; input transition times  $\leq$  20 ns

|                                   | V <sub>DD</sub><br>V | SYMBOL           | TYP. | MAX. |    |        |

|-----------------------------------|----------------------|------------------|------|------|----|--------|

| Propagation delays                |                      |                  |      |      |    |        |

| $V_{is} \rightarrow V_{os}$       | 5                    |                  | 10   | 20   | ns |        |

| HIGH to LOW                       | 10                   | t <sub>PHL</sub> | 5    | 10   | ns | note 1 |

|                                   | 15                   |                  | 5    | 10   | ns |        |

|                                   | 5                    |                  | 15   | 30   | ns |        |

| LOW to HIGH                       | 10                   | t <sub>PLH</sub> | 5    | 10   | ns | note 1 |

|                                   | 15                   |                  | 5    | 10   | ns |        |

| $S_n \rightarrow V_{os}$          | 5                    |                  | 200  | 400  | ns |        |

| HIGH to LOW                       | 10                   | t <sub>PHL</sub> | 85   | 170  | ns | note 2 |

|                                   | 15                   |                  | 65   | 130  | ns |        |

|                                   | 5                    |                  | 275  | 555  | ns |        |

| LOW to HIGH                       | 10                   | t <sub>PLH</sub> | 100  | 200  | ns | note 2 |

|                                   | 15                   |                  | 65   | 130  | ns |        |

| Output disable times              |                      |                  |      |      |    |        |

| $\overline{E} \rightarrow V_{os}$ | 5                    |                  | 200  | 400  | ns |        |

| HIGH                              | 10                   | t <sub>PHZ</sub> | 115  | 230  | ns | note 3 |

|                                   | 15                   |                  | 110  | 220  | ns |        |

|                                   | 5                    |                  | 200  | 400  | ns |        |

| LOW                               | 10                   | t <sub>PLZ</sub> | 120  | 245  | ns | note 3 |

|                                   | 15                   |                  | 110  | 215  | ns |        |

| Output enable times               |                      |                  |      |      |    |        |

| $\overline{E} \to V_{os}$         | 5                    |                  | 260  | 525  | ns |        |

| HIGH                              | 10                   | t <sub>PZH</sub> | 95   | 190  | ns | note 3 |

|                                   | 15                   |                  | 65   | 130  | ns |        |

|                                   | 5                    |                  | 280  | 565  | ns |        |

| LOW                               | 10                   | t <sub>PZL</sub> | 105  | 205  | ns | note 3 |

|                                   | 15                   |                  | 70   | 140  | ns |        |

## HEF4053B MSI

|                       | V <sub>DD</sub><br>V | SYMBOL | TYP. | MAX. |        |

|-----------------------|----------------------|--------|------|------|--------|

| Distortion, sine-wave | 5                    |        | 0,25 | %    |        |

| response              | 10                   |        | 0,04 | %    | note 4 |

|                       | 15                   |        | 0,04 | %    |        |

| Crosstalk between     | 5                    |        | _    | MHz  |        |

| any two channels      | 10                   |        | 1    | MHz  | note 5 |

|                       | 15                   |        | -    | MHz  |        |

| Crosstalk; enable     | 5                    |        | _    | mV   |        |

| or address input      | 10                   |        | 50   | mV   | note 6 |

| to output             | 15                   |        | -    | mV   |        |

| OFF-state             | 5                    |        | -    | MHz  |        |

| feed-through          | 10                   |        | 1    | MHz  | note 7 |

|                       | 15                   |        | -    | MHz  |        |

| ON-state frequency    | 5                    |        | 13   | MHz  |        |

| response              | 10                   |        | 40   | MHz  | note 8 |

|                       | 15                   |        | 70   | MHz  |        |

#### Notes

Vis is the input voltage at a Y or Z terminal, whichever is assigned as input.

Vos is the output voltage at a Y or Z terminal, whichever is assigned as output.

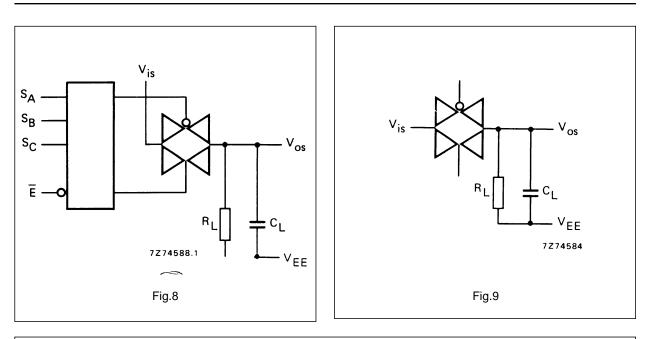

- 1.  $R_L = 10 \text{ k}\Omega$  to  $V_{EE}$ ;  $C_L = 50 \text{ pF}$  to  $V_{EE}$ ;  $\overline{E} = V_{SS}$ ;  $V_{is} = V_{DD}$  (square-wave); see Fig.8.

- 2.  $R_L = 10 \text{ k}\Omega$ ;  $C_L = 50 \text{ pF}$  to  $V_{EE}$ ;  $\overline{E} = V_{SS}$ ;  $S_n = V_{DD}$  (square-wave);  $V_{is} = V_{DD}$  and  $R_L$  to  $V_{EE}$  for  $t_{PLH}$ ;  $V_{is} = V_{EE}$  and  $R_L$  to  $V_{DD}$  for  $t_{PHL}$ ; see Fig.8.

- 3.  $R_L = 10 \text{ k}\Omega$ ;  $C_L = 50 \text{ pF to } V_{EE}$ ;  $\overline{E} = V_{DD}$  (square-wave);  $V_{is} = V_{DD}$  and  $R_L$  to  $V_{EE}$  for  $t_{PHZ}$  and  $t_{PZH}$ ;  $V_{is} = V_{EE}$  and  $R_L$  to  $V_{DD}$  for  $t_{PLZ}$  and  $t_{PZL}$ ; see Fig.8.

- 4.  $R_L = 10 \text{ k}\Omega$ ;  $C_L = 15 \text{ pF}$ ; channel ON;  $V_{is} = \frac{1}{2} V_{DD (p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ );  $f_{is} = 1 \text{ kHz}$ ; see Fig.9.

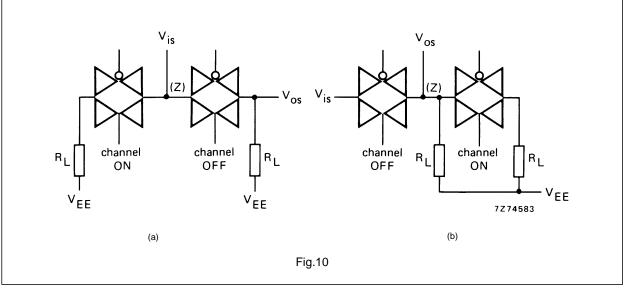

- 5.  $R_L = 1 k\Omega$ ;  $V_{is} = \frac{1}{2} V_{DD (p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ );

20 log

$$\frac{V_{os}}{V_{is}}$$

= -50 dB; see Fig. 10.

- 6.  $R_L = 10 \text{ k}\Omega$  to  $V_{EE}$ ;  $C_L = 15 \text{ pF}$  to  $V_{EE}$ ;  $\overline{E}$  or  $S_n = V_{DD}$  (square-wave); crosstalk is  $|V_{os}|$  (peak value); see Fig.8.

- 7.  $R_L = 1 k\Omega$ ;  $C_L = 5 pF$ ; channel OFF;  $V_{is} = \frac{1}{2} V_{DD (p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ );

20 log

$$\frac{V_{os}}{V_{is}}$$

= -50 dB; see Fig. 9.

8.  $R_L = 1 \text{ k}\Omega$ ;  $C_L = 5 \text{ pF}$ ; channel ON;  $V_{is} = \frac{1}{2} V_{DD (p-p)}$  (sine-wave, symmetrical about  $\frac{1}{2} V_{DD}$ );

20 log

$$\frac{V_{os}}{V_{is}}$$

= -3 dB; see Fig. 9.

HEF4053B

MSI

# Triple 2-channel analogue multiplexer/demultiplexer

#### **APPLICATION INFORMATION**

Some examples of applications for the HEF4053B are:

- Analogue multiplexing and demultiplexing.

- Digital multiplexing and demultiplexing.

- Signal gating.

#### NOTE

If break before make is needed, then it is necessary to use the enable input.