# SANYO Semiconductors **DATA SHEET**

An ON Semiconductor Company

LV8136V-

# For Brushless Motor Drive Direct PWM Drive, Quiet Predriver IC

### Overview

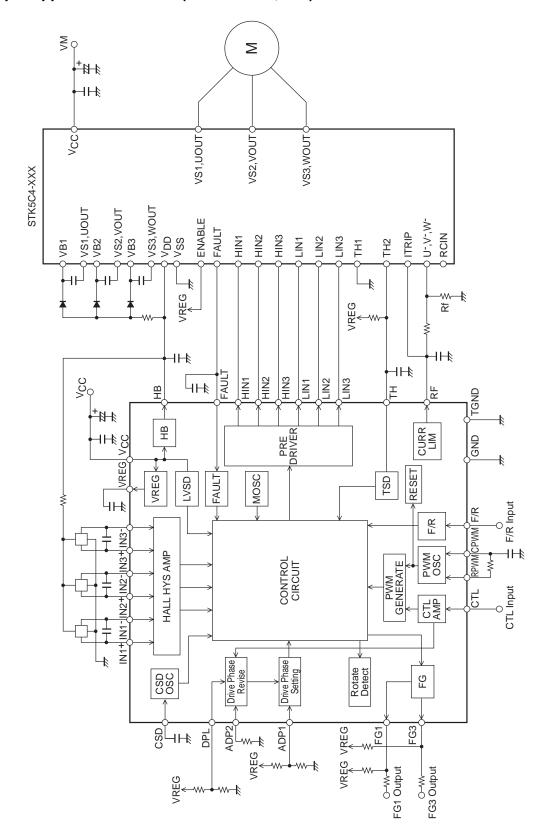

The LV8136V is a PWM system predriver IC designed for three-phase brushless motors.

**Bi-CMOS IC**

This IC reduces motor driving noise by using a high-efficiency, quiet PWM drive (150-degree drive system). It incorporates a full complement of protection circuits and, by combining it with a hybrid IC in the STK611 or STK5C4 series, the number of components used can be reduced and a high level of reliability can be achieved. Furthermore, its power-saving mode enables the power consumption in the standby mode to be reduced to zero. This IC is optimally suited for driving various large-size motors such as those used in air conditioners and hot-water heaters.

## **Features**

- Three-phase bipolar drive

- Quiet PWM drive (150-degree current-carrying)

- Supports drive phase control (15-degree lead angle for 150-degree current-carrying drive. From this state, a lead angle from 0 to 28 degrees can be set in 16 steps)

- Supports power saving mode(power saving mode at CTL pin voltage of 1.0V (typ) or less; I<sub>CC</sub> = 0mA, HB pin turned off)

- Supports bootstrap (maximum duty limit)

- Automatic recovery type constraint protection circuit

- Forward/reverse switching circuit, Hall bias pin

- Current limiter circuit, low-voltage protection circuit, and thermal shutdown protection circuit

- FG1 and FG3 output (360-degree electrical angle/1 pulse and 3 pulses)

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment. The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for new introduction or other application different from current conditions on the usage of automotive device, communication device, office equipment, industrial equipment etc., please consult with us about usage condition (temperature, operation time etc.) prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

## SANYO Semiconductor Co., Ltd.

http://semicon.sanyo.com/en/network

## **Specifications**

## **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol                                         | Conditions                             | Ratings     | Unit |

|-----------------------------|------------------------------------------------|----------------------------------------|-------------|------|

| Supply voltage              | V <sub>CC</sub> max                            | V <sub>CC</sub> pin                    | 18          | V    |

| Output current              | I <sub>O</sub> max                             |                                        | 15          | mA   |

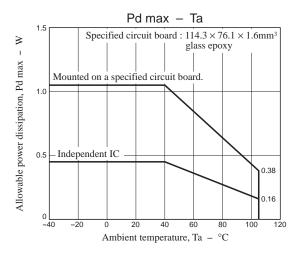

| Allowable power dissipation | Pd max1                                        | Independent IC                         | 0.45        | W    |

|                             | Pd max2                                        | Mounted on a specified circuit board.* | 1.05        | W    |

| CTL pin applied voltage     | V <sub>CTL</sub> max                           |                                        | 18          | V    |

| FG1,FG3 pin applied voltage | V <sub>FG</sub> 1 max<br>V <sub>FG</sub> 3 max |                                        | 18          | ٧    |

| Junction temperature        | Tj max                                         |                                        | 150         | °C   |

| Operating temperature       | Topr                                           |                                        | -40 to +105 | °C   |

| Storage temperature         | Tstg                                           |                                        | -55 to +150 | °C   |

## Allowable Operating range at Ta = 25°C

| Parameter                          | Symbol                               | Conditions | Ratings     | Unit |

|------------------------------------|--------------------------------------|------------|-------------|------|

| Supply voltage range               | VCC                                  |            | 9.5 to 16.5 | V    |

| 5V constant voltage output current | I <sub>REG</sub>                     |            | 10          | mA   |

| HB pin output current              | I <sub>HB</sub>                      |            | 30          | mA   |

| FG1,FG3 pin output current         | I <sub>FG</sub> 1, I <sub>FG</sub> 3 |            | 10          | mA   |

## **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 15V$

| Dovernator                        | Committee and         | Conditions                                            |           | Ratings   |          |       |

|-----------------------------------|-----------------------|-------------------------------------------------------|-----------|-----------|----------|-------|

| Parameter                         | Symbol                | Conditions                                            | min       | typ       | max      | Unit  |

| Supply current 1                  | I <sub>CC</sub> 1     |                                                       |           | 5.0       | 8.0      | mA    |

| Supply current 2                  | I <sub>CC</sub> 2     | At stop CTL ≤ 1.0V typ                                |           | 0         | 20       | μΑ    |

| Output Block                      |                       |                                                       |           |           |          |       |

| High level output voltage         | V <sub>HO</sub>       | I <sub>O</sub> = -10mA                                | VREG-0.35 | VREG-0.15 |          | ٧     |

| Low level output voltage          | V <sub>LO</sub>       | I <sub>O</sub> = 10mA                                 |           | 0.15      | 0.3      | V     |

| Lower output ON resistance        | R <sub>ON</sub> L     | I <sub>O</sub> = 10mA                                 |           | 15        | 30       | Ω     |

| Upper output ON resistance        | R <sub>ON</sub> H     | I <sub>O</sub> = -10mA                                |           | 15        | 35       | Ω     |

| Output leakage current            | l <sub>O</sub> leak   |                                                       |           |           | 10       | μА    |

| Minimum output pulse width        | Tmin                  |                                                       |           | 2.0       | 4.0      | μS    |

| Output minimum dead time          | Tdt                   |                                                       |           | 2.0       | 4.0      | μS    |

| 5V Constant Voltage Output        |                       |                                                       |           |           |          |       |

| Output voltage                    | VREG                  | I <sub>O</sub> = -5mA                                 | 4.7       | 5.0       | 5.3      | V     |

| Voltage fluctuation               | ΔV (REG1)             | V <sub>CC</sub> = 9.5 to 16.5V, I <sub>O</sub> = -5mA |           |           | 100      | mV    |

| Load fluctuation                  | ΔV (REG2)             | I <sub>O</sub> = -5 to -10mA                          |           |           | 100      | mV    |

| Hall Amplifier                    |                       |                                                       |           |           |          |       |

| Input bias current                | IB (HA)               |                                                       | -2        |           | 0        | μА    |

| Common-mode input voltage range 1 | VICM1                 | When a Hall element is used                           | 0.3       |           | VREG-1.7 | V     |

| Common-mode input voltage range 2 | VICM2                 | Single-sided input bias mode (when a Hall IC is used) | 0         |           | VREG     | V     |

| Hall input sensitivity            | VHIN                  | Sine wave, Hall element offset = 0V                   | 80        |           |          | mVp-p |

| Hysteresis width                  | ΔV <sub>IN</sub> (HA) |                                                       | 9         | 20        | 40       | mV    |

| Input voltage Low → High          | VSLH                  |                                                       | 5         | 11        | 19       | mV    |

| Input voltage High → Low          | VSHL                  |                                                       | -19       | -11       | -5       | mV    |

<sup>\*</sup> Specified circuit board : 114.3mm × 76.1mm × 1.6mm, glass epoxy

Note 1) Absolute maximum ratings represent the values that cannot be exceeded for any length of time.

Note 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for further details.

| C         | C    | 11        |       |

|-----------|------|-----------|-------|

| Continued | rrom | preceaing | nage. |

|           |      |           |       |

| Parameter                            | Symbol                         | Conditions                                           | Ratings |       |       | l leit |

|--------------------------------------|--------------------------------|------------------------------------------------------|---------|-------|-------|--------|

| Parameter                            | Symbol                         | Conditions                                           | min     | typ   | max   | Unit   |

| CSD Oscillator Circuit               |                                |                                                      |         |       |       |        |

| High level output voltage            | V <sub>OH</sub> (CSD)          |                                                      | 2.7     | 3.0   | 3.3   | V      |

| Low level output voltage             | V <sub>OL</sub> (CSD)          |                                                      | 0.8     | 1.0   | 1.2   | V      |

| Amplitude                            | V (CSD)                        |                                                      | 1.75    | 2.0   | 2.25  | Vp-p   |

| External capacitor charging current  | ICHG1 (CSD)                    | VCHG1 = 2.0V                                         | -17     | -10   | -4    | μΑ     |

| External capacitor discharging       | ICHG2 (CSD)                    | VCHG2 = 2.0V                                         | 4       | 10    | 17    | μΑ     |

| current                              |                                |                                                      |         |       |       |        |

| Oscillation frequency                | f (CSD)                        | C = 0.22μF (design target value)                     |         | 113.6 |       | Hz     |

| PWM Oscillator (PWM pin)             |                                | 1                                                    |         |       |       |        |

| High level output voltage            | V <sub>OH</sub> (PWM)          |                                                      | 3.3     | 3.5   | 3.8   | V      |

| Low level output voltage             | V <sub>OL</sub> (PWM)          |                                                      | 1.3     | 1.5   | 1.7   | V      |

| Amplitude                            | V (PWM)                        |                                                      | 1.78    | 2.0   | 2.22  | Vp-p   |

| Oscillation frequency                | f (PWM)                        | C = 2200pF, R = $15k\Omega$<br>(design target value) |         | 17    |       | kHz    |

| Current Limiter Operation            |                                |                                                      |         |       |       |        |

| Limiter voltage                      | VRF                            |                                                      | 0.225   | 0.25  | 0.275 | V      |

| Thermal Shutdown Protection Oper     | ation                          |                                                      |         |       |       | 1      |

| Thermal shutdown protection          | TSD                            | * Design target value                                | 150     | 175   |       | °C     |

| operating temperature                |                                | (junction temperature)                               |         |       |       |        |

| Hysteresis width                     | ΔTSD                           | * Design target value<br>(junction temperature)      |         | 35    |       | °C     |

| TH pin                               | -                              |                                                      | •       | •     |       |        |

| Protection start voltage             | VTH                            |                                                      | 0.25    | 0.6   | 1.05  | V      |

| Hysteresis width                     | ΔVTH                           |                                                      | 0.2     | 0.4   | 0.6   | V      |

| HB pin                               | <u> </u>                       | 1                                                    |         | I.    |       |        |

| Output ON resistance                 | R <sub>ON</sub> (HB)           | IHB = 10mA                                           |         | 15    | 30    | Ω      |

| Output leakage current               | I <sub>L</sub> (HB)            | Power saving mode V <sub>CC</sub> = 15V              |         |       | 10    | μΑ     |

| Low Voltage Protection Circuit (dete | ecting V <sub>CC</sub> voltage | )                                                    |         | I.    |       |        |

| Operation voltage                    | VSD                            |                                                      | 7.0     | 8.0   | 9.0   | V      |

| Hysteresis width                     | ΔVSD                           |                                                      | 0.25    | 0.5   | 0.75  | V      |

| FG1 FG3 Pin                          |                                |                                                      |         | 1     |       |        |

| Output ON resistance                 | R <sub>ON</sub> (FG)           | IFG = 5mA                                            |         | 40    | 60    | Ω      |

| Output leakage current               | IL (FG)                        | VFG = 18V                                            |         |       | 10    | μА     |

| CTL Amplifier (drive mode)           |                                |                                                      |         | 1     |       |        |

| Input voltage range                  | V <sub>IN</sub> (CTL)          |                                                      | 0       |       | VCC   | V      |

| High level input voltage             | V <sub>IH</sub> (CTL)          | PWM ON duty 90%                                      | 5.1     | 5.4   | 5.7   | V      |

| Middle level input voltage           | V <sub>IM</sub> (CTLI)         | PWM ON duty 0%                                       | 1.8     | 2.1   | 2.4   | V      |

| CTL Amplifier (power saving mode)    | 1 1141 /                       |                                                      | 1 1     |       |       |        |

| Low level input voltage              | V <sub>IL</sub> 1 (CTL)        | Power saving mode                                    |         | 1.0   | 1.5   | V      |

| Hysteresis width                     | ΔCTL                           | <u> </u>                                             | 0.15    | 0.5   | 0.85  | V      |

| Input current                        | I <sub>IH</sub> (CTLI)         | CTL = 3.5V                                           | 10      | 18    | 26    | μА     |

| F/R Pin                              | 11111-1-9                      |                                                      | 1 1     |       |       | r      |

| High level input voltage             | V <sub>IH</sub> (FR)           |                                                      | 3.0     |       | VREG  | V      |

| Low level input voltage              | V <sub>IL</sub> (FR)           |                                                      | 0       |       | 0.7   | V      |

| Input open voltage                   | V <sub>IO</sub> (FR)           |                                                      |         | 0     | 0.7   | V      |

| Hysteresis width                     | V <sub>IS</sub> (FR)           |                                                      | 0.21    | 0.31  | 0.41  | V      |

| High level input current             | I <sub>IH</sub> (FR)           | VF/R = VREG                                          | 10      | 50    | 100   | ν      |

| r namever mout cultett               | I IIH (FIZ)                    | I VI/IX = VICEG                                      | 10      | 30    | 100   | μΑ     |

Continued from preceding page.

| D                                       | 0                                                  | Conditions               | Ratings |      |      |      |  |  |

|-----------------------------------------|----------------------------------------------------|--------------------------|---------|------|------|------|--|--|

| Parameter                               | Symbol                                             | Symbol Conditions        |         | typ  | max  | Unit |  |  |

| FAULT Pin                               |                                                    |                          |         |      |      |      |  |  |

| Drive stop voltage                      | VFOF                                               |                          | 0       |      | 0.35 | V    |  |  |

| Drive start voltage                     | VFON                                               |                          | 3.0     |      | VREG | V    |  |  |

| Input open voltage                      | V <sub>IO</sub> (FLT)                              |                          | 4.6     | VREG |      | V    |  |  |

| High level input current                | I <sub>IH</sub> (FLT)                              | VFLT=VREG                |         | 0    | 10   | μА   |  |  |

| Low level input current                 | I <sub>IL</sub> (FLT)                              | VFLT=0V                  | -250    | -160 | -70  | μА   |  |  |

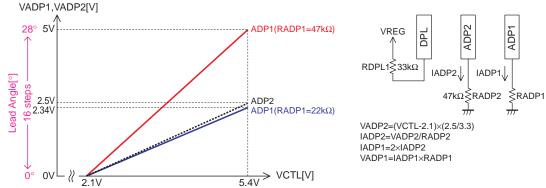

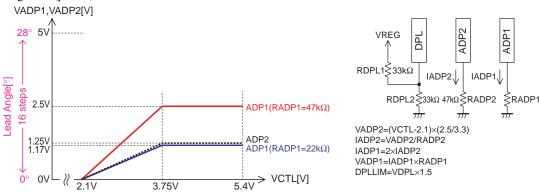

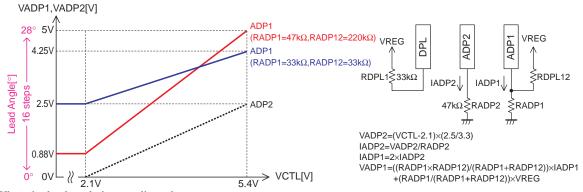

| ADP1 Pin (drive phase adjustment)       |                                                    | •                        |         |      |      |      |  |  |

| Minimum lead angle                      | Vadp01                                             | ADP1 pin = 0V            |         | 0    | 2    | Deg  |  |  |

| Maximum lead angle                      | Vadp16                                             | ADP1 pin = VREG          | 26      | 28   |      | Deg  |  |  |

| Current ratio with the ADP2 pin current | ADP                                                | CTL = 3.75V, IADP1/IADP2 | 1.45    | 2    | 2.55 | A/A  |  |  |

| ADP2 Pin (drive phase adjustment)       |                                                    | •                        |         |      |      |      |  |  |

| High level output voltage               | VADP2H                                             | CTL = 5.4V               | 1.95    | 2.5  | 3.05 | V    |  |  |

| Low level output voltage                | VADP2L                                             | CTL = 0V                 | 0       |      | 0.51 | V    |  |  |

| DPL Pin (drive-phase-adjustment lin     | DPL Pin (drive-phase-adjustment limit setting pin) |                          |         |      |      |      |  |  |

| Lead angle limit high level voltage     | VDPLH                                              |                          | 3.3     | 3.5  | 3.8  | V    |  |  |

| Lead angle limit low level voltage      | VDPLL                                              |                          | 1.3     | 1.5  | 1.7  | V    |  |  |

<sup>\*</sup> These are design target values and no measurements are made.

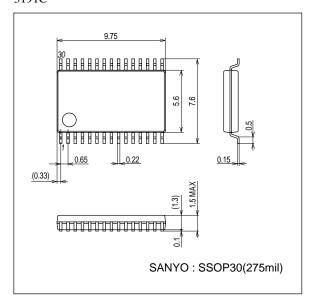

# **Package Dimensions**

unit : mm (typ) 3191C

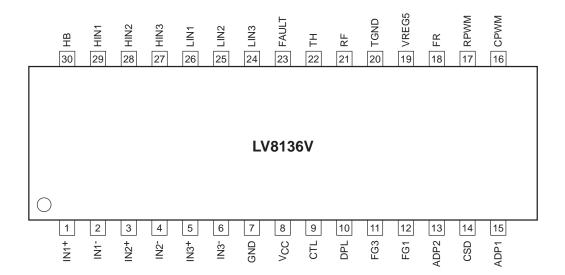

# **Pin Assignment**

Top view

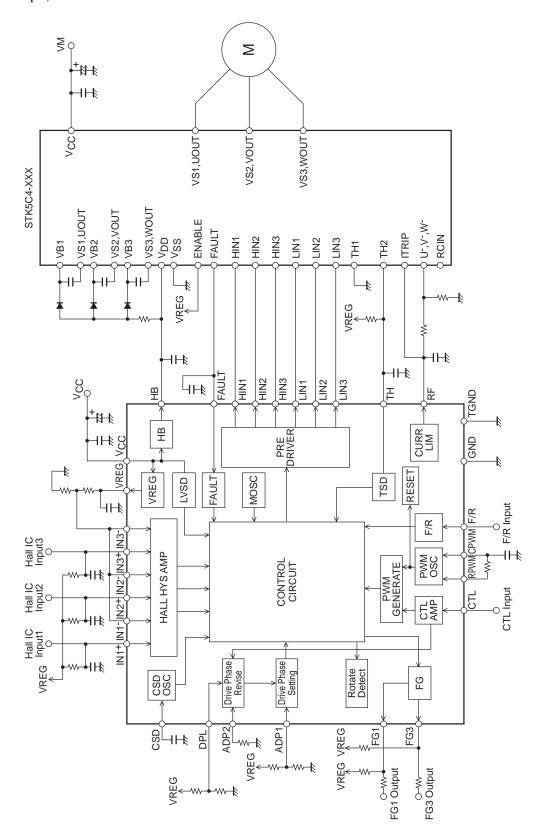

# Sample Application Circuit 1 (Hall element, HIC)

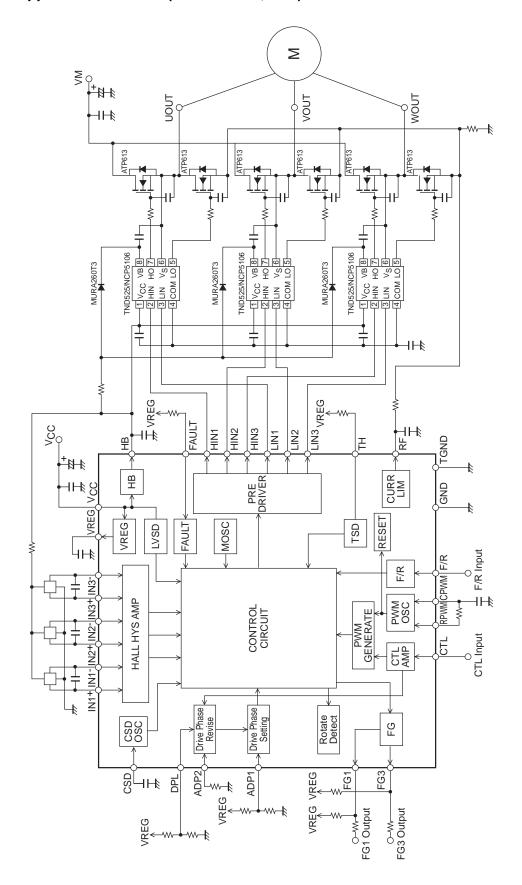

## Sample Application Circuit 2 (Hall IC, HIC)

Note: The Hall IC to be used must be of open collector or open drain type (no internal pull-up resistor connected to the output).

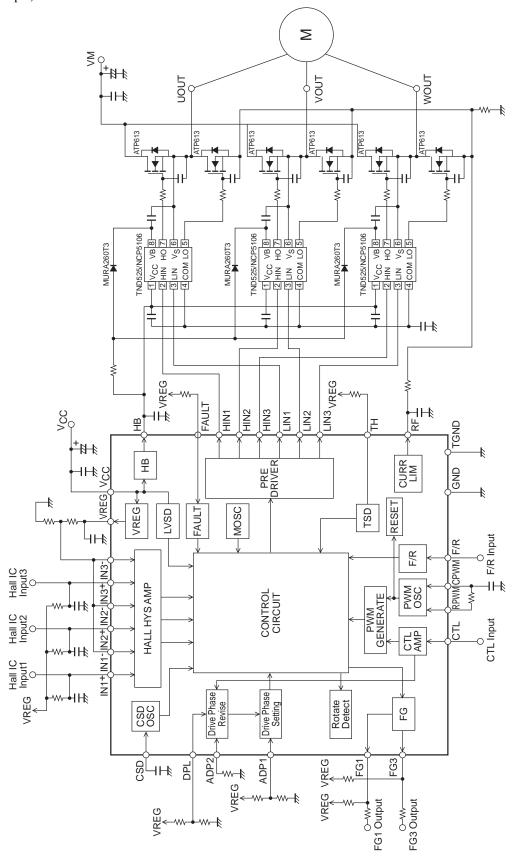

# Sample Application Circuit 3 (Hall element, FET)

## Sample Application Circuit 4 (Hall IC, FET)

Note: The Hall IC to be used must be of open collector or open drain type (no internal pull-up resistor connected to the output).

## **Pin Functions**

| Pin Fur               | Pin Name                             | Pin function                                                                                                                                                                                                                                                    | Equivalent Circuit                         |

|-----------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 1                     | IN1+                                 | Hall signal input pins.                                                                                                                                                                                                                                         | =quitaloin onoun                           |

| 2<br>3<br>4<br>5<br>6 | IN1-<br>IN2+<br>IN2-<br>IN3+<br>IN3- | The high state is when IN+ is greater than IN-, and the low state is the reverse.  An amplitude of at least 100mVp-p (differential) is desirable for the Hall signal inputs. If noise on the Hall signals                                                       | VREG                                       |

|                       |                                      | is a problem, insert capacitors between IN+ and IN- pins. If input is provided from a Hall IC, the common-mode input range can be expanded by biasing either + or                                                                                               | 1 3 5 500Ω<br>1 3 5 W 2 4 6                |

| 7                     | GND                                  | Ground pin of the control circuit block.                                                                                                                                                                                                                        |                                            |

| 8                     | VCC                                  | Power supply pin for control.  Insert a capacitor between this pin and ground to prevent the influence of noise, etc.                                                                                                                                           |                                            |

| 9                     | CTL                                  | Control input pin. When CTL pin voltage rises, the IC changes the output signal PWM duty to increase the torque output.                                                                                                                                         | VREG $V_{CC}$ $65k\Omega$ $9$ $125k\Omega$ |

| 10                    | DPL                                  | Setting pin for drive phase adjustment limit.  This pin is used to limit the lead angle of the drive phase. The lead angle is limited to zero degrees when the voltage is 1.5V or lower and the limit is released when the voltage is 3.5V or higher.           | VREG 500Ω 10                               |

| 11 12                 | FG3<br>FG1                           | FG3: 3-Hall FG signal output pin. 8-pole motor outputs 12 FG pulses per one rotation. In power saving mode, high-level is output.  FG1:1-Hall FG signal output pin. 8-pole motor outputs 4 pulses per one rotation. In power saving mode, high-level is output. | VREG (1) (12) 25Ω \$                       |

| Pin No. | m preceding page. Pin Name | Pin function                                                                                                                                                                                                        | Equivalent Circuit                   |

|---------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 13      | ADP2                       | Setting pin for phase drive correction. This pin sets the amount of correction made to the lead angle according to the CTL input. Insert a resistor between this pin and ground to adjust the amount of correction. | VREG<br>VREG<br>VREG<br>500Ω<br>13   |

| 14      | CSD                        | Pin to set the operating time of the motor constraint protection circuit.  Insert a capacitor between this pin and ground. This pin must be connected to ground if the constraint protection circuit is not used.   | VREG 500Ω 14                         |

| 15      | ADP1                       | Drive phase adjustment pin. The drive phase can be advanced from 0 to 28 degrees during 150-degree current carrying drive. The lead angle becomes 0 degrees when 0V is input and 28 degrees when 5V is input.       | V <sub>CC</sub> VREG  AD 500Ω  AD 15 |

| 16      | CPWM                       | Triangle wave oscillation pin for PWM generation.  Insert a capacitor between this pin and ground and a resistor between this pin and RPWM for triangle wave oscillation.                                           | VREG 200Ω 16                         |

| 17      | RPWM                       | Oscillation pin for PWM generation. Insert a resistor between this pin and CPWM.                                                                                                                                    | VREG 17                              |

Continued from preceding page.

|         | n preceding page. | 1                                                                                                                                                                                                                |                          |

|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Pin No. | Pin Name          | Pin function                                                                                                                                                                                                     | Equivalent Circuit       |

| 18 20   | FR<br>TGND        | FR Forward/reverse rotation setting pin. A low-level specifies forward rotation and a high-level specifies reverse rotation. This pin is held low when open.  TGND Test pin. Connect this pin to ground.         | VREG  2kΩ  18(20)  100kΩ |

| 19      | VREG5             | 5V regulator output pin (control circuit power supply). Insert a capacitor between this pin and ground for power stabilization. 0.1μF or so is desirable.                                                        | VCC<br>50Ω \$ 19         |

| 21      | RF                | Output current detection pin. This pin is used to detect the voltage across the current detection resistor (Rf). The maximum output current is determined by the equation I <sub>OUT</sub> = 0.25V/Rf.           | VREG 5kΩ 21              |

| 22      | TH                | Thermistor connection pin. The thermistor detects heat generated from HIC and turns off the drive output when an overheat condition occurs. If the pin voltage is 0.6V or lower, the drive output is turned off. | VREG 500Ω 222            |

| Pin No.                          | Pin Name                                     | Pin function                                                                                                                                                                                                                                                                               | Equivalent Circuit              |

|----------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 23                               | FAULT                                        | HIC protection signal input pin. This pin accepts an error mode detection signal generated by the HIC side. A low-level indicates that an error mode is detected and turns off the drive output.                                                                                           | VREG \$30kΩ \$500Ω 23           |

| 24<br>25<br>26<br>27<br>28<br>29 | LIN3<br>LIN2<br>LIN1<br>HIN3<br>HIN2<br>HIN1 | LIN1, LIN2, and LIN3: L-side output pins. Generate 0 to VREG5 push-pull outputs.  HIN1, HIN2, and HIN3: H-side output pins. Generate 0 to VREG5 push-pull outputs.                                                                                                                         | VREG  (25)(27)(29) (24)(26)(28) |

| 30                               | НВ                                           | Hall bias HIC power supply pin. Insert a capacitor between this pin and ground. This pin is set to high-impedance state in power saving mode. By supplying Hall bias and HIC power using this pin, the power consumption by Hall bias and HIC in power saving mode can be reduced to zero. | Vcc                             |

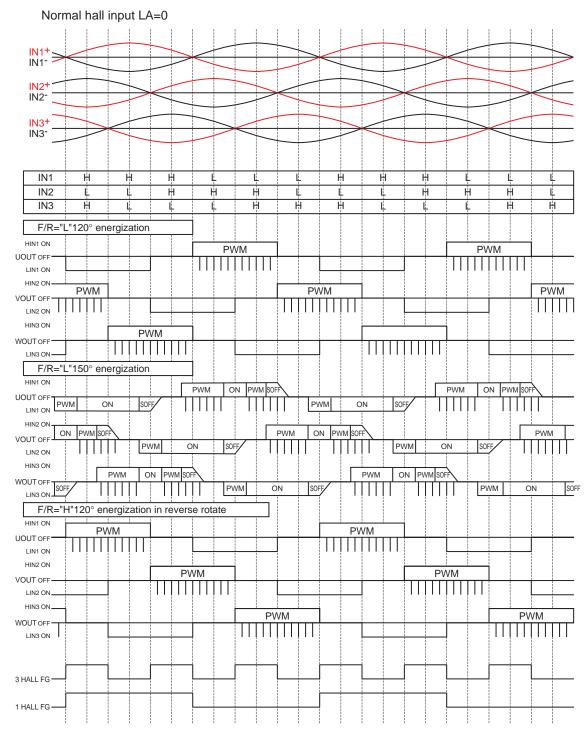

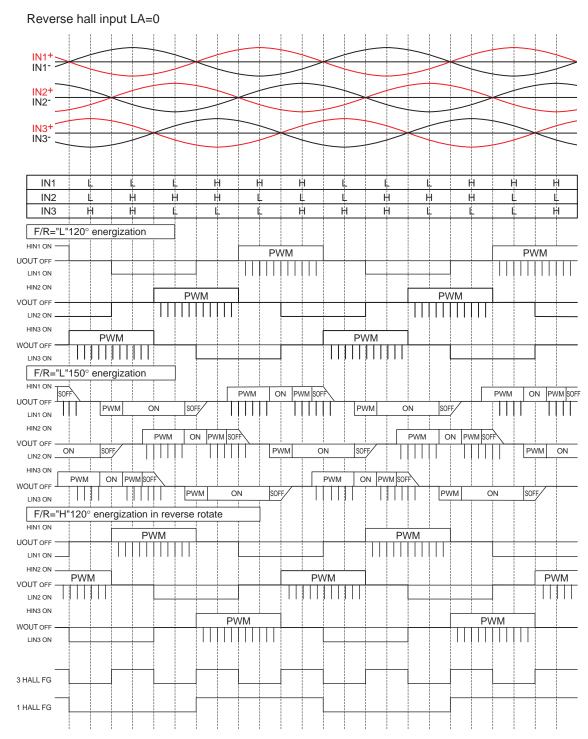

**Timing Chart** (IN = "H"indicates the state in which IN+ is greater than IN-.)

(1) F/R pin = L

The energization is switched to 120° when 3 Hall FG frequency is 6.1Hz (TYP) or lower A direction of rotation is detected from Hall signal according to F/R pin input If the motor rotates in reverse against F/R pin input, 120° energization is maintained forcibly.

## (2) F/R pin = H

The energization is switched to 120° when 3 Hall FG frequency is 6.1Hz (TYP) or lower A direction of rotation is detected from Hall signal according to F/R pin input If the motor rotates in reverse against F/R pin input, 120° energization is maintained forcibly.

## **Functional Description**

- Basic operation of 120-degree ⇔ 150-degree current-carrying switching

At startup, this IC starts at 120-degree current-carrying. The current-carrying is switched to 150 degrees when the 3-Hall

FG frequency is 6.1Hz (typ) or above and the rising edge of the IN2 signal has been detected twice in succession.

- Concerning the Hall signal input sequence

This IC controls the motor rotation direction commands and Hall signal input sequence in order to set the lead angle. If the motor rotation direction commands and Hall signal input sequence do not conform to what is shown on the timing chart, the motor is driven by 120-degree current-carrying.

Example 1: When the Hall signal has been input with the following logic

When F/R pin input is high  $\rightarrow$  120-degree current-carrying

When F/R pin input is low  $\rightarrow$  150-degree current-carrying

Example 2: When the Hall signal has been input with the following logic

When F/R pin input is high  $\rightarrow$  150-degree current-carrying

When F/R pin input is low  $\rightarrow$  120-degree current-carrying

- CTL pin input

- a) Power-saving mode  $V_{CTL} < V_{IL} (1.0V : typ)$

When the CTL pin voltage is lower than  $V_{IL}$  (1.0V: typ), the IC enters the power-saving mode, and the following are set:

- $\bullet$  L<sub>IN</sub>1 to L<sub>IN</sub>3 and H<sub>IN</sub>1 to H<sub>IN</sub>3 outputs all set to low

- $I_{CC} = 0$ , HB pin = OFF

The power consumption of the IC can now be set to 0, and the power consumption of the Hall element connected to the HB pin and the output block can also be set to 0.

b) Standby mode  $V_{IL} < V_{CTL} < V_{IM} (2.1V : typ)$

When the CTL pin voltage is  $V_{IL} < V_{CTL} < V_{IM}$ , the IC enters the standby mode. Low is output for the  $U_{IN}1$  to  $U_{IN}3$  outputs and bootstrap charge pulses (2 $\mu$ s pulse width: design target) are output to the  $U_{IN}1$  to  $U_{IN}3$  outputs to prepare for drive start.

c) Drive mode  $V_{IM} < V_{CTL} < V_{IH} (5.4V : typ)$

When the CTL pin voltage is  $V_{IM} < V_{CTL} < V_{IH}$ , the IC enters the drive mode, and the motor is driven at the PWM duty ratio corresponding to  $V_{CTL}$ . When  $V_{CTL}$  is increased, the PWM duty ratio increases, and the maximum duty ratio (\*90%: typ) is reached at  $V_{IH}$ .

- \* When the PWM oscillation frequency setting is 17kHz.

- d) Test mode  $8V < V_{CTL} < V_{CTL} \max (design target)$

When the CTL pin voltage is 8V or higher, the IC enters the test mode, and the motor is driven at the 120-degree current-carrying and maximum duty ratio.

- The CTL pin is pulled down by  $190k\Omega$ : typ inside the IC. Caution is required when the control input voltage input is subjected to resistance division, for example.

- Bootstrap capacitor initial charging mode

When the mode is switched from the power-saving mode to the standby mode and then to the drive mode, the IC enters the bootstrap capacitor charging mode (UH, VH, WH pins = L UL, VL, WL pins = H 3.84ms typ) in order to charge the bootstrap capacitor.

## • Drive phase adjustment

During 150-degree current-carrying drive, current-carrying is started from the phase that is 15 degrees ahead of the 120-degree current-carrying. From this state, any lead angle from 0 to 28 degrees can be set using the ADP1 pin voltage (lead angle control). This setting can be adjusted in 16 steps (in 1.875-degree increments) from 0 to 28 degrees using the ADP1 pin voltage, and it is updated every Hall signal cycle (it is sampled at the rising edge of the IN3 input and updated at its falling edge).

A number of lead angle adjustments proportionate to the CTL pin voltage can be undertaken by adjusting the resistance levels of resistors connected to the ADP1 pin, ADP2 pin and DPL pin. When these pins are not going to be used, reference must be made to section 4.5, and the pins must not be used in the open status. Furthermore, a resistance of  $47k\Omega$  or more must be used for the resistor (RADP2) that is connected to the ADP2 pin.

1. The slopes of V<sub>CTL</sub> and VADP1 can be adjusted by setting the resistance level of the resistor (RADP1) connected to ADP1 (pin 15).

2. The ADP2 pin rise can be halted (a limit on the lead angle adjustment can be set by means of the CTL voltage) by setting DPL (pin 10).

3. The offset and slope can be adjusted as desired by setting RADP1 and RADP12 of ADP1 (pin 15). (It is also possible to set a limit on the lead angle adjustment by means of the CTL voltage by setting DPL.)

- 4. When the lead angle is not adjusted

- ADP1 pin: shorted to ground; ADP2 pin and DPL pin: pulled down to ground using the resistors

- 5. When the lead angle is not adjusted by means of the CTL pin voltage (for use with a fixed lead angle) ADP1 pin: lead angle setting by resistance division from VREG; ADP2 pin and DPL pin: pulled down to ground by the resistors

## **Description of LV8136V**

### 1. Current Limiter Circuit

The current limiter circuit limits the output current peak value to a level determined by the equation  $I = V_{RF}/Rf$  (where  $V_{RF} = 0.25V$  typ, Rf is the value of the current detection resistor). The current limiter operates by reducing the output on duty to suppress the current.

The current limiter circuit detects the reverse recovery current of the diode due to PWM operation. To assure that the current limiting function does not malfunction, its operation has a delay of approx. 1µs. If the motor coils have a low resistance or a low inductance, current fluctuation at startup (when there is no back electromotive force in the motor) will be rapid. The delay in this circuit means that at such times the current limiter circuit may operate at a point well above the set current. Application must take this increase in the current due to the delay into account when the current limiter value is set.

### 2. Power Saving Circuit (CTL pin)

This IC goes into the power saving mode that stops operation of all the circuits to reduce the power consumption. If the HB pin is used for the Hall element bias and the output block, the current consumption in the power-saving mode is zero.

## 3. Hall Input Signal

Signals with an amplitude in excess of the hysteresis is required for the Hall inputs. However, considering the influence of noise and phase displacement, an amplitude of over 100mV is desirable.

If noise disrupts the output waveform (at phase change), this must be prevented by inserting capacitors or other devices across the Hall inputs. The constraint protection circuit uses the Hall inputs to discriminate the motor constraint state. Although the circuit is designed to tolerate a certain amount of noise, care is required.

If all three phases of the Hall input signal go to the same input state (HHH or LLL), the outputs are all set to the off state.

If the outputs from a Hall IC are used, fixing one side of the inputs (either the + or –side) at a voltage within the common-mode input voltage range (0.3V to VREG-1.7V) allows the other input side to be used as an input over the 0V to VREG range.

#### 4. Constraint Protection Circuit

This IC goes into the power saving mode that stops operation of all the circuits to reduce the power consumption. If the HB pin is used for the Hall element bias and the output block, the current consumption in the power-saving mode is zero.

This IC provides an on-chip constraint protection circuit to protect the IC itself and the motor when the motor is constrained.

If the Hall input signals do not change for over a fixed period when the motor is in operation, this circuit operates. Also, the upper-side output transistor is turned off while the constraint protection circuit is operating. This time is determined by the capacitance of the capacitor connected to the CSD pin.

Set time (in seconds)  $\approx 90 \times C (\mu F)$

If a 0.022μF capacitor is used, the protection time will be about 2.0 seconds.

The set time must be selected to have an adequate margin with respect to the motor startup time

Conditions to clear the constraint protection state:

CTL pin when a low-level voltage is input  $\rightarrow$  Release protection and reset count

When TSD protection is detected  $\rightarrow$  Stop count

#### 5. Power Supply Stabilization

Since this IC adopts a switching drive technique, the power-supply line level can be disrupted easily. Thus capacitors large enough to stabilize the power supply voltage must be inserted between the  $V_{CC}$  pins and ground. If the electrolytic capacitors cannot be connected close to their corresponding pins, ceramic capacitors of about  $0.1\mu F$  must be connected near these pins.

If diodes are inserted in the power-supply line to prevent destruction of the device when the power supply is connected with reverse polarity, the power supply line levels will be even more easily disrupted, and even larger capacitors must be used.

#### 6. VREG Stabilization

A capacitor of at least  $0.1\mu F$  must be used to stabilize the VREG voltage, which is the control circuit power supply. The ground lead of that capacitor must be located as close as possible to the control system ground (SGND) of the IC.

## 7. Forward/Reverse Switching (F/R pin)

Switching between forward rotation and reverse rotation must not be undertaken while the motor is running.

#### 8. TH Pin

The TH pin must normally be pulled up to the 5V regulator for use. When it has been set to low, the outputs of  $L_{IN}1$ ,  $L_{IN}2$  and  $L_{IN}3$  as well as  $H_{IN}1$ ,  $H_{IN}2$  and  $H_{IN}3$  are low.

### 9. FAULT Pin

The FAULT pin must normally be pulled up to the 5V regulator for use. When it has been set to low, the outputs of L<sub>IN</sub>1, L<sub>IN</sub>2 and L<sub>IN</sub>3 as well as H<sub>IN</sub>1, H<sub>IN</sub>2 and H<sub>IN</sub>3 are low.

### 10. PWM Frequency Setting

$fCPWM \approx 1/(1.78CR)$

Components with good temperature characteristics must be used.

An oscillation frequency of about 17kHz is obtained when a 2200pF capacitor and  $15k\Omega$  resistor are used. If the PWM frequency is too low, switching noise will be heard from the motor; conversely, if it is too high, the output power loss will increase. For this reason, a frequency between 15kHz and 30kHz or so is desirable. The capacitor ground must be connected as close as possible to the control system ground (SGND pin) of the IC to minimize the effects of the outputs.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of February, 2012. Specifications and information herein are subject to change without notice.