# 1:9 DIFFERENTIAL CLOCK DRIVER WITH ENABLE

#### **FEATURES**

- **■** Low skew

- Extended 100E VEE range of -4.2V to -5.5V

- **■** Guaranteed skew limits

- Differential design

- **■** VBB output

- **■** Enable input

- Fully compatible with industry standard 10KH, 100K I/O levels

- 75K $\Omega$  input pulldown resistors

- Fully compatible with Motorola MC10E/100E111

- Available in 28-pin PLCC package

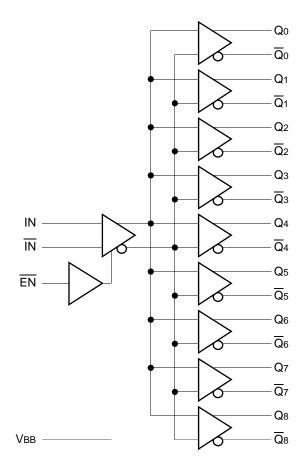

# **BLOCK DIAGRAM**

#### **DESCRIPTION**

The SY10/100E111 are low skew 1-to-9 differential drivers designed for clock distribution in new, high-performance ECL systems. They accept one differential or single-ended input, with VBB used for single-ended operation. The signal is fanned out to nine identical differential outputs. An enable input is also provided such that a logic HIGH disables the device by forcing all Q outputs LOW and all  $\overline{\rm Q}$  outputs HIGH.

The device is specifically designed and produced for low skew. The interconnect scheme and metal layout are carefully optimized for minimal gate-to-gate skew within the device. Wafer characterization and process control ensure consistent distribution of propagation delay from lot to lot. Since the E111 shares a common set of "basic" processing with the other members of the ECLinPS family, wafer characterization at the point of device personalization allows for tighter control of parameters, including propagation delay.

To ensure that the skew specification is met, it is necessary that both sides of the differential output are terminated into  $50\Omega$ , even if only one side is being used. In most applications, all nine differential pairs will be used and, therefore, terminated. In the case where fewer than nine pairs are used, it is necessary to terminate at least the output pairs on the same package side (i.e. sharing the same Vcco as the pair(s) being used on that side) in order to maintain minimum skew.

The VBB output is intended for use as a reference voltage for single-ended reception of ECL signals to that device only. When using VBB for this purpose, it is recommended that VBB is decoupled to VCC via a  $0.01\mu F$  capacitor.

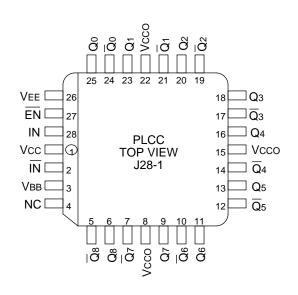

## **PIN CONFIGURATION**

# **PIN NAMES**

| Pin                                       | Function                |

|-------------------------------------------|-------------------------|

| IN, ĪN                                    | Differential Input Pair |

| ĒN                                        | Enable Input            |

| Q0, $\overline{Q}0$ — Q8, $\overline{Q}8$ | Differential Outputs    |

| Vвв                                       | Vвв Output              |

| Vcco                                      | Vcc to Output           |

## DC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

|        |                    |      | TA = 0°C |      | TA = +25°C |       |      | TA = +85°C |       |      |       |      |           |

|--------|--------------------|------|----------|------|------------|-------|------|------------|-------|------|-------|------|-----------|

| Symbol | Parameter          |      | Min.     | Тур. | Max.       | Min.  | Тур. | Max.       | Min.  | Тур. | Max.  | Unit | Condition |

| Vвв    | Output Reference   |      |          |      |            |       |      |            |       |      |       | ٧    | _         |

|        | Voltage            | 10E  | -1.38    | _    | -1.27      | -1.35 | _    | -1.25      | -1.31 | _    | -1.19 |      |           |

|        |                    | 100E | -1.38    | -    | -1.26      | -1.38 | _    | -1.26      | -1.38 | _    | -1.26 |      |           |

| Іін    | Input HIGH Current |      | _        |      | 150        | _     | _    | 150        |       | _    | 150   | μΑ   |           |

| IEE    | Power Supply       |      |          |      |            |       |      |            |       |      |       | mA   | _         |

|        | Current            | 10E  | _        | 48   | 60         |       | 48   | 60         | _     | 48   | 60    |      |           |

|        |                    | 100E | _        | 48   | 60         |       | 48   | 60         | _     | 55   | 69    |      |           |

#### TIMING DIAGRAMS IN -IN -ĪN -ĪN -ĪN ► ts ◄ EN . EN -50% $\overline{\mathsf{EN}}$ 75 mV 75 mV Q Q-**A** 75 mV 75 mV Figure 1. Set-up Time Figure 2. Hold Time Figure 3. Release Time

## **AC ELECTRICAL CHARACTERISTICS**

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

|              |                                                                                | TA = 0°C                 |      | TA = +25°C               |                          |      | TA = +85°C               |                          |      |                          |      |                            |

|--------------|--------------------------------------------------------------------------------|--------------------------|------|--------------------------|--------------------------|------|--------------------------|--------------------------|------|--------------------------|------|----------------------------|

| Symbol       | Parameter                                                                      | Min.                     | Тур. | Max.                     | Min.                     | Тур. | Max.                     | Min.                     | Тур. | Max.                     | Unit | Condition <sup>(1-9)</sup> |

| tPLH<br>tPHL | Propagation Delay to Output IN (differential) IN (single-ended) Enable Disable | 430<br>330<br>450<br>450 |      | 630<br>730<br>850<br>850 | 430<br>330<br>450<br>450 |      | 630<br>730<br>850<br>850 | 430<br>330<br>450<br>450 |      | 630<br>730<br>850<br>850 | ps   | 1<br>2<br>3<br>3           |

| tskew        | Within-Device Skew                                                             | _                        | 25   | 50                       | _                        | 25   | 50                       | _                        | 25   | 50                       | ps   | 4                          |

| ts           | Set-up Time, EN to IN                                                          | 200                      | 0    | _                        | 200                      | 0    | _                        | 200                      | 0    | _                        | ps   | 5                          |

| tH           | Hold Time, IN to EN                                                            | 0                        | -200 | _                        | 0                        | -200 | _                        | 0                        | -200 | _                        | ps   | 6                          |

| tR           | Release Time, EN to IN                                                         | 300                      | 100  | _                        | 300                      | 100  | _                        | 300                      | 100  | _                        | ps   | 7                          |

| VPP          | Minimum Input Swing                                                            | 250                      | _    | _                        | 250                      | _    | _                        | 250                      | _    | _                        | mV   | 8                          |

| VCMR         | Common Mode Range                                                              | -1.6                     |      | -0.4                     | -1.6                     | _    | -0.4                     | -1.6                     | _    | -0.4                     | V    | 9                          |

| tr<br>tf     | Rise/Fall Times<br>20% to 80%                                                  | 275                      | 375  | 600                      | 275                      | 375  | 600                      | 275                      | 375  | 600                      | ps   | _                          |

#### NOTES:

- 1. The differential propagation delay is defined as the delay from the crossing points of the differential input signals to the crossing point of the differential output signals.

- 2. The single-ended propagation delay is defined as the delay from the 50% point of the input signal to the 50% point of the output signal.

- 3. Enable is defined as the propagation delay from the 50% point of a **negative** transition on  $\overline{EN}$  to the 50% point of a **positive** transition on Q (or a negative transition on  $\overline{Q}$ ). Disable is defined as the propagation delay from the 50% point of a **positive** transition on  $\overline{EN}$  to the 50% point of a **negative** transition on Q (or a positive transition on  $\overline{Q}$ ).

- 4. The within-device skew is defined as the worst case difference between any two similar delay paths within a single device.

- 5. The set-up time is the minimum time that EN must be asserted prior to the next transition of IN/IN to prevent an output response greater than ±75mV to that IN/IN transition (see Figure 1).

- 6. The hold time is the minimum time that  $\overline{\text{EN}}$  must remain asserted after a negative going IN or a positive going  $\overline{\text{IN}}$  to prevent an output response greater than  $\pm 75\text{mV}$  to that  $\overline{\text{IN/IN}}$  transition (see Figure 2).

- 7. The release time is the minimum time that  $\overline{\text{EN}}$  must be de-asserted prior to the next  $\overline{\text{IN/IN}}$  transition to ensure an output response that meets the specified IN to Q propagation delay and output transition times (see Figure 3).

- 8. VPP (min.) is defined as the minimum input differential voltage which will cause no increase in the propagation delay. The VPP (min.) is AC limited for the E111, as a differential input as low as 50mV will still produce full ECL levels at the output.

- 9. VCMR is defined as the range within which the VIH level may vary, with the device still meeting the propagation delay specification. The VIL level must be such that the peak-to-peak voltage is less than 1.0V and greater than or equal to VPP (min.).

#### PRODUCT ORDERING CODE

| Ordering<br>Code | Package<br>Type | Operating<br>Range |

|------------------|-----------------|--------------------|

| SY10E111JC       | J28-1           | Commercial         |

| SY10E111JCTR     | J28-1           | Commercial         |

| SY100E111JC      | J28-1           | Commercial         |

| SY100E111JCTR    | J28-1           | Commercial         |

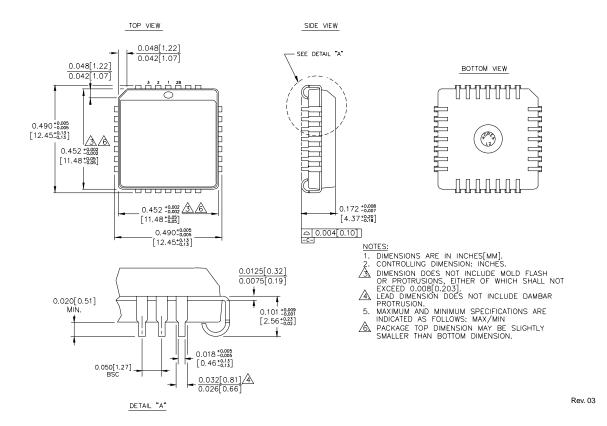

# 28 LEAD PLCC (J28-1)

MICREL-SYNERGY 3250 SCOTT BOULEVARD SANTA CLARA CA 95054 USA

TEL + 1 (408) 980-9191 FAX + 1 (408) 914-7878 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 2000 Micrel Incorporated