# Frequency Generator for Pentium™ Based Systems

## **General Description**

The ICS9169C-232 is a low-cost frequency generator designed specifically for Pentium and Pentium-Pro based chip set systems. The integrated buffer minimizes skew and provides all the clocks required. A 14.318 MHz XTAL oscillator provides the reference clock to generate standard Pentium frequencies. The CPU clock makes gradual frequency transitions without violating the PLL timing of internal microprocessor clock multipliers. A raised frequency setting of 68.5 MHz is available for Turbo-mode of the 66.8 MHz CPU. The ICS9169C-232 contains 8 CPU clocks, 6 PCI clocks, 1 REF at 48MHz and 1 at 24MHz.

Either synchronous (CPU/2) or asynchronous (32 MHz) PCI bus operation can be selected by latching data on BSEL input.

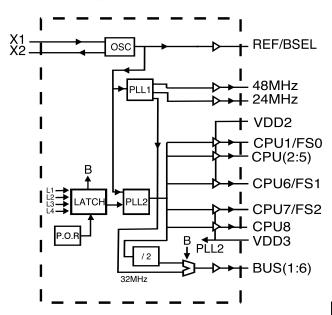

# **Block Diagram**

VDD Groups:

Latched Inputs:

VDD1 = X1, X2, REF/BSEL

L1 = BSEL

VDD2 = CPU1-6

L2 = FS0

VDD3 = CPU7-8 & PLL Core L3 = FS1 VDD4 = BUS1-6 L4 = FS2

VDD5 = 48/24 MHz

#### **Features**

- Strong output drive.

- Eight selectable CPU clocks operate up to 83.3 MHz

- Frequency selections include Turbo-mode speed of 68.5 MHz

- Maximum CPU jitter of ±200ps

- Six BUS clocks support sync or async bus operation

- 250ps skew window for CPU outputs, 500ps skew window for BUS outputs

- CPU clocks to BUS clocks skew 1-4 ns (CPU early)

- 48 MHz clock for USB support & 24 MHz clock for FD.

- Logic inputs latched at Power-On for frequency selection saving pins as Input/Output

- Integrated buffer outputs drive up to 30pF loads

- 3.0V 3.7V supply range, CPU (1:6) outputs 2.5V (2.375 2.6V) VDD option

- 28-pin SOIC or SSOP package

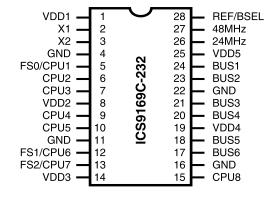

# **Pin Configuration**

28-Pin SOIC or SSOP

# **Functionality**

$3.3V\pm10\%$ ,  $0-70^{\circ}C$ Crystal (X1, X2) = 14.31818 MHz

| ADDRESS<br>SELECT |     |     | CPU(1:8)<br>(MHz) | BUS (1 | :6)MHz | 18MU2   | 24MHz   | REF |

|-------------------|-----|-----|-------------------|--------|--------|---------|---------|-----|

| FS2               | FS1 | FS0 |                   | BSEL=1 | BSEL=0 | 4011112 | 24.1112 | KL1 |

| 0                 | 0   | 0   | 50                | 25     | 32     | 48      | 24      | REF |

| 0                 | 0   | 1   | 60                | 30     | 32     | 48      | 24      | REF |

| 0                 | 1   | 0   | 66.8              | 33.4   | 32     | 48      | 24      | REF |

| 0                 | 1   | 1   | 75.9              | 32     | 32     | 48      | 24      | REF |

| 1                 | 0   | 0   | 55                | 27.5   | 32     | 48      | 24      | REF |

| 1                 | 0   | 1   | 75.9              | 37.5   | 32     | 48      | 24      | REF |

| 1                 | 1   | 0   | 83.3              | 41.7   | 32     | 48      | 24      | REF |

| 1                 | 1   | 1   | 68.5              | 34.25  | 32     | 48      | 24      | REF |

Pentium is a trademark of Intel Corporation

9169C-232RevB031897

ICS reserves the right to make changes in the device data identified in this publication without further notice. ICS advises its customers to obtain the latest version of all device data to verify that any information being relied upon by the customer is current and accurate.

# ICS169C-232

# **Pin Descriptions**

| PIN NUMBER         | PIN NAME            | TYPE | DESCRIPTION                                                                                                                                                                                                                                 |

|--------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | VDD1                | PWR  | Power for control logic and crystal oscillator circuit and 14.318 MHz output                                                                                                                                                                |

| 2                  | X1                  | IN   | XTAL or external reference frequency input. This input includes XTAL load capacitance and feedback bias for a 12-16MHz crystal, nominally 14.31818MHz. External crystal load of 30pF to GND recommended for VDD power on faster than 2.0ms. |

| 3                  | X2                  | OUT  | XTAL output which includes XTAL load capacitance. External crystal load of 10pF to GND recommended for VDD power on faster than 2.0ms.                                                                                                      |

| 4,11,16,22         | GND                 | PWR  | Ground for control logic.                                                                                                                                                                                                                   |

| 6,7,9,10,15        | CPU(2,3,4,5,8)      | OUT  | Processor clock outputs which are a multiple of the input reference clock as shown in the preceding table.                                                                                                                                  |

| 5,12,13            | CPU1, CPU6,<br>CPU7 | OUT  | Processor clock outputs which are a multiple of the input reference clock as shown in the preceding table.                                                                                                                                  |

| 5,12,13            | FS (0:2)            | IN   | Frequency multiplier select pins. See shared pin programming description later in this data sheet for further explanation. 350K* internal pull up.                                                                                          |

| 8                  | VDD2                | PWR  | Power for CPU (1:6) clock buffers only. This VDD supply can be reduced to 2.5V for CPU (1:6) outputs.                                                                                                                                       |

| 14                 | VDD3                | PWR  | Power for CPU (7:8) clock buffers and internal PLL and Core logic. Must be nominal 3.3V (3.0 to 3.7V)                                                                                                                                       |

| 17,18,20,21,23, 24 | BUS(1:6)            | OUT  | BUS clock outputs which are a multiple of the input reference clock as shown in the preceding table.                                                                                                                                        |

| 19                 | VDD4                | PWR  | Power for BUS clock buffers BUS (1;6)                                                                                                                                                                                                       |

| 25                 | VDD5                | PWR  | Power for fixed clock buffer (48 MHz, 24 MHz)                                                                                                                                                                                               |

| 26                 | 24 MHz              | OUT  | Fixed 24 MHz clock (assuming a 14.31818 MHz REF frequency).                                                                                                                                                                                 |

| 27                 | 48 MHz              | OUT  | Fixed 48 MHz clock (assuming a 14.31818 MHz REF frequency).                                                                                                                                                                                 |

| 28                 | REF                 | OUT  | Fixed 14.31818 MHz clock (assuming a 14.31818 MHz REF frequency).                                                                                                                                                                           |

| 20                 | BSEL                | IN   | Selection for synchronous or asynchronous bus clock operation. 350K* internal pull up.                                                                                                                                                      |

<sup>\*</sup> The internal pull up will vary from 350K  $\,$  to 500K based on temperature

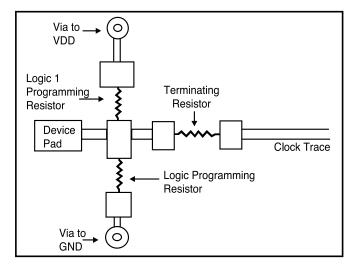

# Shared Pin Operation - Input/Output Pins

Shared Pin Operation - Input/Output, Pins 5, 28, 12 and 13 on the **ICS9169C-232** serve as dual signal functions to the device. During initial power-up, they act as input pins. The logic level (voltage) that is present on these pins at this time is read and stored into a 4-bit internal data latch. At the end of Power-On reset, (see AC characteristics for timing values), the device changes the mode of operations for these pins to an output function. In this mode the pins produce the specified buffered clocks to external loads.

To program (load) the internal configuration register for these pins, a resistor is connected to either the VDD (logic 1) power supply or the GND (logic 0) voltage potential. A 10 Kilohm(10K) resistor is used to provide both the solid CMOS programming voltage needed during the power-up programming period and to provide an insignificant load on the output clock during the subsequent operating period.

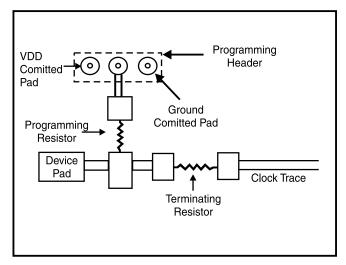

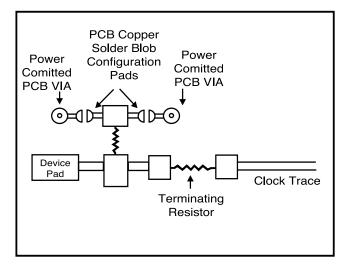

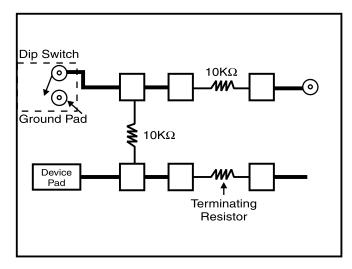

Figs. 1 and 2 show the recommended means of implementing this function. In Fig. 1 either one of the resistors is loaded onto the board (selective stuffing) to configure the device's internal logic. Figs. 2a and b provide a single resistor loading option where either solder spot tabs or a physical jumper header may be used.

These figures illustrate the optimal PCB physical layout options. These configuration resistors are of such a large ohmic value that they do not effect the low impedance clock signals. The layouts have been optimized to provide as little impedance transition to the clock signal as possible, as it passes through the programming resistor pad(s).

## **Test Mode Operation**

The ICS9169C-232 includes a production test verification mode of operation. This requires that the FS0 and FS1 pins be programmed to a logic high and the FS2 pin be programmed to a logic low(see Shared Pin Operation section). In this mode the device will output the following frequencies.

| P          | Frequency |       |  |  |

|------------|-----------|-------|--|--|

| R          | REF       |       |  |  |

| 481        | REF/2     |       |  |  |

| 241        | REF/4     |       |  |  |

| CPU        | (1:8)     | REF2  |  |  |

| DIIC (1.6) | BSEL=1    | REF/4 |  |  |

| BUS (1:6)  | BESEL = 0 | REF/3 |  |  |

**Note:** REF is the frequency of either the crystal connected between the devices X1 and X2 or, in the case of a device being driven by an external reference clock, the frequency of the reference (or test) clock on the device's X1 pin.

Fig. 1

Fig. 2a Fig. 2b

Fig. 3

## **Technical Pin Function Descriptions**

#### VDD1

This is the power supply to the internal logic of the device as well as the following clock output buffers:

A. REF clock output buffers

B. BUS clock output buffers

C. Fixed clock output buffers

This pin may be operated at any voltage between 3.0 and 5.5 volts. Clocks from the listed buffers that it supplies will have a voltage swing from ground to this level. For the actual guaranteed high and low voltage levels of these clocks, please consult the AC parameter table in this data sheet.

#### **GND**

This is the power supply ground return pin for the internal logic of the device as well as the following clock output buffers:

A. REF clock output buffers

B. BUS clock output buffers

C. CPU clock output buffers

#### **X1**

This pin serves one of two functions. When the device is used with a crystal, X1 acts as the input pin for the reference signal that comes from the discrete crystal. When the device is driven by an external clock signal, X1 is the device' input pin for that reference clock. This pin also implements an internal crystal loading capacitor that is connected to ground. See the data tables for the value of the capacitor.

#### X2

This pin is used only when the device uses a Crystal as the reference frequency source. In this mode of operation, X2 is an output signal that drives (or excites) the discrete crystal. This pin also implements an internal crystal loading capacitor that is connected to ground. See the data tables for the value of the capacitor.

#### **CPU** (1:8)

This pin is the clock output that drives processor and other CPU related circuitry that require clocks which are in tight skew tolerance with the CPU clock. The voltage swing of these clocks is controlled by that which is applied to the VDD pin of the device. See the Functionality table at the beginning of this data sheet for a list of the specific frequencies this clock operates at and the selection codes that are necessary to produce these frequencies.

#### **BUS (1:6)**

This pin is the clock output that is intended to drive the systems plug-in card bus. The voltage swing of these clocks is controlled by the supply that is applied to the VDD pin of the device. See the Functionality table at the beginning of this data sheet for a list of the specific frequencies that this clock operates at and the selection codes that are necessary to produce these frequencies.

#### FS0, FS1, FS2

These pins control the frequency of the clocks at the CPU, CPUL, BUS, SDRAM, AGP and IOAPIC pins. See the Funtionality table at the beginning of this data sheet for a list of the specific frequencies that this clock operates at and the selection codes that are necessary to produce these frequencies. The device reads these pins at power-up and stores the programmed selection code in an internal data latch. (See programming section of this data sheet for configuration circuitry recommendations.

#### **BSEL**

When this pin is a logic 1, it will place the CPU clocks in the synchronous mode (running at half the frequency of the Ref). If this pin is a logic 0, it will be in the asynchronous mode for the CPU clocks and will operate at the preprogrammed fixed frequency rate. It is a shared pin and is programed the same way as the Frequency Select pins.

#### **VDD 2.3**

These are the power supply pins for the CPU clock buffers. By separating the clock power pins, each group can receive the appropriate power decoupling and bypassing necessary to minimize EMI and crosstalk between the individual signals. VDD2 can be reduced to 2.5V VDD for advanced processor clocks, which will bring CPU (1:6) outputs at 0 to 2.5V output swings.

#### 48 MHz

This is a fixed frequency clock that is typically used to drive Super I/O peripheral device needs.

#### **24 MHz**

This is a fixed frequency clock that is typically used to drive Keyboard controller clock needs.

#### VDD4

This power pin supplies the BUS clock buffers.

#### REI

This is a fixed frequency clock that runs at the same frequency as the input reference clock (typically 14.31818 MHz) is and typically used to drive Video and ISA BUS requirements.

#### VDD5

This power pin supplies the 48/24 MHz clocks.

# ICS169C-232

# **Absolute Maximum Ratings**

Supply Voltage ...... 7.0 V

Logic Inputs . . . . . . . . . . . . . . . . GND –0.5 V to  $\,$  V  $_{DD}$  +0.5 V

Ambient Operating Temperature ...... 0°C to +70°C

Storage Temperature...... -65°C to +150°C

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristics at 3.3V**

$V_{DD} = 3.0 - 3.7 \text{ V}$ ,  $T_A = 0 - 70^{\circ} \text{C}$  unless otherwise stated

| DC Characteristics               |        |                                     |        |       |        |       |  |  |  |  |

|----------------------------------|--------|-------------------------------------|--------|-------|--------|-------|--|--|--|--|

| PARAMETER                        | SYMBOL | TEST CONDITIONS                     | MIN    | TYP   | MAX    | UNITS |  |  |  |  |

| Input Low Voltage                | VIL    |                                     | -      | -     | 0.2Vdd | V     |  |  |  |  |

| Input High Voltage               | Vih    |                                     | 0.7Vdd | -     | -      | V     |  |  |  |  |

| Input Low Current                | IIL    | $V_{IN} = 0V$                       | -28.0  | -10.5 | -      | μΑ    |  |  |  |  |

| Input High Current               | Iін    | Vin = Vdd                           | -5.0   | -     | 5.0    | μΑ    |  |  |  |  |

| Output Low Current <sup>1</sup>  | Iol    | Vol = 0.8V; for CPU, BUS, REF CLKs  | 19.0   | 30.0  | -      | mA    |  |  |  |  |

| Output High Current <sup>1</sup> | Іон    | Vol = 2.0V; for CPU, BUS, REF CLKs  | -      | -38.0 | -16.0  | mA    |  |  |  |  |

| Output Low Current <sup>1</sup>  | Iol    | Vol = 0.8V; for fixed CLKs          | 16.0   | 25.0  | -      | mA    |  |  |  |  |

| Output High Current <sup>1</sup> | Іон    | Vol = 2.0V; for fixed CLKs          | -      | -30.0 | -14.0  | mA    |  |  |  |  |

| Output Low Voltage <sup>1</sup>  | Vol    | IoL = 10mA; for CPU, BUS, REF CLKs  | -      | 0.3   | 0.4    | V     |  |  |  |  |

| Output High Voltage <sup>1</sup> | Vон    | IOH = -15mA; for CPU, BUS, REF CLKs | 2.4    | 2.8   | -      | V     |  |  |  |  |

| Output Low Voltage <sup>1</sup>  | Vol    | IOL = 8mA; for fixed CLKs           | -      | 0.3   | 0.4    | V     |  |  |  |  |

| Output High Voltage <sup>1</sup> | Voh    | IOH = -8mA; for fixed CLKs          | 2.4    | 2.8   | -      | V     |  |  |  |  |

| Supply Current                   | Idd    | @66.6 MHz; all outputs unloaded     | -      | 70    | 140    | mA    |  |  |  |  |

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

# **Electrical Characteristics at 3.3V**

$V_{DD} = 3.0 - 3.7 \text{ V}$ ,  $T_A = 0 - 70^{\circ} \text{ C}$  unless otherwise stated

| AC Characteristics                          |                  |                                                                                           |      |        |      |       |  |  |

|---------------------------------------------|------------------|-------------------------------------------------------------------------------------------|------|--------|------|-------|--|--|

| PARAMETER                                   | SYMBOL           | TEST CONDITIONS                                                                           | MIN  | TYP    | MAX  | UNITS |  |  |

| Rise Time <sup>1</sup>                      | T <sub>r1</sub>  | 20pF load, 0.8 to 2.0V<br>CPU & BUS                                                       | -    | 0.9    | 1.5  | ns    |  |  |

| Fall Time <sup>1</sup>                      | T <sub>f1</sub>  | 20pF load, 2.0 to 0.8V<br>CPU & BUS                                                       | -    | 0.8    | 1.4  | ns    |  |  |

| Rise Time <sup>1</sup>                      | Tr2              | 20pF load, 20% to 80%<br>CPU & BUS                                                        | -    | 1.5    | 2.5  | ns    |  |  |

| Fall Time <sup>1</sup>                      | Tf2              | 20pF load, 80% to 20%<br>CPU & BUS                                                        | -    | 1.4    | 2.4  | ns    |  |  |

| Duty Cycle <sup>1</sup>                     | Dt               | 20pF load @ VOUT=1.4V                                                                     | 45   | 50     | 60   | %     |  |  |

| Jitter, One Sigma <sup>1</sup>              | Tj1s1            | CPU & BUS Clocks; Load=20pF,<br>BSEL=1                                                    | -    | 50     | 150  | ps    |  |  |

| Jitter, Absolute <sup>1</sup>               | Tjab1            | CPU & BUS Clocks; Load=20pF,<br>BSEL=1                                                    | -250 | -      | 250  | ps    |  |  |

| Jitter, One Sigma <sup>1</sup>              | Tj1s2            | REF & Fixed CLKs; Load=20pF                                                               | -    | 1      | 3    | %     |  |  |

| Jitter, Absolute <sup>1</sup>               | Tjab2            | REF & Fixed CLKs; Load=20pF                                                               | -5   | 2      | 5    | %     |  |  |

| Input Frequency <sup>1</sup>                | Fi               |                                                                                           | 12.0 | 14.318 | 16.0 | MHz   |  |  |

| Logic Input Capacitance <sup>1</sup>        | Cin              | Logic input pins                                                                          | -    | 5      | -    | pF    |  |  |

| Crystal Oscillator Capacitance <sup>1</sup> | Cinx             | X1, X2 pins                                                                               | -    | 18     | -    | pF    |  |  |

| Power-on Time <sup>1</sup>                  | ton              | From V <sub>DD</sub> =1.6V to 1st crossing of 66.6 MHz V <sub>DD</sub> supply ramp < 40ms | -    | 2.5    | 4.5  | ms    |  |  |

| Frequency Settling Time <sup>1</sup>        | $t_{\mathrm{s}}$ | From 1st crossing of acquisition to < 1% settling                                         | -    | 2.0    | 4.0  | ms    |  |  |

| Clock Skew <sup>1</sup>                     | T <sub>sk1</sub> | CPU to CPU; Load=20pF; @1.4V                                                              | -    | 150    | 250  | ps    |  |  |

| Clock Skew <sup>1</sup>                     | T <sub>sk2</sub> | BUS & BUS; Load=20pF; @1.4V                                                               | -    | 160    | 500  | ps    |  |  |

| Clock Skew <sup>1</sup>                     | T <sub>sk3</sub> | CPU to BUS; Load=20pF; @1.4V (CPU is early)                                               | 1    | 2.6    | 4    | ns    |  |  |

Note 1: Parameter is guaranteed by design and characterization. Not 100% tested in production.

# ICS169C-232

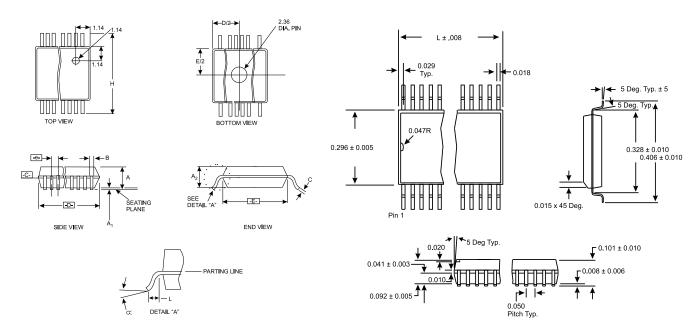

# **SSOP Package**

# **SOIC Package**

| SSOP   |                | COMMON<br>IMENSIONS | S     | SSOP       | D     |       |       |  |

|--------|----------------|---------------------|-------|------------|-------|-------|-------|--|

| SYMBOL | MIN.           | NOM.                | MAX.  | VARIATIONS | MIN.  | NOM.  | MAX.  |  |

| A      | 0.068          | 0.073               | 0.078 | 14         | 0.239 | 0.244 | 0.249 |  |

| A1     | 0.002          | 0.005               | 0.008 | 16         | 0.239 | 0.244 | 0.249 |  |

| A2     | 0.066          | 0.068               | 0.070 | 20         | 0.278 | 0.284 | 0.289 |  |

| В      | 0.010          | 0.012               | 0.015 | 24         | 0.318 | 0.323 | 0.328 |  |

| С      | 0.004          | 0.006               | 0.008 | 28         | 0.397 | 0.402 | 0.407 |  |

| D      |                | See Variations      |       | 30         | 0.397 | 0.402 | 0.407 |  |

| Е      | 0.205          | 0.209               | 0.212 |            |       |       |       |  |

| e      |                | 0.0256 BSC          |       |            |       |       |       |  |

| Н      | 0.301          | 0.307               | 0.311 |            |       |       |       |  |

| L      | 0.025          | 0.030               | 0.037 |            |       |       |       |  |

| N      | See Variations |                     |       |            |       |       |       |  |

| ∞      | 0°             | 4°                  | 8°    |            |       |       |       |  |

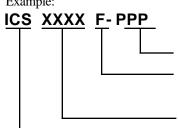

# Ordering Information ICS9169CF-232 ICS9169CM-232

Example:

# SOIC Package (wide body) $_{e\,=\,0.05\;\mathrm{BSC}}$

| LEAD COUNT  | 14L   | 16L   | 18L   | 20L   | 24L   | 28L   | 32L   |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| DIMENSION L | 0.354 | 0.404 | 0.454 | 0.504 | 0.604 | 0.704 | 0.804 |