#

# $\mathbf{AMD-766}^{\mathrm{TM}}$

# **Peripheral Bus Controller**

# **Data Sheet**

#### © 2001 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD logo, and combinations thereof, and AMD-766 are trademarks of Advanced Micro Devices, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

23167B – March 2001

AMD-766<sup>TM</sup> Peripheral Bus Controller Data Sheet

## Table of Contents

| 1 | Ove          | erview                                                  | .5 |

|---|--------------|---------------------------------------------------------|----|

|   | 1.1          | Features                                                | 5  |

| 2 | Or           | dering Information                                      | 6  |

|   |              |                                                         |    |

| 3 | -            | nal Descriptions                                        |    |

|   | 3.1          | Terminology                                             |    |

|   | 3.2          | PCI Interface                                           |    |

|   | 3.3          | Processor Interface                                     |    |

|   | 3.4          | ISA/LPC Bus and Legacy Support Signals                  |    |

|   | 3.5          | Ultra DMA Enhanced IDE Interface                        |    |

|   | 3.6          | System Management Signals                               |    |

|   | 3.7          | Universal Serial Bus Interface                          |    |

|   | 3.8          | Miscellaneous Signals                                   |    |

|   | 3.9          | Power And Ground                                        | 14 |

| 4 | Fu           | nctional Operation                                      | 15 |

|   | 4.1          | Overview                                                | 15 |

|   | 4.1.         | .1 Resets                                               | 15 |

|   | 4.2          | PCI Interface                                           |    |

|   | 4.2.         | 6                                                       |    |

|   | 4.3          | ISA/LPC Bridge And Legacy Logic                         |    |

|   | 4.3.         |                                                         |    |

|   | 4.3.         |                                                         |    |

|   | 4.3.<br>4.3. |                                                         |    |

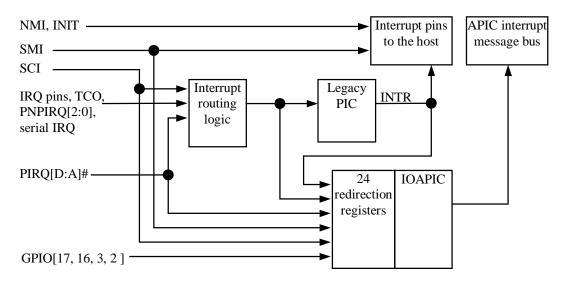

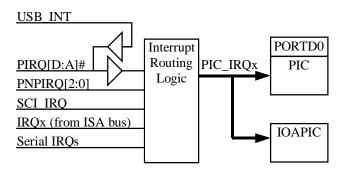

|   |              | 4.3.4.1 Interrupt Routing Logic                         |    |

|   |              | H.3.4.2 IOAPIC                                          |    |

|   |              | 4.3.4.2.1 WSC#                                          |    |

|   |              | 4.3.4.2.2 The IRQ lines                                 | 21 |

|   | 4.3.         |                                                         |    |

|   | 4.4          | Enhanced IDE Controller                                 |    |

|   | 4.5          | USB Controller                                          |    |

|   | 4.5.         |                                                         |    |

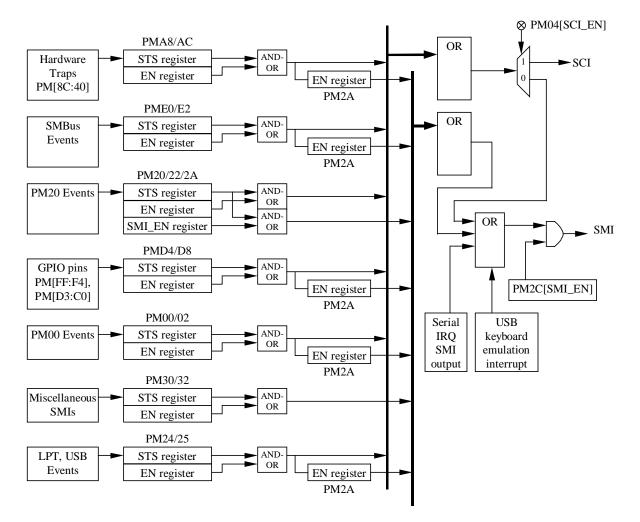

|   | 4.6          | System Management Logic                                 |    |

|   | 4.6.         | 1 Power Management                                      |    |

|   |              | k.6.1.2 Traps                                           |    |

|   |              | 4.6.1.3 System Inactivity Timer.                        |    |

|   |              | <ul><li>4.6.1.4 Throttling logic</li></ul>              |    |

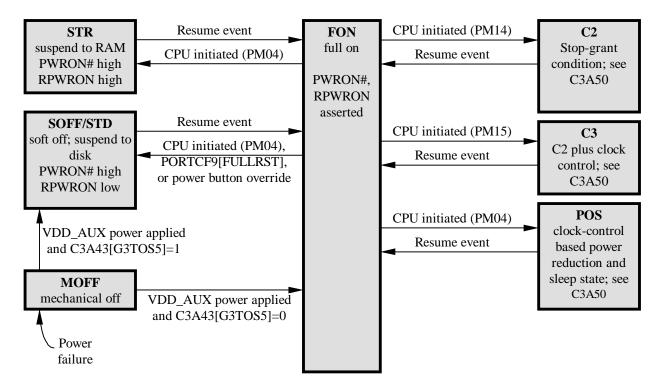

|   | 4            | 4.6.1.5 System Power State Controller (SPSC)            |    |

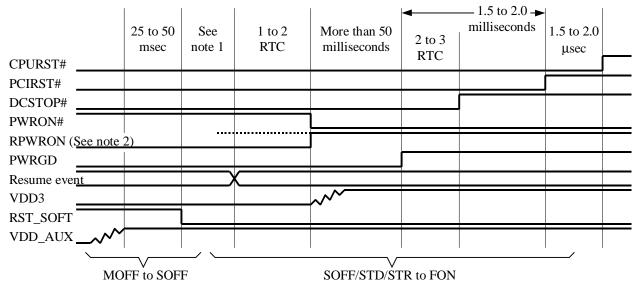

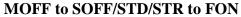

|   |              | 4.6.1.5.1 Transitions Between MOFF/SOFF/STD/STR and FON |    |

|   |              | 4.6.1.5.2 Transitions From FON To C2, C3 And POS        |    |

|   |              | 4.6.1.5.3 Transitions From C2, C3 And POS To FON        |    |

|   | 4.6.         |                                                         |    |

|   | 4.6.         |                                                         |    |

|   | 4.6.<br>4.6. | C 7                                                     |    |

|   | 4.0.         | .5 General Purpose IO                                   | 30 |

| 5 | Reg          | gisters                                                 | 31 |

|   | 5.1          | Register Overview                                       | 31 |

| 5.                                                                          | .1.1 Configuration Space                                                                                                                                                                |                                                                                        |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 5.                                                                          | .1.2 Register Naming And Description Conventions                                                                                                                                        |                                                                                        |

| 5.2                                                                         | PCI-ISA Bridge Configuration Registers (C0Axx)                                                                                                                                          |                                                                                        |

| 5.3                                                                         |                                                                                                                                                                                         |                                                                                        |

| 5.                                                                          | .3.1 Miscellaneous Legacy and Fixed IO Address Registers                                                                                                                                |                                                                                        |

| 5.                                                                          | .3.2 Legacy DMA Controller (DMAC) Registers                                                                                                                                             |                                                                                        |

| 5.                                                                          | .3.3 Legacy Programmable Interval Timer (PIT) Registers                                                                                                                                 |                                                                                        |

| 5.                                                                          | .3.4 Legacy Programmable Interrupt Controller (PIC) Registers                                                                                                                           |                                                                                        |

| 5.                                                                          | .3.5 IOAPIC Registers                                                                                                                                                                   |                                                                                        |

| 5.                                                                          | .3.6 Real-Time Clock Registers                                                                                                                                                          |                                                                                        |

| 5.4                                                                         | Enhanced IDE Controller Configuration Registers (C1Axx)                                                                                                                                 |                                                                                        |

| 5.5                                                                         | ······································                                                                                                                                                  |                                                                                        |

| 5.6                                                                         | USB Host Controller Configuration Registers (C4Axx)                                                                                                                                     | 55                                                                                     |

| 5.7                                                                         |                                                                                                                                                                                         |                                                                                        |

| 5.                                                                          | .7.1 Summary                                                                                                                                                                            |                                                                                        |

| 5.                                                                          | .7.2 Implementation-Specific Items                                                                                                                                                      |                                                                                        |

| 5.8                                                                         | Power Management Configuration Registers (C3Axx)                                                                                                                                        | 58                                                                                     |

| 5.9                                                                         | System Management IO Mapped Registers (PMxx)                                                                                                                                            | 68                                                                                     |

|                                                                             |                                                                                                                                                                                         |                                                                                        |

| 6 E                                                                         | Electrical Data                                                                                                                                                                         |                                                                                        |

|                                                                             | Electrical Data<br>Absolute Ratings                                                                                                                                                     |                                                                                        |

| 6.1                                                                         | Absolute Ratings                                                                                                                                                                        |                                                                                        |

| 6.1<br>6.2                                                                  | Absolute Ratings<br>Operating Ranges                                                                                                                                                    |                                                                                        |

| 6.1<br>6.2<br>6.3                                                           | Absolute Ratings<br>Operating Ranges<br>DC Characteristics                                                                                                                              |                                                                                        |

| 6.1<br>6.2                                                                  | Absolute Ratings<br>Operating Ranges<br>DC Characteristics<br>Power dissipation                                                                                                         |                                                                                        |

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Absolute Ratings<br>Operating Ranges<br>DC Characteristics<br>Power dissipation<br>Switching Characteristics                                                                            |                                                                                        |

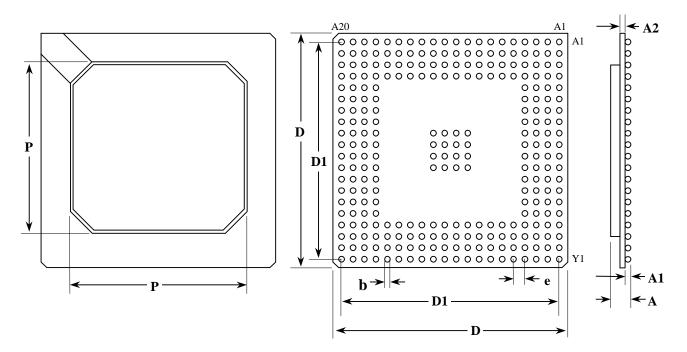

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7 Pt                                     | Absolute Ratings<br>Operating Ranges<br>DC Characteristics<br>Power dissipation<br>Switching Characteristics<br>Pin Designations                                                        |                                                                                        |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7 Pt<br>8 Pc                             | Absolute Ratings         Operating Ranges         DC Characteristics         Power dissipation         Switching Characteristics         Pin Designations         Package Specification | 88<br>88<br>88<br>88<br>89<br>89<br>89<br>89<br>89<br>                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7 Pt<br>8 Pc<br>9 Tc                     | Absolute Ratings         Operating Ranges         DC Characteristics         Power dissipation         Switching Characteristics         Pin Designations         Package Specification | 88<br>88<br>88<br>89<br>89<br>89<br>89<br>89<br>89<br>89<br>89<br>89<br>89<br>8        |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7 Pr<br>8 Pc<br>9 Tc<br>9.1              | Absolute Ratings                                                                                                                                                                        | 88<br>88<br>88<br>89<br>89<br>89<br>89<br>                                             |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7 Pt<br>8 Pc<br>9 Tc                     | Absolute Ratings         Operating Ranges         DC Characteristics         Power dissipation         Switching Characteristics         Pin Designations         Package Specification | 88<br>88<br>88<br>89<br>89<br>89<br>89<br>                                             |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7 Pt<br>8 Pc<br>9 Tc<br>9.1<br>9.2       | Absolute Ratings                                                                                                                                                                        | 88<br>88<br>88<br>89<br>89<br>89<br>89<br>                                             |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>7 Pt<br>8 Pc<br>9 Tc<br>9.1<br>9.2       | Absolute Ratings                                                                                                                                                                        | 88<br>88<br>88<br>89<br>89<br>89<br>89<br>89<br>92<br>92<br>93<br>93<br>93<br>93<br>93 |

#### 1 Overview

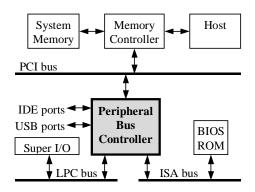

The AMD-766 peripheral bus controller<sup>TM</sup> is an integrated circuit (IC), developed by AMD, to be the system Southbridge component of personal computer chipsets. The AMD-766 peripheral bus controller (*the IC*) connects to a host memory controller through the PCI bus.

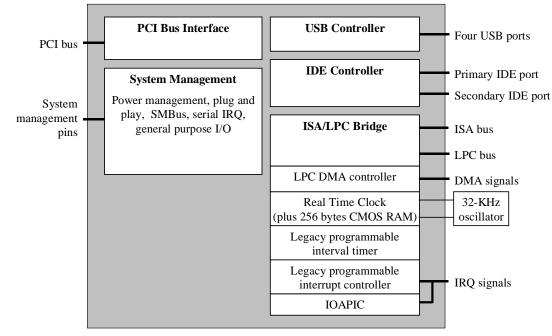

#### 1.1 Features

- PCI interface (PCI specification revision 2.2 compliant).

- LPC bus to connect peripherals such as super IO and BIOS.

- Partial ISA bus.

- 8 bits wide.

- Support for Flash BIOS.

- Enhanced IDE controller.

- Support for two dual-drive ports.

- PIO modes 0-4.

- Multi-word DMA.

- UDMA modes up to ATA-100.

- OHCI-based USB host controller with support for four ports.

- Serial IRQ protocol.

- ACPI-compliant power management logic.

- Programmable C2, C3, power-onsuspend, suspend to RAM, suspend to disk, and soft off states.

- Throttling.

- Hardware traps.

- System inactivity timer.

- 32 general-purpose IO (GPIO) pins (some are multiplexed with other hard-wired functions).

- Privacy/security logic (ROM access control).

- Legacy logic.

- Programmable interrupt controller.

- Programmable interval timer.

- DMA controller (for LPC bus).

- Legacy ports.

- IOAPIC controller.

- Real-time clock.

- 256 bytes of CMOS RAM.

- Battery-powered.

- ACPI-compliant extensions.

- SMBus controller with one SMBus port.

- 272-pin BGA package.

- 3.3-volt core and output drivers; 5-volt tolerant input buffers.

The IC is intended to fit into the traditional Southbridge position on PC-compatible platforms.

Block diagram of the IC:

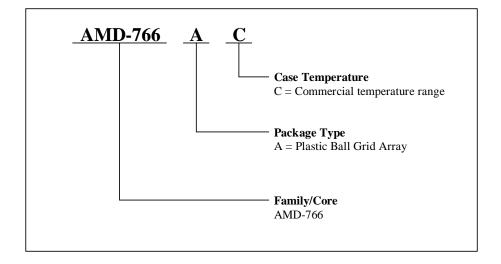

#### 2 Ordering Information

#### 3 Signal Descriptions

#### 3.1 Terminology

See section 5.1.2 for a description of the register naming conventions used in this document. See section 4.6.1.5 for a description of the system power states: MOFF, SOFF, STD, STR, POS, C3, C2, and FON. See section 3.9 for a description of the power planes. See section 4.1.1 for a description of the types of resets.

Signals with a # suffix are active low.

Note: All inputs are 5-volt tolerant except analog pins and as noted in the pin descriptions.

| Signals described in this chapter utilize the following IO cell types: |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| Name   | Notes                                                                                                     |

|--------|-----------------------------------------------------------------------------------------------------------|

| Input  | Input signal only.                                                                                        |

| Output | Output signal only. This includes outputs that are capable of being in the high-impedance state.          |

| OD     | Open drain output. These pins are driven low and designed to be pulled high by external circuitry.        |

| IO     | Input or output signal.                                                                                   |

| IOD    | Input or open-drain output.                                                                               |

| w/H    | With hysteresis on the input (applied with other signal types).                                           |

| -PU    | Pull up included (applied with other signal types). An internal pull-up resister is provided to the line. |

|        | These pull-ups are enabled by C3A48. The resistors vary over process, voltage and temperature from        |

|        | 3400 to 7150 ohms.                                                                                        |

| -PD    | Pull down included (applied with other signal types). An internal pull-down resister is provided to the   |

|        | line. These pull-downs are enabled by C3A48. The resistors vary over process, voltage and temperature     |

|        | from 3400 to 7150 ohms.                                                                                   |

| Analog | Analog signal.                                                                                            |

The following provides definitions and reference data about each of the IC's pins. "During Reset" provides the state of the pin while the pin's power plane is being reset (while RESET# is low for the main power plane; while the internal RST\_SOFT signal is asserted for the VDD\_AUX power plane). "After Reset" provides the state of the pin immediately after that reset. "During POS" provides the state of the pin while in the power on suspend system sleep states. "During S3:S5" provides the state of the pin while in the suspend to disk, suspend to RAM, or soft off system sleep states. "Func" means that the signal is active or functional, operating per its defined function. "Last State" indicates that the signal remains in the state that it was in when the system entered POS.

#### 3.2 PCI Interface

| Pin name and description                                                      | IO cell | Power | During  | Post    | POS     |

|-------------------------------------------------------------------------------|---------|-------|---------|---------|---------|

| ×                                                                             | type    | plane | Reset   | Reset   |         |

| AD[31:0]. Address-data bus.                                                   | IO      | VDD3  | 3-state | 3-state | 3-state |

| <b>CBE_L[3:0].</b> Command-byte enable bus.                                   | IO      | VDD3  | 3-state | 3-state | 3-state |

| DEVSEL#. Device select.                                                       | IO-PU   | VDD3  | 3-state | 3-state | 3-state |

| FRAME#. Frame signal.                                                         | IO-PU   | VDD3  | 3-state | 3-state | 3-state |

| <b>IDSEL.</b> Identification select signal.                                   | Input   | VDD3  | -       | -       | -       |

| <b>IRDY#.</b> Master ready signal.                                            | IO-PU   | VDD3  | 3-state | 3-state | 3-state |

| PAR. Parity signal.                                                           | Output  | VDD3  | 3-state | 3-state | 3-state |

| <b>PCIRST#.</b> PCI reset. This is the system reset signal for logic that is  | Output  | VDD_  | Low     | High    | High    |

| powered by the system's main power supplies.                                  |         | SOFT  |         |         |         |

| <b>PCLK.</b> 33 MHz PCI clock. This is required to remain active during reset | Input   | VDD3  | -       | -       | -       |

| and when the IC enters the power-on suspend state (POS).                      |         |       |         |         |         |

| PGNT#. Master grant signal.                                                   | Input   | VDD3  | -       | -       | -       |

| <b>PIRQ[A, B, C, D]#.</b> PCI interrupt requests. Only PIRQD# is an output    | IOD-    | VDD3  | -       | -       | -       |

| as well as an input; it may be driven active by the USB interrupt. The        | PU      |       |         |         |         |

| other three pins are inputs only.                                             |         |       |         |         |         |

| PREQ#. Master request signal.                                                 | Output  | VDD3  | High    | High    | High    |

| SERR#. PCI system error signal. This may be asserted by the system to         | Input-  | VDD3  | -       | -       | -       |

| indicate a system error condition. If enabled by RTC70[7], an NMI             | PU      |       |         |         |         |

| interrupt may be generated.                                                   |         |       |         |         |         |

| STOP#. Target abort signal.                                                   | IO-PU   | VDD3  | 3-state | 3-state | 3-state |

| TRDY#. Target ready signal.                                                   | IO-PU   | VDD3  | 3-state | 3-state | 3-state |

#### 3.3 Processor Interface

| Pin name and description                                                      | IO cell | Power | During  | Post    | POS     |

|-------------------------------------------------------------------------------|---------|-------|---------|---------|---------|

|                                                                               | type    | plane | Reset   | Reset   |         |

| A20M#. Address bit[20] mask to the processor. This output is a logical        | OD      | VDD3  | 3-state | 3-state | 3-state |

| OR of the KA20G pin from the keyboard controller and PORT92[A20EN].           |         |       |         |         |         |

| <b>CPURST#.</b> CPURST#. Reset to the processor. This is the reset to         | OD      | VDD3  | Low     | Func.   | 3-state |

| processor(s). See sections 4.1.1 and 4.6.1.5.1.                               |         |       |         |         |         |

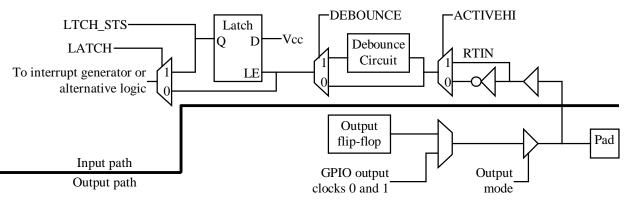

| FERR#. Floating-point error from the processor. The processor asserts         | Input   | VDD3  | -       | -       | -       |

| this signal to indicate a floating-point error has occurred. This is used to  | w/H     |       |         |         |         |

| create IRQ13 to the PIC and IOAPIC.                                           |         |       |         |         |         |

| <b>IGNNE#.</b> Ignore numeric error to the processor.                         | OD      | VDD3  | 3-state | 3-state | 3-state |

| <b>INIT#.</b> Initialization interrupt to the processor.                      | OD      | VDD3  | 3-state | 3-state | 3-state |

| <b>INTR.</b> Interrupt request to the processor.                              | OD      | VDD3  | Low     | Low     | low     |

| <b>NMI.</b> Non-maskable interrupt request to the processor.                  | OD      | VDD3  | Low     | Low     | Low     |

| <b>PICCLK.</b> Interrupt message bus clock for the IOAPIC. This is controlled | IOD     | VDD3  | Func.   | Func.   |         |

| through C0Ax4B[APICCKS]. During POS, PICCLK may be selected to                |         |       |         |         |         |

| either be active or forced low by C3A50[APIC_POSEN].                          |         |       |         |         |         |

| PICD0# and PICD1#. Interrupt message bus data bits 1 and 0 for the            | IOD     | VDD3  | 3-state | 3-state | 3-state |

| IOAPIC.                                                                       |         |       |         |         |         |

| SMI#. System management interrupt to the processor.                           | OD      | VDD3  | 3-state | 3-state | 3-state |

| STPCLK#. Processor stop-grant request.                                        | OD      | VDD3  | 3-state | 3-state | Active  |

| <b>WSC#.</b> Write snoop complete. This signal is used to guarantee the most  | IOD     | VDD3  | 3-state | 3-state | 3-state |

| recent PCI bus writes from the IC to system memory are visible to the host.   |         |       |         |         |         |

| See section 4.3.2 for more details. This signal requires an external pull-up  |         |       |         |         |         |

| resistor with a value between 10K to 200K ohms.                               |         |       |         |         |         |

### 3.4 ISA/LPC Bus and Legacy Support Signals

| Pin name and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IO cell<br>type        | Power<br>plane | During<br>Reset | Post<br>Reset | POS       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|-----------------|---------------|-----------|

| <b>BCLK.</b> ISA bus clock. This is the approximately 8 MHz ISA-bus clock. It is the frequency of PCLK divided by four.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Output                 | VDD3           | Func.           | Func.         | Func.     |

| <b>EKIRQ1.</b> External keyboard controller IRQ1. This is designed to be connected to the keyboard controller's IRQ1 for the internal interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input                  | VDD3           | Input           | Input         | Func.     |

| controller logic.<br><b>EKIRQ12.</b> External keyboard controller IRQ12 mouse interrupt. This is designed to be connected to the keyboard controller's IRQ12 for the internal interrupt controller logic. See C3A46[10:9] for information on how the IRQ12 pin and the mouse interrupt are combined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input                  | VDD3           | Input           | Input         | Func.     |

| <b>IOCHK#.</b> ISA bus IO channel check signal. The assertion of this signal controls PORT61[IOCHK].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input-<br>PU           | VDD3           | -               | -             | -         |

| <b>IOCHRDY.</b> ISA bus IO channel ready signal. This is deasserted by ISA bus slaves to extend the duration of the cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input-<br>PU           | VDD3           | 3-state         | 3-state       | 3-state   |

| IOR#. ISA bus IO read signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Output                 | VDD3           | High            | High          | High      |

| IOW#. ISA bus IO write signal.<br>IRQ[11:9,7:3]. ISA bus interrupt request signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Output<br>Input-<br>PU | VDD3<br>VDD3   | High<br>-       | High<br>-     | High<br>- |

| REQ[7:0]#. PCI bus master request pins (alternate function to IRQ[11:9, 7:3]; selected by PMF5). These pins may be used to set PM00[BM_STS].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |                |                 |               |           |

| <ul> <li>IRQ12. ISA bus interrupt request 12.</li> <li>SMBALERT#. SMBus alert (alternate function to IRQ12; selected by C3A46[10:9]). When enabled to do so, this may be used to generate an SMI or SCI interrupt associated with the SMBus logic.</li> <li>USBOC1#. USB over current detect 1 (alternate function to IRQ12; selected by C3A46[10:9]). When enabled to do so, this may be routed to the USB block to be a second source of USB port over-current detection.</li> </ul>                                                                                                                                                                                                                                                                                                                                      | Input                  | VDD3           | -               | -             | -         |

| <ul> <li>IRQ[15,14]. Input; ISA bus interrupt request signals.</li> <li>NMPIRQ. Native mode primary IDE port IRQ (alternate function to IRQ14; selected by C1A08[8]). When C1A08[8] is high, this pin becomes an active-high, shared interrupt that is logically combined with PIRQA# such that it may be shared with other PCI devices. This is in support of native mode as defined by the <i>PCI IDE Controller Specification</i>.</li> <li>NMSIRQ. Native mode secondary IDE port IRQ (alternate function to IRQ15; selected by C1A08[10]). When C1A08[10] is high, this pin becomes an active-high, shared interrupt that is logically combined with PIRQA# such that it may be shared with other PCI devices. This is in support of native mode as defined by the <i>PCI IDE Controller Specification</i>.</li> </ul> | Input-<br>PU           | VDD3           | -               | -             | -         |

| <b>ISABIOS.</b> Direct BIOS accesses to the ISA bus versus the LPC bus. The state of this pin may be accessed in C3A48[ISABIOS]. 1=The ISA bus. 0=The LPC bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Input                  | VDD3           | Input           | Input         | Input     |

| <b>KA20G.</b> Keyboard A20 gate. This is designed to be the gate A20 signal from the system keyboard controller. It affects A20M#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input                  | VDD3           | Input           | Input         | Func.     |

| <b>KBRC#.</b> Keyboard reset command. This is designed to be the processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input                  | VDD3           | Input           | Input         | Func.     |

23167B – March 2001

AMD-766<sup>TM</sup> Peripheral Bus Controller Data Sheet

| Pin name and description                                                      | IO cell | Power | During  | Post    | POS     |

|-------------------------------------------------------------------------------|---------|-------|---------|---------|---------|

|                                                                               | type    | plane | Reset   | Reset   |         |

| reset signal from the system keyboard controller. When asserted, an INIT      |         |       |         |         |         |

| interrupt to the processor is generated.                                      |         |       |         |         |         |

| LA[23:17]. ISA system address bus bits[23:17]. LA[23:17] and SA[16:0]         | Output  | VDD3  | Low     | Low     | Last    |

| combine to for the 24-bit ISA address bus.                                    |         |       |         |         | state   |

| LAD[3:0]. LPC address-data bus.                                               | IO      | VDD3  | 3-state | 3-state | 3-state |

| LDRQ0# and LDRQ1#. LPC DMA request signals.                                   | Input   | VDD3  | -       | -       | -       |

| LFRAME#. LPC frame signal.                                                    | IO      | VDD3  | High    | High    | High    |

| <b>MEMR#.</b> ISA bus memory cycle read command.                              | Output  | VDD3  | High    | High    | High    |

| MEMW#. ISA bus memory cycle write command.                                    | Output  | VDD3  | High    | High    | High    |

| <b>OSC.</b> 14.31818 MHz. clock. This is used for the programmable interval   | Input   | VDD3  | -       | -       | -       |

| timer and various power management timers.                                    |         |       |         |         |         |

| <b>ROM_KBCS#.</b> ROM chip select and keyboard chip select. This is           | IO      | VDD3  | Input   | High    | High    |

| designed to be connected to both the ISA-bus system ROM BIOS and the          |         |       |         |         |         |

| keyboard controller. During ISA bus memory accesses this pin decodes          |         |       |         |         |         |

| ROM BIOS memory space, as defined by C0A43 (if the ISABIOS pin is             |         |       |         |         |         |

| high). During ISA bus IO cycles to the legacy keyboard controller, this       |         |       |         |         |         |

| pin decodes accesses to the keyboard controller. The state of this bit is     |         |       |         |         |         |

| captured during reset in C3A48[3].                                            |         |       |         |         |         |

| <b>SA[16:0].</b> ISA system address bus bits[16:0]. LA[23:17] and SA[16:0]    | Output  | VDD3  | Low     | Low     | Last    |

| combine to for the 24-bit ISA address bus.                                    |         |       |         |         | state   |

| <b>SD[7:0].</b> ISA data bus.                                                 | IO-PU   | VDD3  | 3-state | 3-state | 3-state |

| <b>SPKR.</b> Speaker driver from the programmable interval timer. This pin is | IO      | VDD3  | Input   | Low     | Last    |

| an input while PWRGD is low; it is used to select the default state of        |         |       |         |         | state   |

| C3A48[ENIDE, ENPCI, ENISA] (the internal pull-up-pull-down IO pin             |         |       |         |         |         |

| resister enables).                                                            |         |       |         |         |         |

#### 3.5 Ultra DMA Enhanced IDE Interface

| Pin name and description                                                                                                        | IO cell      | Power | During  | Post    | POS     |

|---------------------------------------------------------------------------------------------------------------------------------|--------------|-------|---------|---------|---------|

|                                                                                                                                 | type         | plane | Reset   | Reset   |         |

| <b>DADDR[P,S][2:0].</b> IDE controller [primary, secondary] port address.                                                       | Output       | VDD3  | Low     | Low     | Low     |

| <b>DCS1P#.</b> IDE controller primary port chip select 1. This is active during accesses to the IO address space 1F7h – 1F0h.   | Output       | VDD3  | High    | High    | High    |

| <b>DCS1S#.</b> IDE controller secondary port chip select 1. This is active during accesses to the IO address space 177h – 170h. | Output       | VDD3  | High    | High    | High    |

| <b>DCS3P#.</b> IDE controller primary port chip select 3. This is active during accesses to the IO address space 3F7h – 3F4h.   | Output       | VDD3  | High    | High    | High    |

| <b>DCS3S#.</b> IDE controller secondary port chip select 3. This is active during accesses to the IO address space 377h – 374h. | Output       | VDD3  | High    | High    | High    |

| <b>DDACK[P,S]#.</b> IDE controller [primary, secondary] port DMA                                                                | Output       | VDD3  | High    | High    | High    |

| acknowledge signal.<br><b>DDATA[P,S][15:0].</b> IO; IDE controller [primary, secondary] port data                               | IO           | VDD3  | 3-state | 2 stata | 2 state |

| bus.                                                                                                                            | 10           | VDD5  | 5-state | 3-state | 3-state |

| <b>DDRQ[P,S].</b> Input; IDE controller [primary, secondary] port DMA request signal.                                           | Input-<br>PD | VDD3  | -       | -       | -       |

| <b>DIOR[P,S]#.</b> Output; IDE controller [primary, secondary] port IO read command.                                            | Output       | VDD3  | High    | High    | High    |

| <b>DIOW</b> [ <b>P</b> , <b>S</b> ] <b>#.</b> Output; IDE controller [primary, secondary] port IO write command.                | Output       | VDD3  | High    | High    | High    |

| <b>DRDY</b> [ <b>P</b> , <b>S</b> ]. Input; IDE controller [primary, secondary] port ready strobe.                              | Input        | VDD3  | -       | -       | -       |

#### 3.6 System Management Signals

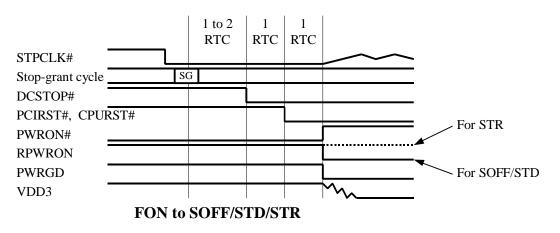

This group includes all the GPIO pins, many of which are multiplexed with other functions. The default function of GPIO pins after reset is specified by PM[FF:F4 and D3:C0]. When programmed as GPIOs, these pins are capable of being programmed to be inputs or push-pull outputs. GPIO pins remain functional during sleep states (if they are powered).

| Pin name and description                                                                                                                                                                                                                                                                                                       | IO cell       | Power       | During | Post  | POS   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|--------|-------|-------|

|                                                                                                                                                                                                                                                                                                                                | type          | plane       | Reset  | Reset |       |

| <b>C32KHZ.</b> 32.768 kHz clock output. This pin may also be configured as GPIO15 by PMCF.                                                                                                                                                                                                                                     | Output,<br>IO | VDD3        | Low    | Low   | Func. |

| <b>CACHE_ZZ.</b> Level 2 cache sleep mode output. This is designed to be connected to the power-control input to the second level cache to place it into low-power mode. It is controlled by C3A50. This pin may also be configured as GPIO8 by PMC8.                                                                          | Output,<br>IO | VDD3        | Low    | Low   | Func. |

| <b>CPUSLEEP#.</b> Processor non-snoop sleep mode output. This may be connected to the sleep pin of the processor to place it into a non-snoop-capable low-power state. It is controlled by C3A50. This pin may also be configured as GPIO5 by PMC5.                                                                            | Output,<br>IO | VDD3        | High   | High  | Func. |

| <b>CPUSTOP#.</b> Processor clock stop output. This may be connected to the system clock chip to control the host clock signals. It is controlled by C3A50. This pin may also be configured as GPIO6 by PMC6.                                                                                                                   | Output,<br>IO | VDD3        | High   | High  | Func. |

| <b>DCSTOP#.</b> DRAM controller stop output. This may be connected to the system memory controller to indicate that its clock is going to stop (so that an alternative DRAM refresh scheme may start). It is controlled by C3A50. This signal is also functional during STD, STR and SOFF.                                     | Output,<br>IO | VDD_<br>AUX | Active | High  | Func. |

| <b>EXTSMI#.</b> External SMI input. This pin may be used to generate SMI or SCI interrupts and resume events. This pin may also be configured as GPIO12 by PMCC.                                                                                                                                                               | Input,<br>IO  | VDD_<br>AUX | -      | -     | -     |

| <b>FLAGRD#.</b> Flag read output. This may be connected to the output-<br>enable input of external buffers with the buffer outputs on the SD pins.<br>Therefore, the inputs to the buffers may be software-readable flags.<br>FLAGRD# is asserted during reads of PM1A. This pin may also be<br>configured as GPIO11 by PMCB.  | Output,<br>IO | VDD3        | High   | High  | High  |

| <b>FLAGWR.</b> Flag write output. This may be connected to the latch-<br>enabled input of external latches with the latch inputs on the SD pins.<br>Therefore, the outputs of the latches may be software-controlled flags.<br>FLAGWR is asserted during writes to PM18. This pin may also be<br>configured as GPIO10 by PMCA. | Output,<br>IO | VDD3        | Low    | Low   | Low   |

23167B – March 2001

Preliminary Information

AMD:

AMD-766<sup>TM</sup> Peripheral Bus Controller Data Sheet

| Pin name and description                                                                                                                                                                                                                                                                                                                                                                                                     | IO cell<br>type | Power plane | During<br>Reset | Post<br>Reset | POS            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|-----------------|---------------|----------------|

| <b>GPIO[31:17, 9, 2].</b> General purpose IO pins. See section 4.6.5 for details about these pins. All GPIO pins are configured by PM[FF:F4 and D3:C0] where the default function is specified. GPIO pins remain functional during sleep states.                                                                                                                                                                             | ΙΟ              | VDD3        | -               | -             | Functio<br>nal |

| MSIRQ. Mouse interrupt request output (alternate function to GPIO17; selected by PMD1). This is the mouse IRQ from the USB keyboard emulation logic.                                                                                                                                                                                                                                                                         |                 |             |                 |               |                |

| PNPIRQ[2:0]. Plug and play interrupt request [2:0] inputs (alternate function to GPIO[20:18]; selected by PM[F4, D3, D2]). These may be assigned to control the IRQ signals to the interrupt routing table shown in section 4.3.2. They are controlled by C3A44.                                                                                                                                                             |                 |             |                 |               |                |

| BMREQ#. PCI bus master request input (alternate function to GPIO21; selected by PMF5). This is intended to be the OR of the external PCI bus request signals. If this function is selected by PMF5, then it controls the PM00[BM_STS] status bit (if not, then IRQ[11:9, 7:3] are selected to be the PCI REQ# signals). BMREQ# is treated as an asynchronous input.                                                          |                 |             |                 |               |                |

| PNPCS[1:0]#. Plug and play chip select [1:0] outputs (alternate function to GPIO[23:22]; selected by PM[F7:F6]). These are programmable chip select for external ISA bus devices. They becomes active during ISA bus cycles to memory space or IO space as specified by C3A46[CS[1:0]MEM and CS[1:0]IO]. They are valid for at least 1 PCLK cycle before and after the ISA-bus command signal (IOR#, IOW#, MEMR#, or MEMW#). |                 |             |                 |               |                |

| PNPCS1#. Output; plug and play chip select 1 (alternate function to GPIO23; selected by PMF7). This is designed to be a programmable chip select to external ISA bus devices. It becomes active during ISA bus cycles to memory space or IO space as specified by C3A46[CS1MEM and CS1IO]. It is guaranteed to be valid before and after the ISA-bus command signal.                                                         |                 |             |                 |               |                |

| <b>INTIRQ8#.</b> Real time clock interrupt output. This is the interrupt output from the IC's real-time clock. This pin may also be configured as GPIO16 by PMD0.                                                                                                                                                                                                                                                            |                 | VDD3        | High            | High          | Func.          |

| SQWAVE. Square wave clock output (alternate function to INTIRQ8#; selected by PMD0). This is a square wave output, the frequency for which is specified by C3A4E.                                                                                                                                                                                                                                                            |                 |             |                 |               |                |

| <b>INTRUDER#.</b> Intruder detection. This controls PM46[INTRDR_STS]. This pin is not 5-volt tolerant.                                                                                                                                                                                                                                                                                                                       | Input           | VDD_<br>AL  | Input           | Input         | Input          |

| <b>PCISTOP#.</b> PCI bus clock stop output. This may be used to control the system clock chip to control the PCI bus clock signals. It is controlled by C3A50. This pin may also be configured as GPIO7 by PMC7.                                                                                                                                                                                                             | ΙΟ              | VDD3        | High            | High          | Func.          |

| <b>PME#.</b> Power management interrupt. This pin may be used to generate                                                                                                                                                                                                                                                                                                                                                    | Input           | VDD_        | -               | -             | -              |

| SMI or SCI interrupts and resume events. It controls PM20[PME_STS].<br>PRDY. Processor ready. When this is asserted, the IC freezes the timers                                                                                                                                                                                                                                                                               | Input,          | AUX<br>VDD3 | -               | _             | -              |

| specified by C3A4C.                                                                                                                                                                                                                                                                                                                                                                                                          | IO              | UDD         |                 |               |                |

| <b>PWRBTN#.</b> Power button. This may be used to control the automatic transition from a sleep state to FON. It controls PM00[PWRBTN_STS]. Also, if it is asserted for four seconds from any state other than SOFF, then                                                                                                                                                                                                    | Input           | VDD_<br>AUX | -               | -             | -              |

Preliminary Information

AMD:

AMD-766<sup>TM</sup> Peripheral Bus Controller Data Sheet

| Pin name and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IO cell<br>type | Power plane | During<br>Reset | Post<br>Reset | POS   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|-----------------|---------------|-------|

| a power button override event is generated. A power button override event causes the PWRON# pin to be driven high and PM00[PBOR_STS] to be set high. The logic for this pin includes a 16 millisecond debounce circuit; the signal must be stable for about 16 milliseconds before it is detected by the rest of the internal logic.                                                                                                                                                                                                                                                                             |                 |             |                 |               |       |

| <b>PWRGD.</b> Power good. This is required to be low while the VDD3 power plane is not valid, stay low for at least 50 milliseconds after it becomes valid, and then go high. It is the reset source for the VDD3 logic in the IC. The rising edge of this pin is debounced for one to two 32 kHz (RTC) clocks before it is internally detected as being high.                                                                                                                                                                                                                                                   | Input<br>w/H    | VDD_<br>AUX | -               | -             | -     |

| <b>PWRON#.</b> Main power on. This is designed to control the main power supplies to the system board, including the IC's VDD3 plane. It is asserted during the FON, C2, C3, and POS states; it is deasserted during the STR, STD and SOFF states. See section 4.6.1.5 for more details.                                                                                                                                                                                                                                                                                                                         | OD              | VDD_<br>AUX | Low             | Low           | Low   |

| <b>RI#.</b> Ring indicate. This pin may be used to generate SMI or SCI interrupts and resume events. It controls PM20[RI_STS]. This pin may also be configured as GPIO14 by PMCE.                                                                                                                                                                                                                                                                                                                                                                                                                                | Input,<br>IO    | VDD_<br>AUX | -               | -             | -     |

| <b>RPWRON.</b> RAM power on. This is designed to control power to the system memory power plane. When high, it is expected that power to system memory is enabled. When low, it is expected that power to system memory is disabled. This pin is low during STD and SOFF and high in all other states. See section 4.6.1.5 for more details.                                                                                                                                                                                                                                                                     | OD              | VDD_<br>AUX | High            | High          | High  |

| <b>RTCX_IN.</b> Real time clock 32.768 kHz crystal input. This pin is designed to be connected through a crystal oscillator to RTCX_OUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Analog          | VDD_<br>AL  | Func.           | Func.         | Func. |

| <b>RTCX_OUT.</b> Real time clock 32.768 kHz crystal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Analog          | VDD_<br>AL  | Func.           | Func.         | Func. |

| <b>SERIRQ.</b> Serial IRQ function. This pin supports the serial IRQ protocol. Control for this is in C3A4A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ΙΟ              | VDD3        | -               | -             | Func. |

| <b>SLPBTN#.</b> Sleep button. This may be used to control the automatic transition from a sleep state to FON. It controls PM00[SLPBTN_STS]. Also, if it is asserted for four seconds from any state other than SOFF, then a power button override event is generated. A power button override event causes the PWRON# pin to be driven high and PM00[PBOR_STS] to be set high. The logic for this pin includes a 16 millisecond debounce circuit; the signal must be stable for about 16 milliseconds before it is detected by the rest of the internal logic. This pin may also be configured as GPIO3 by PMC3. | Input,<br>IO    | VDD_<br>AUX | -               | _             | -     |

| <b>SMBUSC.</b> System management bus (SMBus) clock. This pin may also be configured as GPIO0 by PMC0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I w/H /<br>OD   | VDD_<br>AUX | 3-state         | 3-state       | Func. |

| <b>SMBUSD.</b> System management bus (SMBus) data. This pin may also be configured as GPIO1 by PMC1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I w/H /<br>OD   | VDD_<br>AUX | 3-state         | 3-state       | Func. |

| <b>SUSPEND#.</b> Suspend output. This may be used during the POS state to control an external power planes. It is controlled by C3A50.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IO              | VDD3        | High            | High          | Func. |

| <b>THERM#.</b> Input; thermal warning detect. This may be used to automatically enable processor throttling as specified by C3A50[TTH_EN, TTH_RATIO]. See section 4.6.1.4 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                      | ΙΟ              | VDD3        | -               | -             | Func. |

#### 3.7 Universal Serial Bus Interface

| Pin name and description                                                     | IO cell | Power | During  | Post    | POS     |

|------------------------------------------------------------------------------|---------|-------|---------|---------|---------|

|                                                                              | type    | plane | Reset   | Reset   |         |

| USBCLK. 48 MHz USB clock.                                                    | Input   | VDD3  | -       | -       | -       |

| <b>USBOC0#.</b> USB over current detect 0. This is expected to become active | Input   | VDD3  | -       | -       | -       |

| to report the occurrence of an over-current condition on the voltage         |         |       |         |         |         |

| supplied to the USB ports.                                                   |         |       |         |         |         |

| USBP[3:0], USBN[3:0]. Analog; USB ports. These are four pairs of             | Analog  | VDD_  | 3-state | 3-state | 3-state |

| differential USB signals. USBP[3:0] are the positive signals and             |         | USB   |         |         |         |

| USBN[3:0] are the negative signals. These signals go into the high-          |         |       |         |         |         |

| impedance state during sleep states; internal logic may detect USB resume    |         |       |         |         |         |

| events while in these states and set the status bit, PM20[USB_RSM_STS].      |         |       |         |         |         |

#### 3.8 Miscellaneous Signals

| Pin name and description                                                      | IO cell | Power | During | Post  | POS |

|-------------------------------------------------------------------------------|---------|-------|--------|-------|-----|

|                                                                               | type    | plane | Reset  | Reset |     |

| <b>STRAPH[2:0].</b> These pins should be tied high through a pull-up resistor | Input   | VDD_  | -      | -     | -   |

| (to VDD_AUX).                                                                 |         | AUX   |        |       |     |

| <b>STRAPL[3:0].</b> These should be grounded on the system board.             | Input   | VDD3  | -      | -     | -   |

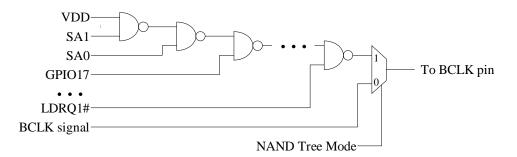

| <b>TEST#.</b> Scan, NAND tree, and high-impedance mode enable. See            | Input   | VDD3  | -      | -     | -   |

| section 9 for details.                                                        |         |       |        |       |     |

#### 3.9 Power And Ground

See section 4.6.1.5 for a description of the system power states. The following power and ground planes are connected to the IC through BGA pins.

VDD3. Main 3.3 volt supply. This plane is required to be valid in the FON and POS power states.

**VDD\_AUX.** Auxiliary 3.3 volt plane. This plane is required to be valid in all system power states except MOFF. The pins powered by these planes are: PWRBTN#, PWRON#, PME#, SMBUS[C,D], EXTSMI#, SLPBTN#, RI#, PWRGD, PCIRST#, RPWRON, DCSTOP#, STRAPH[2:0], STRAPL1. All register bits that are on the VDD\_AUX plane are reset by the internal RST\_SOFT pulse that is generated for about 30 milliseconds after VDD\_AUX becomes valid.

**VDD\_REF.** 5.0 volt reference supply. This plane is required to be valid in all power states except MOFF. It is expected that this plane is connected to a 5-volt power supply that is active in the SOFF (soft off) power state, i.e., the 5-volt version of VDD\_AUX from the power supply is required for this pin.

**VDD\_RTC.** Real-time clock 3.3 volt supply. This plane is required to be valid in all power states. It is typically powered by a battery. It supplies power for the internal VDD\_AL power plane when VDD\_AUX is not valid.

**VDD\_USB.** 3.3 volt supply filtered for the USB transceivers. This plane is required to be valid in all power states except MOFF.

**VSS.** Main ground plane.

VSS\_USB. Ground plane filtered for the USB transceivers.

The IC also includes the following internal power plane.

**VDD\_AL.** VDD always. This is an internal plane. It is supplied by VDD\_AUX when that plane is valid or by VDD\_RTC when VDD\_AUX is not valid. VDD\_AL powers the real-time clock and some system management circuitry. The pins powered by VDD\_AL are: RTCX\_IN, RTCX\_OUT, INTRUDER#.

#### 4 Functional Operation

The IC connects to the host memory controller through PCI bus interface as described in section 1.1.

The IC supports processor accesses to BIOS on either the ISA bus or the LPC bus as specified by the ISABIOS pin.

See section 5.1 for details about the software view of the IC. See section 5.1.2 for a description of the register naming convention.

#### 4.1 Overview

#### 4.1.1 Resets

The IC generates an internal reset for the VDD\_AUX power plane called RST\_SOFT. RST\_SOFT lasts for about 30 milliseconds after the VDD\_AUX plane is greater than 2.5 volts. See section 4.6.1.5.1 for details.

PWRGD is the source of reset for some of the IC's VDD3 logic. From this signal, RESET# and CPURST# are derived. See section 4.6.1.5.1 for details.

It is possible to generate system resets via COA47[SWPCIR].

Various system resets may be initiated through PORTCF9.

It is also possible to reset the processor (without clearing the cache) with an INIT interrupt through the keyboard controller via KBRC#, the PORT92 register, or from a PCI-defined shutdown special cycle from the host.

#### 4.2 PCI Interface

The IC connects to the host through a 32-bit, 33 MHz PCI interface.

#### 4.2.1 Subtractive Versus Medium Decoding

PCI target accesses to the IC are acknowledged with DEVSEL# using either PCI-defined *medium* or *subtractive* decoding. The following equation specifies the timing based on the address space and configuration. See section 10.3 for a description of the logic convention.

```

START_OF_DEVSEL = (PCI_COMMAND != SPECIAL_CYCLE) &

( FRAME3 & ~DEVSEL & (PCI_COMMAND == 2, 3, 6, 7, 12, 14, or 15) &

// subtractive window

(COA48[SUB] != 1Xb)