## PI74LVC3245A

# 8-Bit Dual Supply Bus Transceiver with 3-State Outputs

#### **Product Features**

- 2.7V to 3.6V on A-port and 4.5V to 5.5V on B-port

- TTL Compatible Inputs

- Latch-up performance exceeds 200mA Per JESD78

- ESD protection exceeds JESD22

2000V Human-Body Model (A114-B) 200V Machine Model (A115-A)

- Industrial Temperature: -40°C to +85°C

- · Available Packages:

24-pin 173-mil wide plastic TSSOP (L)

24-pin 150-mil wide plastic QSOP (Q)

24-pin 300-mil wide plastic SOIC (S)

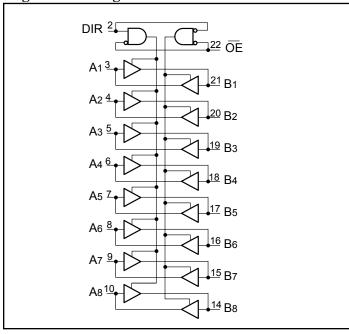

#### Logic Block Diagram

## Truth Table<sup>(1)</sup>

| Inp | outs | Outputs             |

|-----|------|---------------------|

| ŌĒ  | DIR  |                     |

| L   | L    | Bus B Data to Bus A |

| L   | Н    | Bus A Data to Bus B |

| Н   | X    | Z (Isolation)       |

#### Note

H = High Signal Level

X = Don't Care or Irrelevant

L = Low Signal Level Z = High Impedance

1

#### **Product Description**

Pericom Semiconductor's PI74LVC series of logic circuits are produced using the Company's advanced submicron CMOS technology, achieving industry leading speed.

The PI74LVC3245A is a non-inverting 8-bit Bidirectional Transceiver that uses two seperate power supply rails. A-port ( $V_{CCA}$ ) is set to operate at 3.3V and B-port ( $V_{CCB}$ ) is set to operate at 5V. This allows for translation from a 3.3V to a 5Venvironment and vice-versa. This tranceiver is designed for asynchronous two-way communication between data buses. The direction control input pin (DIR) determines the dataflow from the A bus to the B bus or from the B bus to the A bus. The output enable ( $\overline{\rm OE}$ ) input, when HIGH, disables both A and B ports by placing them in HIGH Z condition.

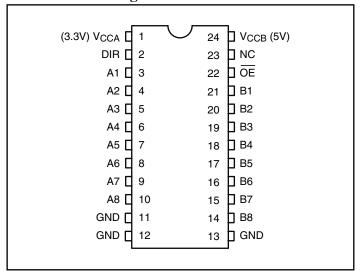

## **Product Pin Configuration**

#### **Product Pin Description**

| Pin Name                           | Description                               |

|------------------------------------|-------------------------------------------|

| ŌĒ                                 | 3-State Output Enable Inputs (Active LOW) |

| DIR                                | Direction Control Input                   |

| Ax                                 | Side A Inputs or 3-State Outputs          |

| Bx                                 | Side B Inputs or 3-State Outputs          |

| NC                                 | NO Internal Connect                       |

| GND                                | Ground                                    |

| V <sub>CCA</sub> ,V <sub>CCB</sub> | Power                                     |

#### ADVANCE INFORMATION

PI74LVC3245A 8-Bit Dual Supply Bus Transceiver with 3-State Outputs

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Supply voltage range, V <sub>CCA</sub> and V <sub>CCB</sub> | -0.5V to +7V                   |

|-------------------------------------------------------------|--------------------------------|

|                                                             | $-0.5V$ to $V_{CCA} + 0.5V$    |

| I/O ports (B-port)                                          | 0.5V to V <sub>CCB</sub> +0.5V |

| Control Pins                                                | $-0.5V$ to $V_{CCA} + 0.5V$    |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> <0)    | 50mA                           |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> <0)   | 50mA                           |

| Continous Output Current IO                                 | ±50mA                          |

| Continous Current through each V <sub>CC</sub> or GND pin   |                                |

| Package thermal impedance, $\theta_{JA}^{(3)}$ : package I  | 84°C/W                         |

| package (                                                   | 2 98°C/W                       |

| package S                                                   | S 79°C/W                       |

| Storage Temperature range, T <sub>stg</sub>                 | 65°C to 150°C                  |

#### **Notes:**

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. This value is limited to 7V maximum.

- 3. The package thermal impedance is calculated in accordance with JESD 51.

P-0.3 08/05/03

2

# Recommended Operating Conditions<sup>(4)</sup>

| Parameters         | Description                                |                                                                                                                                                     | V <sub>CCA</sub> | V <sub>CCB</sub> | Min. | Тур. | Max.             | Units |

|--------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------|------|------------------|-------|

| V <sub>CCA</sub>   | Supply Voltage                             | •                                                                                                                                                   |                  |                  | 2.7  | 3.3  | 3.6              |       |

| V <sub>CCB</sub>   | Supply Voltage                             |                                                                                                                                                     |                  |                  | 4.5  | 5    | 5.5              | ]     |

| V                  | TT' 1 T 1T 1T 1T 1T                        | $V_{OB} \le 0.1 v \text{ or}$                                                                                                                       | 2.7V             | 5.0V             | 2    |      |                  | 1     |

| $V_{\mathrm{IHA}}$ | High-Level Input Voltage                   | $V_{OB} \ge V_{CCB}$ -0.1V                                                                                                                          | 3.6V             | 5.0V             | 2    |      |                  | ]     |

| V                  | High-Level Input Voltage                   | $V_{OA} \le 0.1 V$ or                                                                                                                               | 3.3V             | 4.5V             | 2    |      |                  | ]     |

| $V_{\mathrm{IHB}}$ | riigh-Level input voitage                  | $V_{OA} \ge V_{CCA} - 0.1V$                                                                                                                         | 3.3V             | 5.5V             | 2    |      |                  |       |

| V                  | Low Lovel Innet Velters                    | $V_{OB} \le 0.1 V$ or                                                                                                                               | 2.7V             | 5.0V             |      |      | 0.8              |       |

| $V_{ILA}$          | Low-Level Input Voltage                    | $V_{OB} \ge V_{CCB} - 0.1V$                                                                                                                         | 3.6V             | 5.0V             |      |      | 0.8              | ]     |

| 3.7                | I am I am I I mat Walter a                 | $V_{OA} \le 0.1 V$ or                                                                                                                               | 3.3V             | 4.5V             |      |      | 0.8              | ]     |

| $V_{\rm ILB}$      | Low-Level Input Voltage                    | $V_{OA} \ge V_{CCA} - 0.1V$                                                                                                                         | 3.3V             | 5.5V             |      |      | 0.8              |       |

|                    |                                            | $V_{OA} \le 0.1 V$ or                                                                                                                               | 2.7V             | 4.5V             | 2    |      |                  | V     |

| $ m V_{IH}$        | High-Level Input Voltage<br>(Control Pins) | $\begin{split} V_{OA} &\geq V_{CCA} \text{ -0.1V}, \\ V_{OB} &\leq 0.1 \text{V or} \\ V_{OB} &\geq V_{CCB} \text{ -0.1V} \end{split}$               | 3.6V             | 5.5V             | 2    |      |                  |       |

|                    |                                            | $V_{OA} \le 0.1 V$ or                                                                                                                               | 2.7V             | 4.5V             |      |      | 0.8              | j     |

| $ m V_{IL}$        | Low-Level Input Voltage<br>(Control Pins)  | $\begin{split} V_{OA} &\geq V_{CCA} \text{-}0.1 \text{V}, \\ V_{OB} &\leq 0.1 \text{V or} \\ V_{OB} &\geq V_{CCB} \text{-}0.1 \text{V} \end{split}$ | 3.6V             | 5.5V             |      |      | 0.8              |       |

| V <sub>IA</sub>    | Input Voltage                              |                                                                                                                                                     |                  |                  | 0    |      | $V_{CCA}$        | 1     |

| $V_{\mathrm{IB}}$  | Input Voltage                              |                                                                                                                                                     |                  |                  | 0    |      | V <sub>CCB</sub> |       |

| V <sub>OA</sub>    | Output Voltage                             |                                                                                                                                                     |                  |                  | 0    |      | V <sub>CCA</sub> |       |

| V <sub>OB</sub>    | Output Voltage                             |                                                                                                                                                     |                  |                  | 0    |      | V <sub>CCB</sub> |       |

| т                  | High I and Ontone Comment                  |                                                                                                                                                     | 2.7V             | 4.5V             |      |      | -12              |       |

| $I_{OHA}$          | High-Level Output Current                  |                                                                                                                                                     | 3V               | 4.5V             |      |      | -24              |       |

| I <sub>OHB</sub>   | High-Level Output Current                  |                                                                                                                                                     | 3V               | 4.5V             |      |      | -24              | mA    |

| I <sub>OLA</sub>   | Low-Level Output Current                   |                                                                                                                                                     | 2.7V             | 4.5V             |      |      | 12               |       |

|                    |                                            |                                                                                                                                                     | 3V               | 4.5V             |      |      | 24               |       |

| I <sub>OLB</sub>   | Low-Level Output Current                   |                                                                                                                                                     | 3V               | 4.5V             |      |      | 24               | 1     |

| Δt/Δv              | Input transition Rise or Fall Rate         |                                                                                                                                                     |                  |                  |      |      | 10               | ns/v  |

| T <sub>A</sub>     | Operating Free-Air Temp.                   |                                                                                                                                                     |                  |                  | -40  |      | 85               | °C    |

3

Note: 4. All unused inputs of the device must be held at the associated  $V_{CC}$  or GND to ensure proper device operation.

# **DC Electrical Characteristics** (Over the Operating Range, $T_A = -40$ °C +85°C)

| Parameters                     | Description                                                 | Test Conditions                                                                                                  | V <sub>CCA</sub> | V <sub>CCB</sub> | Min. | Тур. | Max. | Units |  |

|--------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------|------------------|------|------|------|-------|--|

|                                |                                                             | $I_{OH} = -100 \mu A$                                                                                            | 3V               | 4.5V             | 2.9  | 3    |      |       |  |

|                                | Minimum High Level Output Voltage (Port A)                  | I 12m A                                                                                                          | 2.7V             | 4.5V             | 2.2  | 2.55 |      |       |  |

| $V_{ m OHA}$                   |                                                             | $I_{OH} = -12mA$                                                                                                 | 3V               | 4.5V             | 2.4  | 2.8  |      |       |  |

|                                | Output voltage (1 oft 11)                                   | $I_{OH} = -24 \text{mA}$                                                                                         | 2.7V             | 4.5V             | 2    | 2.4  |      |       |  |

|                                |                                                             | I()H = -24IIIA                                                                                                   | 3V               | 4.5V             | 2.25 | 2.7  |      |       |  |

| $V_{ m OHB}$                   | Minimum High Level                                          | $I_{OH} = -100 \mu A$                                                                                            | 3V               | 4.5V             | 4.4  | 4.5  |      |       |  |

| VOHB                           | Output Voltage (Port B)                                     | $I_{OH} = -24 \text{mA}$                                                                                         | 3V               | 4.5V             | 3.76 | 4.21 |      | V     |  |

|                                |                                                             | $I_{OL} = 100 \mu A$                                                                                             | 3V               | 4.5V             |      | 0.01 | 0.1  |       |  |

| Vor                            | Maximum Low Level                                           | $I_{OL} = 12mA$                                                                                                  | 2.7V             | 4.5V             |      | 0.09 | 0.44 |       |  |

| $V_{OLA}$                      | Output Voltage (Port A)                                     | I o z = 24m A                                                                                                    | 2.7V             | 4.5V             |      | 0.18 | 0.5  |       |  |

|                                |                                                             | $I_{OL} = 24mA$                                                                                                  | 3V               | 4.5V             |      | 0.18 | 0.44 |       |  |

| Vors                           | Maximum Low Level                                           | $I_{OL} = 100 \mu A$                                                                                             | 3V               | 4.5V             |      | 0.01 | 0.1  |       |  |

| $V_{ m OLB}$                   | Output Voltage (Port B)                                     | $I_{OL} = 24mA$                                                                                                  | 3V               | 4.5V             |      | 0.18 | 0.44 | 1     |  |

| $I_{\mathrm{I}}$               | Maximum Input Leakage<br>Current (Control Inputs)           | $V_{\rm I} = V_{\rm CCA}$ or GND                                                                                 | 3.6V             | 5.5V             |      |      | ±1   |       |  |

| I <sub>OZ</sub> <sup>(5)</sup> | Maximum 3-State Output<br>Leakage Current (A or B<br>ports) | $V_{I} = V_{IL} \text{ or } V_{IH}, \overline{OE} = V_{CCA}$ $V_{O} = V_{CCA/B} \text{ or GND}$                  | 3.6V             | 5.5V             |      |      | ±5   | μΑ    |  |

| I <sub>CCA</sub>               | Quiescent V <sub>CCA</sub> Supply Current                   | B to A, B-Port = $V_{CCB}$ or GND, $I_{O}$ (A port) = 0                                                          | 3.6V             | 5.5V             |      |      | 10   |       |  |

| I <sub>CCB</sub>               | Quiescent V <sub>CCB</sub><br>Supply Current                | A to B, A port = $V_{CCA}$ or GND, $I_{O}$ (B port) = 0                                                          | 3.6V             | 5.5V             |      |      | 10   |       |  |

|                                | I <sub>CC</sub> per input (A port)                          |                                                                                                                  | 3.6V             | 5.5V             |      |      | 50   |       |  |

|                                | I <sub>CC</sub> per input ( $\overline{\rm OE}$ )           | One input $V_I = V_{CCA} - 0.6V$ , other inputs = $V_{CCA}$ or GND, DIR = $V_{CCA}$                              | 3.6V             | 5.5V             |      |      | 50   | uA    |  |

| $\Delta I_{CC}^{(6)}$          | I <sub>CC</sub> per input (DIR)                             | $V_{I} = V_{CCA} - 0.6V, \text{ other}$ inputs = $V_{CCA}$ or GND, $\overline{OE}$ = GND                         | 3.6V             | 5.5V             |      |      | 50   |       |  |

|                                | I <sub>CC</sub> per input (B Port)                          | One Input $V_I = V_{CCB} - 2.1V$ ,<br>other inputs = $V_{CCB}$ or<br>GND, $\overline{OE} = GND$ and DIR<br>= GND | 3.6V             | 5.5V             |      | 0.7  | 1.5  | mA    |  |

#### Notes:

5. For I/O ports, the parameter I<sub>OZ</sub> includes the input leakage current.

6. This is the increase in supply current for each input that is at one of the specified voltage levels, rather than 0V or the associated V<sub>CC</sub>.

4

## **Capacitance** $(T_A = 25^{\circ}C)$

| Param-<br>eters  | Description                               | Test Conditions                                             |                        | Тур. | Units |

|------------------|-------------------------------------------|-------------------------------------------------------------|------------------------|------|-------|

| $C_{IN}$         | Control Input Capacitance                 | $V_I = V_{CCA}$ or GND, $V_{CCA} = Open$ , $V_{CCB} = Open$ |                        | 2.8  |       |

| C <sub>I/O</sub> | Input/Output Capacitance<br>(A or B port) | $V_{I/O} = V_{CCA/B}$ or GN                                 | 9                      | pF   |       |

| C                | Power Dissipation                         | Outputs Enabled $V_{CCA} = 3.3V, V_{CCB} = 5V$              |                        | 22   |       |

| $C_{PD}$         | Capacitance (7)                           | Outputs Disabled                                            | $C_L = 0pF, f = 10MHz$ | 2.2  |       |

#### **Notes:**

## AC Electrical Characteristics (Over Operating Range, $T_A = -40$ °C to +85°C)

|                    |              |                            | $V_{CCA} = 2.7V \text{ to } 3.6V$ | $V_{CCA} = 2.7V \text{ to } 3.6V, V_{CCB} = 5V \pm 0.5V$ |       |  |

|--------------------|--------------|----------------------------|-----------------------------------|----------------------------------------------------------|-------|--|

| Parameters         | From (Input) | To (Output)                | $C_L = 50 pF$                     | $R_L = 500\Omega$                                        | Units |  |

|                    |              |                            | Min.                              | Max.                                                     |       |  |

| $t_{ m PHL}$       | A            | В                          | 1.0                               | 6.3                                                      |       |  |

| $t_{\rm PLH}$      | A            | Ð                          | 1.0                               | 6.0                                                      |       |  |

| $t_{ m PHL}$       | В            | A                          | 1.0                               | 5.7                                                      |       |  |

| $t_{\rm PLH}$      | D            | Α                          | 1.0                               | 6.0                                                      |       |  |

| $t_{\mathrm{PZL}}$ | ŌĒ           | A                          | 1.0                               | 7.8                                                      |       |  |

| $t_{PZH}$          |              | A                          | 1.0                               | 7.5                                                      |       |  |

| t <sub>PZL</sub>   | ŌĒ           | В                          | 1.0                               | 7.8                                                      | ns    |  |

| t <sub>PZH</sub>   | OL           | Ð                          | 1.0                               | 7.6                                                      |       |  |

| $t_{\rm PLZ}$      | ŌĒ           | A                          | 1.0                               | 7.0                                                      |       |  |

| $t_{PHZ}$          |              | A                          | 1.0                               | 7.5                                                      |       |  |

| $t_{\rm PLZ}$      | ŌĒ           | В                          | 1.0                               | 7.0                                                      |       |  |

| $t_{PHZ}$          |              | D                          | E D                               | 1.0                                                      | 7.3   |  |

| t <sub>SK(O)</sub> | Output-to-   | Output Skew <sup>(8)</sup> |                                   | 1.5                                                      |       |  |

#### Note:

8. Skew between any two outputs of the same device, switching in the same direction. Parameter guaranteed by design.

5

C<sub>PD</sub> is defined as the value of the internal equivalent capacitance which is derived from dynamic operating current consumption (I<sub>CCD</sub>) at no output loading and operating at 50% duty cycle, C<sub>PD</sub> is related to I<sub>CCD</sub> dynamic operating current by the expression: I<sub>CCD</sub> = (C<sub>PD</sub>)(V<sub>CC</sub>)(f<sub>IN</sub>) +(I<sub>CC</sub> static)

#### **Power- Up Considerations**

To avoid excessive supply current, bus contention or oscillation during power-up, the following guidelines should be followed:

- 1. Connect ground first before any supply voltage is applied.

- 2. Power up V<sub>CCA</sub>, which is the control side of the device.

- 3. Ramp  $\overline{OE}$  ahead of or with  $V_{CCA}$  to help prevent bus contention

- 4. Ramp DIR with V<sub>CCA</sub> if DIR high is needed (A bus to B bus). Otherwise keep DIR Low.

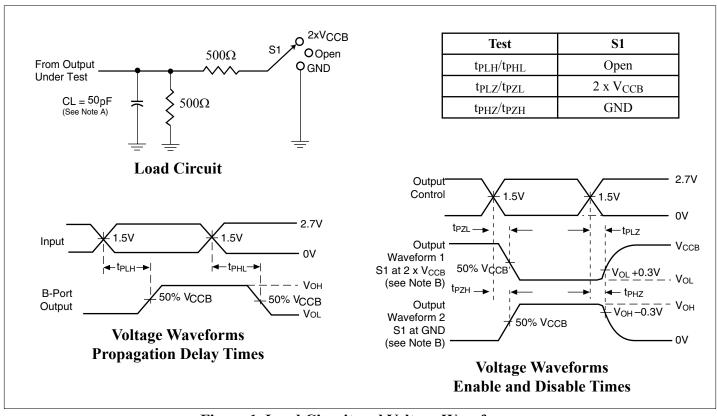

# PARAMETER MEASUREMENT INFORMATION FOR A TO B PORT $V_{CCA}$ =2.7V TO 3.6V and $V_{CCB}$ = 5V ± 0.5V

Figure 1. Load Circuit and Voltage Waveforms

6

#### Notes:

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input impulses are supplied by generators having the following characteristics:  $PRR \le 10 \text{ MHz}$ ,  $Z_O = 50\Omega$ ,  $t_R \le 2.5 \text{ns}$ ,  $t_F \le 2.5 \text{ns}$ .

- D. The outputs are measured one at a time with one transition per measurement.

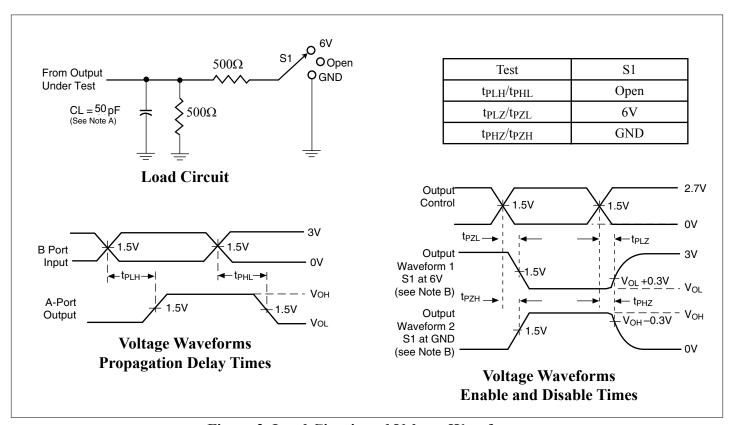

# PARAMETER MEASUREMENT INFORMATION FOR B TO A PORT $V_{CCA}$ =2.7V TO 3.6V and $V_{CCB}$ = 5V ± 0.5V

Figure 2. Load Circuit and Voltage Waveforms

7

#### **Notes:**

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input impulses are supplied by generators having the following characteristics:  $PRR \le 10 \text{ MHz}$ ,  $Z_O = 50\Omega$ ,  $t_R \le 2.5 \text{ns}$ ,  $t_F \le 2.5 \text{ns}$ .

- D. The outputs are measured one at a time with one transition per measurement.

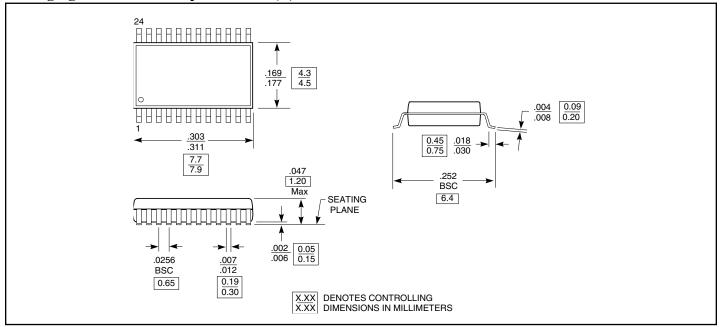

# Packaging Mechanical: 24-pin TSSOP (L)

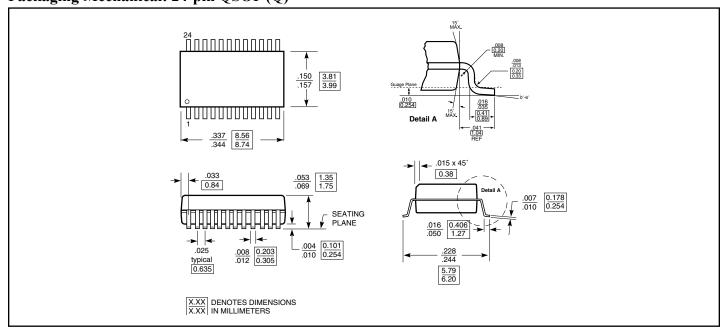

# Packaging Mechanical: 24-pin QSOP (Q)

8

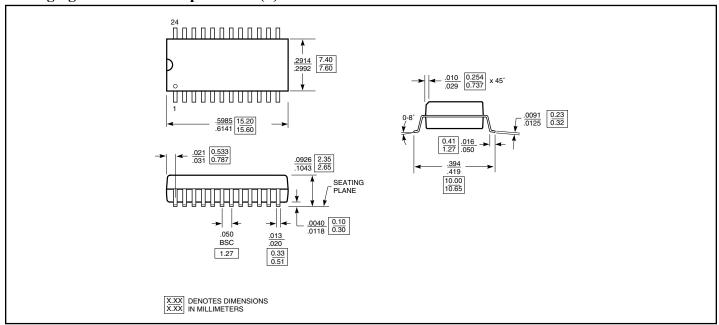

## Packaging Mechanical: 24-pin SOIC (S)

## **Ordering Information**

| Ordering Code | Package Code | Package Type                       |

|---------------|--------------|------------------------------------|

| PI74LVC3245AL | L            | 24-pin, 173-mil wide plastic TSSOP |

| PI74LVC3245AQ | Q            | 24-pin, 150-mil wide plastic QSOP  |

| PI74LVC3245AS | S            | 24-pin, 300-mil wide plastic SOIC  |

#### **Notes:**

1. Thermal characteristics can be found on the company web site at http://www.pericom.com/packaging/mechanicals.php

**Pericom Semiconductor Corporation**

2380 Bering Drive • San Jose, CA 95131 • 1-800-435-2336 • Fax (408) 435-1100 • http://www.pericom.com