|        | GENETAL DERCEMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2 |

|        | WEDITAL CURESTICATIONS NO. ON THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3 |

| $\Box$ | HIGH-CURRENT INTERFACE DRIVERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4 |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 |

|        | ogiet and Decrees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6 |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7 |

|        | Parantina de la companyo de la compa | 8 |

### SECTION 4-HIGH-CURRENT (≥1 A) INTERFACE DRIVERS

| Selection Guide                                                  | . 4-2          |

|------------------------------------------------------------------|----------------|

| ULN-2061M through 2075B 1.5 A Darlington Switches                | . 4-3          |

| UDN-2540B Quad 1.25 A Power Driver.                              | 4-14           |

| UDN-2545B Universal Quad 2.5 A Driver                            | 4~17           |

| UDN-2841B and 2845B Quad 1.5 A Darlington Drivers                | 4-19           |

| UDN-28/8W and 2879W Quad 4 A Darlington Switches                 | $A_{-}2^{\mu}$ |

| UDN-2906W 3-Phase 2 A Brushless DC Motor Driver                  | 4-2            |

| UDN-2931B/W 3-Channel 2 A Half-Bridge Drivers                    | 4-31           |

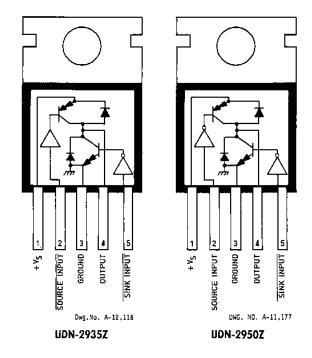

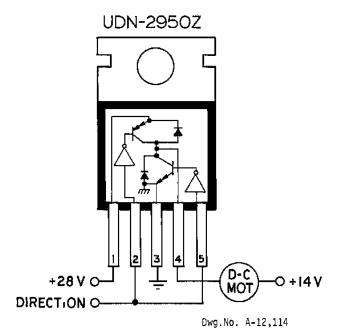

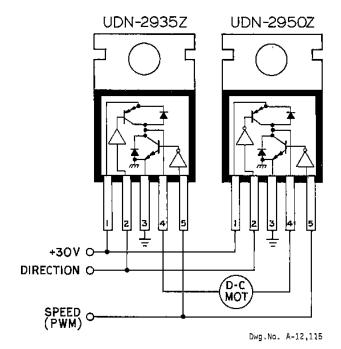

| UDN-2935Z 2 A Half-Bridge Motor Driver                           | 4-34           |

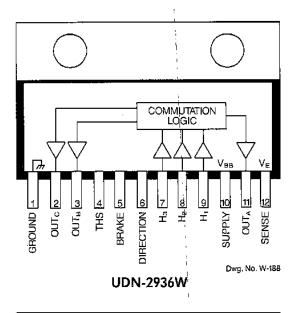

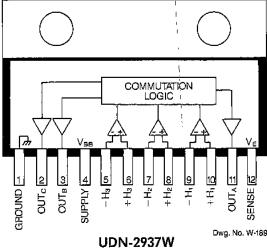

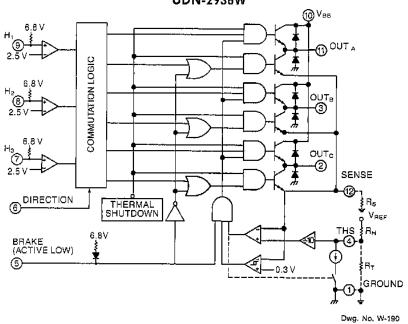

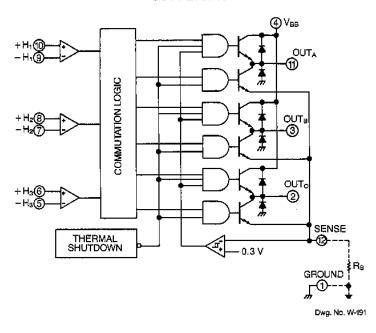

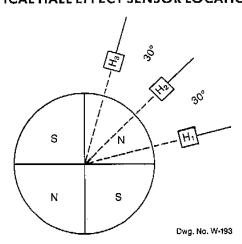

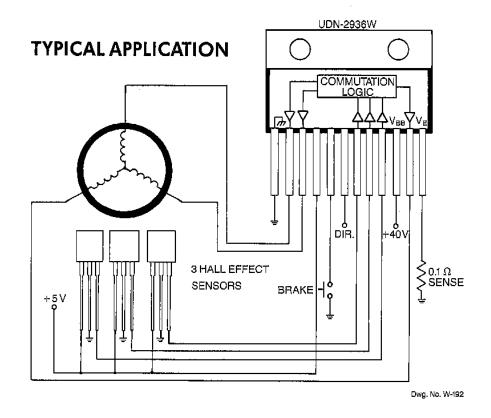

| UDN-2936W and 2937W 3-Phase 3 A Brushless DC Motor Drivers       | 4-40           |

| UDN-2938W and 2939B 3-Phase 4 A Brushless DC Motor Drivers       | 4-46           |

| UDN-2941B Quad 2 A Source Driver                                 | 4-48           |

| UDN-2943Z 1 A Half-Bridge Motor Driver                           | 4-51           |

| UDN-2944W Quad 4 A High-Voltage Source Driver                    | 4-55           |

| UDN-2948W Quad 6 A High-Voltage Source Driver                    | 4-58           |

| UDN-2949Z 2 A Half-Bridge Motor DriverSee, HDN-2                 | 9507           |

| UDN-2950Z 2 A Half-Bridge Motor Driver                           | 4-34           |

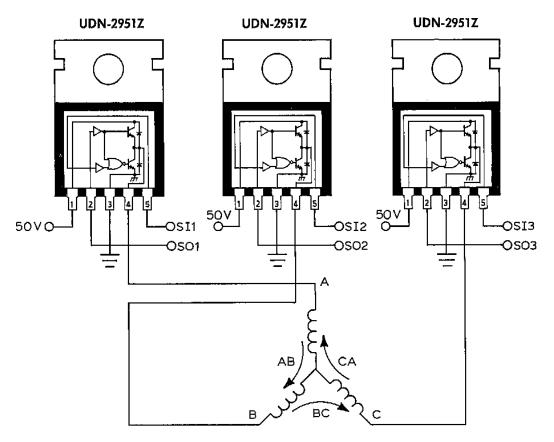

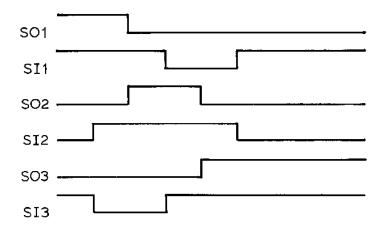

| UDN-2951Z & A Half-Bridge Driver                                 | 4-61           |

| UDN-2952B/W 2 A Full-Bridge Motor Drivers                        | 4-64           |

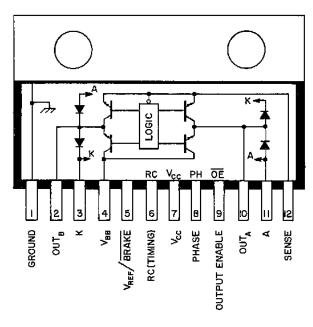

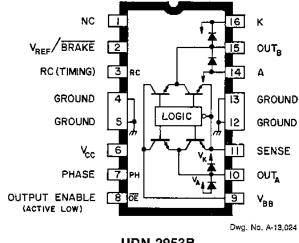

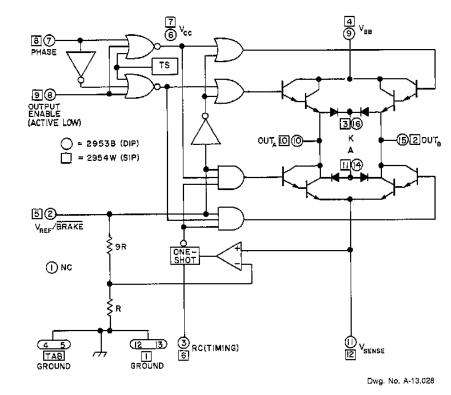

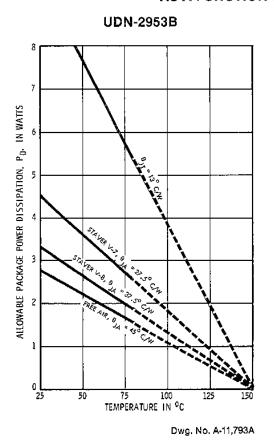

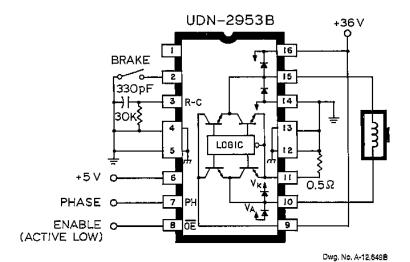

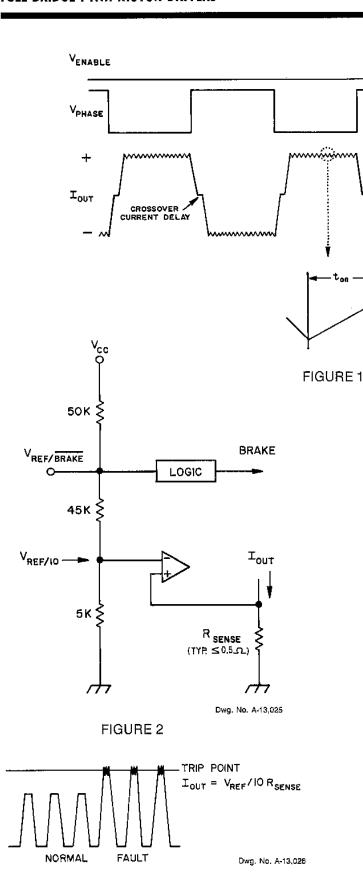

| UDN-2953B and 2954W 2 A Full-Bridge Motor Drivers                | 4-70           |

| UDN-2955W 8 A Half-Bridge Motor Driver                           | 4-61           |

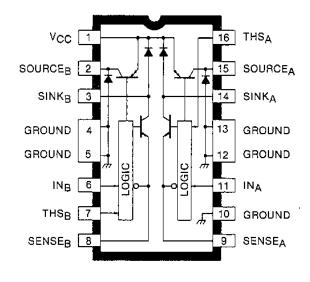

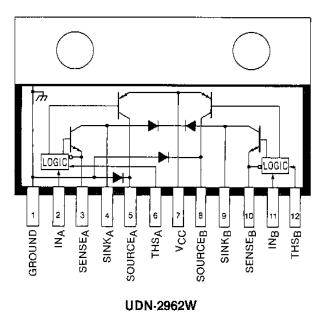

| UDN-2962B/W Dual 3 A PWM Solenoid/Motor Drivers                  | 4-75           |

| UDN-2965W-2 Dual 4 A Solenoid/Motor Driver                       | 4-81           |

| UDN-2975W and 2976W Dual 4 A Solenoid Drivers                    | 4-86           |

| UDN-2998W Dual 2 A Full-Bridge Motor Driver                      | 4-89           |

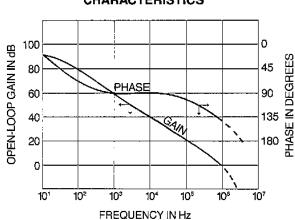

| ULN-3751Z Power Operational Amplifier                            | 4-93           |

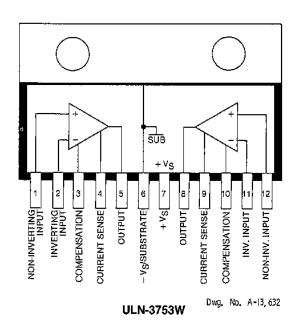

| ULN-3753B/W Dual Power Operational Amplifiers                    | 4-98           |

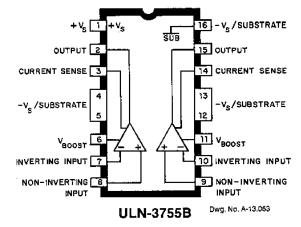

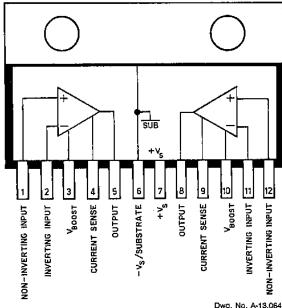

| ULN-3/55B/W Dual Power Operational Amplifiers                    | -107           |

| UUN-5/25M Dual Peripheral/Power Driver                           | -117           |

| UDN-7078 Quad High-Current Darlington Switches                   | -121           |

|                                                                  |                |

| Application Notes:                                               |                |

| Power Interface ICs for Motor Drive Applications                 | -124           |

| Switching Inductive Loads with Power Interface ICs               | -139           |

| An Integrated 3-Phase Brushless DC Motor Driver4                 | -143           |

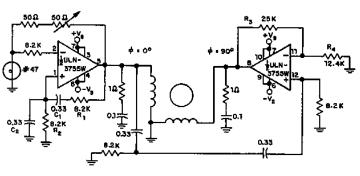

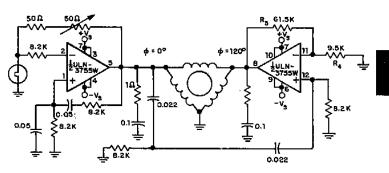

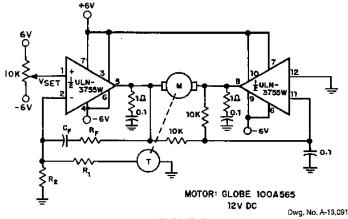

| Power Op Amp Applications                                        | -147           |

|                                                                  |                |

| See Also:                                                        |                |

| UCN-5813 and 5814B 4-Bit Latched 1.5 A Drivers                   | j- 41          |

| UCN-5825 and 5826B 4-Bit Serial-Input, Latched 2 A Drivers       | 5-59           |

| ULN-7064B through 7074B Quad High-Voltage, 1 A Darlington Arrays | 215            |

SELECTION GUIDE (in order of tested output current rating)

| l <sub>out</sub> | V <sub>out</sub> | Outputs           | Device Type        | Page  |

|------------------|------------------|-------------------|--------------------|-------|

| ± 1.0 A          | 26 V             | Half-Bridge       | UDN-2943Z          | 4-51  |

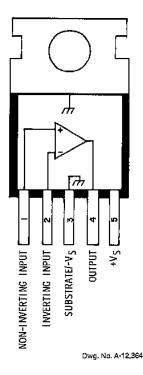

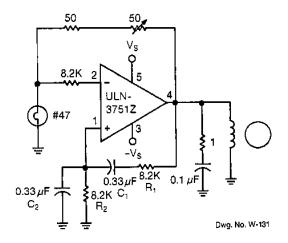

| ± 1.0 A Linear   | 28 V             | Power Op Amp      | ULN-3751Z          | 4-93  |

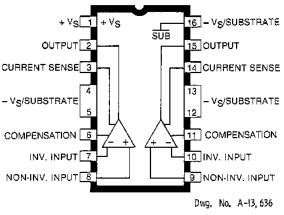

| ± 1.0 A Linear   | 40 V             | Dual Power Op Amp | ULN-3753B/W        | 4-98  |

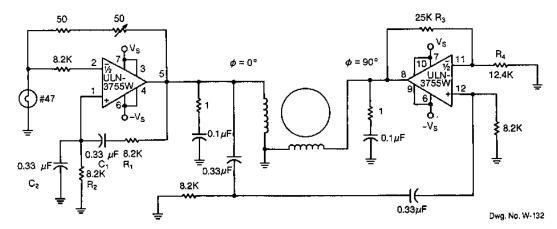

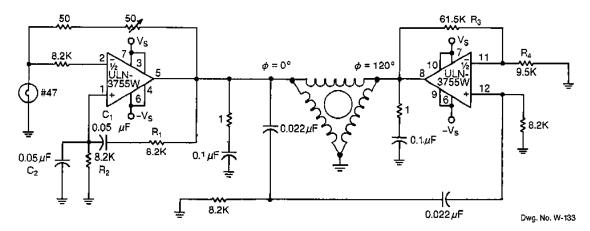

| ± 1.0 A Linear   | 40 V             | Dual Power Op Amp | ULN-3755B/W        | 4-107 |

| 1.0 A            | 50 V             | Sink 4†           | UCN-5813/14B       | 5-41  |

| 1.0 A            | 70 V             | Sink 2            | UDN-5725M          | 4-117 |

| 1.0 A            | 80 V             | Sink 4†           | UCN-5813/14B-1     | 5-41  |

| 1.0 A            | 150 V            | Sink 4            | ULN-7064/68/74B    | 2-15  |

| 1.25 A           | 50 V             | Source/Sink 2     | ULN-2061M          | 4-3   |

| 1.25 A           | 50 V             | Sink 4            | ULN-2064/66/68/70B | 4-3   |

| 1.25 A           | 50 V             | Source/Sink 4     | ULN-2074B          | 4-3   |

| 1.25 A           | 60 V             | Sink 4            | UDN-2540B          | 4-14  |

| — 1.5 A          | 35 V             | Source 4          | UDN-2941B          | 4-48  |

| 1.5 A            | — 50 V           | Sink 4            | UDN-2841/45B       | 4-19  |

| - 1.5 A          | - 50 V           | Ѕоцгсе 4          | UDN-2845B          | 4-19  |

| 1.5 A            | 80 V             | Source/Sink 2     | ULN-2062M          | 4-3   |

| 1.5 A            | 80 V             | Sink 4            | ULN-2065/67/69/71B | 4-3   |

| 1.5 A            | V 08             | Source/Sink 4     | ULN-2075B          | 4-3   |

| 1.75 A           | 60 V             | Sink 4†           | UCN-5825B          | 5-59  |

| 1.75 A           | V 08             | Sink 4†           | UCN-5826B          | 5-59  |

| ± 2.0 A          | 15 V             | 3 × Half-Bridge   | UDN-2906W          | *     |

| ± 2.0 A          | 15 V             | 3 × Half-Bridge   | UDN-2931B/W        | 4-31  |

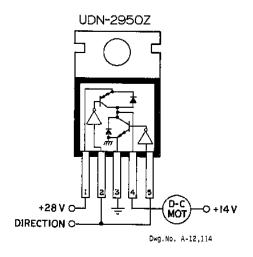

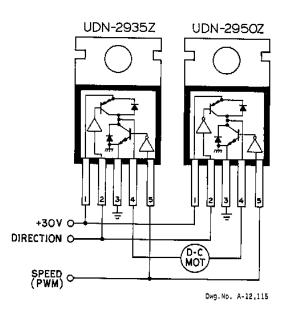

| $\pm 2.0 A$      | 35 V             | Half-Bridge       | UDN-2935/50Z       | 4-34  |

| ± 2.0 A          | 40 V             | Full-Bridge       | UDN-2952B/W        | 4-64  |

| ± 2.0 A          | 50 V             | Full-Bridge       | UDN-2953B/54W      | 4-70  |

| ± 2.0 A          | 50 V             | 2 × Full-Bridge   | UDN-2998W          | 4-89  |

| 2.0 A            | 80 V             | Sink 4            | UDN-2545B          | 4-17  |

| ± 3.0 A          | 45 V             | 3 × Half-Bridge   | UDN-2936/37W       | 4-40  |

| 3.0 A PWM        | 45 V             | Source/Sink 2     | UDN-2962W          | 4-75  |

| 3.0 A            | 90 V             | Sink 4            | UDN-7078W          | 4-121 |

| 4.0 A            | 50 V             | Sink 4            | UDN-2878W          | 4-25  |

| 4.0 A            | 50 V             | Sink 3            | UDN-2938W/39B      | 4-46  |

| 4.0 A            | 50 V             | Source/Sink 2     | UDN-2975W          | 4-86  |

| 4.0 A PWM        | 50 V             | Source/Sink 2     | UDN-2965W-2        | 4-81  |

| 4.0 A            | 60 V             | Source/Sink 2     | UDN-2976W          | 4-86  |

| - 4.0 A          | 60 V             | Source 4          | UDN-2944W          | 4-55  |

| 4.0 A            | 80 V             | Sink 4            | UDN-2879W          | 4-25  |

| — 6.0 A          | 60 V             | Source 4          | UDN-2948W          | 4-58  |

| ±8.0 A           | 50 V             | Half-Bridge       | UDN-2951Z/55W      | 4-61  |

Current ratings shown are maximum tested condition; allowable peak, or start-up currents are generally higher; voltage ratings shown are maximum allowable. Devices with ratings of less than 1 A are listed in Section 3.

<sup>†</sup>Latched Smart Power drivers.

\*New product. Contact factory for information.

### ULN-2061M THROUGH ULN-2075B 1.5 A DARLINGTON SWITCHES

#### **FEATURES**

- TTL, DTL, CMOS Compatible Inputs

- Transient-Protected Outputs

- Loads to 480 Watts

- Plastic Dual In-Line Packages

- Heat-Sink Contact Tabs on Quad Arrays

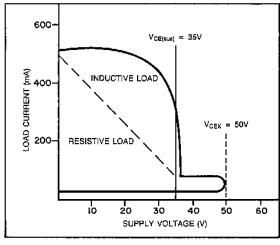

HIGH-VOLTAGE, HIGH-CURRENT Darlington arrays ULN-2061M through ULN-2075B are designed as interface between low-level logic and a variety of peripheral loads such as relays, solenoids, dc and stepper motors, multiplexed LED and incandescent displays, heaters, and similar loads to 480 watts (1.5 A per output, 80 V, 26% duty cycle).

The devices have a minimum output breakdown of 50 V and a minimum  $V_{CE(SUS)}$  of 35 V measured at 100 mA, or a minimum output breakdown of 80 V and a minimum  $V_{CE(SUS)}$  of 50 V.

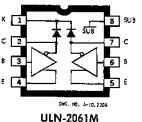

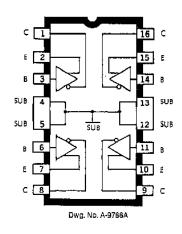

Dual-driver arrays ULN-2061M and ULN-2062M

ULN-2061M ULN-2062M

are used for common-emitter (externally connected), or emitter-follower applications. Both devices are supplied in miniature 8-pin dual in-line plastic packages.

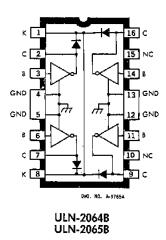

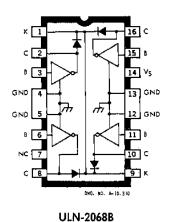

Quad drivers ULN-2064B, ULN-2065B, ULN-2068B and ULN-2069B are intended for use with TTL, low-speed TTL, and 5 V MOS logic. Types ULN-2065B and ULN-2069B are selected for the 80 V minimum output breakdown specification. Types ULN-2068B and ULN-2069B have predriver stages and are most suitable for applications requiring high gain (low input-current loading).

ULN-2069B

ULN-2074B ULN-2075B

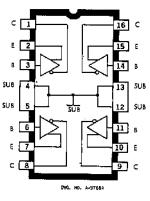

Isolated Darlington arrays ULN-2074B and ULN-2075B are identical to Types ULN-2064B and ULN-2065B except for the isolated Darlington pinout and the deletion of suppression diodes. These switches are for emitter-follower or similar isolated-Darlington applications.

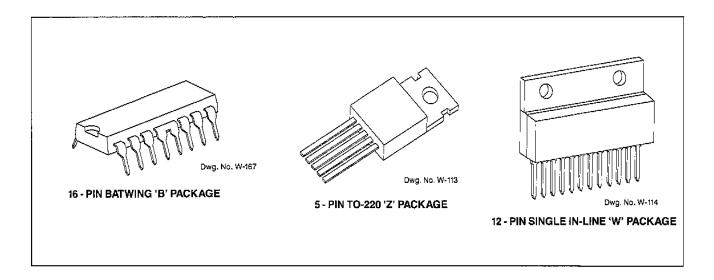

All quad Darlington arrays (suffix "B" devices) are supplied in a 16-pin plastic dual in-line package with heat-sink contact tabs. A copper-alloy lead frame provides maximum power dissipation using standard cooling methods. This lead configuration facilitates attachment of external heat sinks for increased power dissipation with standard IC sockets and printed wiring boards.

### **SELECTION GUIDE**

| Part      | MAX.             | Min.                 | Max.            | Application                          |

|-----------|------------------|----------------------|-----------------|--------------------------------------|

| Number    | V <sub>CEX</sub> | V <sub>CE(SUS)</sub> | V <sub>IN</sub> |                                      |

| ULN-2061M | 50 V             | 35 V                 | 30 V            | TTL, DTL, Schottky TTL,              |

| ULN-2062M | 80 V             | 50 V                 | 60 V            | and 5 V CMOS                         |

| ULN-2064B | 50 V             | 35 V                 | 15 V            | TTL, DTL, Schottky TTL               |

| ULN-2065B | 80 V             | 50 V                 | 15 V            | and 5 V CMOS                         |

| ULN-2068B | 50 V             | 35 V                 | 15 V            | TTL, DTL, Schottky TTL, and 5 V CMOS |

| ULN-2069B | 80 V             | 50 V                 | 15 V            |                                      |

| ULN-2074B | 50 V             | 35 V                 | 30 V            | General Purpose                      |

| ULN-2075B | 80 V             | 50 V                 | 60 V            |                                      |

### ABSOLUTE MAXIMUM RATINGS at + 25°C Free-Air Temperature for Any One Driver (unless otherwise noted)

| Output Voltage, V <sub>CEX</sub>                     | e Guide                 |

|------------------------------------------------------|-------------------------|

| Output Sustaining Voltage, V <sub>CE(SUS)</sub> Se   |                         |

| Output Current, Iour (Note 1)                        | 1.75 A                  |

| Input Voltage, V <sub>IN</sub> (Note 2) Se           | e Guide                 |

| Input Current, I <sub>a</sub> (Note 3)               | 25 mA                   |

| Supply Voltage, V <sub>s</sub> (ULN-2068/69B)        | . 10 V                  |

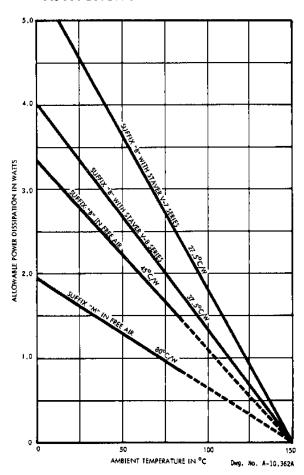

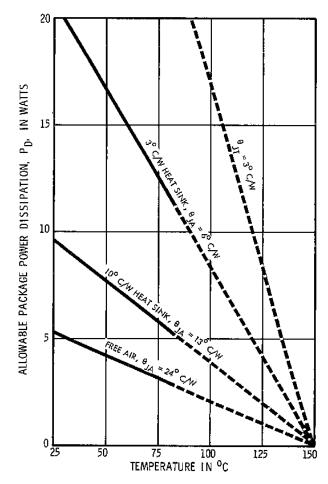

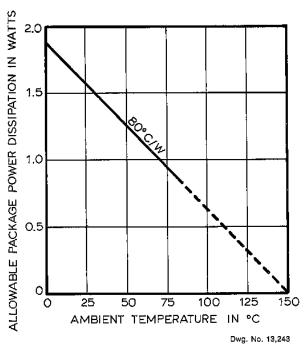

| Total Package Power Dissipation Se                   | e Graph                 |

| Operating Temperature Range, $T_A = -20^{\circ}C$ to | $+85^{\circ}\mathrm{C}$ |

| Storage Temperature Range, $T_s$                     |                         |

### NOTES:

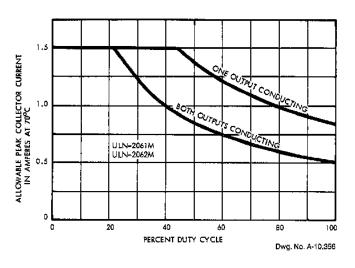

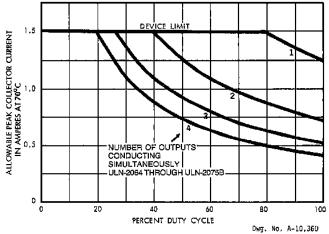

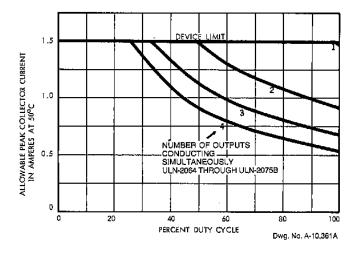

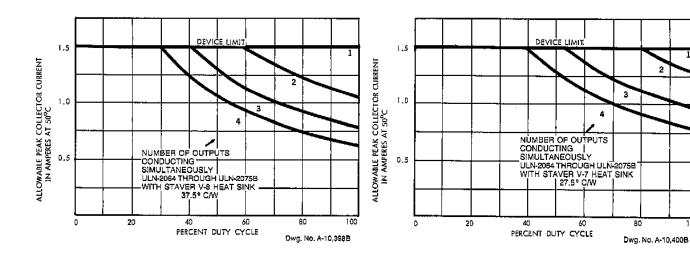

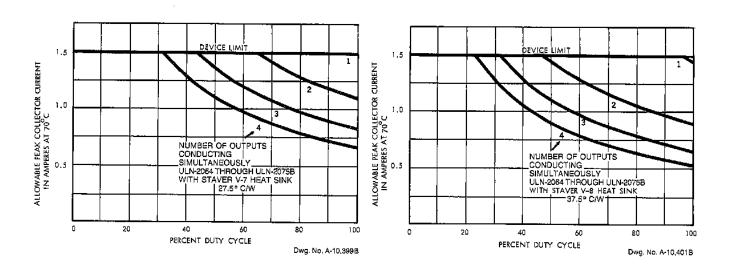

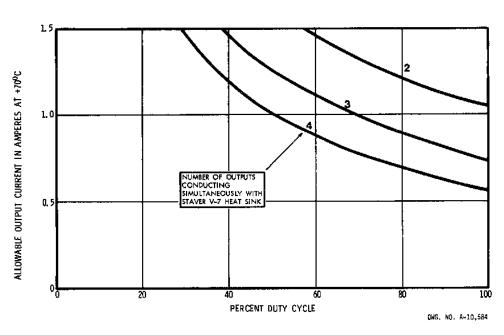

- Allowable combinations of output current, number of outputs conducting, and duty cycle are shown on following pages.

- Input voltage is referenced to the substrate (no connection to other pins) for Type ULN-2061/62M and ULN-2074/75B; reference is ground for all other types.

- 3. Input current may be limited by maximum allowable input voltage.

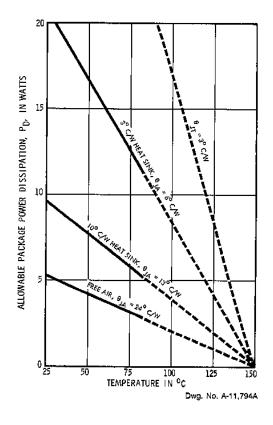

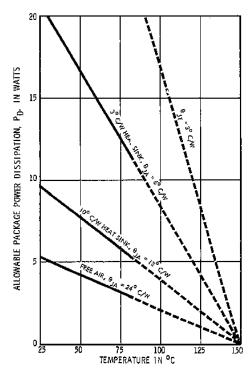

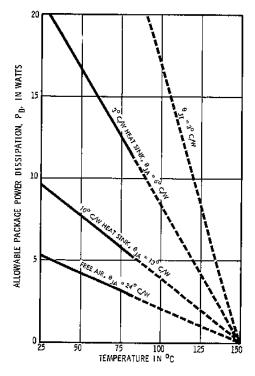

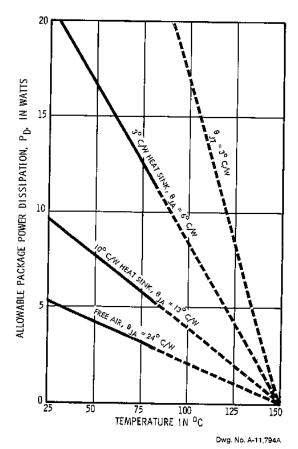

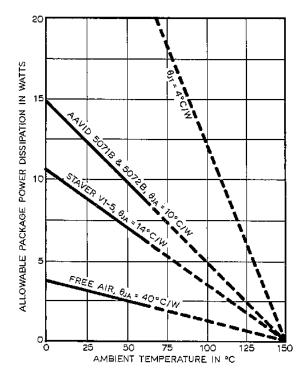

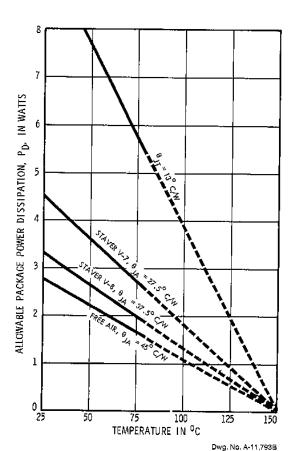

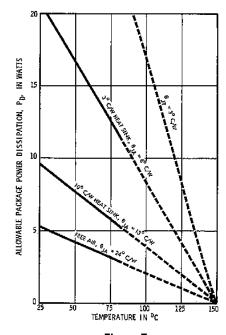

## ALLOWABLE POWER DISSIPATION AS A FUNCTION OF TEMPERATURE

### **ULN-2061M AND ULN-2062M**

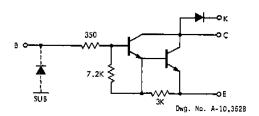

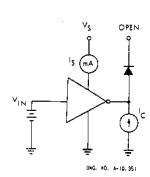

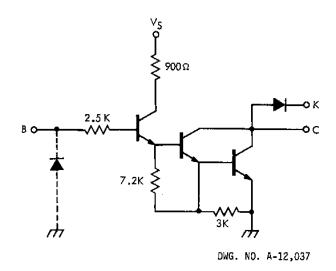

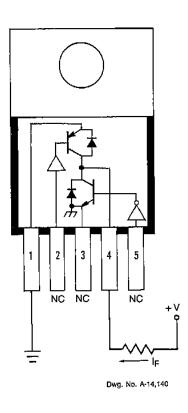

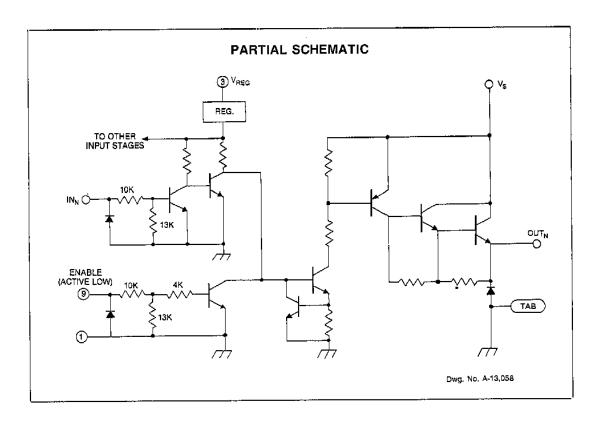

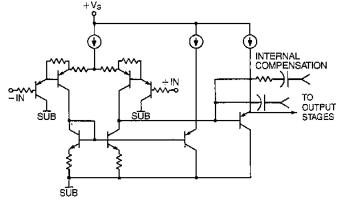

### **PARTIAL SCHEMATIC**

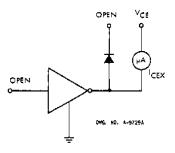

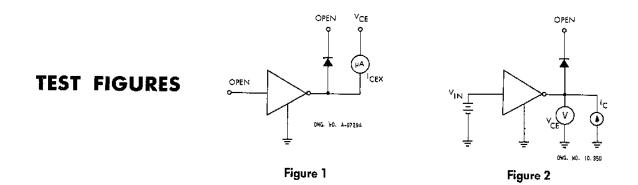

### ELECTRICAL CHARACTERISTICS at +25°C (unless otherwise noted)

|                           |                      | Test     | Applicable |                                                      |          | Limits |       |

|---------------------------|----------------------|----------|------------|------------------------------------------------------|----------|--------|-------|

| Characteristic            | Symbol               | Fig.     | Devices    | Test Conditions                                      | Min.     | Max.   | Units |

| Output Leakage Current    | I <sub>CEX</sub>     | 1        | ULN-2061M  | $V_{CE} = 50 \text{ V}$                              |          | 100    | μΑ    |

|                           |                      |          |            | $V_{CE} = 50 \text{ V}, T_A = 70^{\circ}\text{C}$    |          | 500    | μΑ    |

|                           |                      |          | ULN-2062M  | $V_{ce} = 80 \text{ V}$                              |          | 100    | μΑ    |

|                           | <u> </u>             |          |            | $V_{CE} = 80 \text{ V}, T_A = 70^{\circ}\text{C}$    | I —      | 500    | μΑ    |

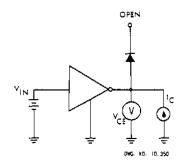

| Output Sustaining Voltage | V <sub>CE(SUS)</sub> | 2        | ULN-2061M  | $I_c = 100 \text{ mA}, V_{IN} = 0.4 \text{ V}$       | 35       | —      | ٧     |

|                           |                      | <u> </u> | ULN-2062M  | $I_c = 100 \text{ mA}, V_{IN} = 0.4 \text{ V}$       | 50       |        | ٧     |

| Collector-Emitter         | V <sub>CE(SAT)</sub> | 3        | Both       | $I_c = 500 \text{ mA}, I_B = 625 \mu\text{A}$        |          | 1.1    | γ     |

| Saturation Voltage        |                      |          |            | $I_{c} = 750 \text{ mA}, I_{B} = 935 \mu\text{A}$    | _        | 1.2    | V     |

|                           |                      |          |            | $I_{c} = 1.0 \text{ A}, I_{B} = 1.25 \text{ mA}$     | 1-511-   | 1.3    | ٧     |

|                           |                      |          |            | $I_{c} = 1.25  A^{+}, I_{B} = 2.0  \text{mA}$        |          | 1.4    | ٧     |

|                           |                      |          | ULN-2062M  | $I_c = 1.5  A^*, I_8 = 2.25  mA$                     | <u> </u> | 1.5    | ٧     |

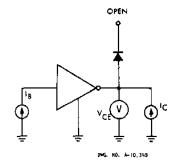

| Input Current             | I <sub>IN(ON)</sub>  | 4        | Both       | $V_{IN} = 2.4 \text{ V}$                             | 1.4      | 4.3    | mA    |

|                           |                      |          |            | $V_{IN} = 3.75 \text{ V}$                            | 3.3      | 9.6    | mA    |

| Input Voltage             | V <sub>IN(ON)</sub>  | 5        | Both       | $V_{CE} = 2.0  V_r  I_C = 1.0  A$                    | _        | 2.0    | ٧     |

|                           |                      |          | ULN-2061M  | $V_{CE} = 2.0V, I_{C} = 1.25 A^*$                    |          | 2.5    | ٧     |

|                           | <u></u>              |          | ULN-2062M  | $V_{cg} = 2.0 \text{ V, } I_{c} = 1.5 \text{ A}^{*}$ | _        | 2.5    | ٧     |

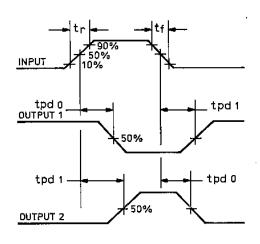

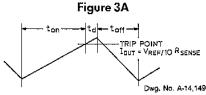

| Turn-On Delay             | t <sub>elH</sub>     |          | Both       | 0.5 E <sub>in</sub> to 0.5 E <sub>out</sub>          | *****    | 1.0    | μS    |

| Turn-Off Delay            | t <sub>PHL</sub>     |          | Both       | 0.5 E <sub>in</sub> to 0.5 E <sub>out</sub>          | <u> </u> | 1.5    | μS    |

| Clamp Diode               | I <sub>R</sub>       | 6        | ULN-2061M  | $V_R = 50 \text{ V}$                                 |          | 50     | μΑ    |

| Leakage Current           |                      |          |            | $V_R = 50 \text{ V}, T_A = 70^{\circ}\text{C}$       | <u> </u> | 100    | μΑ    |

|                           |                      |          | ULN-2062M  | $V_R = 80 \text{ V}$                                 |          | 50     | μΑ    |

|                           |                      |          |            | $V_R = 80 \text{ V}, T_A = 70^{\circ}\text{C}$       |          | 100    | μΑ    |

| Clamp Diode               | V <sub>F</sub>       | 7        | Both       | $I_F = 1.0 A$                                        |          | 1.75   | ٧     |

| Forward Voltage           |                      |          | <u></u>    | $I_{\rm F} = 1.5  {\rm A}$                           | _        | 2.0    | ٧     |

<sup>\*</sup>Pulse-Test

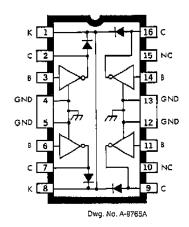

### **ULN-2064B AND ULN-2065B**

### **PARTIAL SCHEMATIC**

(SIMILAR TO ULN-2074B AND ULN-2075B)

### ELECTRICAL CHARACTERISTICS at ± 25°C (unless otherwise noted)

| ,                           |                      | Test | Applicable |                                                   |      | Limits |       |

|-----------------------------|----------------------|------|------------|---------------------------------------------------|------|--------|-------|

| Characteristic              | Symbol               | Fig. | Devices    | Test Conditions                                   | Min. | Max.   | Units |

| Output Leakage Current      | I <sub>CEX</sub>     | 1    | ULN-2064B  | V <sub>CE</sub> = 50 V                            | _    | 100    | μА    |

|                             |                      |      |            | $V_{CE} = 50 \text{ V}, T_A = 70^{\circ}\text{C}$ | _    | 500    | μА    |

|                             |                      |      | ULN-2065B  | $V_{CE} = 80 \text{ V}$                           | _    | 100    | μΑ    |

|                             |                      |      |            | $V_{CE} = 80 \text{ V}, T_A = 70^{\circ}\text{C}$ |      | 500    | μΑ    |

| Output Sustaining Voltage   | V <sub>CE(SUS)</sub> | 2    | ULN-2064B  | $I_{c} = 100 \text{ mA}, V_{IN} = 0.4 \text{ V}$  | 35   |        | V     |

|                             |                      |      | ULN-2065B  | $I_{c} = 100 \text{ mA}, V_{IN} = 0.4 \text{ V}$  | 50   | _      | ٧     |

| Collector-Emitter           | V <sub>CE(SAT)</sub> | 3    | Both       | $I_c = 500 \text{ mA}, I_B = 625 \mu\text{A}$     | _    | 1.1    | ٧     |

| Saturation Voltage          |                      |      |            | $I_{c} = 750 \text{ mA}, I_{B} = 935 \mu\text{A}$ |      | 1.2    | ٧     |

|                             |                      |      |            | $I_{c} = 1.0 \text{ A}, I_{B} = 1.25 \text{ mA}$  |      | 1.3    | V     |

|                             |                      |      |            | $I_{c} = 1.25  A, I_{B} = 2.0  mA$                | _    | 1.4    | ٧     |

|                             |                      |      | ULN-2065B  | $I_c = 1.5  A, I_8 = 2.25  mA$                    | _    | 1.5    | ٧     |

| Input Current               | I <sub>IN(ON)</sub>  | 4    | Both       | $V_{1N} = 2.4 \text{ V}$                          | 1.4  | 4.3    | mΑ    |

|                             |                      |      |            | $V_{IN} = 3.75 \text{ V}$                         | 3.3  | 9.6    | mΑ    |

| Input Voltage               | V <sub>IN(ON)</sub>  | 5    | Both       | $V_{ce} = 2.0  V, I_{c} = 1.0  A$                 | _    | 2.0    | ٧     |

|                             |                      |      | ULN-2064B  | $V_{ce} = 2.0  V, I_c = 1.25  A$                  |      | 2.5    | V     |

|                             |                      |      | ULN-2065B  | $V_{CE} = 2.0 \text{ V}, I_{C} = 1.5 \text{ A}$   |      | 2.5    | ٧     |

| Turn-On Delay               | t <sub>PLH</sub>     |      | Both       | 0.5 E <sub>in</sub> to 0.5 E <sub>out</sub>       |      | 1.0    | μς    |

| Turn-Off Delay              | t <sub>PPL</sub>     | _    | Both       | 0.5 E <sub>in</sub> to 0.5 <sub>out</sub>         | _    | 1.5    | μs    |

| Clamp Diode Leakage Current | I <sub>R</sub>       | 6    | ULN-2064B  | $V_R = 50 \text{ V}$                              | _    | 50     | μА    |

|                             |                      |      |            | $V_R = 50 \text{ V}, T_A = 70^{\circ}\text{C}$    |      | 100    | μΑ    |

|                             |                      |      | ULN-2065B  | $V_R = 80 \text{ V}$                              |      | 50     | μΑ    |

|                             |                      |      |            | $V_R = 80 \text{ V}, T_A = 70^{\circ}\text{C}$    |      | 100    | μA    |

| Clamp Diode Forward Voltage | V <sub>F</sub>       | 7    | Both       | $I_F = 1.0 A$                                     | _    | 1.75   | ٧     |

|                             |                      |      |            | $I_{\rm F} = 1.5  {\rm A}$                        |      | 2.0    | V     |

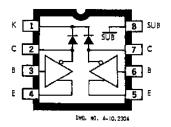

### ULN-2068B AND ULN-2069B

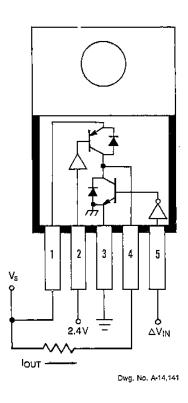

### **PARTIAL SCHEMATIC**

### ELECTRICAL CHARACTERISTICS AT $+25^{\circ}$ C, $V_s = 5.0 \text{ V}$ (unless otherwise noted)

|                             |                      | Test | Applicable |                                                                                     |      | Limits |       |

|-----------------------------|----------------------|------|------------|-------------------------------------------------------------------------------------|------|--------|-------|

| Characteristic              | Symbol               | Fig. | Devices    | Test Conditions                                                                     | Min. | Max.   | Units |

| Output Leakage Current      | I <sub>CEX</sub>     | 1    | ULN-2068B  | $V_{CE} = 50 \text{ V}$                                                             | _    | 100    | μA    |

|                             |                      |      |            | $V_{CE} = 50 \text{ V}, T_A = 70^{\circ}\text{C}$                                   | ,    | 500    | μA    |

|                             |                      |      | ULN-2069B  | $V_{CE} = 80 \text{ V}$                                                             | _    | 100    | μΑ    |

|                             |                      |      |            | $V_{CE} = 80 \text{ V}, T_A = 70^{\circ}\text{C}$                                   | _    | 500    | μА    |

| Output Sustaining Voltage   | V <sub>CE(SUS)</sub> | 2    | ULN-2068B  | $I_{\rm C}=100$ mA, $V_{\rm IN}=0.4$ V                                              | 35   |        | V     |

| <u></u>                     |                      |      | ULN-2069B  | $I_{c}=100$ mA, $V_{tN}=0.4$ V                                                      | 50   |        | ν     |

| Collector-Emitter           | VCE(SAT)             | 3    | Both       | $I_{c} = 500 \text{ mA}, I_{IN} = 2.75 \text{ V}$                                   | _    | 1.1    | V     |

| Saturation Voltage          |                      |      |            | $I_c = 750 \text{ mA}, I_{IN} = 2.75 \text{ V}$                                     |      | 1.2    | ٧     |

|                             |                      |      |            | $I_{\rm c} = 1.0  \rm A,  I_{\rm IN} = 2.75  \rm V$                                 |      | 1.3    | ٧     |

|                             |                      |      |            | $I_c = 1.25 \text{ A}, I_{IN} = 2.75 \text{ V}$                                     | _    | 1.4    | ٧     |

|                             |                      |      | ULN-2069B  | $I_{c} = 1.5 \text{ A}, I_{IN} = 2.75 \text{ V}$                                    | _    | 1.5    | ν     |

| Input Current               | I <sub>IN(ON)</sub>  | 4    | Both       | $V_{IN} = 2.75 V$                                                                   | L—   | 550    | μΑ    |

|                             | <u></u>              |      |            | $V_{IN} = 3.75 V$                                                                   |      | 1000   | μΑ    |

| Input Voltage               | V <sub>IN(ON)</sub>  | 5    | ULN-2068B  | $V_{ce} = 2.0  V,  I_c = 1.25  A$                                                   | _    | 2.75   | ٧     |

|                             |                      |      | ULN-2069B  | $V_{ce} = 2.0 \text{ V}, I_{c} = 1.5 \text{ A}$                                     |      | 2.75   | V     |

| Supply Current              | l <sub>s</sub>       | 8    | Both       | $I_c = 500 \text{ mA}, V_{IN} = 2.75 \text{ V}$                                     |      | 6.0    | mA    |

| Turn-On Delay               | t <sub>PLH</sub>     | _    | Both       | 0.5 E <sub>in</sub> to 0.5 E <sub>out</sub>                                         |      | 1.0    | μ\$   |

| Turn-Off Delay              | t <sub>PHL</sub>     |      | Both       | $0.5~\mathrm{E_{in}}$ to $0.5~\mathrm{_{out}}$ , $\mathrm{I_{C}} = 1.25~\mathrm{A}$ | _    | 1.5    | μs    |

| Clamp Diode Leakage Current | í <sub>R</sub>       | 6    | ULN-2068B  | $V_R = 50 \text{ V}$                                                                | _    | 50     | μΑ    |

|                             |                      |      |            | $V_R = 50 \text{ V}, T_A = 70^{\circ}\text{C}$                                      |      | 100    | μA    |

|                             |                      |      | ULN-2069B  | $V_R = 80 \text{ V}$                                                                | _    | 50     | μA    |

|                             |                      |      |            | $V_R = 80 \text{ V}, T_A = 70^{\circ}\text{C}$                                      |      | 100    | μΑ    |

| Clamp Diode Forward Voltage | V <sub>F</sub>       | 7    | Both       | $l_{\rm f} = 1.0  \rm A$                                                            |      | 1.75   | ٧     |

|                             |                      |      |            | $I_F = 1.5 A$                                                                       | _    | 2.0    | V     |

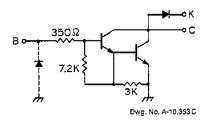

### **ULN-2074B AND ULN-2075B**

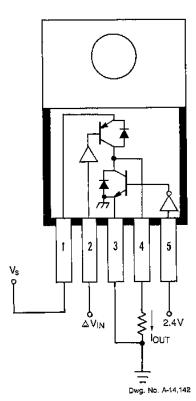

### **PARTIAL SCHEMATIC**

(SIMILAR TO ULN-2064B AND ULN-2065B)

### **ELECTRICAL CHARACTERISTICS at + 25°C (unless otherwise noted)**

|                           |                      | Test | Applicable |                                                   |      | Limits |       |

|---------------------------|----------------------|------|------------|---------------------------------------------------|------|--------|-------|

| Characteristic            | Symbol               | Fig. | Devices    | Test Conditions                                   | Min. | Max.   | Units |

| Output Leakage Current    | ICEX                 | 1    | ULN-2074B  | $V_{CE} = 50 \text{ V}$                           | _    | 100    | μА    |

|                           |                      |      |            | $V_{CE} = 50 \text{ V}, T_A = 70^{\circ}\text{C}$ | _    | 500    | μΑ    |

|                           |                      |      | ULN-2075B  | $V_{CE} = 80 \text{ V}$                           |      | 100    | μA    |

|                           |                      |      |            | $V_{CE} = 50 \text{ V}, T_A = 70^{\circ}\text{C}$ | _    | 500    | μΑ    |

| Output Sustaining Voltage | V <sub>CE(SUS)</sub> | 2    | ULN-2074B  | $I_{c} = 100 \text{ mA}, V_{IN} = 0.4 \text{ V}$  | 35   | _      | ٧     |

|                           |                      |      | ULN-2075B  | $I_{c} = 100 \text{ mA}, V_{IN} = 0.4 \text{ V}$  | 50   |        | ٧     |

| Collector-Emitter         | V <sub>CE(SAT)</sub> | 3    | Both       | $I_{c} = 500 \text{ mA}, I_{B} = 625 \mu\text{A}$ |      | 1.1    | ٧     |

| Saturation Voltage        |                      |      |            | $I_c = 750 \text{ mA}, I_B = 935 \mu A$           | _    | 1.2    | ٧     |

|                           |                      |      |            | $I_{c} = 1.0 \text{ A}, I_{B} = 1.25 \text{ mA}$  | _    | 1.3    | ٧     |

|                           |                      |      |            | $I_{c} = 1.25  A, I_{B} = 2.0  mA$                | —    | 1.4    | ٧     |

|                           |                      |      | ULN-2075B  | $I_{c} = 1.5 \text{ A}, I_{B} = 2.25 \text{ mA}$  | _    | 1.5    | ٧     |

| Input Current             | I <sub>IN(ON)</sub>  | 4    | Both       | $V_{tN} = 2.4 \text{ V}$                          | 1.4  | 4.3    | mА    |

|                           |                      |      |            | $V_{IN} = 3.75 V$                                 | 3.3  | 9.6    | mA    |

| Input Voltage             | V <sub>IN(ON)</sub>  | 5    | Both       | $V_{CE} = 2.0 \text{ V}, I_{C} = 1.0 \text{ A}$   | _    | 2.0    | ν.    |

|                           |                      |      | ULN-2074B  | $V_{CE} = 2.0 \text{ V}, I_{C} = 1.25 \text{ A}$  |      | 2.5    | ٧     |

|                           |                      |      | ULN-2075B  | $V_{CE} = 2.0 \text{ V}, I_{C} = 1.5 \text{ A}$   |      | 2.5    | ٧     |

| Turn-On Delay             | t <sub>PLH</sub>     | _    | Both       | 0.5 E <sub>in</sub> to 0.5 E <sub>out</sub>       | _    | 1.0    | μs    |

| Turn-Off Delay            | t <sub>PHL</sub>     |      | Both       | 0.5 E <sub>In</sub> to 0.5 <sub>out</sub>         |      | 1.5    | μ\$   |

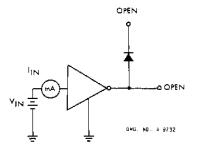

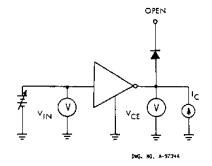

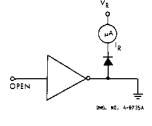

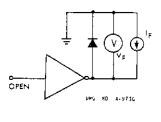

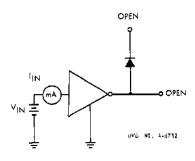

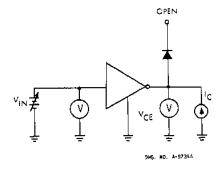

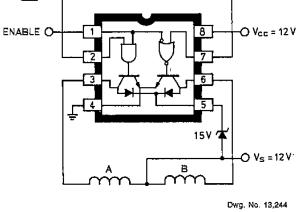

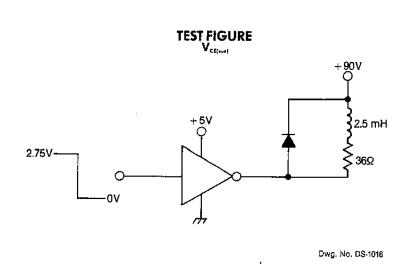

### **TEST FIGURES**

Figure 1

Figure 2

Figure 3

Figure 4

Figure 5

Figure 6

Figure 7

Figure 8

### PEAK COLLECTOR CURRENT AS A FUNCTION OF DUTY CYCLE

# PEAK COLLECTOR CURRENT AS A FUNCTION OF DUTY CYCLE (Continued)

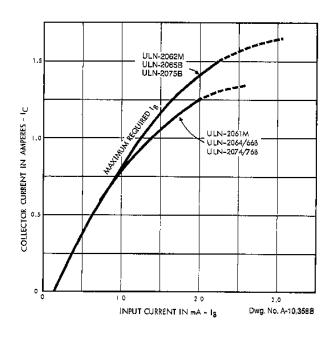

### COLLECTOR CURRENT AS A FUNCTION OF INPUT CURRENT AT +25°C

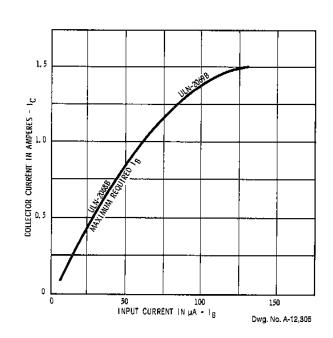

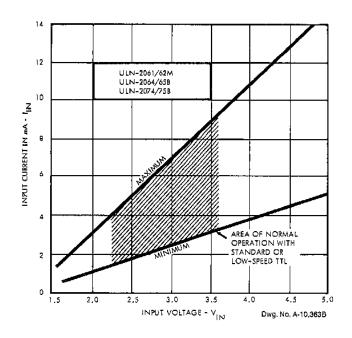

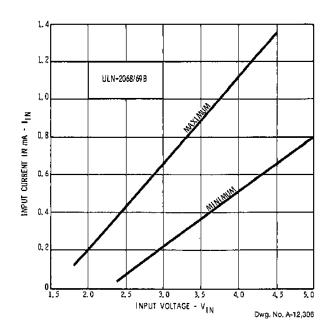

### INPUT CURRENT AS A FUNCTION OF INPUT VOLTAGE AT +25°C

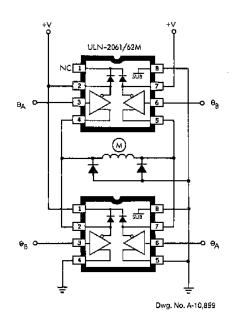

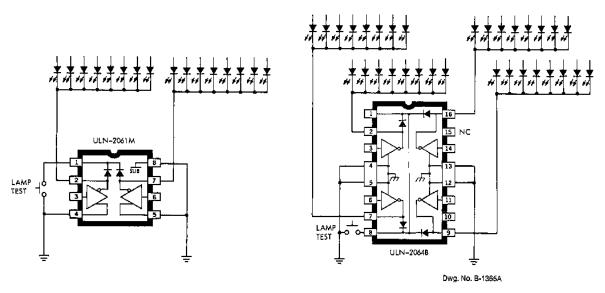

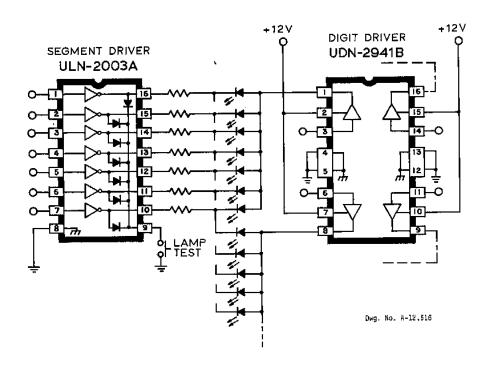

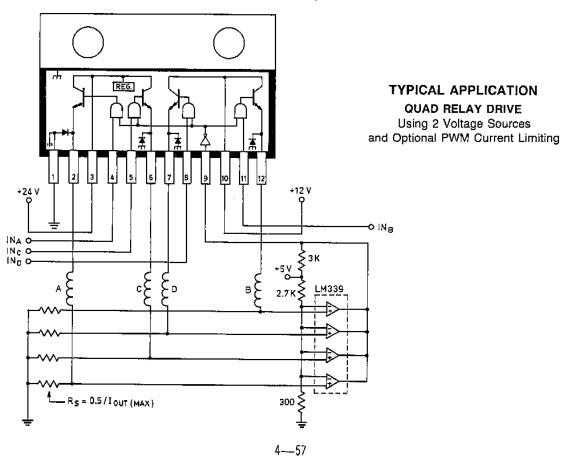

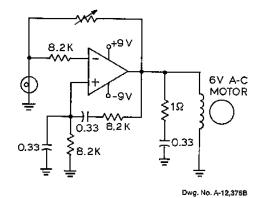

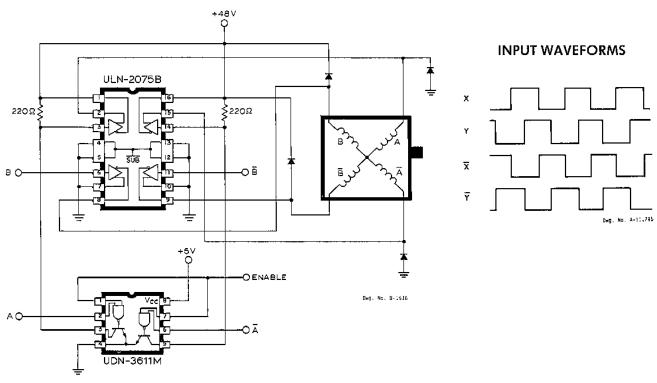

### TYPICAL APPLICATION

**BIDIRECTIONAL MOTOR CONTROL**

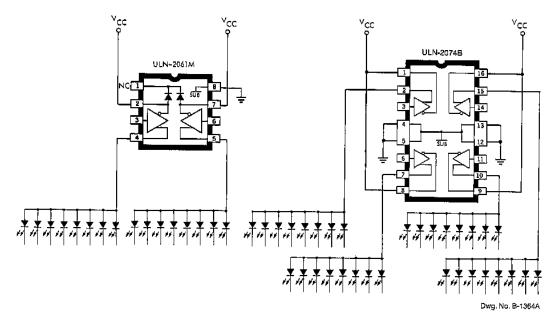

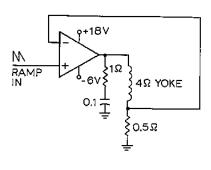

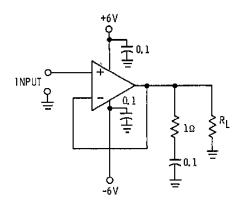

### **TYPICAL APPLICATIONS (Continued)**

### **COMMON-ANODE LED DRIVERS**

(Series UDN-2980A devices can be used in similar applications at currents of up to 500 mA)

### **COMMON-CATHODE LED DRIVERS**

(Type ULN-2068B is also applicable)

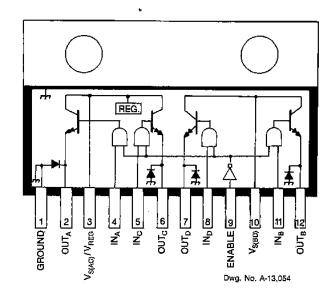

# UDN-2540B QUAD-NAND GATE POWER DRIVER

#### **FEATURES**

- 1.5 A Output Current

- Output Voltage to 60 V

- Integral Transient-Suppression Diodes

- Efficient Input/Output Pin Structure

- TTL, CMOS, PMOS, NMOS Compatible

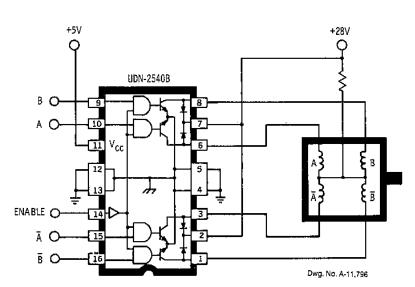

Combining NAND logic gates and high-current bipolar outputs, the UDN-2540B power and relay driver provides interface between low-level signal-processing circuits and power loads to 350 W. Each of the four independent outputs of this device can sink up to 1.5 A in the on state. In the off state the drivers will withstand at least 60 V. Transient-suppression clamp diodes and a minimum 35 V output sustaining voltage allow their use with many inductive loads.

Typical applications include relays, solenoids, and dc stepping motors. It can also be used to drive high-current incandescent lamps, LEDs, and heaters. In display applications, the diodes can be used to perform the "lamp test" function.

Inputs are compatible with most TTL, DTL, LSTTL, and 5 V or 12 V CMOS and PMOS logic.

Dwg. No. A-11,561

Each of the four outputs is recommended for continuous load currents to 1.25 A. Outputs can be paralleled for higher load currents.

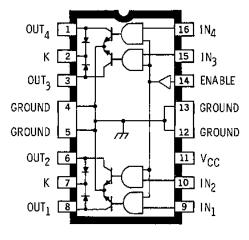

The UDN-2540B is supplied in a 16-pin dual-inline package with heat-sink contact tabs. This configuration allows attachment of an inexpensive heat sink and fits a standard integrated circuit socket or printed wiring board layout.

## ABSOLUTE MAXIMUM RATINGS at + 25°C Free-Air Temperature

| Output Voltage, V <sub>CE</sub>             |

|---------------------------------------------|

| Output Current, I <sub>out</sub>            |

| Supply Voltage, V <sub>cc</sub>             |

| Input Voltage, $V_{iN}$                     |

| Power Dissipation, Po (Each Driver)2.5 W    |

| (Total Package)                             |

| Operating Temperature Range, T <sub>A</sub> |

| Storage Temperature Range, $T_s$            |

## ELECTRICAL CHARACTERISTICS at $T_A = +25$ °C, $T_{TAB} = +70$ °C, $V_{CC} = 4.75$ V to 12.6 V (unless otherwise noted)

|                             |                      |                                                                                                                 |      | Limits       |       |

|-----------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------|------|--------------|-------|

| Characteristic              | Symbol               | Test Conditions                                                                                                 | Min. | Max.         | Units |

| Output Leakage Current      | I <sub>CEX</sub>     | $V_{out} = 60 \text{ V}, V_{in} = 0.7 \text{ V}, V_{ENABLE} = 2.0 \text{ V}$                                    |      | 100          | μΑ    |

|                             |                      | $V_{OUT} = 60 \text{ V}, V_{IN} = 2.0 \text{ V}, V_{ENABLE} = 0.7 \text{ V}$                                    | _    | 100          | μΑ    |

| Output Sustaining Voltage   | V <sub>CE(SUS)</sub> | $I_{\text{OUT}} = 100 \text{ mA}, V_{\text{IN}} = V_{\text{ENABLE}} = 0.7 \text{ V}$                            | 35   | _            | ٧     |

| Output Saturation Voltage   | V <sub>CE(SAT)</sub> | $I_{OUT} = 250 \text{ mA}, V_{IN} = V_{ENABLE} = 2.0 \text{ V}$                                                 |      | 1.0          | V     |

|                             |                      | $I_{OUT} = 500 \text{ mA}, V_{IN} = V_{ENABLE} = 2.0 \text{ V}$                                                 | _    | 1.1          | ٧     |

|                             |                      | $I_{OUT} = 750 \text{ mA}, V_{IN} = V_{ENABLE} = 2.0 \text{ V}$                                                 | _    | 1.25         | ٧     |

|                             |                      | $I_{OUT} = 1.0 \text{ A}, V_{IN} = V_{ENABLE} = 2.0 \text{ V}$                                                  | _    | 1.4          | ٧     |

|                             |                      | $I_{OUT} = 1.25 \text{ A, } V_{IN} = V_{ENABLE} = 2.0 \text{ V}$                                                |      | 1.6          | ٧     |

| Input Voltage               | Logic 1              | V <sub>IN(1)</sub> or V <sub>ENABLE(1)</sub>                                                                    | 2.0  | _            | ٧     |

|                             | Logic 0              | V <sub>IN(0)</sub> or V <sub>ENABLE(0)</sub>                                                                    |      | 0.7          | γ     |

| Input Current               | Logic 1              | $V_{IN(1)}$ or $V_{ENABLE(1)} = 2.0 \text{ V}$                                                                  | _    | 20           | μA    |

|                             | Logic 0              | $V_{M(0)}$ or $V_{ENABLE(0)} = 0.4 \text{ V}$                                                                   | I —  | <b>—</b> 200 | μΑ    |

| Input Clamp Voltage         | V <sub>IK</sub>      | $I_{IN}$ or $I_{ENABLE} = -10$ mA                                                                               | _    | -1.5         | ٧     |

| Total Supply Current        | l <sub>cc</sub>      | $V_{IN}^* = V_{ENABLE} = 2.0 \text{ V}, V_{CC} = 5.0 \text{ V}, \text{ Outputs Open}$                           | _    | 8.0          | mA    |

|                             |                      | $V_{\text{IN}}^{\star} = V_{\text{ENABLE}} = 2.0 \text{ V}, V_{\text{CC}} = 15 \text{ V}, \text{ Outputs Open}$ | _    | 33           | mA    |

|                             |                      | $V_{M}^{*} = V_{ENABLE} = 0.7 \text{ V}, V_{CC} = 5.0 \text{ V}$                                                |      | 2.0          | mA    |

|                             |                      | $V_{IN}^{*} = V_{ENABLE} = 0.7 \text{ V}, V_{CC} = 15 \text{ V}$                                                | _    | 7.0          | mΑ    |

| Clamp Diode Forward Voltage | V <sub>F</sub>       | $I_{\rm F}=1.0{\rm A}$                                                                                          | _    | 2.1          | ٧     |

|                             |                      | $I_F = 1.25  A$                                                                                                 |      | 2.5          | ν     |

| Clamp Diode Leakage Current |                      | $V_R = 60 \text{ V}, V_{IN} = V_{ENABLE} = 2.0 \text{ V}, D_1 + D_2 \text{ or } D_3 + D_4$                      | _    | 100          | μA    |

<sup>\*</sup>All inputs simultaneously, all other tests are performed with each input tested separately.

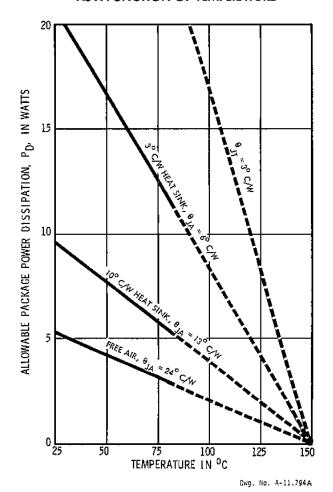

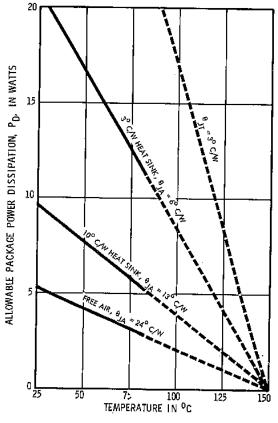

## ALLOWABLE AVERAGE PACKAGE POWER DISSIPATION AS A FUNCTION OF TEMPERATURE

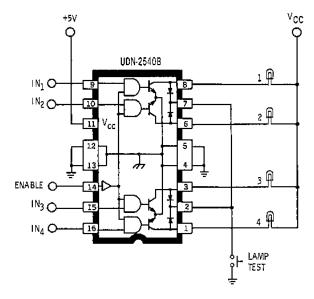

### **APPLICATIONS**

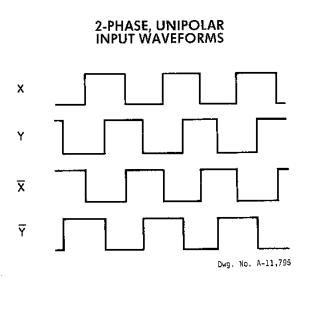

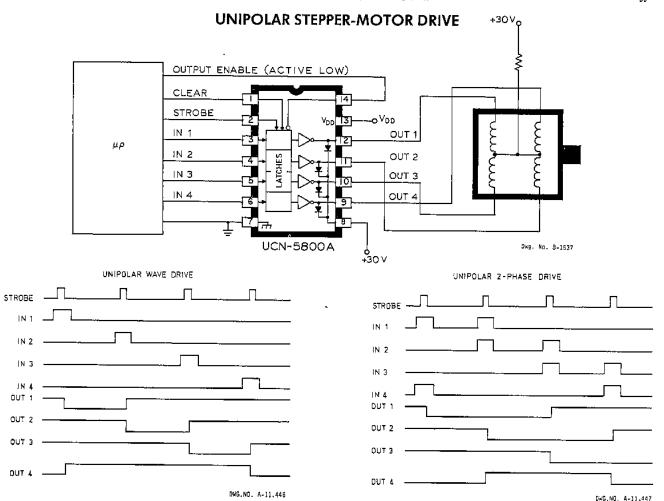

Typical applications for this device include driving incandescent lamps and dc stepper motors. Lamps with steady-state current ratings up to 150 mA can be driven without current limiting or warming resistors (assumes 1.5 A peak in-rush). The internal diodes can be used to perform the "lamp test" function as shown. Bifilar (unipolar) stepper motors can be driven directly. The internal transient-suppression diodes prevent damage to the output transistor from positive high-voltage inductive spikes as the output switches off.

#### **INCANDESCENT LAMP DRIVER**

Dwg. No. A-12,048A

### STEPPER-MOTOR DRIVER

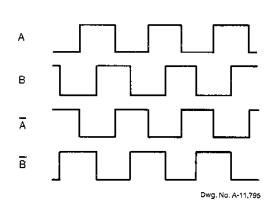

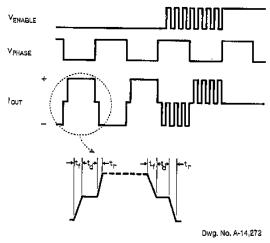

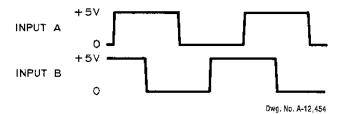

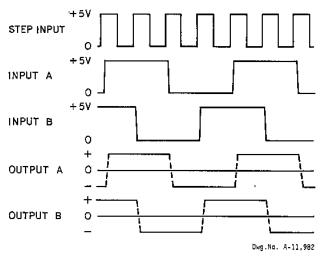

### **INPUT WAVEFORMS**

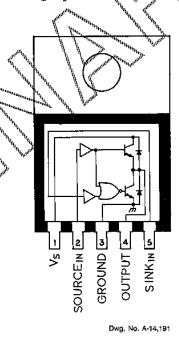

### UDN-2545B UNIVERSAL QUAD DRIVER

### **FEATURES**

- Output Current of 2 A

- 80 V Min, Output Breakdown

- 40 V Output Sustaining Voltage

- PMOS, CMOS, TTL Compatible

- Built-in Thermal Shutdown

- Output Transient Protection

- CHIP ENABLE for Microprocessor Control

- Under-Voltage Protection

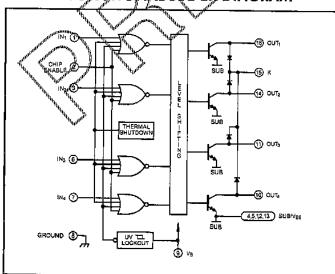

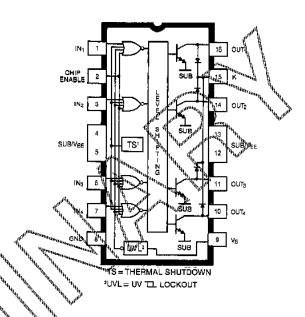

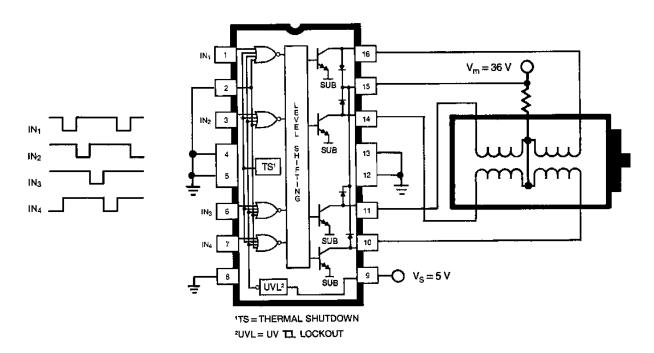

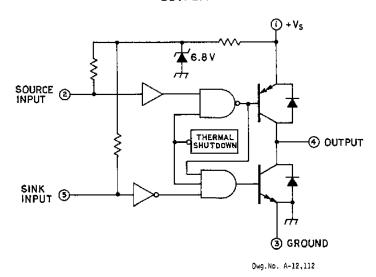

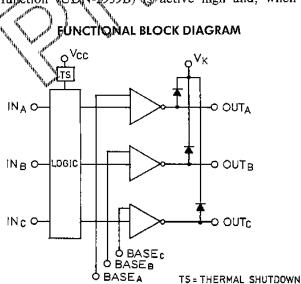

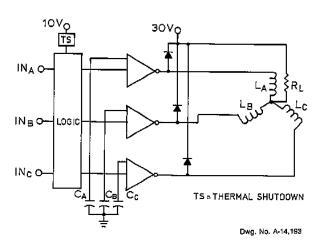

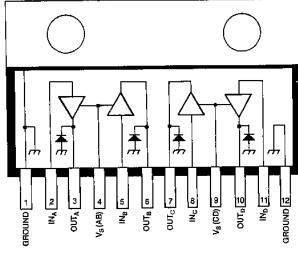

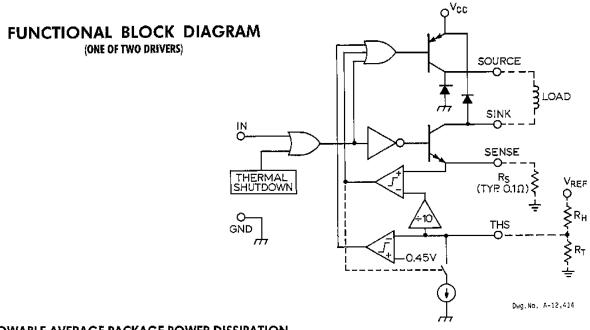

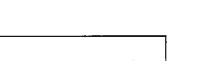

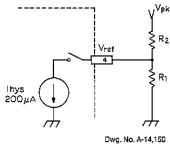

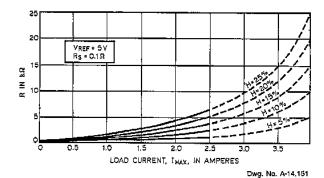

The UDN-2545B is a four-channel high-current, high-voltage integrated circuit designed to provide the interface between stepper motors and microprocessor or logic motor control circuitry. The UDN-2545B will accept most standard logic signal inputs and provide motor drive current to both positive and negative supply rails.

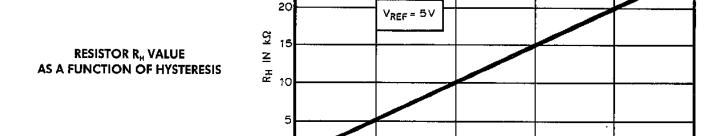

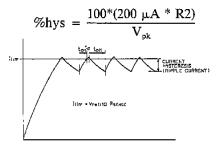

The UDN-2545B is capable of sinking up to 2.5 A and maintaining an output OFF voltage of 80 volts. This device incorporates some unique features such as under-voltage protection, thermal shutdown, and CHIP ENABLE control. The under-voltage protection guards against supply line transients and has

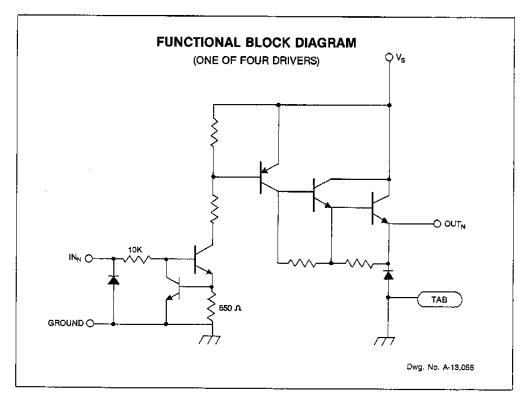

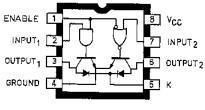

FUNCTIONAL BLOCK DIAGRAM

built-in hystersis. The thermal shutdown with hystersis is to guard against damage to the device. CHIP ENABLE is especially good for use in microprocessor control. All outputs have clamp diodes for suppression of inductive loads.

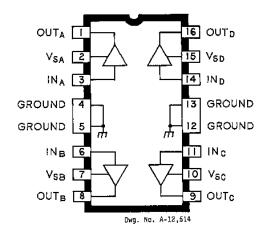

The UDN-2545B is supplied in a 16 pin plastic dual in-line package with heat-sink contact tabs. A copper-alloy lead frame provides maximum power dissipation using standard cooling methods. This lead configuration facilitates attachment of external heat sinks for increased power dissipation with standard IC sockets and printed wiring boards.

## ABSOLUTE MAXIMUM RATINGS at $T_A = +25^{\circ}C$

| Output Voltage, V <sub>CE</sub> 80 V                                                   |

|----------------------------------------------------------------------------------------|

| Emitter Supply Voltage, V <sub>EE</sub> 25 V                                           |

| Logic Supply Voltage, V <sub>s</sub> 20 V                                              |

| Output Current, Iour                                                                   |

| Input Voltage, V <sub>IN</sub>                                                         |

| Package Power Dissipation, Po 2.77 W*                                                  |

| Operating Temperature Range, $T_A 	ext{} -20^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |

| Storage Temperature Range, T <sub>s</sub> 55°C to +150°C                               |

| *Derate at the Rate of 22.2 mW/°C above T = 25°C                                       |

### ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}\text{C}$ , $V_S = 5~\text{V}$ to 15 V, $V_{EE} = 0~\text{V}$ (unless otherwise noted)

|                             |                      |                                                                                      |          | Limits       |       |

|-----------------------------|----------------------|--------------------------------------------------------------------------------------|----------|--------------|-------|

| Characteristic              | Symbol               | Test Conditions                                                                      | Min.     | Max.         | Units |

| Output Leakage Current      | I <sub>CEX</sub>     | $V_{out} = 80 \text{ V}, V_{IN} = 2.0 \text{ V}, \text{ Other Inputs} = 0 \text{ V}$ | <b>—</b> | 500          | μΑ    |

| Output Sustaining Voltage   | V <sub>CE(sus)</sub> | I <sub>out</sub> = 2 A, Inputs = 5.0 V, L = 3 mH                                     | 40       | _            | ٧     |

| Output Saturation Voltage*  | V <sub>CE(SAT)</sub> | I <sub>out</sub> = 2 A, Inputs = 0 V                                                 |          | 2.2          | ٧     |

| Clamp Diode Leakage Current | I <sub>R</sub>       | $V_R = 80 \text{ V}$                                                                 | T —      | 50           | μΑ    |

| Clamp Diode Forward Voltage | V <sub>F</sub>       | $I_F = 2 A$                                                                          |          | 2.5          | ٧     |

| Input Current               | I <sub>IN(ON)</sub>  | $V_{IN} = 0.8 V$                                                                     |          | <b>– 250</b> | μΑ    |

|                             | I <sub>IN(OFF)</sub> | $V_{IN} = V_{S}$                                                                     | 1 —      | 50           | μΑ    |

| Supply Current              | I <sub>S(ON)</sub>   | All Inputs = $0.8 \text{ V}$ , $V_s = 5.0 \text{ V}$                                 | <b>—</b> | 65           | mA    |

|                             |                      | All Inputs = 0.8 V, V <sub>s</sub> = 15 V                                            |          | 70           | mA    |

|                             | I <sub>S(OFF)</sub>  | All Inputs = $5.0 \text{ V}$ , $V_s = 5.0 \text{ V}$                                 |          | 20           | mA    |

|                             |                      | All Inputs = $15 \text{ V}$ , $\text{V}_{\text{S}} = 15 \text{ V}$                   |          | 30           | mA    |

<sup>\*</sup>Pulse Test

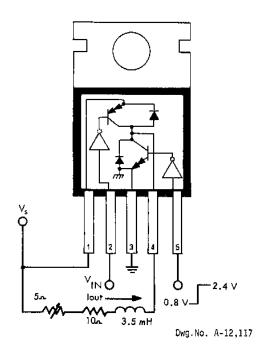

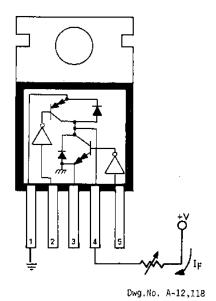

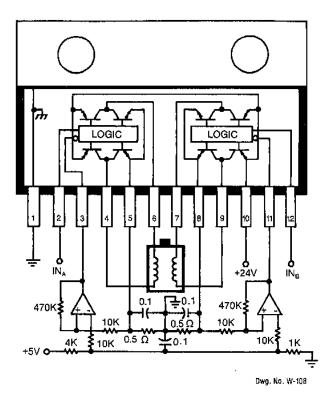

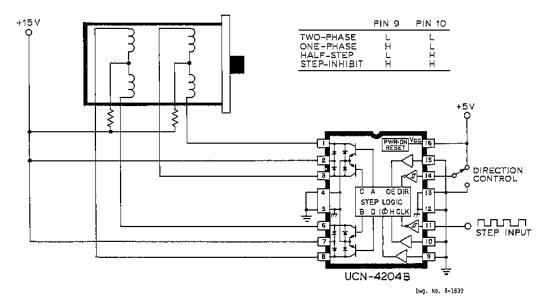

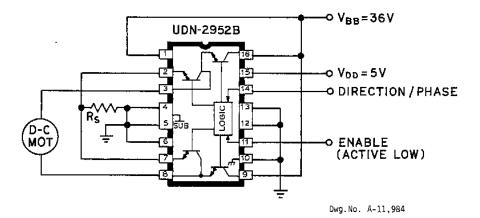

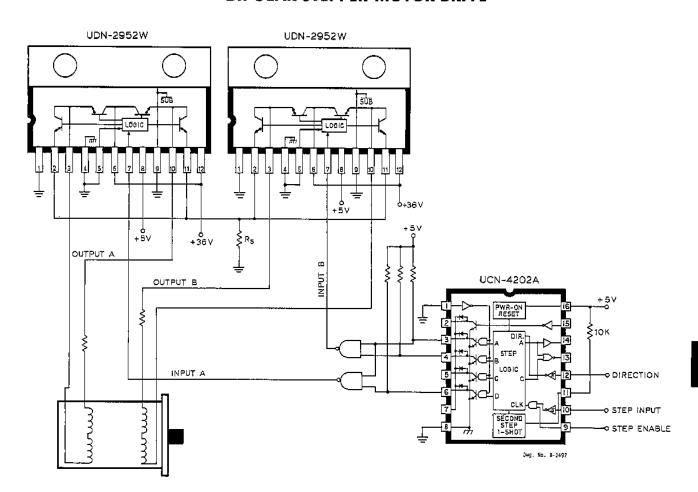

### STEPPER MOTOR APPLICATION

### UDN-2841B AND UDN-2845B QUAD DARLINGTON 1.5 A DRIVERS

### **FEATURES**

- Inputs Compatible with DTL, TTL, LSTTL, CMOS

- − 50 V Darlington Outputs

- Current-Sink or Sink-and-Source Combination

- 16-Pin Dual In-Line Plastic Package

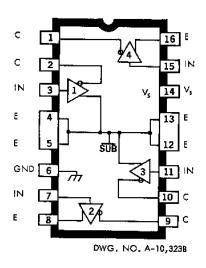

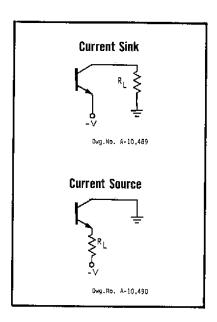

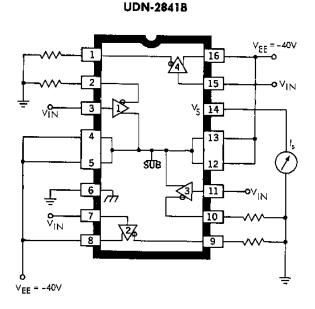

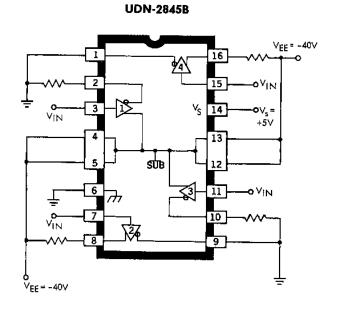

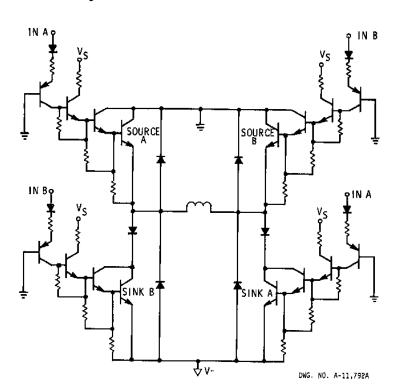

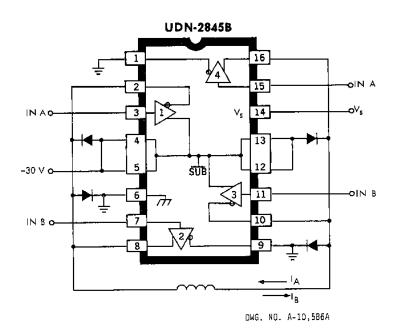

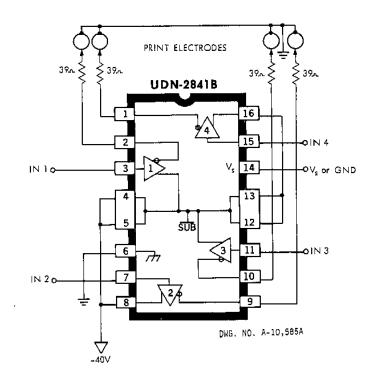

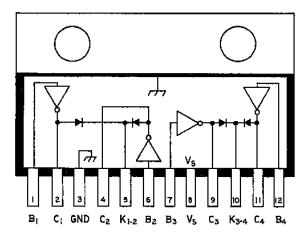

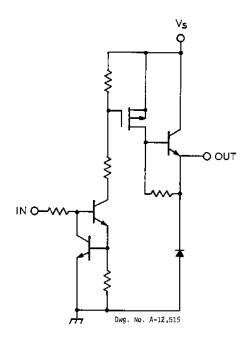

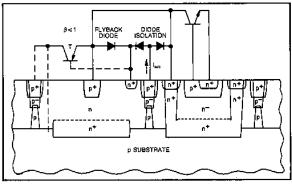

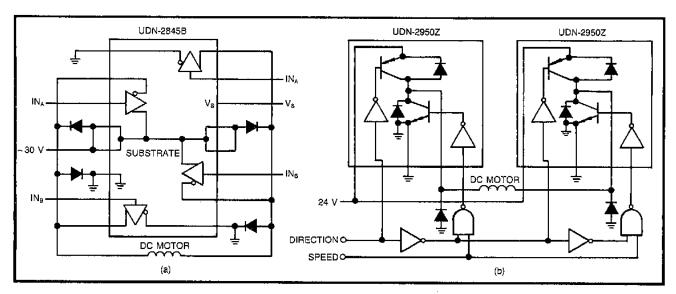

THIS PAIR OF QUAD DARLINGTON switches is designed for high-current, high-voltage peripheral driver applications. They provide solutions to interface problems involving electronic discharge printers, d-c motor drive (bipolar or unipolar), telephone relays, PIN diodes, LEDs, and other high-current loads operating with negative voltage supplies.

Type UDN-2841B is for current-sink applications in which the load is connected to ground. The outputs switch the negative supply. The input PNP transistor in each driver serves as a level translator. The first NPN stage provides current gain to drive the Darlington-pair outputs.

Type UDN-2845B is a current-sink, current-source combination in a single dual in-line plastic package. It can be used in bipolar switching applications in which neither end of the load is at ground potential.

Types UDN-2841 and UDN-2845B are intended for use with 5 V TTL, Schottky TTL, DTL, and CMOS logic. Both drivers reduce component count, lower system costs, and reduce circuit and board complexity.

## ABSOLUTE MAXIMUM RATINGS at +25°C Free-Air Temperature

### For Single Darlington Output (Unless Otherwise Noted)

| Output Voltage, V <sub>CE(OFF)</sub>                                              |

|-----------------------------------------------------------------------------------|

| Output Sustaining Voltage, V <sub>CE(SUS)</sub>                                   |

| Substrate Voltage, V <sub>SUB</sub>                                               |

| Continuous Output Current, Iout                                                   |

| Supply Voltage, V <sub>s</sub>                                                    |

| Input Voltage, V <sub>IN</sub>                                                    |

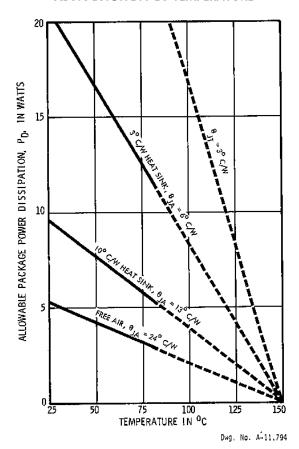

| Power Dissipation, Po (one output) See Graph                                      |

| Operating Temperature Range, $T_A = -20^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |

| Storage Temperature Range, T <sub>s</sub>                                         |

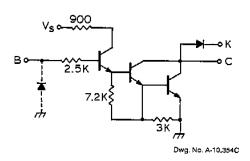

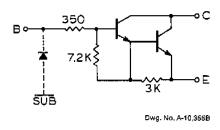

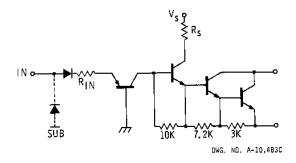

### SCHEMATIC (Each Driver)

|             | Resistor Values in $k\Omega$ |                |                  |          |  |  |

|-------------|------------------------------|----------------|------------------|----------|--|--|

|             | Amplific                     | er 1 & 3       | Amplifie         | er 2 & 4 |  |  |

| Type Number | R <sub>IN</sub>              | R <sub>s</sub> | Ř <sub>IN.</sub> | $R_s$    |  |  |

| UDN-2841B   | 3.3                          | 15             | 3.3              | 15       |  |  |

| UDN-2845B   | 3.3                          | 15             | 3.3              | 1        |  |  |

NOTE: The substrate terminals must be tied to the most negative point in the external circuit to maintain isolation between transistors and to provide for normal device operation.

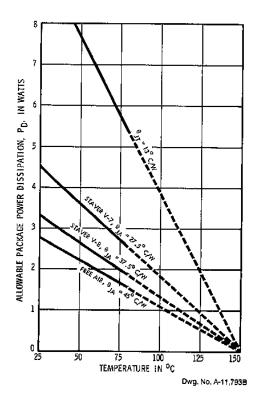

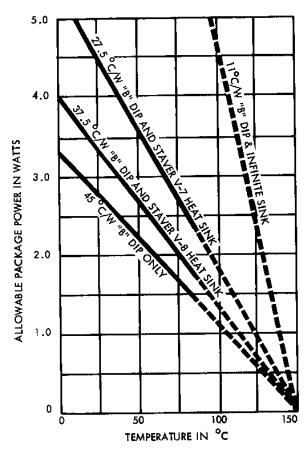

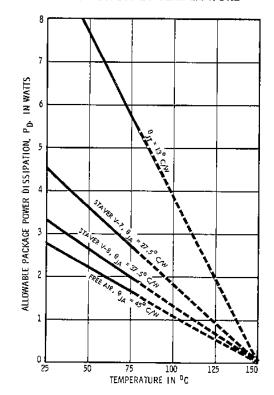

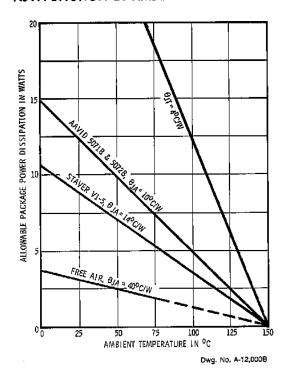

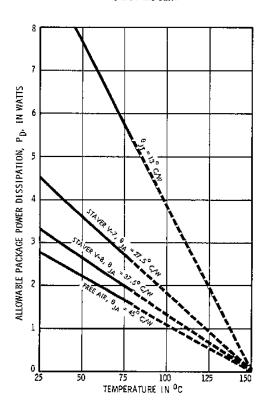

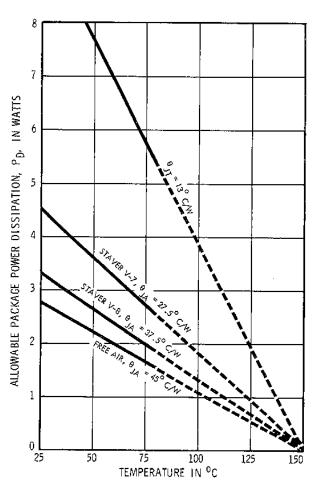

## ALLOWABLE POWER DISSIPATION AS A FUNCTION OF TEMPERATURE

DWG. NO. A-10,488C

### ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ (unless otherwise noted)

|                              |                      |                                                                             | _    | _ l  | imits |       |

|------------------------------|----------------------|-----------------------------------------------------------------------------|------|------|-------|-------|

| Characteristic               | Symbol               | Test Conditions                                                             | Min. | Тур. | Max.  | Units |

| Output Leakage               | I <sub>CEX</sub>     | $V_{EE} = -50 \text{ V}, V_{IN} = 0.4 \text{ V}, T_A = 25 ^{\circ}\text{C}$ |      |      | 100   | μA    |

| Current                      |                      | $V_{EE} = -50 \text{V},  V_{IN} = 0.4 \text{V},  T_{A} = 70 \text{°C}$      |      |      | 500   | μA    |

| Output Sustaining<br>Voltage | V <sub>CE(SUS)</sub> | $V_{EE} = -50 \text{ V}, V_{IN} = 0.4 \text{ V}, I_{OUY} = 100 \text{ mA}$  | 35   | 50   | _     | Ÿ     |

| Output Saturation            | V <sub>CE(SAT)</sub> | l <sub>οιπ</sub> = 500 mA                                                   |      |      | 1.1   | ٧     |

| Voltage                      | 1                    | $I_{OUT} = 1.0 \text{ A (Note 1)}$                                          |      |      | 1.4   | ٧     |

| <u>_</u> _                   |                      | $I_{\text{OUT}} = 1.5 \text{ A (Note 1)}$                                   | _    |      | 1.6   | ٧     |

| Input Current                | I <sub>IN(ON)</sub>  | $I_{\text{out}} = 500 \text{mA}, V_{\text{in}} = 2.4 \text{V}$              |      | 300  | 500   | μA    |

| Input Voltage<br>(Note 1)    | V <sub>IN(ON)</sub>  | $I_{OUT} = 1.5A$                                                            |      | _    | 2.4   | V     |

| Supply Current               | I <sub>s</sub>       | I <sub>OUT</sub> = 500 mA, UDN-2841B, UDN-2845B (Note 2)                    |      | 2.5  | 3.75  | mA    |

| (Note 1)                     |                      | I <sub>OUT</sub> = 500 mA, UDN-2845B (Note 3)                               |      | 3.3  | 7.5   | πА    |

| Turn-On Delay                | t <sub>pd(ON)</sub>  | $R_L = 39\Omega$ , 0.5 $V_{IN}$ to 0.5 $V_{OUT}$                            |      |      | 2.0   | μS    |

| Turn-Off Delay               | t <sub>pd(OFF)</sub> | $R_L = 39\Omega$ , $0.5V_{IN}$ to $0.5V_{OUT}$                              |      |      | 5.0   | μs    |

#### NOTES.

- 1. Each driver tested separately. 2. Drivers 1 & 3 (sink drivers) only,  $V_s=0\,V$ ,  $V_{\epsilon\epsilon}=-40\,V$ . 3. Drivers 2 & 4 (source drivers) only,  $V_s=5\,V$ ,  $V_{\epsilon\epsilon}=-40\,V$ .

### **TEST CIRCUITS**

DWG. NO. A-10,487A

DWG. NO. A-10,484A

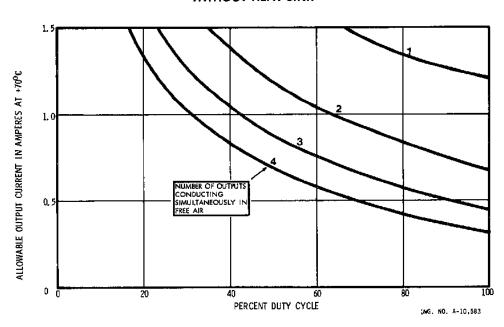

## ALLOWABLE OUTPUT CURRENT AS A FUNCTION OF DUTY CYCLE

### WITHOUT HEAT SINK

### WITH STAVER V-7 HEAT SINK

### **OUTPUT-STAGE TRANSIENT PROTECTION**

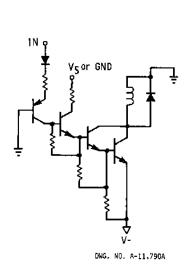

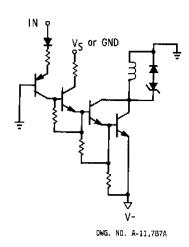

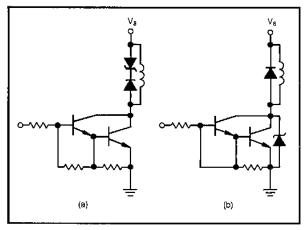

When switching inductive loads, the output transistors of UDN-2841B and UDN-2845B drivers should be protected by a suitable clamping technique. The simplest approach is to clamp each output with a discrete diode, as shown in Figures 1 and 2.

Figure 1 UDN-2841B

Figure 3 UDN-2841B

Figure 2 UDN-2845B

For improved turnoff, a combination diode/Zener diode scheme can be used. The Zener diode in the clamp circuit of Figure 3 allows the flyback voltage to rise above the supply voltage, speeding turnoff of the load. An appropriate resistor can be substituted for the Zener diode. With a 1A load, substitution of a  $15\Omega$  resistor results in operation similar to that of the Zener diode circuit.

### TYPICAL APPLICATIONS

### **BIPOLAR MOTOR DRIVER**

### **ELECTROSENSITIVE PRINTER INTERFACE**

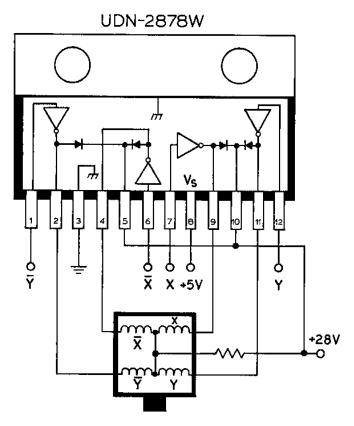

# UDN-2878W AND UDN-2879W QUAD HIGH-CURRENT DARLINGTON SWITCHES

#### **FEATURES**

- Output Currents to 4 A

- Output Voltages to 80 V

- . Loads to 1280 W

- TTL, DTL, or CMOS Compatible Inputs

- Internal Clamp Diodes

- Plastic Single In-Line Package

- Heat-Sink Tab

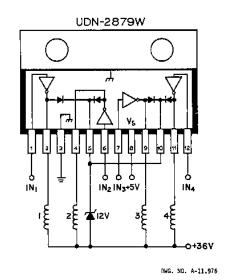

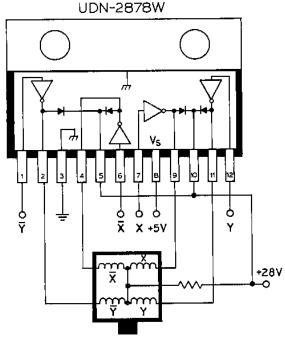

THESE QUAD DARLINGTON ARRAYS are designed to serve as interface between low-level logic and peripheral power devices such as solenoids, motors, incandescent displays, heaters, and similar loads of up to 320 W per channel. Both integrated circuits include transient-suppression diodes that enable use with inductive loads. The input logic is compatible with most TTL, DTL, LS TTL, and 5 V CMOS logic.

Type UDN-2878W and UDN-2879W 4 A arrays are identical except for output-voltage ratings. The former is rated for operation to 50 V (35 V sustaining), while the latter has a minimum output breakdown rating of 80 V (50 V sustaining). The

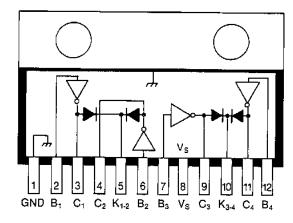

DWG. NO. A-11,974

economical Type UDN-2878W-2 and Type UDN-2879W-2 are recommended for applications requiring load currents of 3 A or less. These less expensive devices are identical to the basic parts except for the maximum allowable load-current rating.

For maximum power-handling capability, all drivers are supplied in a 12-pin single in-line power-tab package. The tab is at ground potential and needs no insulation. External heat sinks are usually required for proper operation of these devices.

| Device      | Output<br>Voltage | Sustaining<br>Voltage | Output<br>Current |

|-------------|-------------------|-----------------------|-------------------|

| UDN-2878W   | 50 V              | 35 V                  | 4 A               |

| UDN-2878W-2 | 50 V              | 35 V                  | 3 A               |

| UDN-2879W   | 80 V              | 50 V                  | 4 A               |

| UDN-2879W-2 | 80 V              | 50 V                  | 3 A               |

### ABSOLUTE MAXIMUM RATINGS at +25°C Free-Air Temperature for any driver (unless otherwise noted)

| Output Voltage, V <sub>CEX</sub> (UDN-2878W & UDN-2878W-2)                                |

|-------------------------------------------------------------------------------------------|

| (UDN-2879W & UDN-2879W-2) 80 V                                                            |

| Output Current, Ic (UDN-2878W & UDN-2879W)                                                |

| (UDN-2878W-2 & UDN-2979W-2)                                                               |

| Input Voltage, V <sub>IN</sub>                                                            |

| Input Current, I <sub>IN</sub>                                                            |

| Supply Voltage, V <sub>s</sub>                                                            |

| Total Package Power Dissipation, P See Graph                                              |

| Operating Ambient Temperature Range, $T_A = -20^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |

| Storage Temperature Range, T <sub>s</sub>                                                 |

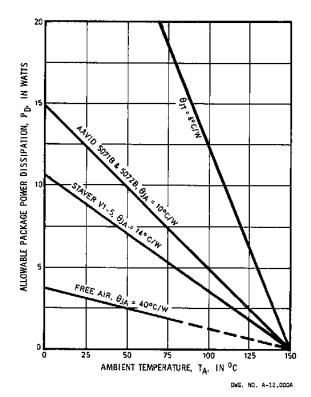

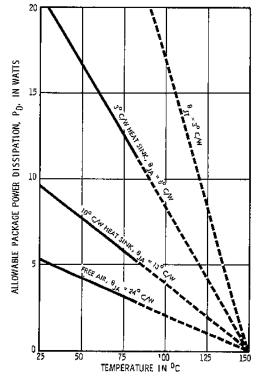

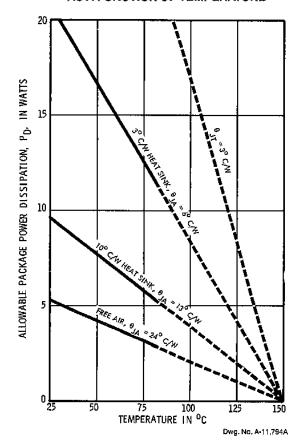

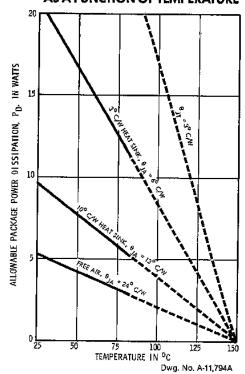

## ALLOWABLE AVERAGE PACKAGE POWER DISSIPATION AS A FUNCTION OF TEMPERATURE

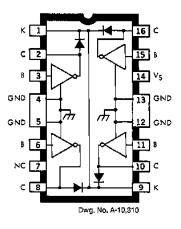

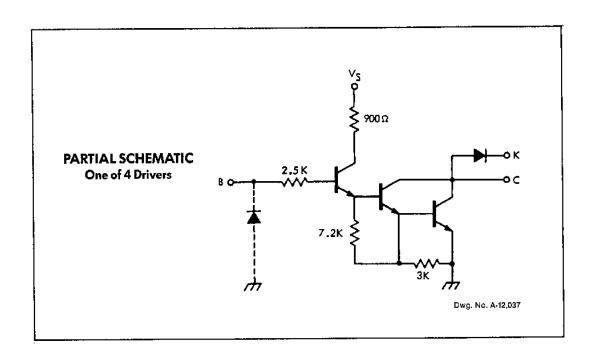

## PARTIAL SCHEMATIC One of 4 Drivers

## ELECTRICAL CHARACTERISTICS at $V_s = 5.0 \, V$ , $T_A = +25 \, ^{\circ} C$ (unless otherwise noted)

| _                         |                      | Test | Applicable     |                                                          |              | Limits |            |

|---------------------------|----------------------|------|----------------|----------------------------------------------------------|--------------|--------|------------|

| Characteristic            | Symbol               | Fig. | Devices        | Test Conditions                                          | Min.         | Max.   | Units      |

| Output Leakage Current    | I <sub>CEX</sub>     | 1    | UDN-2878W/W-2  | $V_{CE} = 50 \text{ V}$                                  |              | 100    | μΑ         |

|                           | i                    |      |                | $V_{CE} = 50 \text{ V, } T_{A} = +70 ^{\circ}\text{C}$   | _            | 500    | μĀ         |

|                           |                      |      | UDN-2879W/W-2  | $V_{CE} = 80 \text{ V}$                                  | T =          | 100    | μА         |

|                           |                      |      |                | $V_{CE} = 80 \text{ V}, T_{A} = +70^{\circ}\text{C}$     |              | 500    | μΑ         |

| Output Sustaining         | V <sub>CE(SUS)</sub> | 2    | UDN-2878W/W-2  | $I_{c} = 100 \text{ mA}, V_{IN} = 0.4 \text{ V}$         | 35           |        | ٧          |

| Voltage                   |                      |      | UDN-2879W/W-2  | $I_{c} = 100 \text{ mA}, V_{IN} = 0.4 \text{ V}$         | 50           |        | ٧          |

| Collector-Emitter         | V <sub>CE(SAT)</sub> | 2    | Aii            | $I_c = 500 \text{ mA}, V_{IN} = 2.75 \text{ V}$          |              | 1.1    | ٧          |

| Saturation Voltage        |                      |      |                | $I_c = 1.0 \text{ A}, V_{IN} = 2.75 \text{ V}$           |              | 1.3    | ٧          |

|                           |                      |      |                | $I_c = 2.0 \text{ A}, V_{in} = 2.75 \text{ V}$           | _            | 1.5    | V          |

|                           |                      |      |                | $I_c = 3.0 \text{ A}, V_{IN} = 2.75 \text{ V}$           |              | 1.9    | ٧          |

|                           |                      |      | UDN-2878/2879W | $I_c = 4.0 \text{ A}, V_{IN} = 2.75 \text{ V}$           |              | 2.2    | ٧          |

| Input Current             | I <sub>IN</sub>      | 3    | All            | $V_{IN} = 2.75 V$                                        | T —          | 550    | μΑ         |

|                           |                      |      | <u> </u>       | $V_{IN} = 3.75 \text{ V}$                                |              | 1000   | μА         |

| Input Voltage             | V <sub>IN(ON)</sub>  | 4    | All            | $V_{cE} = 2.2 \text{ V}, I_{c} = 3.0 \text{ A}$          |              | 2.75   | V          |

|                           |                      |      | UDN-2878/2879W | $V_{CE} = 2.2 \text{ V}, I_{C} = 4.0 \text{ A}$          | T            | 2.75   | ٧          |

| Supply Current per Driver | l <sub>s</sub>       | 7    | All            | $I_{\rm c} = 500  {\rm mA},  V_{\rm in} = 2.75  {\rm V}$ |              | 6.0    | mA         |

| Turn-On Delay             | t <sub>PLH</sub>     |      | All            | 0.5 E <sub>in</sub> to 0.5 E <sub>out</sub>              |              | 1.0    | μS         |

| Turn-Off Delay            | t <sub>PHL</sub>     | _    | All            | $0.5 E_{in}$ to $0.5 E_{out}$ , $I_{C} = 3.0 A$          | _            | 1.5    | μs         |

| Clamp Diode               | I <sub>R</sub>       | 5    | All            | $V_R = 50 \text{ V}$                                     | T            | 50     | μA         |

| Leakage Current           |                      |      | [              | $V_R = 50 \text{ V}, T_A = +70^{\circ}\text{C}$          | _            | 100    | μA         |

|                           |                      |      | UDN-2879W/W-2  | $V_R = 80 \text{ V}$                                     | <b> </b>     | 50     | μA         |

|                           |                      |      |                | $V_R = 80 \text{ V}, T_A = +70 ^{\circ}\text{C}$         |              | 100    | μA         |

| Clamp Diode               | V <sub>F</sub>       | 6    | All            | $I_F = 3.0 \text{ A}$                                    | <del></del>  | 2.5    | V          |

| Forward Voltage           | ļ                    |      | UDN-2878/2879W | $I_F = 4.0 \text{ A}$                                    | <del> </del> | 3.0    | <u>·</u> - |

CAUTION: High-current tests are pulse tests or require heat sinking.

## **TEST FIGURES (Continued)**

Figure 3

Figure 4

Figure 5

Figure 6

Figure 7

### TYPICAL APPLICATIONS

### STEPPER-MOTOR DRIVER

DWG. NO. A-11,975

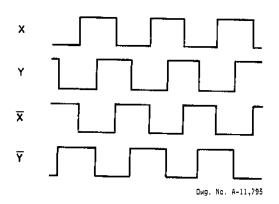

### **INPUT WAVEFORMS**

## TYPICAL APPLICATIONS

### PRINT-HAMMER DRIVER

DIGIT DRIVER

FOR MULTIPLEXED INCANDESCENT LAMP DISPLAY

SEGMENT

SELECT

DIGIT

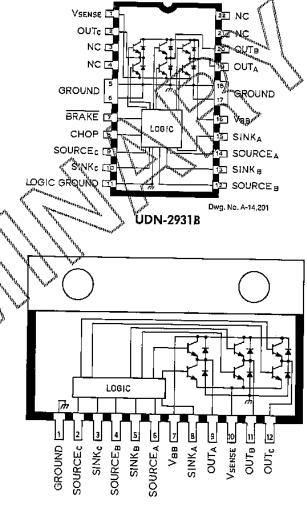

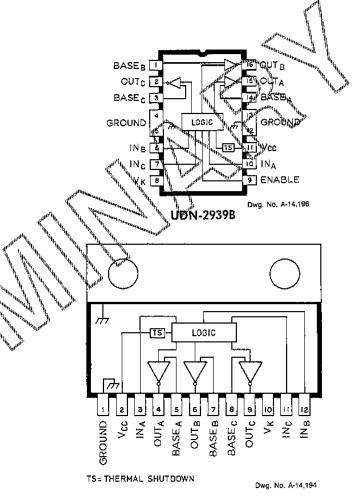

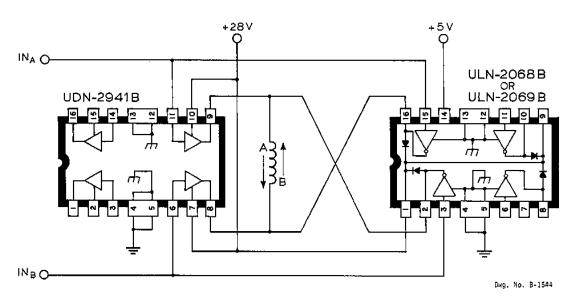

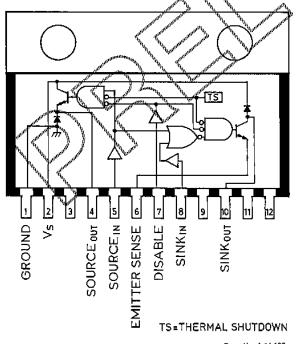

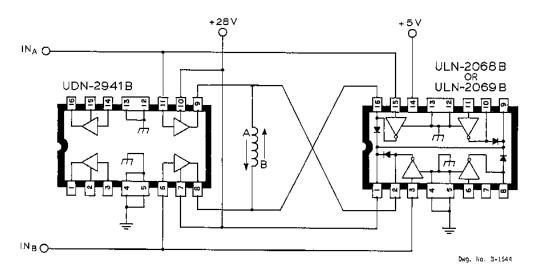

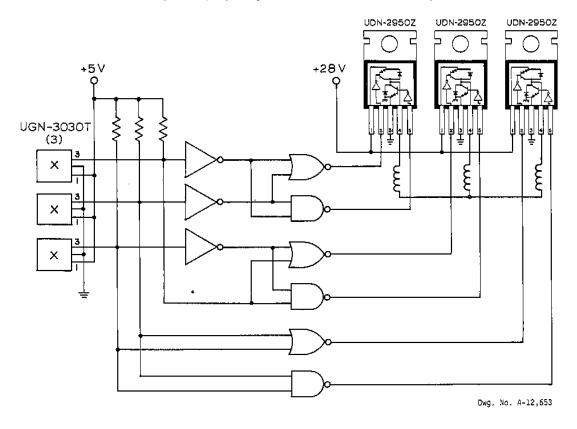

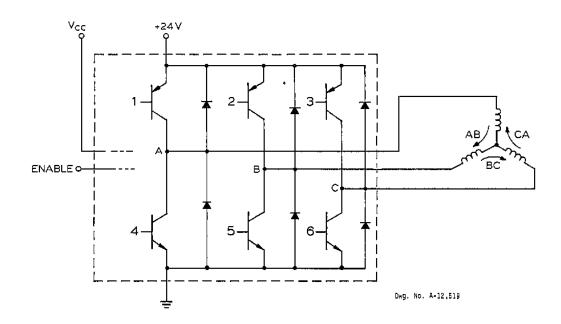

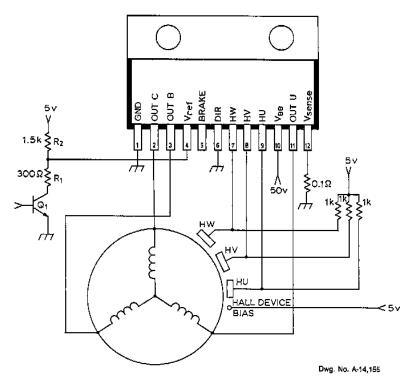

# UDN-2931B AND UDN-2931W 3-PHASE BRUSHLESS DC MOTOR DRIVERS

### **FEATURES**

- Output Current of 2 A

- Internal Transient-Suppression Diodes

- Low-Saturation Output Drivers

- Anti-Crossover Protection

- Braking and Chopping Functions (UDN-2931B)

- Thermal Shutdown with Hysteresis

- External Current-Sense Capability

- Input Lockout Circuitry

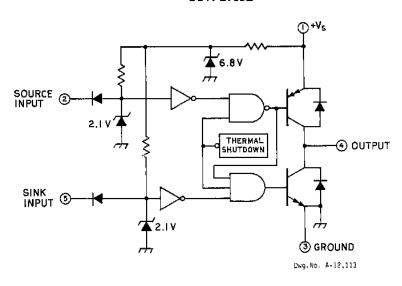

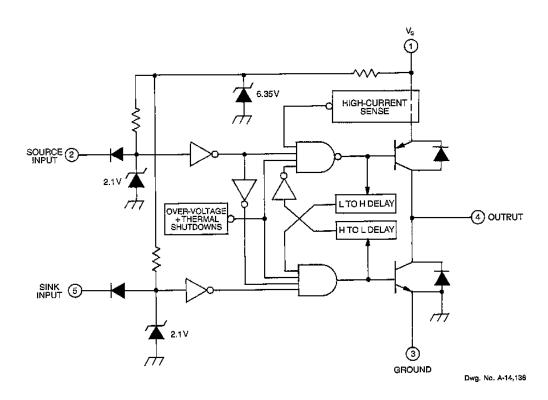

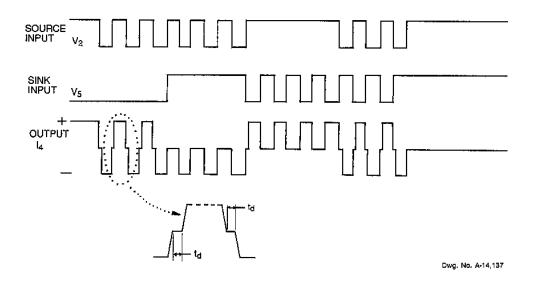

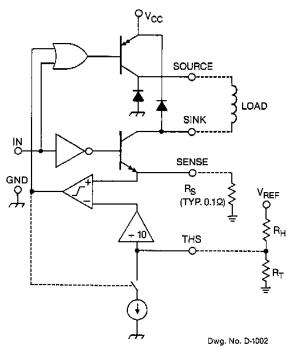

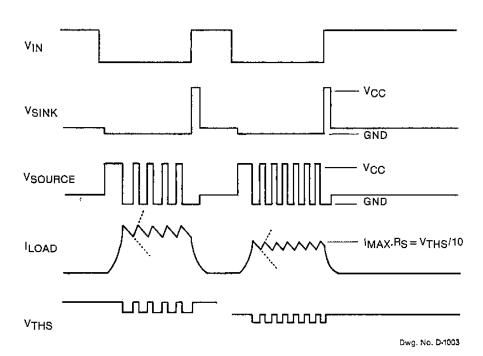

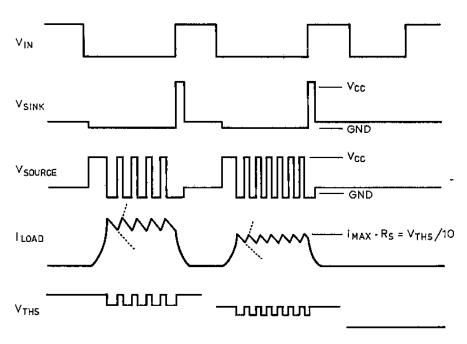

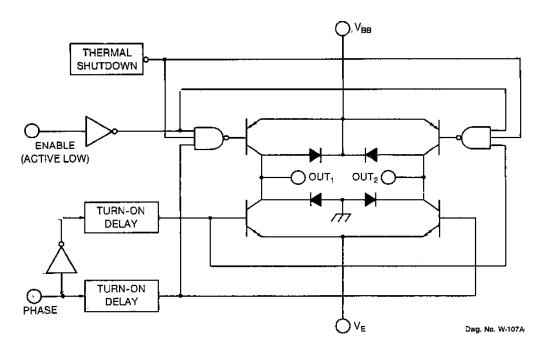

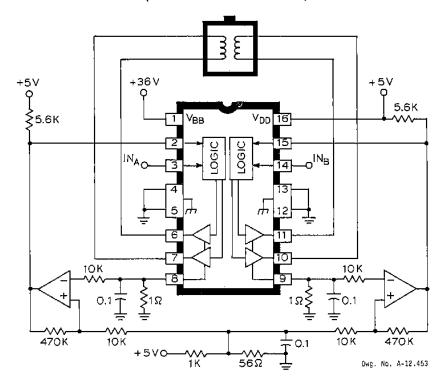

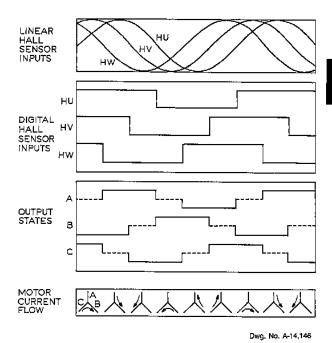

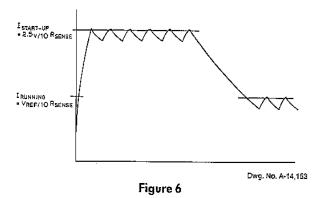

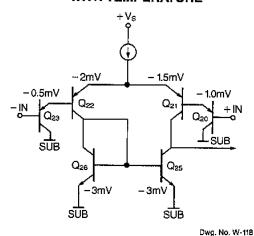

The UDN-2931B/W 3-phase brushless dc motor driver is designed for low output saturation-voltage levels. These drivers maximize motor capacity limited by power supply constraints. The output driver features low output saturation source and sink drivers and integral output suppression diodes. The outputs are capable of maintaining an output off voltage of 15 V and an on current of 2 A (3.54 peak).

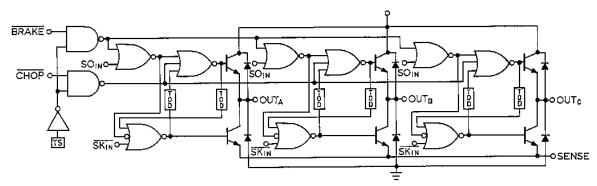

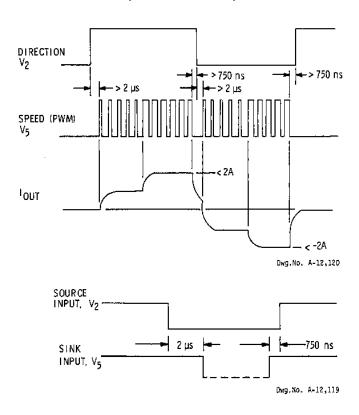

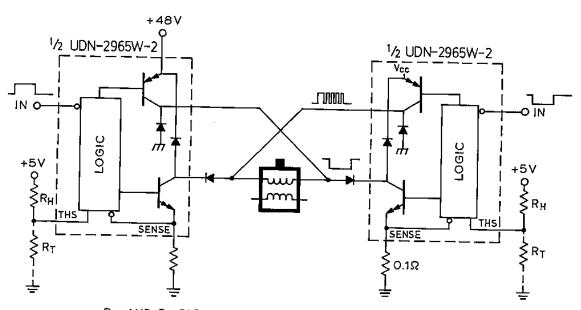

Crossover current protection has been incorporated to guard against common sink and source drivers being on at the same time. Circuitry on the input structure has been added to lock-out the sink driver when both driver inputs have been activated at the same time.

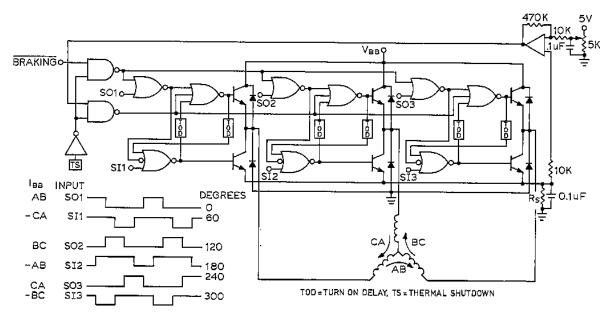

The UDN-20318 has extended flexibility with the and BRAKE functions. The chop function affects the source driver by switching it on and off while the chop is being toggled. In utilizing the BRAKE function the source drivers are turned on while the sink drivers are turned off. The BRAKING input is active low. Crossover-current protection is still in operation during BRAKING.

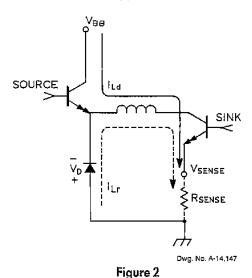

Both devices feature a common-emitter pin on the sink drivers. The emitter-current sense is useful in chopper-mode configurations. Thermal shutdown in these devices has been set to 165°C.

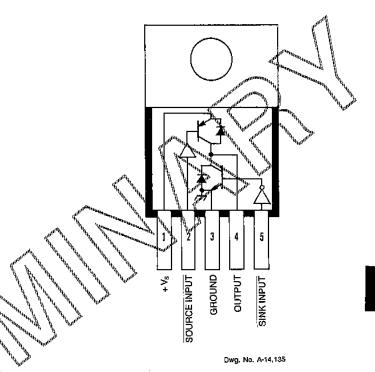

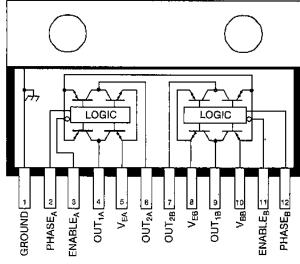

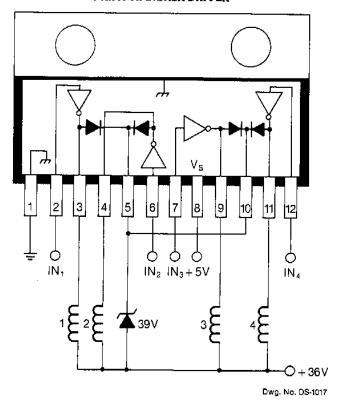

Dwg. No. A-14,202

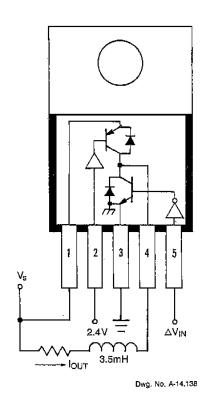

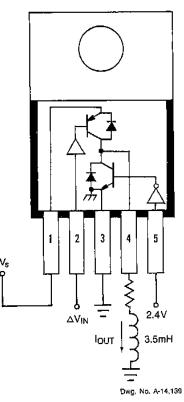

The UDN-2931B is supplied in a 16-pin dual inline package with heat-sink contact tabs. This package allows for ease of circuit-board insertion. The UDN-2931W is supplied in a 12-pin single in-line power-tab package. These packages allow for easy attachment of an external heat-sink for extended power dissipation capabilities.

### **ABSOLUTE MAXIMUM RATINGS** at $T_A = +25$ °C

| Motor Supply Voltage, V <sub>BB</sub>                      |

|------------------------------------------------------------|

| Output Current, I <sub>OUT</sub> (Peak)                    |

| (DC)                                                       |

| Input Voltage, V <sub>IN</sub>                             |

| Sense Voltage, V <sub>SENSE</sub>                          |

| Package Power Dissipation, Po                              |

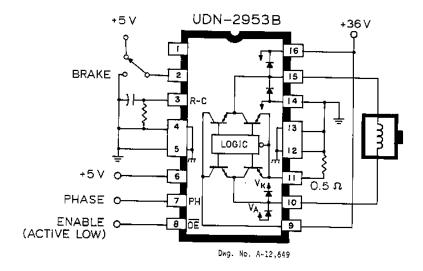

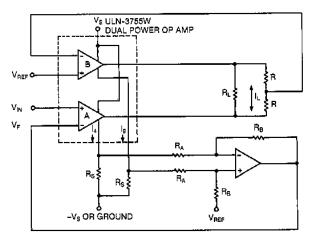

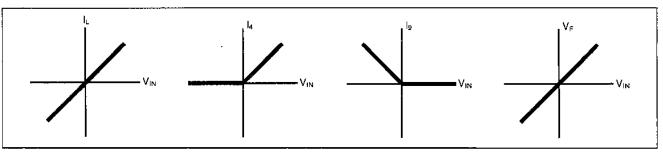

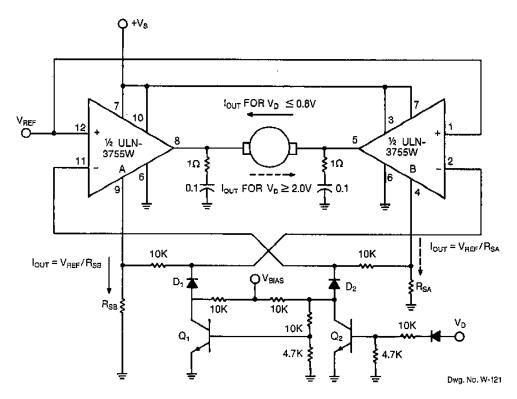

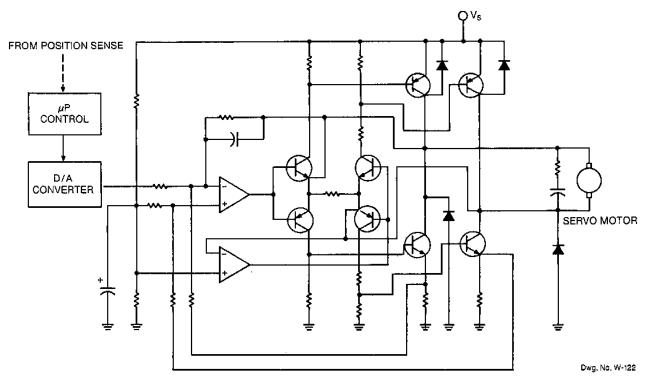

| (UDN-2931B)                                                |