# LOGY Positive High Voltage Ideal Diode-OR with Input Supply and Fuse Monitors

# **FEATURES**

- Replaces Power Schottky Diodes

- Controls N-Channel MOSFETs

- 0.5µs Turn-Off Time Limits Peak Fault Current

- Wide Operating Voltage Range: 9V to 80V

- Smooth Switchover without Oscillation

- No Reverse DC Current

- Monitors V<sub>IN</sub>, Fuse, and MOSFET Diode

- Available in 14-Lead (4mm × 3mm) DFN and 16-Lead SO Packages

## **APPLICATIONS**

- High Availability Systems

- AdvancedTCA® (ATCA) Systems

- +48V and -48V Distributed Power Systems

- Telecom Infrastructure

(T), LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

# DESCRIPTION

The LTC®4355 is a positive voltage ideal diode-OR controller that drives two external N-channel MOSFETs. Forming the diode-OR with N-channel MOSFETs instead of Schottky diodes reduces power consumption, heat dissipation and PC board area.

With the LTC4355, power sources can easily be ORed together to increase total system reliability. The LTC4355 can diode-OR two positive supplies or the return paths of two negative supplies, such as in a -48V system.

In the forward direction the LTC4355 controls the voltage drop across the MOSFET to ensure smooth current transfer from one path to the other without oscillation. If a power source fails or is shorted, fast turnoff minimizes reverse current transients.

Power fault detection indicates if the input supplies are not in regulation, the inline fuses are blown, or the voltages across the MOSFETs are greater than the fault threshold.

# TYPICAL APPLICATION

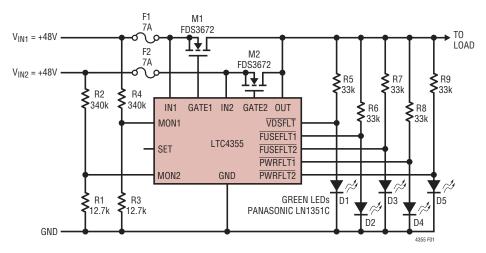

#### 7A FDB3632 V<sub>IN1</sub> = +48V -ΙŧΓ LOAD 7A FDB3632 $V_{1N2} = +48V$ ΙŧΙ **≶**22k **≨** 22k 22k **≥**340k **≨** 22k **≥** 340k 22k GATE1 IN2 GATE2 OUT IN1 VDSFLT MON1 FUSEFLT1 LTC4355 SET FUSEFLT2 PWRFLT1 MON2 PWRFLT2 GND **≨**12.7k **≥**12.7k **GREEN LEDs** PANASONIC LN13510 GND

+48V Diode-OR

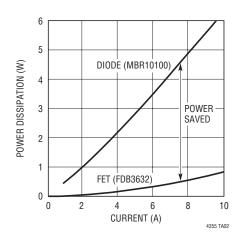

#### **Power Dissipation vs Load Current**

LINEAR

(Notes 1 2)

# **ABSOLUTE MAXIMUM RATINGS**

| (NUIGS 1, 2)                                       |

|----------------------------------------------------|

| Supply Voltages                                    |

| IN1, IN20.3V to 100V                               |

| OUT0.3V to 100V                                    |

| Input Voltages                                     |

| MON1, MON2, SET0.3V to 7V                          |

| Output Voltages                                    |

| GATE1 (Note 3) $V_{IN1} - 0.2V$ to $V_{IN1} + 13V$ |

| GATE2 (Note 3) $V_{IN2} - 0.2V$ to $V_{IN2} + 13V$ |

| PWRFLT1, PWRFLT2, VDSFLT,                          |

| FUSEFLT1, FUSEFLT20.3V to 8V                       |

| Operating Temperature Range          |               |

|--------------------------------------|---------------|

| LTC4355C                             | 0°C to 70°C   |

| LTC4355I                             | 40°C to 85°C  |

| Storage Temperature Range            |               |

| DFN Package                          | 65°C to 125°C |

| SO Package                           | 65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |               |

| SO Package                           | 300°C         |

|                                      |               |

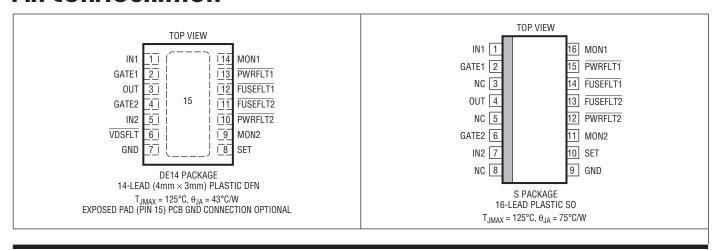

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|---------------|---------------------------------|-------------------|

| LTC4355CDE#PBF   | LTC4355CDE#TRPBF | 4355          | 14-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4355IDE#PBF   | LTC4355IDE#TRPBF | 4355          | 14-Lead (4mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4355CS#PBF    | LTC4355CS#TRPBF  | LTC4355CS     | 16-Lead Plastic SO              | 0°C to 70°C       |

| LTC4355IS#PBF    | LTC4355IS#TRPBF  | LTC4355IS     | 16-Lead Plastic SO              | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*Temperature grades are identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

LINEAR TECHNOLOGY

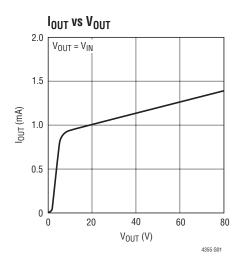

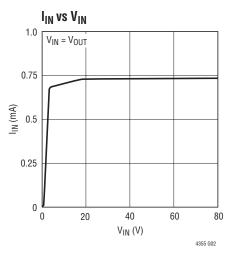

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . 9V < $V_{OUT}$ < 80V, unless otherwise noted.

| SYMBOL                     | PARAMETER                                                                    | CONDITIONS                                                               |   | MIN               | TYP                | MAX               | UNITS       |

|----------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|---|-------------------|--------------------|-------------------|-------------|

| $V_{OUT}$                  | Operating Supply Range                                                       |                                                                          | • | 9                 |                    | 80                | V           |

| I <sub>OUT</sub>           | Supply Current                                                               |                                                                          | • |                   | 2                  | 3                 | mA          |

| I <sub>INX</sub>           | INx Pin Input Current                                                        | GATE High                                                                | • | 0.5               | 0.6                | 1.2               | mA          |

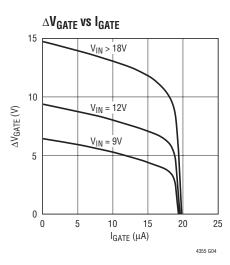

| $\Delta V_{GATEx}$         | External N-Channel Gate Drive (V <sub>GATEx</sub> – V <sub>INx</sub> )       | V <sub>OUT</sub> = 20V to 80V<br>V <sub>OUT</sub> = 9V to 20V            | • | 10<br>4.5         | 14<br>6            | 18<br>18          | V           |

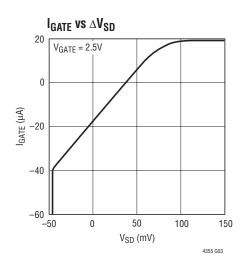

| I <sub>GATEX(UP)</sub>     | External N-Channel Gate Pull-Up Current                                      | $V_{GATE} = V_{INx},$<br>$V_{INx} - V_{OUT} = 100mV$                     | • | -14               | -20                | -26               | μА          |

| I <sub>GATEX(DN)</sub>     | External N-Channel Gate Pulldown in Fault Condition                          | Gate Drive Off, V <sub>GATEx</sub> = V <sub>INx</sub> +5V                | • | 1                 | 2                  |                   | A           |

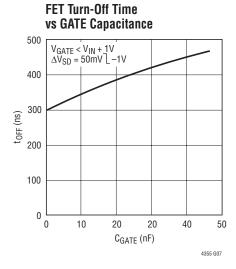

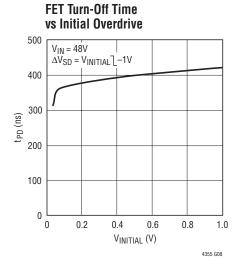

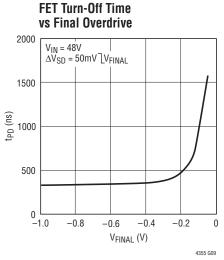

| t <sub>OFF</sub>           | Gate Turn-Off Time                                                           | $V_{INX} - V_{OUT} = 55mV \boxed{-1V}$<br>$V_{GATEX} - V_{INX} < 1V$     | • |                   | 0.3                | 0.4               | μs          |

| V <sub>MONx(TH)</sub>      | MONx Pin Threshold Voltage                                                   | V <sub>MONx</sub> Rising                                                 | • | 1.209             | 1.227              | 1.245             | V           |

| V <sub>MONx(HYST)</sub>    | MONx Pin Hysteresis Voltage                                                  |                                                                          | • | 10                | 30                 | 45                | mV          |

| I <sub>MONx(IN)</sub>      | MONx Pin Input Current                                                       | V <sub>MONx</sub> = 1.23V                                                | • |                   | 0                  | ±1                | μА          |

| V <sub>INx(TH)</sub>       | INx Pin Threshold Voltage                                                    | V <sub>INx</sub> Rising                                                  | • | 3                 | 3.5                | 4                 | V           |

| V <sub>INx(HYST)</sub>     | INx Pin Hysteresis Voltage                                                   |                                                                          | • | 25                | 75                 | 150               | mV          |

| $\Delta V_{SD}$            | Source-Drain Regulation Voltage (V <sub>INx</sub> – V <sub>OUT</sub> )       | $V_{GATEX} - V_{INX} = 2.5V$                                             | • | 10                | 25                 | 55                | mV          |

| $\Delta V_{SD(FLT)}$       | Short-Circuit Fault Voltage<br>(V <sub>INx</sub> – V <sub>OUT</sub> ) Rising | $SET = 0V$ $SET = 100k\Omega$ $SET = Hi-Z$                               | • | 0.2<br>0.4<br>1.3 | 0.25<br>0.5<br>1.5 | 0.3<br>0.6<br>1.6 | V<br>V<br>V |

| $\Delta V_{SD(FLT)(HYST)}$ | Short-Circuit Fault Hysteresis Voltage                                       |                                                                          |   |                   | 30                 |                   | mV          |

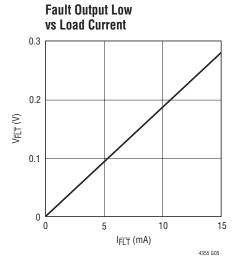

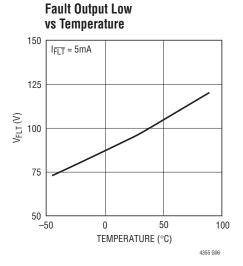

| V <sub>F,</sub> r,L        | PWRFLTx, FUSEFLTx, VDSFLT Pins<br>Output Low                                 | I <sub>PWRFLTx</sub> , I <sub>FUSEFLTx</sub> , I <sub>VDSFLT</sub> = 5mA | • |                   | 100                | 200               | mV          |

| l <sub>'F'L'T</sub>        | PWRFLTx, FUSEFLTx, VDSFLT Pins<br>Leakage Current                            | V <sub>PWRFLTx</sub> , V <sub>FUSEFLTx</sub> , V <sub>VDSFLT</sub> = 5V  | • |                   | 0                  | ±1                | μА          |

| R <sub>SET(L)</sub>        | SET Resistance Range for $\Delta V_{SD(FLT)} = 0.25V$                        |                                                                          | • | 0                 |                    | 5                 | kΩ          |

| R <sub>SET(M)</sub>        | SET Resistance Range for $\Delta V_{SD(FLT)} = 0.5V$                         |                                                                          | • | 50                |                    | 150               | kΩ          |

| R <sub>SET(H)</sub>        | SET Resistance Range for $\Delta V_{SD(FLT)} = 1.5V$                         |                                                                          | • | 1                 |                    |                   | MΩ          |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into pins are positive, all voltages are referenced to GND unless otherwise specified.

**Note 3:** The GATEx pins are internally limited to a minimum of 13V above INx. Driving these pins beyond the clamp may damage the part.

# TYPICAL PERFORMANCE CHARACTERISTICS

4355fa

# PIN FUNCTIONS (DE/S Packages)

**EXPOSED PAD (Pin 15, DE Package Only):** Exposed pad may be left open or connected to GND.

**FUSEFLTx** (**Pins 11,12/13,14**): Fuse Fault Outputs. Open-drain output that pulls to GND when  $V_{INx} < 3.5V$ , indicating that the fuse has blown open. Otherwise, this output is high-impedance. Connect to GND if unused.

GATEx (Pins 2,4/2,6): Gate Drive Outputs. The GATE pins pull high, enhancing the N-channel MOSFET when the load current creates more than 25mV of voltage drop across the MOSFET. When the load current is small, the gates are actively driven to maintain 25mV across the MOSFET. If the reverse current develops more than –25mV of voltage drop across a MOSFET, a fast pulldown circuit quickly connects the GATE pin to the IN pin, turning off the MOSFET. Limit the capacitance between the GATE and IN pins to less than 0.1μF.

GND (7/9): Device Ground.

INx (Pins 1,5/1,7): Input Voltages and GATE Fast Pulldown Returns. The IN pins are the anodes of the ideal diodes and connect to the sources of the N-channel MOSFETs. The voltages sensed at these pins are used to control the source-drain voltages across the MOSFETs and are used by the fault detection circuits that drive the PWRFLT, FUSEFLT, and VDSFLT pins. The GATE fast pulldown current is returned through the IN pins. Connect these pins as close to the MOSFET sources as possible. Connect to OUT if unused.

**MONx (Pins 9,14/11,16):** Input Supply Monitors. These pins are used to sense the input supply voltages. Connect these pins to external resistive dividers between the input

supplies and GND. If  $V_{MONx}$  falls below 1.23V, the  $\overline{PWRFLTx}$  pin pulls to GND. Connect to GND if unused.

**OUT (Pin 3/4):** Drain Voltage Sense and Positive Supply Input. OUT is the diode-OR output of IN1 and IN2. It connects to the common drain connection of the N-channel MOSFETs. The voltage sensed at this pin is used to control the source-drain voltages across the MOSFETs and is used by the fault detection circuits that drive the PWRFLT and VDSFLT pins. The LTC4355 is powered from the OUT pin.

**PWRFLTx** (**Pins 10,13/12,15**): Power Fault Outputs. Open-drain output that pulls to GND when  $V_{MONx}$  falls below 1.23V or the forward voltage across the MOSFET exceeds  $\Delta V_{SD(FLT)}$ . When  $V_{MONx}$  is above 1.23V and the forward voltage across the MOSFET is less than  $\Delta V_{SD(FLT)}$ ,  $\overline{PWRFLTx}$  is high-impedance. Connect to GND if unused.

**SET (Pin 8/10):**  $\Delta V_{SD(FLT)}$  Threshold Configuration Input. Tying SET to GND, to a  $100k\Omega$  resistor connected to GND, or leaving SET open configures the  $\Delta V_{SD(FLT)}$  forward voltage fault threshold to 250mV, 500mV, or 1.5V respectively. When the voltage across a MOSFET exceeds  $\Delta V_{SD(FLT)}$ , the  $\overline{VSDFLT}$  pin and at least one of the  $\overline{PWRFLT}$  pins pull to GND.

VDSFLT (Pin 6, DE Package Only): MOSFET Fault Output. Open-drain output that pulls to GND when the forward voltage across either MOSFET exceeds  $\Delta V_{SD(FLT)}$ . PWRFLT1 or PWRFLT2 also pulls low to indicate which MOSFET's forward voltage drop exceeds  $\Delta V_{SD(FLT)}$ . Otherwise, this pin is high-impedance. Connect to GND if unused.

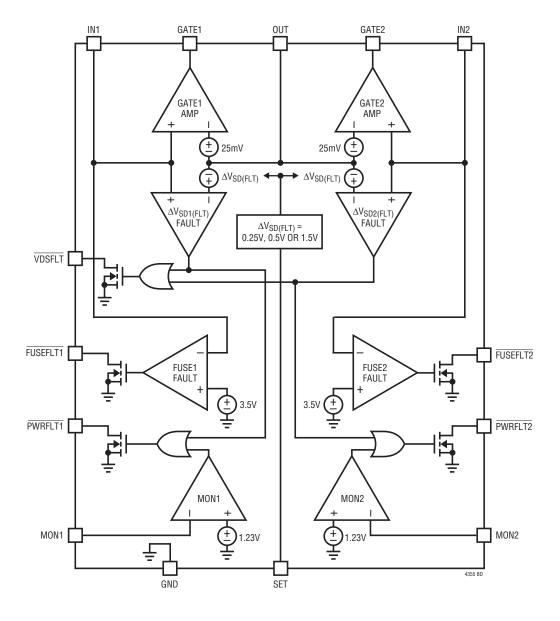

# **BLOCK DIAGRAM**

# **OPERATION**

High availability systems often employ parallel-connected power supplies or battery feeds to achieve redundancy and enhance system reliability. ORing diodes have been a popular means of connecting these supplies at the point of load. The disadvantage of this approach is the forward voltage drop and resulting efficiency loss. This drop reduces the available supply voltage and dissipates significant power. Using N-channel MOSFETs to replace Schottky diodes reduces the power dissipation and eliminates the need for costly heat sinks or large thermal layouts in high power applications.

The LTC4355 is a positive voltage diode-OR controller that drives two external N-channel MOSFETs as pass transistors to replace ORing diodes. The IN and OUT pins form the anodes and cathodes of the ideal diodes. The source pins of the external MOSFETs are connected to the IN pins. The drains of the MOSFETs are connected together at the OUT pin, which is the positive supply of the device. The gates of the external MOSFETs are driven by the LTC4355 to regulate the voltage drop across the pass transistors.

At power-up, the initial load current flows through the body diode of the MOSFET with the higher INx voltage. The associated GATEx pin immediately ramps up and turns on the MOSFET. The amplifier tries to regulate the voltage drop across the source and drain connections to 25mV. If the load current causes more than 25mV of drop, the MOSFET gate is driven fully on and the voltage drop is equal to  $R_{\rm DS(ON)} \bullet I_{\rm LOAD}$ .

When the power supply voltages are nearly equal, this regulation technique ensures that the load current is smoothly shared between the MOSFETs without oscillation. The current flowing through each pass trans-

istor depends on the  $R_{DS(ON)}$  of each MOSFET and the output impedances of the supplies.

In the event of a supply failure, such as if the supply that is conducting most or all of the current is shorted to GND, reverse current flows temporarily through the MOSFET that is on. This current is sourced from any load capacitance and from the second supply through the body diode of the other MOSFET. The LTC4355 quickly responds to this condition, turning off the MOSFET in about 500ns. This fast turn-off prevents the reverse current from ramping up to a damaging level.

In the case where the forward voltage drop exceeds the configurable fault threshold,  $\Delta V_{SD(FLT)}$ , the  $\overline{VDSFLT}$  pin pulls low. Using this pin to shunt current away from an LED or optocoupler provides an indication that a pass transistor has either failed or has excessive forward current. Additionally, in this condition the  $\overline{PWRFLT1}$  or  $\overline{PWRFLT2}$  pin pulls low to identify the faulting channel.

The  $\overline{PWRFLT}$  pins also indicate if an input supply is within regulation. When  $V_{MON1} < 1.23V$  or  $V_{MON2} < 1.23V$ , the corresponding  $\overline{PWRFLT}$  pin pulls low to indicate that the input supply is low, turning off an optional LED or optocoupler.

The FUSEFLT pins indicate the status of input fuses. If the voltage at one of the IN pins is less than 3.5V, the corresponding FUSEFLT pin pulls low. The IN pins sink a minimum of 0.5mA to guarantee that the IN pin will pull low when the input fuse is blown open. Note that the FUSEFLT pin will activate if the input supply is less than 3.5V even if the fuse is intact.

#### **MOSFET Selection**

The LTC4355 drives N-channel MOSFETs to conduct the load current. The important features of the MOSFETs are on-resistance  $R_{DS(0N)}$ , the maximum drain-source voltage  $V_{DSS}$ , and the threshold voltage.

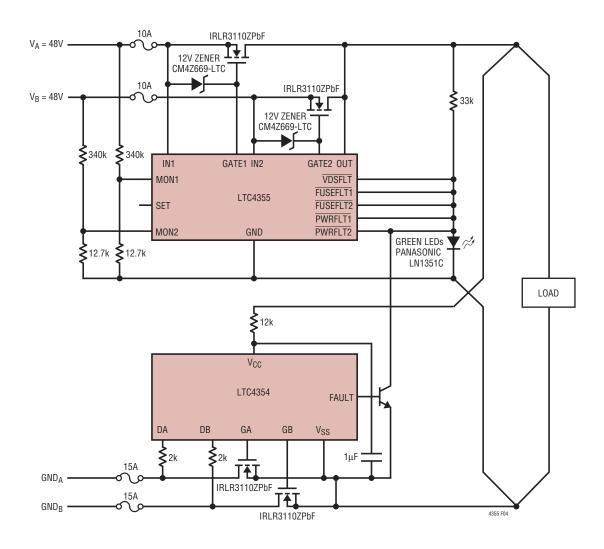

The gate drive for the MOSFET is guaranteed to be greater than 4.5V when the supply voltage at  $V_{OUT}$  is between 9V and 20V. When the supply voltage at  $V_{OUT}$  is greater than 20V, the gate drive is guaranteed to be greater than 10V. The gate drive is limited to less than 18V. This allows the use of logic level threshold N-channel MOSFETs and standard N-channel MOSFETs above 20V. An external zener diode can be used to clamp the potential from the MOSFET's gate to source if the rated breakdown voltage is less than 18V. See the circuit in Figure 4 for an example.

The maximum allowable drain-source voltage,  $BV_{DSS}$ , must be higher than the supply voltages. If an input is connected to GND, the full supply voltage will appear across the MOSFET.

If the voltage drop across either MOSFET exceeds the configurable  $\Delta V_{SD(FLT)}$  fault threshold, the  $\overline{VDS-FLT}$  pin and the  $\overline{PWRFLT}$  pin corresponding to the faulting channel pull low. The  $R_{DS(ON)}$  should be small enough to conduct the maximum load current while not triggering a fault, and to stay within the MOSFET's power rating at the maximum load current (I²  $\bullet$   $R_{DS(ON)}$ ).

#### **Fault Conditions**

The LTC4355 monitors fault conditions and shunts current away from LEDs or optocouplers, turning each one off to indicate a specific fault condition (see Table 1).

When the voltage drop across the pass transistor is higher than the configurable  $\Delta V_{SD(FLT)}$  fault threshold, the internal pulldown at the  $\overline{VDSFLT}$  pin and the  $\overline{PWRFLT1}$  or  $\overline{PWRFLT2}$  pin corresponding to the faulting channel turns on. The  $\Delta V_{SD(FLT)}$  threshold is configured by the SET pin. Tying SET to GND, tying SET to a 100k $\Omega$  resistor connected to GND, or floating SET configures  $\Delta V_{SD(FLT)}$  to 250mV, 500mV, or 1.5V respectively.

Fault conditions that may cause a high voltage across the pass transistor include: a MOSFET open on the higher

supply, excessive MOSFET current due to overcurrent on the load or a shorted MOSFET on the lower supply. During startup or when a switchover between supplies occurs, the VDSFLT pin and PWRFLT1 or PWRFLT2 pin may momentarily indicate that the forward voltage has exceeded the programmed threshold during the short interval when the MOSFET gate ramps up and the body diode conducts.

The PWRFLT pins are additionally used to indicate if either input supply is below its normal regulation range. If the voltage at the MON1 or MON2 pin is less than V<sub>MON(TH)</sub>, typically 1.23V, the corresponding PWRFLT1 or PWRFLT2 pin will pull low. A resistive divider connected to the input supply drives the MON pin for the corresponding supply, configuring the PWRFLT threshold for that supply. Be sure to account for the tolerance of the MON pin threshold, the resistor tolerances, and the regulation range of the supply being monitored. Also, ensure that the voltage on the MON pin will not exceed 7V.

The FUSEFLT pins are used to indicate the status of the input fuses. If one of the IN pins falls below  $V_{INx(TH)}$ , typically 3.5V, the  $\overline{FUSEFLT}$  pin corresponding to that supply will pull low. The IN pins each sink a minimum of 0.5mA,

Table 1. Fault Table

| $\Delta V_{SD1}$ < $\Delta V_{SD(FLT)}$ | V <sub>IN1</sub> > 3.5V | V <sub>MON1</sub> > 1.23V | VDSFLT*  | FUSEFLT1 | PWRFLT1  |

|-----------------------------------------|-------------------------|---------------------------|----------|----------|----------|

| True                                    | True                    | True                      | Hi-Z     | Hi-Z     | Hi-Z     |

| True                                    | True                    | False                     | Hi-Z     | Hi-Z     | Pulldown |

| True                                    | False                   | True                      | Hi-Z     | Pulldown | Hi-Z     |

| True                                    | False                   | False                     | Hi-Z     | Pulldown | Pulldown |

| False                                   | True                    | True                      | Pulldown | Hi-Z     | Pulldown |

| False                                   | True                    | False                     | Pulldown | Hi-Z     | Pulldown |

| False                                   | False                   | True                      | Pulldown | Pulldown | Pulldown |

| False                                   | False                   | False                     | Pulldown | Pulldown | Pulldown |

$<sup>^*\</sup>Delta V_{SD2} < \Delta V_{SD(FLT)}$

enough to pull the pin low after an input fuse blows open. If there is a possibility that the MOSFET leakage current can be greater than 0.5mA, a resistor can be connected between the IN pin and GND to sink more current. Note that if the input supply voltage is less than  $V_{INx(TH)}$  the FUSEFLT pin will pull low.

4355fa

#### **System Power Supply Failure**

The LTC4355 automatically supplies load current from the system input supply with the higher voltage. If this supply shorts to ground, reverse current begins to flow through the pass transistor temporarily and the transistor begins to turn off. When this reverse current creates –25mV of voltage drop across the drain and source pins of the pass transistor, a fast pulldown circuit engages to drive the gate low faster.

The remaining system power supply delivers the load current through the body diode of its pass transistor until the channel turns on. The LTC4355 ramps the gate up with  $20\mu A$ , turning on the N-channel MOSFET to reduce the voltage drop across it.

When the capacitances at the inputs and output are very small, large changes in current can cause inductive transients that exceed the 100V Absolute Maximum Ratings of the pins. A surge suppressor (TransZorb) at the output will minimize this ringing.

# **Loop Stability**

The servo loop is compensated by the parasitic capacitance of the power N-channel MOSFET. No further compensation components are normally required. In the case when a MOSFET with less than 1000pF gate capacitance is chosen, a 1000pF compensation capacitor connected across the gate and source pins might be required.

#### **Design Example**

The following design example demonstrates the calculations involved for selecting components in a 36V to 72V system with 5A maximum load current (see Figure 1).

First, choose the N-channel MOSFET. The 100V, FDS3672 in the SO-8 package with  $R_{DS(ON)}$  =  $22m\Omega(max)$  offers a good solution. The maximum voltage drop across it is:

$$\Delta V = 5A \cdot 22m\Omega = 110mV$$

The maximum power dissipation in the MOSFET is a mere:

$$P = 5A \cdot 110 \text{mV} = 0.55 \text{W}$$

Next, select the resistive dividers that guarantee the PWRFLT pins will not assert when the input supplies are above 36V. The maximum  $V_{MONx(TH)}$  is 1.245V and the maximum  $I_{MONx(IN)}$  is 1 $\mu$ A. Choose a 1% tolerance resistor R1 = 12.7 $\mu$ C. Then,

$$\begin{split} I_{R2} &= \frac{V_{MONx(TH)}}{R1(MIN)} + I_{MONx(TH)(MAX)} \\ &= \frac{1.245V}{12.7k\Omega(-1\%)} + 1\mu A = 100\mu A \end{split}$$

Use I<sub>R2</sub> to choose R2.

$$R2 = \frac{36V - 1.245V}{100\mu A} = 348k\Omega$$

Figure 1. 36V to 72V/5A Design Example

Adjust R2 down by 1% to 344k $\Omega$  to account for its tolerance. The next lower standard resistor value is R2 = 340k $\Omega$ .

The LED D1, a Panasonic Green LN1351C, requires at least 1mA of current to fully turn on. Therefore, R5 is set to  $33k\Omega$  to accommodate the lowest input supply voltage of 36V.

#### **Layout Considerations**

The following advice should be considered when laying out a printed circuit board for the LTC4355.

The inputs to the servo amplifiers, IN1, IN2, and OUT should be connected as closely as possible to the MOSFETs' terminals for good accuracy.

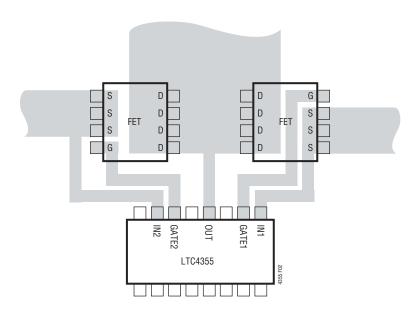

Keep the traces to the MOSFETs wide and short. The PCB traces associated with the power path through the MOSFETs should have low resistance (see Figure 2).

For the DFN package, pin spacing may be a concern at voltages greater then 30V. Check creepage and clearance guidelines to determine if this is an issue. Use no-clean solder to minimize PCB contamination.

Figure 2. Layout Considerations

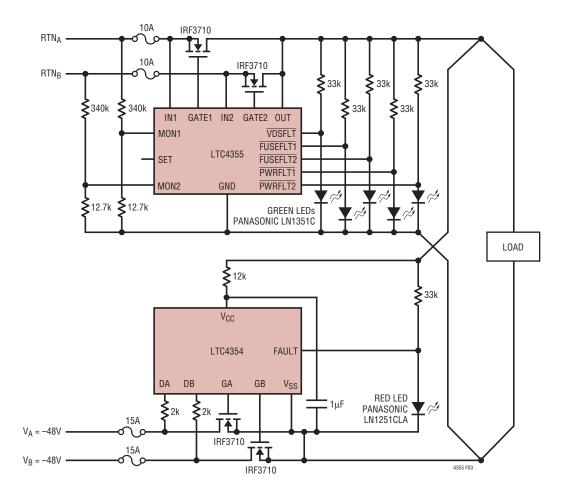

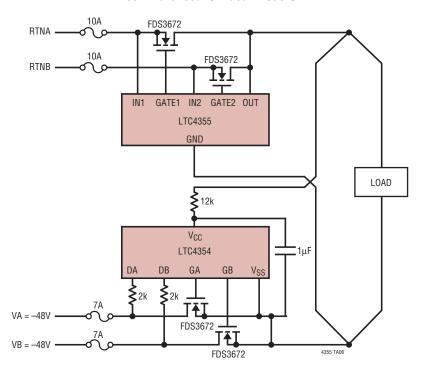

Figure 3. -36V to -72V/10A with Positive Supply and Negative Supply Diode-ORing

Figure 4. 36V to 72V/10A with Positive Supply and Negative Supply Diode-ORing, Combined Fault Outputs, and Zener Clamps on MOSFET Gates

# TYPICAL APPLICATIONS

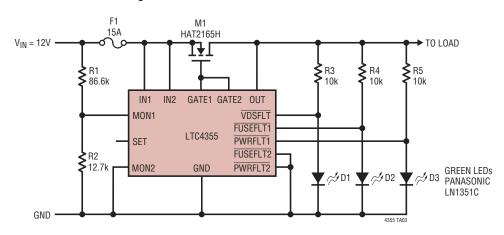

#### Single 12V/15A Ideal Diode with Parallel Drivers

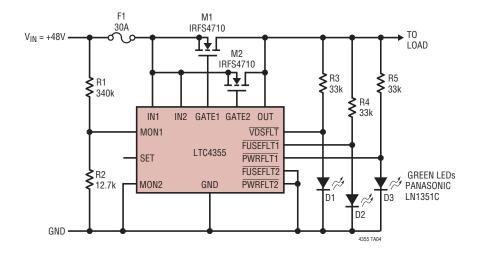

#### Single 36V to 72V/30A Ideal Diode Using Parallel MOSFETs

# TYPICAL APPLICATIONS

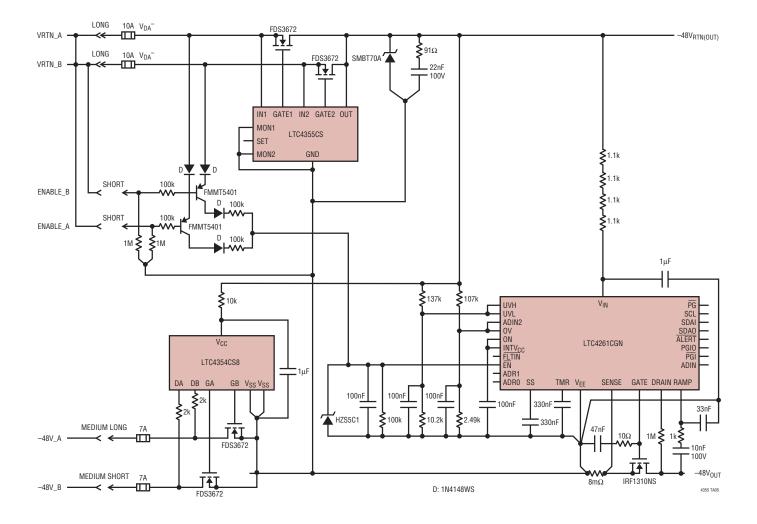

AdvancedTCA with High-Side and Low-Side Ideal Diode-OR and Hot Swap Controller with I<sup>2</sup>C Current and Voltage Monitor

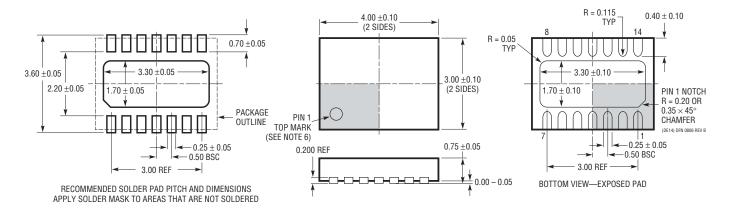

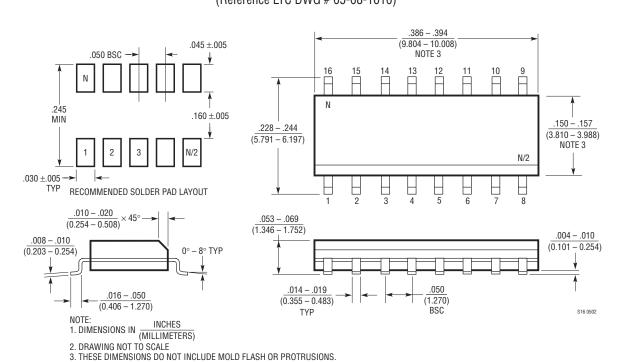

# PACKAGE DESCRIPTION

#### **DE Package** 14-Lead Plastic DFN (4mm × 3mm)

(Reference LTC DWG # 05-08-1708 Rev A)

#### NOTE:

- 1. DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WGED-3) IN JEDEC PACKAGE OUTLINE MO-229

- 2. DRAWING NOT TO SCALE

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

- MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

#### S Package 16-Lead Plastic Small Outline (Narrow .150 Inch) (Reference LTC DWG # 05-08-1610)

4355fa

# TYPICAL APPLICATION

#### 200W AdvancedTCA Ideal Diode-OR

# **RELATED PARTS**

| PART NUMBER                                   | DESCRIPTION                                               | COMMENTS                                                                                                   |

|-----------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| LT1640AH/LT1640AL                             | Negative High Voltage Hot Swap™ Controllers in SO-8       | Negative High Voltage Supplies From -10V to -80V                                                           |

| LT1641-1/LT1641-2                             | Positive High Voltage Hot Swap Controllers                | Active Current Limiting, Supplies From 9V to 80V                                                           |

| LTC1921                                       | Dual –48V Supply and Fuse Monitor                         | UV/OV Monitor, -10V to -80V Operation, MSOP Package                                                        |

| LT4250                                        | -48V Hot Swap Controller                                  | Active Current Limiting, Supplies From –20V to –80V                                                        |

| LTC4251/LTC4251-1/<br>LTC4251-2               | -48V Hot Swap Controllers in SOT-23                       | Fast Active Current Limiting, Supplies From –15V                                                           |

| LTC4252-1/LTC4252-2/<br>LTC4252-1A/LTC4252-2A | -48V Hot Swap Controllers in MS8/MS10                     | Fast Active Current Limiting, Supplies From –15V, Drain Accelerated Response                               |

| LTC4253                                       | -48V Hot Swap Controller with Sequencer                   | Fast Active Current Limiting, Supplies From –15V, Drain Accelerated Response, Sequenced Power Good Outputs |

| LT4256                                        | Positive 48V Hot Swap Controller with Open-Circuit Detect | Foldback Current Limiting, Open-Circuit and Overcurrent Fault Output, Up to 80V Supply                     |

| LTC4260                                       | Positive High Voltage Hot Swap Controller                 | With I <sup>2</sup> C and ADC, Supplies from 8.5V to 80V                                                   |

| LTC4261                                       | Negative High Voltage Hot Swap Controller                 | With I <sup>2</sup> C and 10-Bit ADC, Adjustable Inrush and Overcurrent Limits                             |

| LTC4350                                       | Hot Swappable Load Share Controller                       | Output Voltage: 1.2V to 20V, Equal Load Sharing                                                            |

| LT4351                                        | MOSFET Diode-OR Controller                                | External N-Channel MOSFETs Replace ORing Diodes, 1.2V to 20V                                               |

| LTC4354                                       | Negative Voltage Diode-OR Controller and Monitor          | Controls Two N-Channel MOSFETs, 1µs Turn-Off, 80V Operation                                                |

Hot Swap is a trademark of Linear Technology Corporation.

LT 0907 REV A • PRINTED IN USA

LINEAR TECHNOLOGY CORPORATION 2007