# Hot-Swappable I<sup>2</sup>C Isolators

#### **FEATURES**

- Bidirectional I<sup>2</sup>C Communication Between Two Isolated Buses

- Full Isolation with Inexpensive Ethernet Transformers or Capacitors

- Low Voltage Level Shifting

- I<sup>2</sup>C Maximum Operating Frequency: 100kHz for LTC4310-1 400kHz for LTC4310-2

- I<sup>2</sup>C Specification Compliant V<sub>OL</sub>, V<sub>IL</sub>

- ±5kV Human Body Model ESD Protection

- Rise Time Accelerators

- SDA, SCL Hot-Swapping

- Very Low Shutdown Current

- Stuck Bus Disconnect and Recovery

- Thermal Shutdown

- 10-Lead MSOP and 3mm × 3mm DFN Packages

#### **APPLICATIONS**

- Isolated I<sup>2</sup>C, SMBus and PMBus Interfaces

- Isolated Power Supplies

- Positive-to-Negative Rail Communications

- Power-over-Ethernet

#### DESCRIPTION

The LTC®4310 provides bidirectional I²C communications between two I²C buses whose grounds are isolated from one another. Each LTC4310 encodes I²C bus logic states into signals that are transmitted across an isolation barrier to another LTC4310. The receiving LTC4310 decodes the transmission and drives its I²C bus to the appropriate logic state. The isolation barrier can be bridged by an inexpensive Ethernet, or other transformer, to achieve communications across voltage differences reaching thousands of volts, or it can be bridged by capacitors for lower voltage isolation. The LTC4310-1 is intended for use in 100kHz I²C systems. The LTC4310-2 is intended for 400kHz I²C systems.

Rise time accelerators provide strong pull-up currents on SCL and SDA rising edges to meet rise time specifications for heavily loaded systems. Data and clock Hot Swap<sup>TM</sup> circuitry prevent data corruption when a card is inserted into or removed from a live bus. When a bus is stuck low for 37ms, the LTC4310 turns off its pull-down devices and generates up to sixteen clocks and a STOP bit in an attempt to free the bus. Driving EN low sets the LTC4310 in a very low current shutdown mode to conserve power.

∠T, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. Hot Swap is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

# TYPICAL APPLICATION

#### 1500V Isolated I<sup>2</sup>C System

#### 10/100Base-TX **ISOLATED** 3.3V ETHERNET TRANSFORMER 0.01µF 0.01μF 5V VCC TXP RXP Vcc SCL ٥v SDA $3.3k \le 3.3k$ 3.3k **≤ ₹**3.3k **7**0.01µF LTC4310-1 LTC4310-1 SDA TXN SDA RXN SDA1 SDA2 20kV/µs SCL RXP TXP SCL SCL<sub>2</sub> ΕN EN READY 0.01µl READY **GND RXN** TXN GND 431012 TA01a

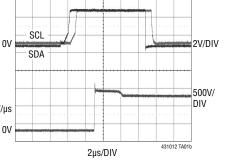

# LTC4310 Operating Through 20kV/µs Common Mode Transient

431012f

# **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 4)

| Input Supply Voltage (V <sub>CC</sub> ) –0.3V to 6 | V          |

|----------------------------------------------------|------------|

| Input and Bidirectional Pin Voltages               |            |

| SCL, SDA, EN, RXP, RXN0.3V to 6                    | V          |

| Output Voltages                                    |            |

| READY0.3V to 6                                     | V          |

| TXP, TXN $-0.3V$ to $V_{CC}$ + 0.3V (6V Max        | <b>(</b> ) |

| Maximum Sink Current (SDA, SCL, READY)30m.         | À          |

| <b>Operating Ambient Temperature Range</b> |                |

|--------------------------------------------|----------------|

| LTC4310C                                   | 0°C to 70°C    |

| LTC4310I                                   | –40°C to 85°C  |

| Storage Temperature Range                  |                |

| DD                                         | –65°C to 125°C |

| MS                                         | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec)       |                |

| MS Package                                 | 300°C          |

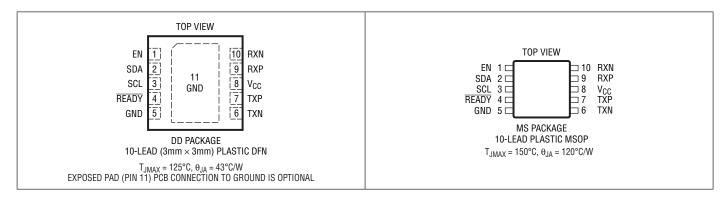

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC4310CDD-1#PBF | LTC4310CDD-1#TRPBF | LFCH          | 10-Lead (3mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4310IDD-1#PBF | LTC4310IDD-1#TRPBF | LFCH          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4310CMS-1#PBF | LTC4310CMS-1#TRPBF | LTFCG         | 10-Lead Plastic MSOP            | 0°C to 70°C       |

| LTC4310IMS-1#PBF | LTC4310IMS-1#TRPBF | LTFCG         | 10-Lead Plastic MSOP            | -40°C to 85°C     |

| LTC4310CDD-2#PBF | LTC4310CDD-2#TRPBF | LFCK          | 10-Lead (3mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4310IDD-2#PBF | LTC4310IDD-2#TRPBF | LFCK          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC4310CMS-2#PBF | LTC4310CMS-2#TRPBF | LTFCJ         | 10-Lead Plastic MSOP            | 0°C to 70°C       |

| LTC4310IMS-2#PBF | LTC4310IMS-2#TRPBF | LTFCJ         | 10-Lead Plastic MSOP            | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = 3.3V$ , unless otherwise noted.

| SYMBOL                        | PARAMETER                                                          | CONDITIONS                                                                                                                                             |   | MIN                    | TYP                    | MAX                   | UNITS        |

|-------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------|------------------------|-----------------------|--------------|

| Supplies                      | 1                                                                  | 1                                                                                                                                                      |   |                        |                        |                       |              |

| $V_{CC}$                      | Input Supply Range                                                 |                                                                                                                                                        | • | 3                      |                        | 5.5                   | V            |

| I <sub>CC</sub>               | Input Supply Current, LTC4310-1<br>Input Supply Current, LTC4310-2 | $\begin{aligned} &EN = V_{CC} = 5.5V,  SDA = SCL = V_{SDA,SCL(OL)} \\ &EN = V_{CC} = 5.5V,  SDA = SCL = V_{SDA,SCL(OL)} \end{aligned}$                 | • |                        | 6.5<br>7               | 8<br>8.5              | mA<br>mA     |

| I <sub>CC(SD)</sub>           | Shutdown Input Supply Current                                      | EN = 0V, V <sub>CC</sub> = 5.5V                                                                                                                        | • |                        | 0.1                    | ±10                   | μΑ           |

| V <sub>CCH(UVL)</sub>         | Input Supply Undervoltage Lockout<br>Rising Threshold Voltage      |                                                                                                                                                        | • | 2.1                    | 2.4                    | 2.7                   | V            |

| V <sub>CC(UVL, HYST)</sub>    | Input Supply Undervoltage Lockout<br>Hysteresis                    |                                                                                                                                                        | • | 90                     | 190                    | 270                   | m۷           |

| I <sup>2</sup> C Interface    |                                                                    |                                                                                                                                                        |   |                        |                        |                       |              |

| V <sub>SDA,SCL(OL)</sub>      | SDA, SCL Logic Low Output Voltage                                  | $I_{(SDA,SCL)} = 4mA, 500\mu A; V_{CC} = 3V, 5.5V$                                                                                                     | • | 310                    | 350                    | 380                   | mV           |

| V <sub>SDA,SCL(IL,R)</sub>    | SDA, SCL Controlled Rising Edge Rate<br>Turn-Off Threshold Voltage | V <sub>CC</sub> = 3V, 5.5V (Note 5)                                                                                                                    | • | 0.3 • V <sub>CC</sub>  | 0.35 • V <sub>CC</sub> | 0.4 • V <sub>CC</sub> | V            |

| V <sub>SDA,SCL(IL,F)</sub>    | SDA, SCL Logic Low Falling Input<br>Threshold Voltage              | V <sub>CC</sub> = 3V                                                                                                                                   | • | 0.4 • V <sub>CC</sub>  | 0.45 • V <sub>CC</sub> | 0.5 • V <sub>CC</sub> | V            |

| I <sub>SDA,SCL(OH)</sub>      | SDA, SCL Input Current                                             | SCL, SDA = $V_{CC}$ = 0V, 5.5V                                                                                                                         | • |                        | 0                      | ±5                    | μΑ           |

| I <sup>2</sup> C Interface Ti | ming                                                               |                                                                                                                                                        |   |                        |                        |                       |              |

| dV/dt <sub>RISE</sub>         | Bus Line Controlled Rising Edge Rate,<br>LTC4310-1                 | 0.35V < V <sub>BUS</sub> < 0.35 • V <sub>CC</sub> , V <sub>CC</sub> = 3V<br>0.35V < V <sub>BUS</sub> < 0.35 • V <sub>CC</sub> , V <sub>CC</sub> = 5.5V | • | 0.8<br>1.5             | 1.16<br>2.14           | 1.4<br>2.6            | V/µs<br>V/µs |

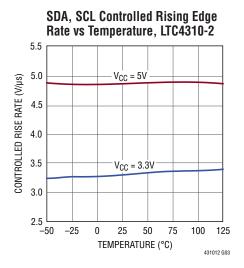

|                               | Bus Line Controlled Rising Edge Rate, LTC4310-2                    | 0.35V < V <sub>BUS</sub> < 0.35 • V <sub>CC</sub> , V <sub>CC</sub> = 3V<br>0.35V < V <sub>BUS</sub> < 0.35 • V <sub>CC</sub> , V <sub>CC</sub> = 5.5V | • | 2<br>3.9               | 3<br>5.4               | 3.9<br>6.9            | V/µs<br>V/µs |

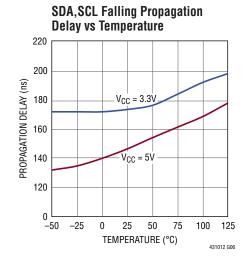

| t <sub>PHL</sub> (SDA,SCL)    | SDA, SCL High-to-Low Propagation<br>Delay                          | V <sub>CC</sub> = 5.5V (Note 3)                                                                                                                        | • |                        | 170                    | 270                   | ns           |

| f <sub>SCL(MAX)</sub>         | Maximum SCL Clock Frequency                                        | LTC4310-1<br>LTC4310-2                                                                                                                                 | • | 100<br>400             |                        |                       | kHz<br>kHz   |

| C <sub>IN</sub>               | SCL, SDA Input Capacitance                                         | SCL, SDA = V <sub>CC</sub> (Note 2)                                                                                                                    |   |                        |                        | 10                    | pF           |

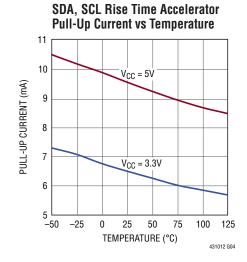

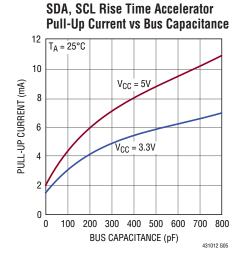

| Rise Time Acce                | elerators                                                          |                                                                                                                                                        |   |                        |                        |                       |              |

| V <sub>BOOST</sub>            | SDA, SCL Rise Time Accelerator<br>Activation Threshold Voltage     | V <sub>CC</sub> = 3V (Note 5)                                                                                                                          | • | 0.32 • V <sub>CC</sub> | 0.45 • V <sub>CC</sub> | 0.5 • V <sub>CC</sub> | V            |

| I <sub>BOOST</sub>            | SDA, SCL Rise Time Accelerator<br>Current                          | V <sub>CC</sub> = 3V                                                                                                                                   | • | 2                      | 6                      |                       | mA           |

| READY Open-D                  | •                                                                  |                                                                                                                                                        |   |                        |                        |                       |              |

| $V_{\overline{READY}(OL)}$    | READY Output Low Voltage                                           | I <sub>READY</sub> = 4mA                                                                                                                               | • |                        | 50                     | 400                   | mV           |

| I <sub>READY</sub> (OH)       | READY Off-Current                                                  | $\overline{\text{READY}} = V_{\text{CC}} = 5.5V$ , $\text{EN} = 0V$                                                                                    | • |                        | 0.1                    | ±10                   | μΑ           |

| Connection Con                | ntrol                                                              |                                                                                                                                                        |   |                        |                        |                       |              |

| V <sub>EN,RISE</sub>          | EN Rising Threshold Voltage                                        |                                                                                                                                                        | • |                        | 0.6 • V <sub>CC</sub>  | 0.9 • V <sub>CC</sub> | V            |

| V <sub>EN,FALL</sub>          | EN Falling Threshold Voltage                                       |                                                                                                                                                        | • | 0.1 • V <sub>CC</sub>  | 0.3 • V <sub>CC</sub>  |                       | V            |

| I <sub>EN(OH)</sub>           | EN Input Current                                                   | EN = V <sub>CC</sub> = 5.5V                                                                                                                            | • |                        | 0.1                    | ±10                   | μА           |

| t <sub>IDLE</sub>             | Bus Idle Time                                                      |                                                                                                                                                        | • | 75                     | 115                    | 155                   | μs           |

| t <sub>UVLO,EN_FILT</sub>     | Start-Up Filter Time                                               |                                                                                                                                                        | • | 700                    | 900                    | 1200                  | μs           |

| t <sub>STUCK</sub>            | SDA, SCL Bus Stuck Low Disconnect                                  |                                                                                                                                                        | • | 27                     | 37                     | 47                    | ms           |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{CC} = 3.3 \,\text{V}$ , unless otherwise noted.

| SYMBOL                 | PARAMETER                                        | CONDITIONS                                                  |   | MIN  | TYP  | MAX   | UNITS |

|------------------------|--------------------------------------------------|-------------------------------------------------------------|---|------|------|-------|-------|

| t <sub>MAX(TX)</sub>   | Maximum Time Between TXP, TXN<br>Transmit Events |                                                             | • | 0.85 | 1.15 | 1.45  | ms    |

| t <sub>MAX(RX)</sub>   | Maximum Time Between RXP, RXN<br>Receive Events  |                                                             | • | 3.4  | 4.6  | 5.8   | ms    |

| Transmit Outp          | uts                                              |                                                             |   |      |      |       |       |

| V <sub>TX(OL)</sub>    | TXP, TXN Single-Ended Output Low                 | $I_{SINK} = 100\mu A, V_{CC} = 3V$                          | • |      | 1.5  | 5     | mV    |

| V <sub>TX(OH)</sub>    | TXP, TXN Single-Ended Output High                | 15k $\Omega$ to GND on TXP, TXN; V <sub>CC</sub> = 3V, 5.5V | • | 0.95 | 1.25 | 1.52  | V     |

| t <sub>R(TX)</sub>     | TXP, TXN Output Rise Time                        | $C_{TXP}$ , $C_{TXN} = 20pF$                                | • |      | 1    | 3     | ns    |

| t <sub>F(TX)</sub>     | TXP, TXN Output Fall Time                        | $C_{TXP}$ , $C_{TXN} = 20pF$                                | • |      | 1    | 3     | ns    |

| t <sub>PWMIN(TX)</sub> | TXP, TXN Minimum Transmission<br>Pulse Width     | V <sub>CC</sub> = 3V, 5.5V                                  | • | 31.5 | 35   | 39    | ns    |

| Receive Input          | s                                                |                                                             |   |      |      |       |       |

| V <sub>RX(TH)</sub>    | RXP, RXN Differential High Level<br>Threshold    | RXP, RXN Pins; V <sub>CC</sub> = 3V, 5.5V                   | • | 0.3  | 0.5  | 0.875 | V     |

| t <sub>PWMIN(RX)</sub> | RXP, RXN Minimum Received Pulse<br>Width         | V <sub>CC</sub> = 3V, 5.5V                                  | • | 30   |      |       | ns    |

| R <sub>RX(IN)</sub>    | RXP, RXN Differential Input Resistance           |                                                             | • | 13   | 16.5 | 20    | kΩ    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2. Guaranteed by design, not tested in production.

**Note 3.** SDA, SCL high-to-low propagation delay is measured from the beginning of a new received message telling the LTC4310 to drive its SDA, SCL pins from high to low, to when the SDA, SCL lines have fallen below  $0.5 \bullet V_{CC}$ . It includes approximately 87ns required for an LTC4310 to

receive a message on the RXP and RXN pins, plus the time the LTC4310 requires to process the message and pass the low to the data and clock buffers, plus the time required by the buffers to drive their bus pins below  $0.5 \bullet V_{CC}.$

**Note 4.** All currents into pins are positive, all voltages are referenced to GND unless otherwise specified.

**Note 5.** Internal control circuitry prevents the rise time accelerators from activating until the rising edge rate control circuitry is off.

431012 G02

## TYPICAL PERFORMANCE CHARACTERISTICS

I<sub>CC</sub> vs Temperature, LTC4310-1 SDA = 0V  $V_{CC} = 5V$  $SCL = V_{CC}$ Icc (mA)  $V_{CC} = 3.3V$ 4.2 4.0 <del>-</del>50 -25 0 25 50 75 100 125 TEMPERATURE (°C) 431012 G01

SDA, SCL Controlled Rising Edge Rate vs Temperature, LTC4310-1

2.0  $V_{CC} = 5V$ 1.8  $V_{CC} = 3.3V$ 1.2  $V_{CC} = 3.3V$ TEMPERATURE (°C)

431012f

#### PIN FUNCTIONS

**EN (Pin 1):** Device Enable Input. Pulling EN up to  $V_{CC}$  sets the device in normal operation mode, allowing bus information to be sent and received across the barrier. Grounding EN disables communication across the barrier and debiases all internal circuitry, setting the device in a very low current shutdown mode. Connect to  $V_{CC}$  if unused.

**SDA** (Pin 2): Serial Bus Data Input/Output. This is the bidirectional data line for the two-wire bus. An external pull-up resistor or current source from SDA to a supply voltage greater than or equal to the  $V_{CC}$  voltage is required. See the Applications Information section for guidance on selecting the resistor or current source value. Do not leave open.

**SCL** (**Pin 3**): Serial Bus Clock Input/Output. This is the bidirectional clock line for the two-wire bus. An external pull-up resistor or current source from SCL to a supply voltage greater than or equal to the  $V_{CC}$  voltage is required. See the Applications Information section for guidance on selecting the resistor or current source value. Do not leave open.

**READY** (Pin 4): Device Receiving Indicator Output. READY is an open-drain digital output that pulls low when the LTC4310 is driving its SDA and SCL pins with the logic state information it is receiving on its RXP and RXN pins. Connect this pin to  $V_{CC}$  with a 10k resistor. This pin can be left open or tied to GND if unused.

**GND (Pin 5):** Device Ground.

**TXN (Pin 6):** Negative Transmit Output. Tie TXN to the negative side of the transformer primary winding or to the RXN pin of another LTC4310 through a ceramic capacitor. See the Applications Information section for guidance in selecting the capacitor value. Do not leave open.

**TXP (Pin 7):** Positive Transmit Output. Tie TXP to the positive side of the transformer primary winding or to the RXP pin of another LTC4310 through a ceramic capacitor. See the Applications Information section for guidance in selecting the capacitor value. Do not leave open.

$V_{CC}$  (Pin 8): Device Power Supply Input. Connect a bypass capacitor of at least 0.01 $\mu$ F directly between  $V_{CC}$  and GND.

**RXP (Pin 9):** Positive Receive Input. Tie RXP to the positive side of the transformer secondary winding or to the TXP pin of another LTC4310 through a ceramic capacitor. See the Applications Information section for guidance in selecting the capacitor value. Do not leave open.

**RXN (Pin 10):** Negative Receive Input. Tie RXN to the negative side of the transformer secondary winding or to the TXN pin of another LTC4310 through a ceramic capacitor. See the Applications Information section for guidance in selecting the capacitor value. Do not leave open.

**Exposed Pad (Pin 11) DFN Package Only:** The exposed pad may be left open or connected to device ground.

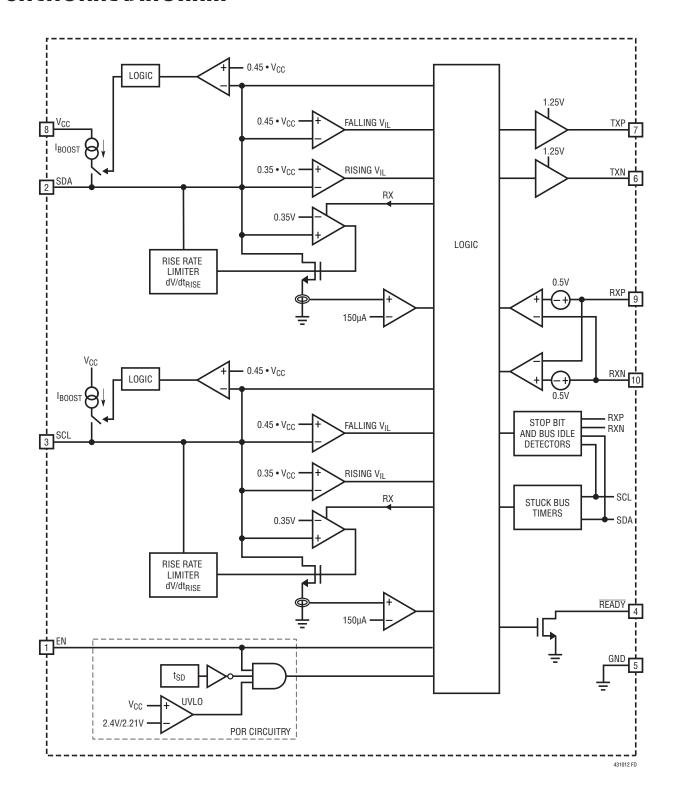

# **FUNCTIONAL DIAGRAM**

# **OPERATION** (LTC4310 refers to both LTC4310-1 and LTC4310-2)

The LTC4310 provides fully bidirectional communications between two I<sup>2</sup>C or SMBus buses whose grounds are isolated from one another. Clock stretching, clock synchronization, arbitration and data acknowledging all work seamlessly across the barrier, regardless of the locations of the master(s) and slave(s).

Referring to the application circuit shown in Figure 1, an LTC4310 is located on each side of the isolation barrier. Each LTC4310 contains logic detection circuitry that can differentiate externally driven SDA and SCL logic signals from its own output signals. Each LTC4310 converts the logic state of the externally driven signals into a sequence of pulses that are then transmitted across the isolation barrier via an Ethernet transformer (or coupling capacitors for low isolation voltage applications) to the other LTC4310. Each LTC4310 also receives and decodes corresponding pulses from the other LTC4310 and drives its SDA and SCL pins accordingly.

Transmissions occur on the TXP and TXN pins in a sequence of 1.25V pulses. The LTC4310 receives messages on its RXP and RXN pins. Signals having less than 500mV differential voltages are rejected to provide noise immunity against common-mode transients.

When the LTC4310 receives a message to drive SDA low, it regulates SDA to 0.35V. If an external device pulls SDA below 0.35V during this time, the LTC4310 detects this condition and immediately transmits a LOW to the other LTC4310.

When an external pull-down device drives SDA below  $0.45 \bullet V_{CC}$  from a logic high, TXP and TXN transmit a message across the isolation barrier instructing the other LTC4310 to drive its SDA line low.

When the external pull-down device turns off and SDA is rising between 0V and 0.35  $\bullet$  V<sub>CC</sub>, the LTC4310 limits the

bus rise rate to  $dV/dt_{RISE}$  via the rise rate limiter circuitry. It also transmits a high to the other LTC4310. If the SDA rise rate falls below the threshold, it is assumed that another pull-down on the bus has turned on and is pulling SDA low, and a command to pull the far side low is sent across the isolation barrier.

When SDA rises above 0.35 •  $V_{CC}$ , the rise rate limiter circuitry is deactivated. When SDA rises above 0.45 •  $V_{CC}$ , the rise time accelerator current  $I_{BOOST}$  is activated, which provides a strong, slew-limited pull-up current to reduce system rise time.

The LTC4310 contains power-on reset (POR) circuitry that sets the data and clock pins in a high impedance state and deactivates the transmit and receive circuitry until the EN voltage is high, the device is not in thermal shutdown and the  $V_{CC}$  voltage is above the 2.4V UVLO threshold voltage. The LTC4310 enters thermal shutdown when the die temperature exceeds 150°C. Grounding EN sets the LTC4310 in a near-zero current mode.

After the LTC4310 exits POR, STOP bit and bus idle detector circuitry monitors the logic state of its own SDA and SCL bus and of the other  $I^2C$  bus in the system via RXP and RXN. When a STOP bit or bus idle occurs simultaneously on both  $I^2C$  buses, the LTC4310 activates its SDA and SCL drivers, logic detection circuitry and rise time accelerators and drives  $\overline{READY}$  low.

The stuck bus timer and recovery circuitry disable the SDA and SCL driver, logic detection circuitry and rise time accelerators if the bus is low for 37ms. A stuck bus also causes  $\overline{READY}$  to be released high. If the stuck bus releases high, the I<sup>2</sup>C driver and accelerator circuitry are reactivated when a STOP bit or bus idle occurs simultaneously on both I<sup>2</sup>C buses, as previously described.

# **OPERATION**

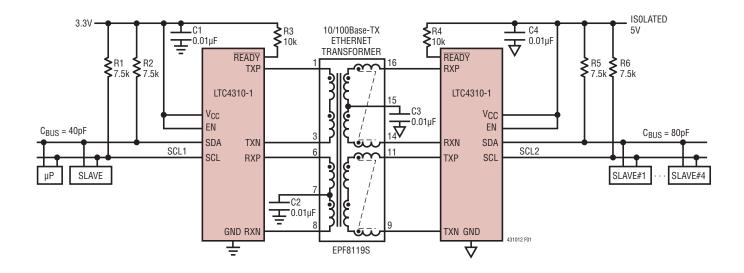

Figure 1. The LTC4310-1 in a Transformer Isolated Application

#### SDA, SCL Bus Pull-Up Resistor Value Selection

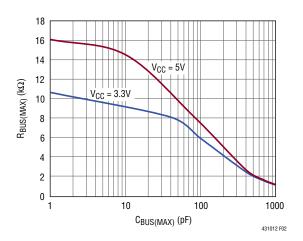

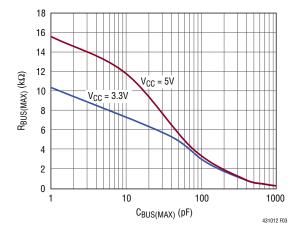

When the SDA (or SCL) bus is rising between 0V and  $0.35 \cdot V_{CC}$ , the LTC4310 controls the bus rise rate to  $(0.35 \cdot V_{CC})/900$ ns for the LTC4310-1 and to  $(0.35 \cdot V_{CC})/300$ ns for the LTC4310-2. Users must quantify their parasitic bus capacitance,  $C_{BUS}$ , and choose a bus pull-up resistor,  $R_{BUS}$ , based on their bus pull-up supply voltage and maximum bus switching frequency to ensure that each bus rises faster than the controlled rise rate. For bus frequencies up to 100kHz, choose the LTC4310-1 and refer to Figure 2 for the maximum pull-up resistance to use. For bus frequencies between 100kHz and 400kHz, choose the LTC4310-2 and refer to Figure 3 for the maximum pull-up resistance to use. Be sure to include worst-case resistor tolerance when selecting resistor value.

#### **Rise Time Accelerators**

The LTC4310's rise time accelerator circuitry on the SDA and SCL lines turns on during rising edges to

Figure 2. Maximum SDA, SCL Bus Pull-Up Resistor Value as a Function of Parasitic Bus Capacitance for the LTC4310-1

reduce the bus rise time. When the bus has risen above 0.45 • V<sub>CC</sub>, the LTC4310 turns on a strong, slew-limited pull-up current, IBOOST, to help even heavily loaded buses meet the rise time specifications. See the Typical Performance Characteristics section for the rise time accelerator pull-up current as a function of temperature and bus capacitance. When either the bus has risen above  $(V_{CC} - 1V)$  or 300ns after the pull-up current has turned on (whichever comes first), the LTC4310 deactivates its pull-up current to deter fighting with the subsequent falling edge. Users must ensure that the bus pull-up supply voltage  $V_{BUS} \ge$ V<sub>CC</sub>, so that the accelerators do not overdrive the SDA, SCL bus and source current into V<sub>BUS</sub>. The rise time accelerators are deactivated during start-up, thermal shutdown. shutdown and after disconnection due to a stuck bus or failure to receive a transmission within 4.6ms.

Figure 3. Maximum SDA,SCL Bus Pull-Up Resistor Value as a Function of Parasitic Bus Capacitance for the LTC4310-2

LINEAR TECHNOLOGY

#### **Bus Rising Edge Waveform**

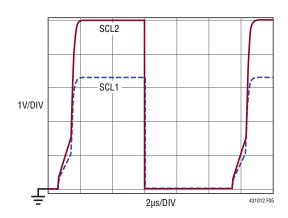

When all external pull-downs on SCL1 (Figure 1) turn off, the SCL1 rising waveform will resemble that shown in Figure 4. The LTC4310-1 senses that SCL1 is rising and transmits a message to the other LTC4310-1 to release SCL2 high. During the transmission, the first LTC4310-1 also drives SCL1 to 0.35V, so that when the transmission is complete, both buses will rise simultaneously from 0.35V at a rate of  $(0.35 \cdot V_{CC})/900$ ns. This functionality minimizes the effective skew between the two buses. When SCL1 reaches 0.35  $\cdot V_{CC}$ , the LTC4310-1 deactivates its rise rate regulation circuitry. The bus then rises with a time constant of (R<sub>BUS</sub>  $\cdot$  C<sub>BUS</sub>) until it reaches 0.45  $\cdot$  V<sub>CC</sub>, at which point the I<sub>BOOST</sub> rise time accelerator pull-up current is activated.

Figure 5 shows SCL1 and SCL2 for an entire 100kHz switching cycle. Because the LTC4310-1 regulates the bus rise rate to  $(0.35 \cdot V_{CC})/900$ ns, the 5V bus signal rises more quickly than the 3.3V bus signal. Both buses reach  $(0.35 \cdot V_{CC})$  in approximately 900ns, so the effective skew between the buses is nearly zero. The LTC4310-2 functions the same as the LTC4310-1, except the controlled rise rate is limited to  $(0.35 \cdot V_{CC})/300$ ns.

# RISE TIME ACCELERATOR ACTIVE BUS RC SCL1 SET TO 0.35V DURING TX dV/dt = 0.35 • V<sub>CC</sub> 900 ns

Figure 4. SCL1 Rising Waveform of SCL1 for Application Circuit Shown in Figure 1

#### Start-Up, Data and Clock Hot Swap Circuitry

The LTC4310 contains power-on reset (POR) circuitry that sets the data and clock pins in a high impedance state and deactivates the transmit circuitry until the EN voltage is high, the device is not in thermal shutdown and the  $V_{CC}$  voltage is above 2.4V. After the LTC4310 exits the POR state, it activates its transmit circuitry and communicates its SDA, SCL logic states across the barrier to the other LTC4310 via its TXP and TXN pins.

The receive circuitry remains deactivated for an additional 900µs after the LTC4310 exits POR. The 900µs filter time is required for the LTC4310 to charge its RXP and RXN pins to their DC bias voltage, assuming a 0.01µF common-mode noise filtering capacitor at the center-tap of the secondary side of the external transformer. When the filter time has elapsed, the LTC4310 activates its receive circuitry and decodes the messages it receives on its RXP and RXN pins, registering the logic state of the remote I<sup>2</sup>C bus.

When both the local and remote two-wire buses are "quiet" (i.e., no data transactions are occurring on either bus), the LTC4310 then drives its  $\overline{READY}$  pin low to indicate that it has linked the logic state of the local I<sup>2</sup>C bus with the logic state of the remote I<sup>2</sup>C bus. This means that the LTC4310 will now drive its SDA and SCL pins to the logic state of the remote I<sup>2</sup>C bus, as specified by the messages it receives on RXP and RXN. The LTC4310 considers a two-wire bus

Figure 5. 100kHz SCL Waveforms for Application Circuit Shown in Figure 1

quiet if it has been idle high for at least 115 $\mu$ s, or if a STOP bit has occurred and both data and clock have remained high since the STOP bit. This functionality makes the LTC4310 ideal for hot-swapping cards into and out of a live l<sup>2</sup>C system. The threshold voltages for the STOP bit and bus idle comparators are 0.5 • V<sub>CC</sub>.

#### **Stuck Bus Disconnect and Recovery**

An internal timer runs whenever SDA, SCL or both are low. The timer is only reset when both SDA and SCL are high. If the timer does not reset within 37ms, the LTC4310 assumes the bus is stuck low. Accordingly, it ceases driving its SDA and SCL pins and transmits a special message across the barrier to inform the other LTC4310. Upon receiving this message, the other LTC4310 also ceases driving its SDA and SCL pins. At least 40µs after determining the bus is stuck low, the LTC4310 generates up to sixteen clock cycles on SCL in an attempt to make the slave release the SDA line. The LTC4310 stops issuing clocks when the SDA line releases high, or after sixteen cycles, whichever comes first. Once the clock pulses have completed, the LTC4310 issues a STOP bit on SDA and SCL to reset all devices on the bus.

The LTC4310 reactivates its amplifiers and rise time accelerators when the bus releases high and a STOP bit or bus idle occurs on both the local and isolated buses, as previously described in the Start-Up, Data and Clock Hot Swap Circuitry section. The stuck bus disconnect and recovery circuitry is disabled when the LTC4310 is in UVLO, thermal shutdown and low current shutdown.

#### **Transmit and Receive Circuitry**

Transmissions occur on the TXP and TXN pins whenever the externally driven SDA or SCL logic state changes – in other words, transmissions are event driven. In addition, if SDA and SCL do not change state for 1.15ms, the LTC4310 retransmits the logic state. The TXP and TXN pins are driven in a pseudo differential fashion. Both pins are driven to ground when inactive and are driven to 1.25V (typical) in matched sets of alternating 35ns pulses to send information across the barrier to the other LTC4310.

The LTC4310 receives and decodes the pulses sent by the other LTC4310 on its RXP and RXN pins. Assuming the start-up sequence previously described has been com-

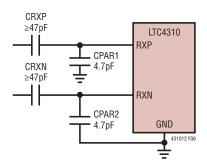

pleted, the LTC4310 drives its SDA and SCL lines to the logic state dictated by the decoded RXP and RXN signals. The LTC4310 rejects RXP and RXN signals having less than 500mV magnitude to provide noise immunity against common-mode transients. The parasitic capacitances of the LTC4310's RXP and RXN pins and their associated board traces form a capacitive divider with the transmit/receive coupling capacitors, as shown in Figure 6. To guarantee robust communications, minimize the parasitic capacitance CPAR by minimizing the trace length from the coupling capacitors to the RXP and RXN pins and choose coupling capacitor values, CRXP and CRXN, that are at least ten times larger than CPAR.

Figure 6. Parasitic Trace and Pin Capacitances Form a Capacitive Divider with  $C_{RXP}$  and  $C_{RXN}$ . Ensure  $C_{RXP}$ ,  $C_{RXN} \ge 10 \bullet C_{PAR}$

If the LTC4310 has not received a message in 4.6ms, it assumes there is a communication problem and ceases driving its SDA and SCL pins. It also transmits a special message to the other LTC4310 to inform it that it is no longer driving its SDA and SCL bus. Upon receiving this message, the other LTC4310 also ceases driving its SDA and SCL pins. Once the communication problem is resolved, both LTC4310's reactivate their amplifiers and rise time accelerators after a STOP bit or bus idle has occurred on both buses, as previously described in the Start-Up, Data and Clock Hot Swap Circuitry section.

#### Thermal Shutdown

If the die temperature of the LTC4310 exceeds 150°C, the LTC4310 enters a thermal shutdown mode. It sets TXP and TXN to a high impedance state, ceases driving SDA and SCL, and ignores the signals on RXP and RXN. When the temperature drops back below 130°C, the LTC4310 goes through the POR sequence previously described.

Once a STOP bit or bus idle occurs on both the local and isolated buses, the LTC4310 reactivates its buffers and rise time accelerators.

#### **READY** Digital Output

The READY pin provides a digital output flag that pulls low to indicate that the LTC4310 is driving its SDA and SCL pins with the logic state information it is receiving on its RXP and RXN pins from the other LTC4310. READY is driven by an N-channel MOSFET open-drain pull-down that is capable of sinking 4mA while holding 0.4V maximum. The pull-down turns off whenever the LTC4310 is not driving its SDA and SCL pins—during start-up, thermal shutdown, low current shutdown and after disconnection due to a stuck bus or failure to receive a transmission within 4.6ms. Connect a resistor to the bus pull-up supply to provide the pull-up.

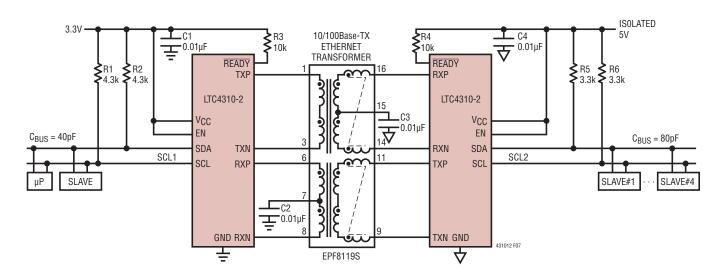

# Design Example: High Voltage Isolation Using an Inexpensive Ethernet Transformer

Figure 1 shows the LTC4310-1 providing I<sup>2</sup>C communications between two buses whose ground voltages can

differ up to 1500V. An EPF8119S Ethernet transformer is used to bridge the isolation barrier. The left  $I^2C$  bus connects to the LTC4310-1 and two other devices, resulting in a bus parasitic capacitance of 40pF in this example set-up. Referring to the  $V_{CC}=3.3V$  curve in Figure 2, 7.5k pull-up resistors are chosen for R1 and R2. The right  $I^2C$  bus connects to another LTC4310-1 and four slave devices, resulting in a bus parasitic capacitance of 80pF. Referring to the  $V_{CC}=5V$  curve in Figure 2, 7.5k pull-up resistors are also chosen for R5 and R6. Standard 5% resistors are used.

Sudden changes in the ground differential across the isolation barrier can be effectively resisted by tying the center tap of the receive side of the transformer to the local ground through a  $0.01\mu F$  capacitor, as shown by capacitors C2 and C3.

Figure 7 shows the same application as Figure 1, but with each LTC4310-1 replaced by an LTC4310-2, so that the bus can switch at frequencies up to 400kHz. To meet the requirements shown in the curves of Figure 3, R1 and R2 are changed from 7.5k to 4.3k, and R5 and R6 are changed from 7.5k to 3.3k.

Figure 7. The LTC4310-2 in a 400kHz Application

#### TYPICAL APPLICATIONS

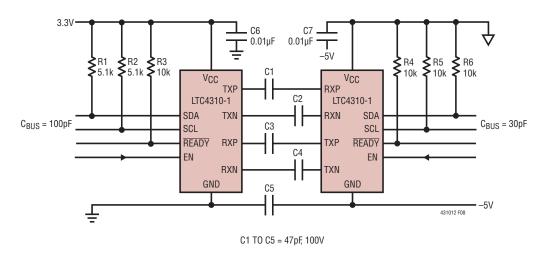

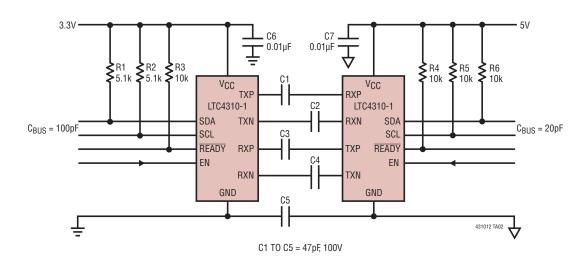

Figure 8 shows the LTC4310-1 providing  $I^2C$  communications between an  $I^2C$  bus referenced to system ground and an  $I^2C$  bus using -5V for its ground reference. Ceramic coupling capacitors, C1-C5, are used to bridge the isolation barrier. This circuit is recommended for ground isolation voltages less than 100V and is limited by the voltage rating of C1-C5. Higher voltage ceramic capacitors may be used to achieve higher isolation voltages. Because the LTC4310 uses a pseudo-differential transmit scheme, capacitor C5 must be connected between ground and -5V to provide a return path for the transmitted current.

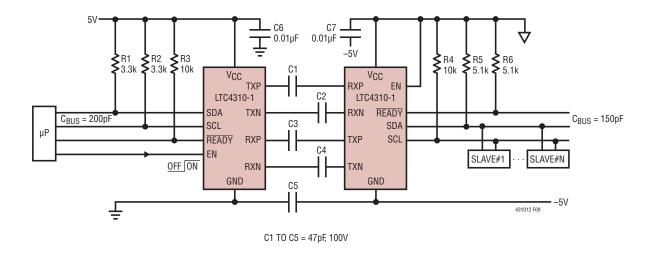

Figure 9 shows the LTC4310-1 in an application circuit using its zero current shutdown mode. A microprocessor only activates the left LTC4310-1 when it needs to com-

municate with the isolated  $I^2C$  bus. Because the LTC4310-1 contains a STOP bit and bus idle detection circuitry, there is no danger of connecting in the middle of a message when the microprocessor asynchronously reenables the LTC4310-1.

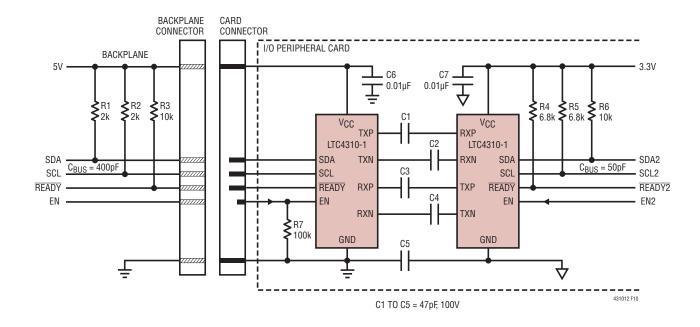

Figure 10 shows the LTC4310-1 in a two-wire bus Hot Swap application. Using a staggered connector, make EN the shortest length pin to ensure that the transients associated with hot swapping have settled before the LTC4310-1 can be enabled. After connection is complete, a master on the backplane may drive EN high to bring the LTC4310-1 out of shutdown mode and into normal operation. Due to its STOP bit and bus idle detection circuitry, the LTC4310-1's driver circuitry is not activated until transactions on both buses are complete.

Figure 8. Low Voltage I<sup>2</sup>C Isolation Between a Ground Referenced Bus and a -5V Referenced Bus

Figure 9. The LTC4310-1 in a Zero Current Shutdown Application

Figure 10. The LTC4310-1 in an I<sup>2</sup>C Hot-Swapping Application

#### LTC4310 Compatibility with Other LTC Bus Buffers

The LTC4310 cannot be used on the same I<sup>2</sup>C bus with the LTC4300A-1, LTC4303 or LTC4307. During rising edges, the rise time accelerators of these buffers turn on before the LTC4310 disables its rise rate regulation circuitry, resulting in nonmonotonic bus edges.

The LTC4310-1 is compatible with the LTC4301 and LTC4301L. It is also compatible with the LTC4302, LTC4304, LTC4305 and LTC4306, provided that the rise time accelerators of these buffers are permanently disabled. All of the previously mentioned buffers are incompatible with the LTC4310-2 because the compensation networks of these buffers cause the bus to rise more slowly than (0.35 •  $V_{CC}$ )/300ns, therefore the LTC4310-2 would not be able to control the bus rise rate.

#### LTC4310-1 Compatibility with LTC4310-2

In a typical application such as shown in Figure 1, an LTC4310-1 can be used on one bus and an LTC4310-2 can be used on the other, provided that the bus pull-up resistors connected to the LTC4310-1 meet the requirements

of Figure 2, and the bus pull-up resistors connected to the LTC4310-2 meet the requirements of Figure 3. However, the bus switching frequency is limited by the rise rate regulation circuitry of the LTC4310-1. In addition, significant skew is introduced on the rising edges due to the large difference in the controlled rise rates of the two buses. For this reason, it is recommended to use two LTC4310-1's in SMBus and standard mode I<sup>2</sup>C applications and to use two LTC4310-2's in fast mode I<sup>2</sup>C applications.

The LTC4310-1 cannot be used on the same physical  $I^2C$  bus with the LTC4310-2, because the LTC4310-1's rise rate regulation circuitry controls the bus rise rate to (0.35 •  $V_{CC}$ )/900ns, therefore the LTC4310-2 would not be able to control the bus rise rate.

#### Using the LTC4310-1 at Frequencies Above 100kHz

Users who implement custom two-wire buses may use the LTC4310-1 at bus frequencies above 100kHz provided that all other devices on the bus can tolerate the approximately 1µs bus rise times resulting from the LTC4310-1's bus rise rate regulation circuitry.

#### TYPICAL APPLICATIONS

#### **Transformer Selection Guide**

As shown in Figure 1, a transformer passes transmit and receive signals between the two LTC4310's. The transmit signals have 1.25V magnitude and 35ns pulse width. The receive circuitry has an equivalent input impedance of 16.5k $\Omega$  and can receive differential signals ranging from 0.875V to 1.55V. To meet these requirements, choose a transformer having a magnetizing inductance ranging from 50 $\mu$ H to 350 $\mu$ H, a 1:1 turns ratio and a maximum insertion loss of –1.5dB. For optimal common mode noise rejection, choose a center-tapped transformer and connect the center tap on the receiving side to local ground using a 0.01 $\mu$ F capacitor. Ringing at the LTC4310's RXP and RXN pins can effectively be damped by inserting 50 $\Omega$  series resistors between each LTC4310's TXP and TXN pins and the corresponding transformer primary windings.

Table 1 shows a recommended list of transformers for use with the LTC4310. 10/100BaseTX Ethernet transformers

are inexpensive and work very well in this application for isolation voltages up to 1500V. For applications requiring 4000V isolation, the Würth Electronics Midcom 749014012 transformer is recommended.

#### **RF Radiated Emissions**

The LTC4310 evaluation board passes CISPR22 Class B requirements for radiated emissions. The results of CISPR22 testing are shown in the evaluation board manual. To reduce radiated emission levels further, enclose the LTC4310 application circuit in a shielded enclosure.

#### **Common Mode Transient Immunity**

The LTC4310 has high immunity to common mode transients. This is tested by applying a square voltage pulse having very fast edges between the isolated grounds. The LTC4310 passes 20kV/us edges without corruption of the  $I^2C$  bus logic states.

Table 1. LTC4310 Recommended Transformers

|                   |                  | ISOLATION            | FORM FACTOR (mm) |       |       | TURNS | CENTER | OPERATING     |  |

|-------------------|------------------|----------------------|------------------|-------|-------|-------|--------|---------------|--|

| MANUFACTURER      | PART NUMBER      | VOLTAGE              | Х                | у     | Z     | RATIO | TAP    | TEMPERATURE   |  |

| PCA Electronics   | EPF8119S         | 1500V <sub>RMS</sub> | 10.41            | 12.45 | 5.84  | 1:1   | Yes    | 0°C TO 70°C   |  |

|                   | EPF8119SE        | 1500V <sub>RMS</sub> | 10.2             | 12.7  | 5.96  | 1:1   | Yes    | -40°C TO 85°C |  |

| Pulse             | E5017            | 1500V <sub>RMS</sub> | 9.4              | 12.7  | 5.08  | 1:1   | Yes    | 0°C TO 70°C   |  |

| Würth Electronics | 000-7090-37R-LF1 | 1500V <sub>RMS</sub> | 9.4              | 12.95 | 5.33  | 1:1   | Yes    | -40°C TO 85°C |  |

| Midcom            | 749014012        | 4000V <sub>RMS</sub> | 17               | 24.55 | 10.85 | 1:1   | Yes    | 0°C TO 70°C   |  |

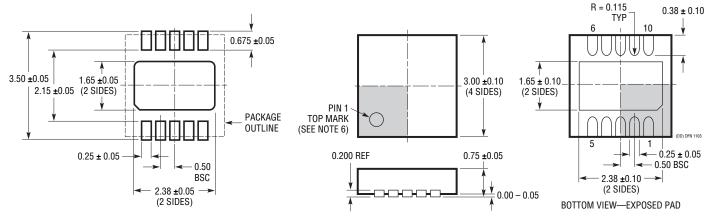

## PACKAGE DESCRIPTION

# $\begin{array}{c} \textbf{DD Package} \\ \textbf{10-Lead Plastic DFN (3mm} \times \textbf{3mm)} \end{array}$

(Reference LTC DWG # 05-08-1699)

#### **RECOMMENDED** SOLDER PAD PITCH AND DIMENSIONS

#### NOTE

- 1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE MO-229 VARIATION OF (WEED-2). CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

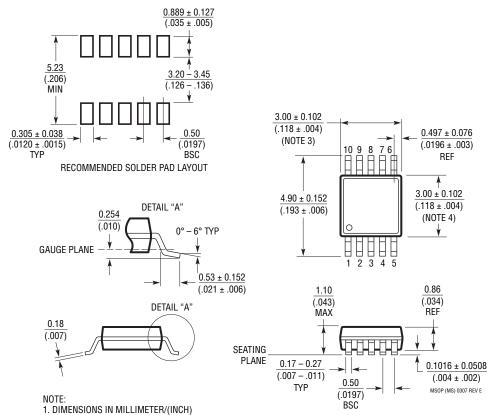

## PACKAGE DESCRIPTION

#### MS Package 10-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1661 Rev E)

- 2. DRAWING NOT TO SCALE

- DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

# TYPICAL APPLICATION

#### **Breaking Ground Loops Using Capacitors**

# **RELATED PARTS**

| PART NUMBER                          | DESCRIPTION                                                                           | COMMENTS                                                                                                                                                                                  |

|--------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC4300A-1/LTC4300A-2/<br>LTC4300A-3 | Hot-Swappable 2-Wire Bus Buffers                                                      | LTC4300A-1: Bus Buffer with READY and ENABLE,<br>LTC4300A-2: Dual Supply Bus Buffer with V <sub>CC2</sub> and ACC,<br>LTC4300A-3: Dual Supply Bus Buffer with V <sub>CC2</sub> and ENABLE |

| LTC4301                              | Supply Independent Hot-Swappable 2-Wire<br>Bus Buffer                                 | Supply Independent                                                                                                                                                                        |

| LTC4302-1/LTC4302-2                  | Addressable 2-Wire Bus Buffer                                                         | Address Expansion, GPIO, Software Controlled                                                                                                                                              |

| LTC4303/LTC4304                      | Hot-Swappable 2-Wire Bus Buffer with Stuck<br>Bus Recovery                            | Provides Automatic Clocking to Free Stuck I <sup>2</sup> C Busses                                                                                                                         |

| LTC4305/LTC4306                      | 2- or 4-Channel, 2-Wire Bus Multiplexers with Capacitance Buffering                   | Two or Four Selectable Downstream Busses, Stuck Bus Disconnect, Rise Time Accelerators, Fault Reporting, ±10kV HBM ESD Tolerance                                                          |

| LTC4307                              | Low Offset Hot-Swappable 2-Wire Bus Buffer with Stuck Bus Recovery                    | 60mV Buffer Offset, 30ms Stuck Bus Disconnect and Recovery, Rise Time Accelerators, ±5kV HBM ESD Tolerance                                                                                |

| LTC4307-1                            | High Definition Multimedia Interface (HDMI)<br>Level Shifting                         | 2-Wire Bus Buffer, 60mV Buffer Offset, 3.3V to 5V Level Shifting, ±5kV HBM ESD Tolerance                                                                                                  |

| LTC4308                              | Low Voltage Level Shifting Hot-Swappable<br>2-Wire Bus Buffer with Stuck Bus Recovery | -200mV Offset In-Out/+300mV Offset Out-In, 0.9V to 5.5V Level Shifting, 30ms Stuck Bus Disconnect and Recovery, Output Side Rise Time Accelerators, ±6kV HBM ESD Tolerance                |

| LTC4309                              | Level Shifting Low Offset Hot-Swappable<br>2-Wire Bus Buffer with Stuck Bus Recovery  | 60mV Buffer Offset, 30ms Stuck Bus Disconnect and Recovery, Rise Time Accelerators, 1.8V to 5V Level Shifting, ±5kV HBM ESD Tolerance                                                     |

| LTC4311                              | I <sup>2</sup> C/SMBus Rise Time Accelerator                                          | Strong Slew Limited Current Source, Wide 1.6V to 5.5V Supply Range, Auto Detect Low Power Standby, Low <5µA Supply Shutdown Current, ±8kV HBM ESD Tolerance                               |