# Active Energy Metering IC with di/dt Sensor Interface

ADE7759\*

#### **FEATURES**

High Accuracy, Supports IEC 687/1036

On-Chip Digital Integrator Allows Direct Interface with Current Sensors with di/dt Output Such as Rogowski Coil Less Than 0.1% Error over a Dynamic Range of 1000 to 1 On-Chip User-Programmable Threshold for Line Voltage SAG Detection and PSU Supervisory

The ADE7759 Supplies Sampled Waveform Data and Active Energy (40 Bits)

Digital Power, Phase and Input DC Offset Calibration On-Chip Temperature Sensor (Typical 1 LSB/°C Resolution) SPI-Compatible Serial Interface

Pulse Output with Programmable Frequency Interrupt Request Pin (IRQ) and IRQ Status Register Proprietary ADCs and DSP provide High Accuracy over Large Variations in Environmental Conditions and Time Reference 2.4 V ± 8% (20 ppm/°C Typical) with External Overdrive Capability

Single 5 V Supply, Low Power Consumption (25 mW Typical)

#### **GENERAL DESCRIPTION**

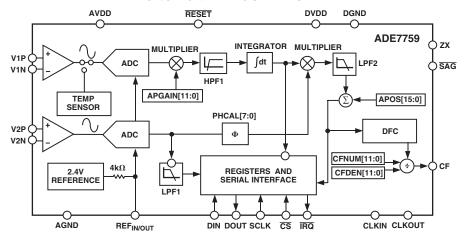

The ADE7759 is an accurate active power and energy measurement IC with a serial interface and a pulse output. The ADE7759 incorporates two second order  $\Sigma$ - $\Delta$  ADCs, a digital integrator (on CH1), reference circuitry, temperature sensor, and all the signal processing required to perform active power and energy measurement.

An on-chip digital integrator allows direct interface to di/dt current sensors such as a Rogowski coil. The digital integrator eliminates the need for an external analog integrator and provides excellent long-term stability and precise phase matching

between the current and the voltage channels. The integrator can be switched off if the ADE7759 is used with conventional current sensors.

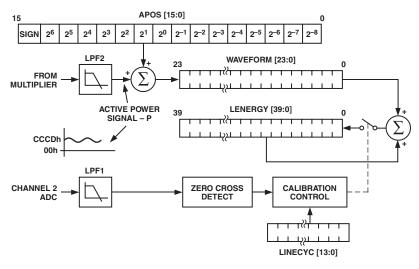

The ADE7759 contains a sampled Waveform register and an Active Energy register capable of holding at least 11.53 seconds of accumulated power at full ac load. Data is read from the ADE7759 via the serial interface. The ADE7759 also provides a pulse output (CF) with frequency that is proportional to the active power.

In addition to active power information, the ADE7759 also provides various system calibration features, i.e., channel offset correction, phase calibration, and power offset correction. The part also incorporates a detection circuit for short duration voltage drop (SAG). The voltage threshold and the duration (in number of half-line cycles) of the drop are user programmable. An open drain logic output  $(\overline{SAG})$  goes active low when a sag event occurs.

A zero crossing output (ZX) produces an output that is synchronized to the zero crossing point of the line voltage. This output can be used to extract timing or frequency information from the line. The signal is also used internally to the chip in the line cycle energy accumulation mode; i.e., the number of half-line cycles in which the energy accumulation occurs can be controlled. Line cycle energy accumulation enables a faster and more precise energy accumulation and is especially useful during calibration. This signal is also useful for synchronization of relay switching with a voltage zero crossing.

The interrupt request output is an open drain, active low logic output. The Interrupt Status Register indicates the nature of the interrupt, and the Interrupt Enable Register controls which event produces an output on the  $\overline{IRQ}$  pin. The ADE7759 is available in a 20-lead SSOP package.

#### FUNCTIONAL BLOCK DIAGRAM

\*U.S. Patents 5,745,323; 5,760,617; 5,862,069; 5,872,469; others pending. REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

### TABLE OF CONTENTS

| FEATURES 1                                  | CHANNEL 1 ADC                         | 17 |

|---------------------------------------------|---------------------------------------|----|

| GENERAL DESCRIPTION 1                       | Channel 1 ADC Gain Adjust             | 18 |

| FUNCTIONAL BLOCK DIAGRAM 1                  | Channel 1 Sampling                    | 18 |

| SPECIFICATIONS 3                            | CHANNEL 1 AND CHANNEL 2 WAVEFORM      |    |

| TIMING CHARACTERISTICS 5                    | SAMPLING MODE                         |    |

| ABSOLUTE MAXIMUM RATINGS 6                  | CHANNEL 2 ADC                         |    |

| ORDERING GUIDE 6                            | Channel 2 Sampling                    |    |

| PIN CONFIGURATION 7                         | PHASE COMPENSATION                    |    |

| PIN FUNCTION DESCRIPTIONS 7                 | ACTIVE POWER CALCULATION              |    |

| TERMINOLOGY 8                               | ENERGY CALCULATION                    |    |

| MEASUREMENT ERROR 8                         | Integration Time under Steady Load    | 22 |

| PHASE ERROR BETWEEN CHANNELS 8              | POWER OFFSET CALIBRATION              |    |

| POWER SUPPLY REJECTION 8                    | ENERGY-TO-FREQUENCY CONVERSION        | 22 |

| ADC OFFSET ERROR 8                          | LINE CYCLE ENERGY ACCUMULATION MODE   | 24 |

| GAIN ERROR 8                                | CALIBRATING THE ENERGY METER          | 24 |

| GAIN ERROR MATCH 8                          | Calculating the Average Active Power  |    |

| TYPICAL PERFORMANCE CHARACTERISTICS (TPC) 9 | Calibrating the Frequency at CF       | 25 |

| TEST CIRCUITS 11                            | Energy Meter Display                  |    |

| ANALOG INPUTS11                             | CLKIN FREQUENCY                       |    |

| di/dt CURRENT SENSOR AND DIGITAL            | SUSPENDING THE ADE7759 FUNCTIONALITY  |    |

| INTEGRATOR 12                               | APPLICATION INFORMATION               |    |

| ZERO CROSSING DETECTION                     | SERIAL INTERFACE                      | 26 |

| LINE VOLTAGE SAG DETECTION 14               | Serial Write Operation                | 26 |

| Sag Level Set                               | Serial Read Operation                 | 27 |

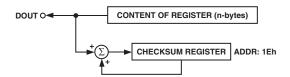

| POWER SUPPLY MONITOR 14                     | CHECKSUM REGISTER                     | 28 |

| INTERRUPTS 15                               | REGISTER DESCRIPTIONS                 | 29 |

| Using the ADE7759 Interrupts with an MCU 15 | Communications Register               | 29 |

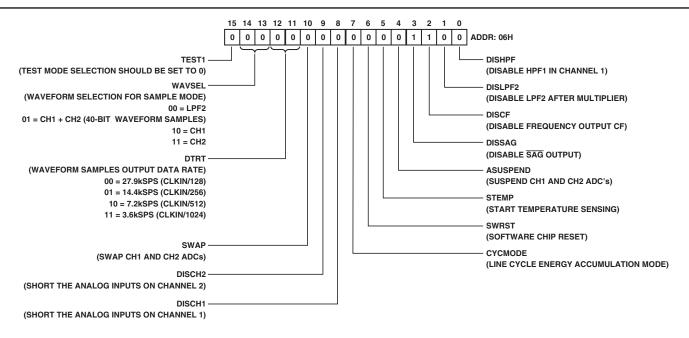

| Interrupt Timing                            | Mode Register (06H)                   | 30 |

| TEMPERATURE MEASUREMENT                     | Interrupt Status Register (04H)       | 31 |

| ANALOG-TO-DIGITAL CONVERSION 16             | Reset Interrupt Status Register (05H) | 31 |

| Antialias Filter                            | CH1OS Register (08H)                  | 32 |

| ADC Transfer Function                       | OUTLINE DIMENSIONS                    | 32 |

| Poforonco Circuit                           |                                       |    |

-2- REV. 0

$\begin{array}{l} \textbf{SPECIFICATIONS}^{1} & \text{(AV}_{DD} = DV_{DD} = 5 \text{ V} \pm 5\%, \text{ AGND} = D\text{GND} = 0 \text{ V}, \text{ On-Chip Reference, CLKIN} = 3.579545 \text{ MHz XTAL,} \\ & T_{\text{MIN}} \text{ to } T_{\text{MAX}} = -40^{\circ}\text{C to } +85^{\circ}\text{C unless otherwise noted.)} \end{array}$

| Parameter                                   |       | Unit   | Test Conditions/Comments                                      |

|---------------------------------------------|-------|--------|---------------------------------------------------------------|

| ENERGY MEASUREMENT ACCURACY                 |       |        |                                                               |

| Measurement Bandwidth                       | 14    | kHz    | CLKIN = 3.579545 MHz                                          |

| Measurement Error <sup>1</sup> on Channel 1 |       |        | Channel $2 = 300 \text{ mV rms/}60 \text{ Hz}$ , Gain = 1     |

| Channel 1 Range = 0.5 V Full-Scale          |       |        |                                                               |

| Gain = 1                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 2                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 4                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 8                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 16                                   | 0.2   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Channel 1 Range = 0.25 V Full-Scale         |       |        |                                                               |

| Gain = 1                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 2                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 4                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 8                                    | 0.2   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 16                                   | 0.2   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Channel 1 Range = 0.125 V Full-Scale        |       |        |                                                               |

| Gain = 1                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 2                                    | 0.1   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 4                                    | 0.2   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 8                                    | 0.2   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Gain = 16                                   | 0.4   | % typ  | Over a Dynamic Range 1000 to 1                                |

| Phase Error <sup>1</sup> between Channels   | ±0.05 | ° max  | Line Frequency = 45 Hz to 65 Hz, HPF on                       |

| AC Power Supply Rejection <sup>1</sup>      |       | 0.4    | $AV_{DD} = DV_{DD} = 5 V + 175 \text{ mV rms}/120 \text{ Hz}$ |

| Output Frequency Variation (CF)             | 0.2   | % typ  | Channel 1 = 20 mV rms/60 Hz, Gain = 16, Range = 0.5 V         |

|                                             |       |        | Channel 2 = 300 mV rms/60 Hz, Gain = 1                        |

| DC Power Supply Rejection <sup>1</sup>      |       | 0/     | $AV_{DD} = DV_{DD} = 5 \text{ V} \pm 250 \text{ mV dc}$       |

| Output Frequency Variation (CF)             | ±0.3  | % typ  | Channel 1 = 20 mV rms/60 Hz, Gain = 16, Range = 0.5 V         |

|                                             |       |        | Channel 2 = 300 mV rms/60 Hz, Gain = 1                        |

| ANALOG INPUTS                               |       |        | See Analog Inputs Section                                     |

| Maximum Signal Levels                       | ±0.5  | V max  | V1P, V1N, V2N, and V2P to AGND                                |

| Input Impedance (DC)                        | 390   | kΩ min |                                                               |

| Bandwidth                                   | 14    | kHz    | CLKIN/256, $CLKIN = 3.579545 MHz$                             |

| Gain Error <sup>1, 3</sup>                  |       |        | External 2.5 V Reference, Gain = 1 on Channel 1 and 2         |

| Channel 1                                   |       |        |                                                               |

| Range = 0.5 V Full-Scale                    | ±4    | % typ  | V1 = 0.5 V dc                                                 |

| Range = 0.25 V Full-Scale                   | ±4    | % typ  | V1 = 0.25  V dc                                               |

| Range = 0.125 V Full-Scale                  | ±4    | % typ  | V1 = 0.125  V dc                                              |

| Channel 2                                   | ±4    | % typ  | V2 = 0.5 V dc                                                 |

| Gain Error Match                            |       |        | External 2.5 V Reference                                      |

| Channel 1                                   |       |        |                                                               |

| Range = 0.5 V Full-Scale                    | ±0.3  | % typ  | Gain = 1, 2, 4, 8, 16                                         |

| Range = 0.25 V Full-Scale                   | ±0.3  | % typ  | Gain = 1, 2, 4, 8, 16                                         |

| Range = 0.125 V Full-Scale                  | ±0.3  | % typ  | Gain = 1, 2, 4, 8, 16                                         |

| Channel 2                                   | ±0.3  | % typ  | Gain = 1, 2, 4, 8, 16                                         |

| Offset Error <sup>1</sup>                   |       |        |                                                               |

| Channel 1                                   | ±10   | mV max | Gain = 1                                                      |

| Channel 2                                   | ±10   | mV max | Gain = 1                                                      |

| WAVEFORM SAMPLING                           |       |        | Sampling CLKIN/128, 3.579545 MHz/128 = 27.9 kSPS              |

| Channel 1                                   |       |        | See Channel 1 Sampling                                        |

| Signal-to-Noise plus Distortion             | 62    | dB typ | 150 mV rms/60 Hz, Range = 0.5 V, Gain = 2                     |

| Bandwidth (-3 dB)                           | 14    | kHz    | CLKIN = 3.579545 MHz                                          |

| Channel 2                                   |       |        | See Channel 2 Sampling                                        |

| Signal-to-Noise plus Distortion             | 52    | dB typ | 150 mV rms/60 Hz, Gain = 2                                    |

| Bandwidth (-3 dB)                           | 156   | Hz     | CLKIN = 3.579545 MHz                                          |

|                                             | 150   | 112    | CALCITY J.J. 1.J. 1.J. 1.J. 1.J. 1.J. 1.J. 1.J                |

REV. 0 -3-

## ADE7759—SPECIFICATIONS (continued)

| Parameter                                                                                                                                                                                                                                          | Spec                   | Unit                                                                                                                        | Test Conditions/Comments                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE INPUT REF <sub>IN/OUT</sub> Input Voltage Range Input Capacitance                                                                                                                                                                        | 2.6<br>2.2<br>10       | V max<br>V min<br>pF max                                                                                                    | 2.4 V + 8%<br>2.4 V - 8%                                                                                                                                                                                          |

| ON-CHIP REFERENCE                                                                                                                                                                                                                                  |                        |                                                                                                                             | Nominal 2.4 V at REF <sub>IN/OUT</sub> Pin                                                                                                                                                                        |

| Reference Error Current Source Output Impedance Temperature Coefficient                                                                                                                                                                            | ±200<br>10<br>4<br>20  | $\begin{array}{l} \text{mV max} \\ \mu \text{A max} \\ k\Omega \text{ min} \\ \text{ppm/}^{\circ} \text{C typ} \end{array}$ |                                                                                                                                                                                                                   |

| CLKIN Input Clock Frequency                                                                                                                                                                                                                        | 4 1                    | MHz max<br>MHz min                                                                                                          | Note All Specifications CLKIN of 3.579545 MHz                                                                                                                                                                     |

| $\overline{RESET},  DIN,  SCLK,  CLKIN,  and  \overline{CS}$ $\overline{RESET},  DIN,  SCLK,  CLKIN,  and  \overline{CS}$ $Input  High  Voltage,  V_{INH}$ $Input  Low  Voltage,  V_{INL}$ $Input  Current,  I_{IN}$ $Input  Capacitance,  C_{IN}$ | 2.4<br>0.8<br>±3<br>10 | V min<br>V max<br>µA max<br>pF max                                                                                          | $DV_{DD}$ = 5 V ± 5%<br>$DV_{DD}$ = 5 V ± 5%<br>Typically 10 nA, $V_{IN}$ = 0 V to $DV_{DD}$                                                                                                                      |

| LOGIC OUTPUTS  SAG and IRQ  Output High Voltage, V <sub>OH</sub> Output Low Voltage, V <sub>OL</sub> ZX and DOUT  Output High Voltage, V <sub>OH</sub> Output Low Voltage, V <sub>OH</sub>                                                         | 4<br>0.4<br>4<br>0.4   | V min<br>V max<br>V min<br>V max                                                                                            | Open Drain Outputs, $10 \text{ k}\Omega$ pull-up resistor<br>$I_{\text{SOURCE}} = 5 \text{ mA}$<br>$I_{\text{SINK}} = 0.8 \text{ mA}$<br>$I_{\text{SOURCE}} = 5 \text{ mA}$<br>$I_{\text{SINK}} = 0.8 \text{ mA}$ |

| CF Output High Voltage, $V_{OH}$ Output Low Voltage, $V_{OL}$                                                                                                                                                                                      | 4                      | V min<br>V max                                                                                                              | I <sub>SOURCE</sub> = 5 mA<br>I <sub>SINK</sub> = 7 mA                                                                                                                                                            |

| POWER SUPPLY $AV_{DD}$                                                                                                                                                                                                                             | 4.75<br>5.25           | V min<br>V max                                                                                                              | For Specified Performance 5 V - 5% 5 V + 5%                                                                                                                                                                       |

| $\mathrm{DV}_{\mathrm{DD}}$                                                                                                                                                                                                                        | 4.75<br>5.25           | V min<br>V max                                                                                                              | 5 V - 5%<br>5 V + 5%                                                                                                                                                                                              |

| AI <sub>DD</sub> DI <sub>DD</sub>                                                                                                                                                                                                                  | 3 4                    | mA max<br>mA max                                                                                                            | Typically 2.0 mA<br>Typically 3.0 mA                                                                                                                                                                              |

Specifications subject to change without notice.

NOTES

<sup>1</sup>See Terminology section for explanation of specifications.

<sup>2</sup>See plots in Typical Performance Characteristics.

<sup>3</sup>See Analog Inputs section.

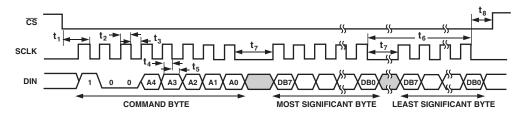

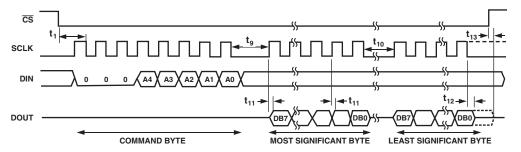

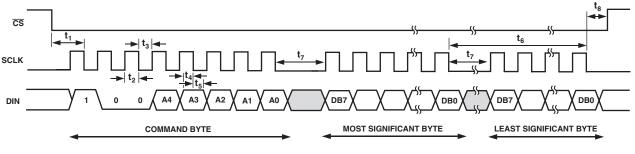

## TIMING CHARACTERISTICS 1, 2 (AV<sub>DD</sub> = DV<sub>DD</sub> = 5 V $\pm$ 5%, AGND = DGND = 0 V, On-Chip Reference, CLKIN = 3.579545 MHz XTAL, $T_{MIN}$ to $T_{MAX} = -40^{\circ}$ C to $+85^{\circ}$ C unless otherwise noted.)

| Parameter         | A, B Versions | Unit                 | Test Conditions/Comments                                                                    |

|-------------------|---------------|----------------------|---------------------------------------------------------------------------------------------|

| Write Timing      |               |                      |                                                                                             |

| $t_1$             | 20            | ns (min)             | CS Falling Edge to First SCLK Falling Edge                                                  |

| $t_2$             | 150           | ns (min)             | SCLK Logic High Pulsewidth                                                                  |

| $t_3$             | 150           | ns (min)             | SCLK Logic Low Pulsewidth                                                                   |

| $t_4$             | 10            | ns (min)             | Valid Data Setup Time Before Falling Edge of SCLK                                           |

| t <sub>5</sub>    | 5             | ns (min)             | Data Hold Time After SCLK Falling Edge                                                      |

| $t_6$             | 6.4           | μs (min)             | Minimum Time between the End of Data Byte Transfers                                         |

| $t_7$             | 4             | μs (min)             | Minimum Time between Byte Transfers During a Serial Write                                   |

| $t_8$             | 100           | ns (min)             | CS Hold Time After SCLK Falling Edge                                                        |

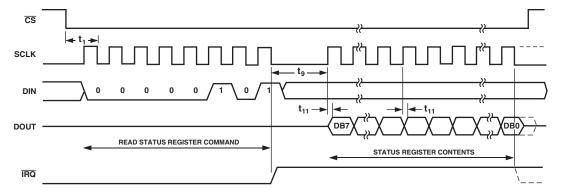

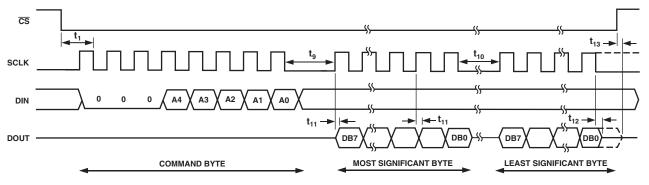

| Read Timing       |               |                      |                                                                                             |

| t <sub>9</sub>    | 4             | μs (min)             | Minimum Time between Read Command (i.e., a Write to Communications                          |

|                   | 4             | us (mains)           | Register) and Data Read  Minimum Time horseen Data Parts Transfers Duning a Multilaste Book |

| $t_{10}$          | 4             | μs (min)             | Minimum Time between Data Byte Transfers During a Multibyte Read                            |

| t <sub>11</sub> 3 | 30            | ns (min)             | Data Access Time After SCLK Rising Edge following a Write to the Communications Register    |

| $t_{12}^{\ \ 4}$  | 100           | ns (max)             | Bus Relinquish Time After Falling Edge of SCLK                                              |

|                   | 10            | ns (min)             |                                                                                             |

| $t_{13}^{\ 4}$    | 100           | ns (max)<br>ns (min) | Bus Relinquish Time After Rising Edge of CS                                                 |

#### NOTES

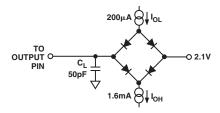

<sup>&</sup>lt;sup>4</sup>Derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit in Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the time quoted in the timing characteristics is the true bus relinquish time of the part and is independent of the bus loading.

Figure 1. Load Circuit for Timing Specifications

Figure 2. Serial Write Timing

Figure 3. Serial Read Timing

$<sup>^{1}</sup>$ Sample tested during initial release and after any redesign or process change that may affect this parameter. All input signals are specified with tr = tf = 5 ns (10% to 90%) and timed from a voltage level of 1.6 V.

<sup>&</sup>lt;sup>2</sup>See Figures 2 and 3 and Serial Interface section of this data sheet.

<sup>&</sup>lt;sup>3</sup>Measured with the load circuit in Figure 1 and defined as the time required for the output to cross 0.8 V or 2.4 V.

#### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_A = 25^{\circ}C \text{ unless otherwise noted})$                                           |

|------------------------------------------------------------------------------------------------|

| $AV_{DD}$ to $AGND$ 0.3 V to +7 V                                                              |

| $DV_{DD}$ to $DGND$                                                                            |

| $DV_{DD}$ to $AV_{DD}$                                                                         |

| Analog Input Voltage to AGND                                                                   |

| $V_{1P}$ , $V_{1N}$ , $V_{2P}$ , and $V_{2N}$                                                  |

| Reference Input Voltage to AGND $\cdot \cdot \cdot -0.3 \text{ V}$ to AV <sub>DD</sub> + 0.3 V |

| Digital Input Voltage to DGND $\dots$ -0.3 V to DV <sub>DD</sub> + 0.3 V                       |

| Digital Output Voltage to DGND $-0.3 \text{ V}$ to DV <sub>DD</sub> + 0.3 V                    |

| Operating Temperature Range                                                                    |

| Industrial (A, B Versions)40°C to +85°C                                                        |

| Storage Temperature Range65°C to +150°C                                                        |

| Junction Temperature                                                                           |

| 20-Lead SSOP, Power Dissipation                                                                |

| $\theta_{JA}$ Thermal Impedance                                                                |

| Lead Temperature, Soldering                                                                    |

| Vapor Phase (60 sec)                                                                           |

| Infrared (15 sec)                                                                              |

|                                                                                                |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ORDERING GUIDE**

| Model         | Package Option*          |

|---------------|--------------------------|

| ADE7759ARS    | RS-20                    |

| ADE7759ARSRL  | RS-20                    |

| EVAL-ADE7759E | ADE7759 Evaluation Board |

<sup>\*</sup>RS = Shrink Small Outline Package in tubes; RSRL = Shrink Small Outline Package in reel.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADE7759 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

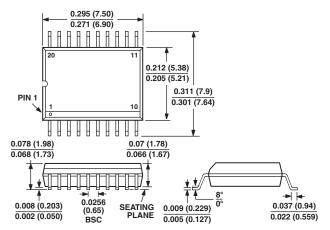

#### PIN CONFIGURATION

### PIN FUNCTION DESCRIPTIONS

| Pin No. | Mnemonic                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | RESET                       | Reset Pin for the ADE7759. A logic low on this pin will hold the ADCs and digital circuitry (including the serial interface) in a reset condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 2       | $\mathrm{DV}_{\mathrm{DD}}$ | Digital Power Supply. This pin provides the supply voltage for the digital circuitry in the ADE7759. The supply voltage should be maintained at $5 \text{ V} \pm 5\%$ for specified operation. This pin should be decoupled to DGND with a $10  \mu\text{F}$ capacitor in parallel with a ceramic $100  \text{nF}$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 3       | AV <sub>DD</sub>            | Analog Power Supply. This pin provides the supply voltage for the analog circuitry in the ADE7759. The supply should be maintained at 5 V $\pm$ 5% for specified operation. Every effort should be made to minimize power supply ripple and noise at this pin by the use of proper decoupling method. This pin should be decoupled to AGND with a 10 $\mu$ F capacitor in parallel with a ceramic 100 nF capacitor.                                                                                                                                                                                                                                                                                                           |  |  |  |

| 4, 5    | V1P, V1N                    | Analog Inputs for Channel 1. This channel is intended for use with the di/dt current transducers such as Rogowski coil, or other current sensors such as shunt or current transformer (CT). These inputs are fully differential voltage inputs with maximum differential input signal levels of $\pm 0.5$ V, $\pm 0.25$ V and $\pm 0.125$ V, depending on the full scale selection—See Analog Inputs section. Channel 1 also has a PGA with gain selections of 1, 2, 4, 8, or 16. The maximum signal level at these pins with respect to AGND is $\pm 0.5$ V. Both inputs have internal ESD protection circuitry. In addition, an overvoltage of $\pm 6$ V can be sustained on these inputs without risk of permanent damage. |  |  |  |

| 6, 7    | V2N, V2P                    | Analog Inputs for Channel 2. This channel is intended for use with the voltage transducer. These inputs are fully differential voltage inputs with a maximum differential signal level of $\pm 0.5$ V. Channel 2 also has a PGA with gain selections of 1, 2, 4, 8, or 16. The maximum signal level at these pins with respect to AGND is $\pm 0.5$ V. Both inputs have internal ESD protection circuitry, and an overvoltage of $\pm 6$ V can be sustained on these inputs without risk of permanent damage.                                                                                                                                                                                                                 |  |  |  |

| 8       | AGND                        | This pin provides the ground reference for the analog circuitry in the ADE7759, i.e., ADCs and reference. This pin should be tied to the analog ground plane or the quietest ground reference in the system. This quiet ground reference should be used for all analog circuitry, e.g., antialiasing filters, current and voltage transducers, etc. In order to keep ground noise around the ADE7759 to a minimum, the quiet ground plane should be connected to the digital ground plane at only one point. It is acceptable to place the entire device on the analog ground plane—see Application Information section.                                                                                                      |  |  |  |

| 9       | REF <sub>IN/OUT</sub>       | This pin provides access to the on-chip voltage reference. The on-chip reference has a nominal value of $2.4~V\pm8\%$ and a typical temperature coefficient of $20~ppm/^{\circ}C$ . An external reference source may be connected at this pin. In either case this pin should be decoupled to AGND with a $1~\mu F$ capacitor in parallel with a $100~nF$ capacitor.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 10      | DGND                        | This provides the ground reference for the digital circuitry in the ADE7759, i.e., multiplier, filters, and frequency output (CF). Because the digital return currents in the ADE7759 are small, it is acceptable to connect this pin to the analog ground plane of the system—see Application Information section. However, high bus capacitance on the DOUT pin may result in noisy digital current that affects performance.                                                                                                                                                                                                                                                                                               |  |  |  |

| 11      | CF                          | Calibration Frequency Logic Output. The CF logic output gives Active Power information. This output is intended to be used for operational and calibration purposes. The full-scale output frequency can be adjusted by writing to the APGAIN, CFNUM and CFDEN Registers—see Energy to Frequency Conversion section.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

REV. 0 -7-

#### PIN FUNCTION DESCRIPTIONS (continued)

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 12      | ZX       | Voltage Waveform (Channel 2) Zero Crossing Output. This output toggles logic high and low at the zero crossing of the differential signal on Channel 2—see Zero Crossing Detection section.                                                                                                                                                                                                                                                                                                |  |

| 13      | SAG      | This open drain logic output goes active low when either no zero crossings are detected or a low voltage threshold (Channel 2) is crossed for a specified duration. See Line Voltage Sag Detection section.                                                                                                                                                                                                                                                                                |  |

| 14      | ĪRQ      | Interrupt Request Output. This is an active low open drain logic output. Maskable interrupts include Active Energy register rollover, Active Energy register at half-full, zero crossing, SAG, and arrivals of new waveform samples—See Interrupts section.                                                                                                                                                                                                                                |  |

| 15      | CLKIN    | Master Clock for ADCs and Digital Signal Processing. An external clock can be provided at this logic input. Alternatively, a parallel resonant AT crystal can be connected across CLKIN and CLKOUT to provide a clock source for the ADE7759. The clock frequency for specified operation is 3.579545 MHz. Ceramic load capacitors of between 10 pF to 30 pF should be used with the gate oscillator circuit. Refer to crystal manufacturers data sheet for load capacitance requirements. |  |

| 16      | CLKOUT   | A crystal can be connected across this pin and CLKIN as described above to provide a clock source for the ADE7759. The CLKOUT pin can drive one CMOS load when either an external clock is supplied at CLKIN or a crystal is being used.                                                                                                                                                                                                                                                   |  |

| 17      | CS       | Chip Select. Part of the 4-wire SPI Serial Interface. This active low logic input allows the ADE7759 to share the serial bus with several other devices. See Serial Interface section.                                                                                                                                                                                                                                                                                                     |  |

| 18      | SCLK     | Serial Clock Input for the Synchronous serial interface. All serial data transfers are synchronized to this clock—see Serial Interface section. The SCLK has a Schmitt-trigger input for use with a clock source that has a slow edge transition time, e.g., opto-isolator outputs.                                                                                                                                                                                                        |  |

| 19      | DOUT     | Data Output for the Serial Interface. Data is shifted out at this pin on the rising edge of SCLK. This logic output is normally in a high impedance state unless it is driving data onto the serial data bus—see Serial Interface section.                                                                                                                                                                                                                                                 |  |

| 20      | DIN      | Data Input for the Serial Interface. Data is shifted in at this pin on the falling edge of SCLK—see Serial Interface section.                                                                                                                                                                                                                                                                                                                                                              |  |

#### TERMINOLOGY MEASUREMENT ERROR

The error associated with the energy measurement made by the ADE7759 is defined by the following formula:

$Percentage\ Error =$

Energy registered by the ADE7759 – True Energy

True Energy

#### PHASE ERROR BETWEEN CHANNELS

The digital integrator and the HPF1 (High-Pass Filter) in Channel 1 have nonideal phase response. To offset this phase response and equalize the phase response between channels, two phase correction networks are placed in Channel 1: one for the digital integrator and the other for the HPF1. Each phase correction network corrects the phase response of the corresponding component and ensures a phase match between Channel 1 (current) and Channel 2 (voltage) to within  $\pm 0.1^{\circ}$  over a range of 45 Hz to 65 Hz and  $\pm 0.2^{\circ}$  over a range 40 Hz to 1 kHz.

#### POWER SUPPLY REJECTION

This quantifies the ADE7759 measurement error as a percentage of reading when the power supplies are varied.

For the ac PSR measurement a reading at nominal supplies (5 V) is taken. A second reading is obtained with the same input signal levels when an ac (175 mV rms/120 Hz) signal is introduced onto the supplies. Any error introduced by this ac signal is expressed as a percentage of reading—see Measurement Error definition above. For the dc PSR measurement a reading at

nominal supplies (5 V) is taken. A second reading is obtained with the same input signal levels when the supplies are varied  $\pm 5\%$ . Any error introduced is again expressed as a percentage of reading.

#### ADC OFFSET ERROR

This refers to the dc offset associated with the analog inputs to the ADCs. It means that with the analog inputs connected to AGND the ADCs still see a dc analog input signal. The magnitude of the offset depends on the gain and input range selection—see characteristic curves. However, when HPF1 is switched on, the offset is removed from Channel 1 (current) and the power calculation is not affected by this offset. The offsets may be removed by performing an offset calibration—see Analog Inputs section.

#### **GAIN ERROR**

The gain error in the ADE7759 ADCs is defined as the difference between the measured ADC output code (minus the offset) and the ideal output code—see Channel 1 ADC and Channel 2 ADC. It is measured for each of the input ranges on Channel 1 (0.5 V, 0.25 V and 0.125 V). The difference is expressed as a percentage of the ideal code.

#### **GAIN ERROR MATCH**

The Gain Error Match is defined as the gain error (minus the offset) obtained when switching between a gain of 1 (for each of the input ranges) and a gain of 2, 4, 8, or 16. It is expressed as a percentage of the output ADC code obtained under a gain of 1. This gives the gain error observed when the gain selection is changed from 1 to 2, 4, 8, or 16.

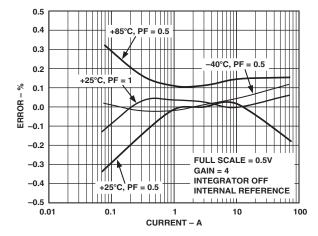

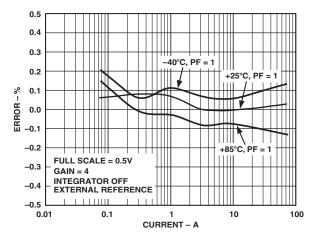

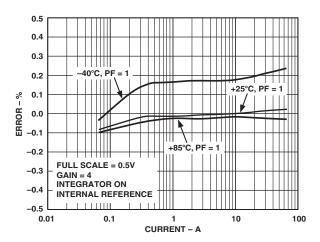

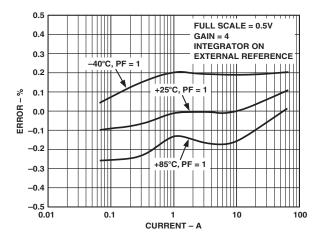

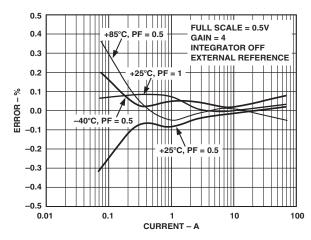

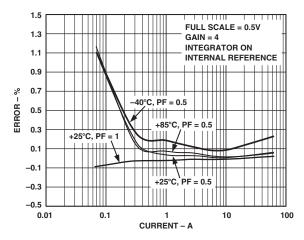

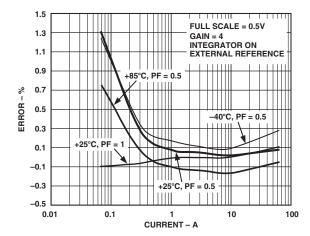

## **Typical Performance Characteristics—ADE7759**

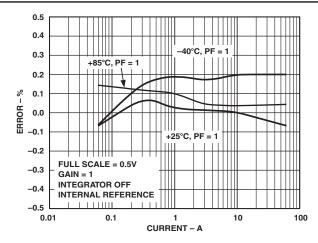

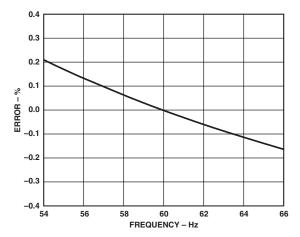

TPC 1. Error as a % of Reading (Integrator OFF, Power Factor = 1, Internal Reference, Gain = 1)

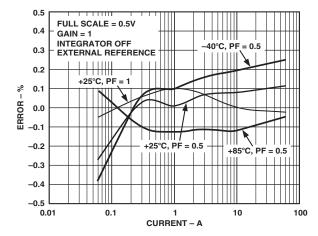

TPC 2. Error as a % of Reading (Integrator OFF, Power Factor = 1, External Reference, Gain = 1)

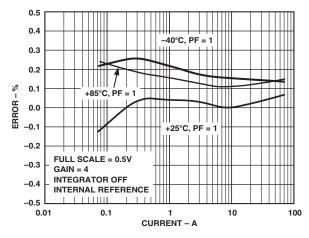

TPC 3. Error as a % of Reading (Integrator OFF, Power Factor = 1, Internal Reference, Gain = 4)

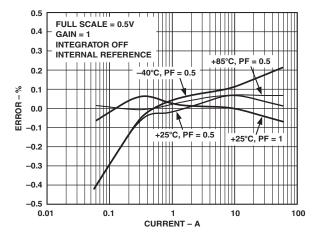

TPC 4. Error as a % of Reading (Integrator OFF, Power Factor = 0.5, Internal Reference, Gain = 1)

TPC 5. Error as a % of Reading (Integrator OFF, Power Factor = 0.5, External Reference, Gain = 1)

TPC 6. Error as a % of Reading (Integrator OFF, Power Factor = 0.5, Internal Reference, Gain = 4)

REV. 0 -9-

TPC 7. Error as a % of Reading (Integrator OFF, Power Factor = 1, External Reference, Gain = 4)

TPC 8. Error as a % of Reading (Integrator ON, Power Factor = 1, Internal Reference, Gain = 4)

TPC 9. Error as a % of Reading (Integrator ON, Power Factor = 1, External Reference, Gain = 4)

TPC 10. Error as a % of Reading (Integrator OFF, Power Factor = 0.5, External Reference, Gain = 4)

TPC 11. Error as a % of Reading (Integrator ON, Power Factor = 0.5, Internal Reference, Gain = 4)

TPC 12. Error as a % of Reading (Integrator ON, Power Factor = 0.5, External Reference, Gain = 4)

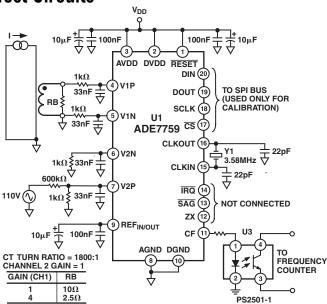

## **Test Circuits**

Test Circuit 1. Performance Curve (Integrator OFF)

#### $V_{DD}$ 100nF 100nF di/dt CURRENT AVDD DVDD RESET SENSOR DIN (20 1000 33nF TO SPI BUS (USED ONLY FOR DOUT ₹ $100\Omega$ $1k\Omega$ CALIBRATION) U1 ADE7759 CS 22pF 1kΩ ≸33nF CLKIN 22pF 600k $\Omega$ ĪRQ 33nF **SAG** (13) NOT CONNECTED ZX (12 REF<sub>IN/OUT</sub> CF U3 100nF AGND DGND то CHANNEL 1 GAIN = 4 FREQUENCY CHANNEL 2 GAIN = 1 COUNTER PS2501-1

Test Circuit 2. Performance Curve (Integrator ON)

#### ANALOG INPUTS

The ADE7759 has two fully differential voltage input channels. The maximum differential input voltage for input pairs V1P/V1N and V2P/V2N are  $\pm 0.5$  V. In addition, the maximum signal level on analog inputs for V1P/V1N and V2P/V2N are  $\pm 0.5$  V with respect to AGND.

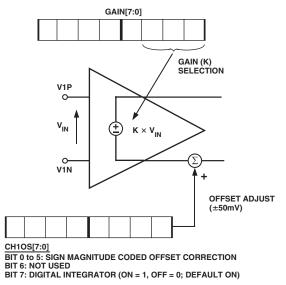

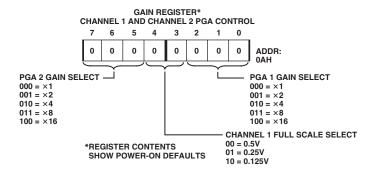

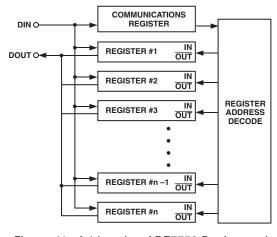

Each analog input channel has a PGA (Programmable Gain Amplifier) with possible gain selections of 1, 2, 4, 8, and 16. The gain selections are made by writing to the Gain register—see Figure 5. Bits 0 to 2 select the gain for the PGA in Channel 1 and the gain selection for the PGA in Channel 2 is made via Bits 5 to 7. Figure 4 shows how a gain selection for Channel 1 is made using the Gain register.

Figure 4. PGA in Channel 1

In addition to the PGA, Channel 1 also has a full-scale input range selection for the ADC. The ADC analog input range selection is also made using the Gain register—see Figure 2. As mentioned previously the maximum differential input voltage is 0.5 V. However, by using Bits 3 and 4 in the Gain register, the maximum ADC input voltage can be set to 0.5 V, 0.25 V, or 0.125 V. This is achieved by adjusting the ADC reference—see Reference Circuit section. Table I summarizes the maximum differential input signal level on Channel 1 for the various ADC range and gain selections.

Table I. Maximum Input Signal Levels for Channel 1

| Max Signal | ADC Input Range Selection |           |          |  |  |

|------------|---------------------------|-----------|----------|--|--|

| Channel 1  | 0.5 V                     | 0.25 V    | 0.125 V  |  |  |

| 0.5 V      | Gain = 1                  |           |          |  |  |

| 0.25 V     | Gain = 2                  | Gain = 1  |          |  |  |

| 0.125 V    | Gain = 4                  | Gain = 2  | Gain = 1 |  |  |

| 0.0625 V   | Gain = 8                  | Gain = 4  | Gain = 2 |  |  |

| 0.0313 V   | Gain = 16                 | Gain = 8  | Gain = 4 |  |  |

| 0.0156 V   |                           | Gain = 16 | Gain = 8 |  |  |

| 0.00781 V  |                           |           | Gain = 1 |  |  |

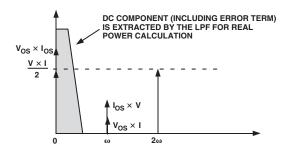

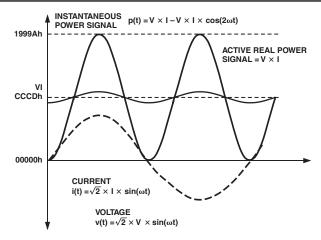

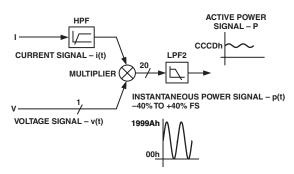

Figure 5. Analog Gain Register

It is also possible to adjust offset errors on Channel 1 and Channel 2 by writing to the Offset Correction registers (CH1OS and CH2OS respectively). These registers allow channel offsets in the range  $\pm 24$  mV to  $\pm 50$  mV (depending on the gain setting) to be removed. Note that it is not necessary to perform an offset correction in an energy measurement application if HPF1 Channel 1 is switched on. Figure 6 shows the effect of offsets on the real power calculation. As seen in Figure 6, an offset on Channel 1 and Channel 2 will contribute a dc component after multiplication. Since this dc component is extracted by LPF2 to generate the Active (Real) Power information, the offsets will have contributed an error to the Active Power calculation. This problem is easily avoided by enabling HPF1 in Channel 1. By removing the offset from at least one channel, no error component is generated at dc by the multiplication. Error terms at cos(ωt) are removed by LPF2 and by integration of the Active Power signal in the Active Energy register (AENERGY[39:0])—see Energy Calculation section.

Figure 6. Effect of Channel Offsets on the Real Power Calculation

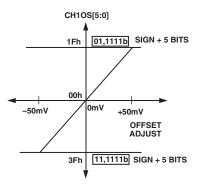

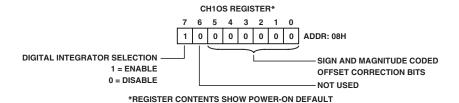

The contents of the Offset Correction registers are 6-bit, sign, and magnitude coded. The weighting of the LSB size depends on the gain setting, i.e., 1, 2, 4, 8, or 16. Table II shows the correctable offset span for each of the gain settings and the LSB weight (mV) for the Offset Correction registers. The maximum value that can be written to the offset correction registers is  $\pm 31$  decimal—see Figure 7.

Table II. Offset Correction Range

| Gain | Correctable Span | LSB Size    |

|------|------------------|-------------|

| 1    | ±50 mV           | 1.61 mV/LSB |

| 2    | ±37 mV           | 1.19 mV/LSB |

| 4    | ±30 mV           | 0.97 mV/LSB |

| 8    | ±26 mV           | 0.84 mV/LSB |

| 16   | ±24 mV           | 0.77 mV/LSB |

Figure 7 shows the relationship between the Offset Correction register contents and the offset (mV) on the analog inputs for a gain setting of one. In order to perform an offset adjustment, the analog inputs should be first connected to AGND, and there should be no signal on either Channel 1 or Channel 2. A read from Channel 1 or Channel 2 using the Waveform register will give an indication of the offset in the channel. This offset can be canceled by writing an equal but opposite offset value to the relevant offset register. The offset correction can be confirmed by performing another read. Note that when adjusting the offset of Channel 1, the digital integrator and the HPF1 should be disabled.

Figure 7. Channel Offset Correction Range (Gain = 1)

#### di/dt CURRENT SENSOR AND DIGITAL INTEGRATOR

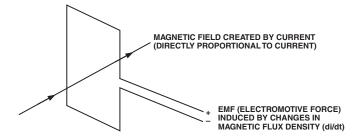

di/dt sensor detects changes in magnetic field caused by ac current. Figure 8 shows the principle of a di/dt current sensor.

Figure 8. Principle of a di/dt Current Sensor

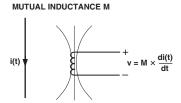

The flux density of a magnetic field induced by a current is directly proportional to the magnitude of the current. The changes in the magnetic flux density passing through a conductor loop generate an electromotive force (EMF) between the two ends of the loop. The EMF is a voltage signal that is proportional to the di/dt of the current. The voltage output from the di/dt current sensor is determined by the mutual inductance between the current-carrying conductor and the di/dt sensor. Figure 9 shows the mutual inductance produces a di/dt signal at the output of the sensor.

Figure 9. Mutual Inductance Between the di/dt Sensor and the Current Carrying Conductor

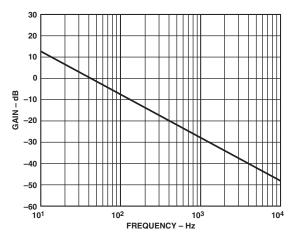

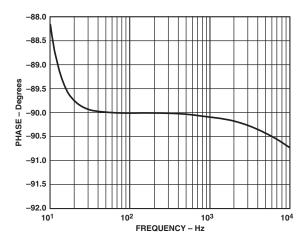

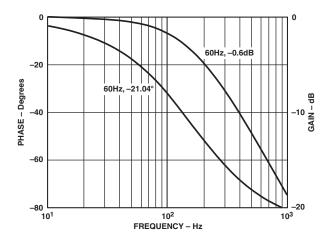

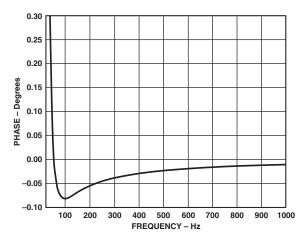

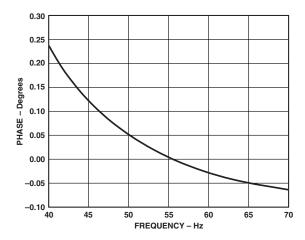

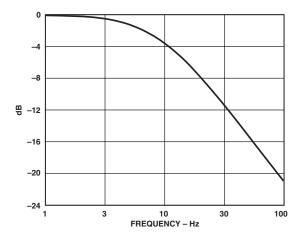

The current signal needs to be recovered from the di/dt signal before it can be used for active power calculation. An integrator is therefore necessary to restore the signal to its original form. The ADE7759 has a built-in digital integrator to recover the current signal from the di/dt sensor. The digital integrator on Channel 1 is switched on by default when the ADE7759 is powered up. Setting the MSB of the CH1OS register to 0 will turn off the integrator. Figures 10 to 13 show the magnitude and phase response of the digital integrator.

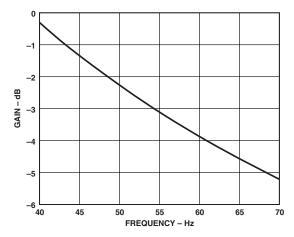

Figure 10. Gain Response of the Digital Integrator

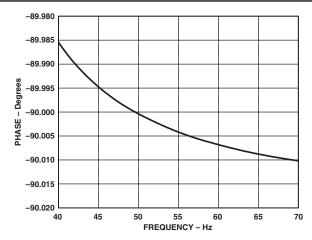

Figure 11. Phase Response of the Digital Integrator

Figure 12. Gain Response of the Digital Integrator (40 Hz to 70 Hz)

Figure 13. Phase Response of the Digital Integrator (40 Hz to 70 Hz)

Note that the integrator has a -20 dB/dec attenuation and approximately  $-90^{\circ}$  phase shift. When combined with a di/dt sensor, the resulting magnitude and phase response should be a flat gain over the frequency band of interest. However, the di/dt sensor has a 20 dB/dec gain associated with it, and generates significant high frequency noise. A more effective antialiasing filter is needed to avoid noise due to aliasing—see Antialias Filter section.

When the digital integrator is switched off, the ADE7759 can be used directly with a conventional current sensor such as current transformer (CT) or a low resistance current shunt.

#### ZERO CROSSING DETECTION

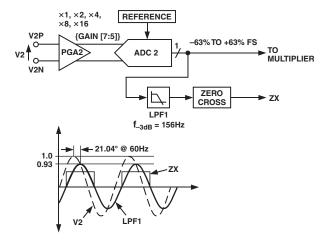

The ADE7759 has a zero crossing detection circuit on Channel 2. This zero crossing is used to produce an external zero cross signal (ZX) and it is also used in the calibration mode—see Energy Calibration section. The zero crossing signal is also used to initiate a temperature measurement on the ADE7759—see Temperature Measurement section. Figure 14 shows how the zero cross signal is generated from the output of LPF1.

Figure 14. Zero Cross Detection on Channel 2

The ZX signal will go logic high on a positive going zero crossing and logic low on a negative going zero crossing on Channel 2. The zero crossing signal ZX is generated from the output of LPF1. LPF1 has a single pole at 156 Hz (CLKIN = 3.579545 MHz). As a result there will be a phase lag between the analog input signal V2 and the output of LPF1. The phase response of this filter is shown in the Channel 2 Sampling section of this data sheet. The phase lag response of LPF1 results in a time delay of approximately 0.97 ms (@ 60 Hz) between the zero crossing on the analog inputs of Channel 2 and the rising or falling edge of ZX.

The zero crossing detection also has an associated time-out register, ZXTOUT. This unsigned, 12-bit register is decremented 1 LSB every 128/CLKIN seconds. The register is reset to its user programmed full-scale value every time a zero crossing on Channel 2 is detected. The default power on value in this register is FFFh. If the register decrements to zero before a zero crossing is detected and the DISSAG bit in the Mode register is logic zero, the  $\overline{SAG}$ pin will go active low. The absence of a zero crossing is also indicated on the  $\overline{IRQ}$  output if the SAG enable bit in the Interrupt Enable register is set to Logic 1. Irrespective of the enable bit setting, the SAG flag in the Interrupt Status register is always set when the ZXTOUT register is decremented to zero—see Interrupts section. The zero cross timeout register can be written/read by the user and has an address of 0Eh—see Serial Interface section. The resolution of the register is 128/CLKIN seconds per LSB. Thus the maximum delay for an interrupt is 0.15 second  $(128/CLKIN \times 2^{12}).$

#### LINE VOLTAGE SAG DETECTION

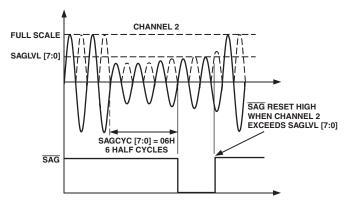

In addition to the detection of the loss of the line voltage signal (zero crossing), the ADE7759 can also be programmed to detect when the absolute value of the line voltage drops below a certain peak value, for a number of half cycles. This condition is illustrated in Figure 15.

Figure 15. Sag Detection

Figure 15 shows the line voltage fall below a threshold that is set in the Sag Level register (SAGLVL[7:0]) for nine half cycles. Since the Sag Cycle register (SAGCYC[7:0]) contains 06h, the SAG pin will go active low at the end of the sixth half cycle for which the line voltage falls below the threshold, if the DISSAG bit in the Mode register is logic zero. As is the case when zero crossings are no longer detected, the sag event is also recorded by setting the SAG flag in the Interrupt Status register. If the SAG enable bit is set to Logic 1, the  $\overline{IRQ}$  logic output will go active low—see Interrupts section.

The  $\overline{SAG}$  pin will go logic high again when the absolute value of the signal on Channel 2 exceeds the sag level set in the Sag Level register. This is shown in Figure 15 when the  $\overline{SAG}$  pin goes high during the tenth half cycle from the time when the signal on Channel 2 first dropped below the threshold level.

#### Sag Level Set

The contents of the Sag Level register (1 byte) are compared to the absolute value of the most significant byte output from LPF1, after it is shifted left by one bit. For example, the nominal maximum code from LPF1 with a full-scale signal on Channel 2 is 257F6h or (0010, 0101, 0111, 1111, 0110b)—see Channel 2 Sampling section. Shifting one bit left will give 0100, 1010, 1111, 1110, 1100b or 4AFECh. Therefore writing 4Ah to the Sag Level register will put the sag detection level at full scale. Writing 00h will put the sag detection level at zero. The Sag Level register is compared to the most significant byte of a waveform sample after the shift left, and detection is made when the contents of the Sag Level register are greater.

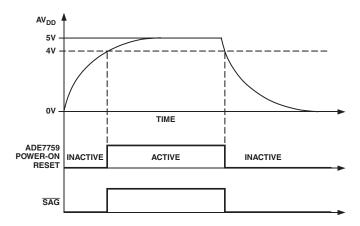

#### POWER SUPPLY MONITOR

The ADE7759 also contains an on-chip power supply monitor. The Analog Supply (AVDD) is continuously monitored by the ADE7759. If the supply is less than  $4\,V\pm 5\%$ , the ADE7759 will go into an inactive state, i.e., no energy will be accumulated when the supply voltage is below  $4\,V$ . This is useful to ensure correct device operation at power-up and during power-down. The power supply monitor has built-in hysteresis and filtering. This gives a high degree of immunity to false triggering due to noisy supplies.

Figure 16. On-Chip Power Supply Monitor

As seen in Figure 16, the trigger level is nominally set at 4 V. The tolerance on this trigger level is about  $\pm 5\%$ . The  $\overline{SAG}$  pin can also be used as a power supply monitor input to the MCU. The  $\overline{SAG}$  pin will go logic low when the ADE7759 is reset. The power supply and decoupling for the part should be such that the ripple at  $AV_{DD}$  does not exceed 5 V  $\pm$  5% as specified for normal operation.

Bit 6 of the Interrupt Status register (STATUS[7:0]) will be set to Logic High upon power-up or every time the analog supply (AV $_{DD}$ ) dips below the power supply monitor threshold (4 V  $\pm$  5%) and recovers. However, no interrupt can be generated because the corresponding bit (Bit 6) in the Interrupt Enable register (IRQEN[7:0]) is not active—see Interrupts section.

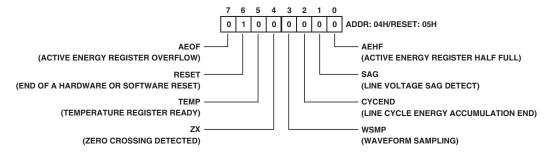

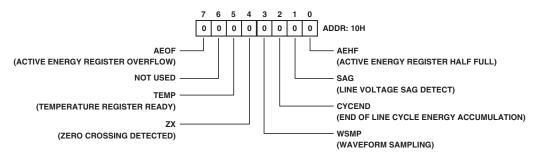

#### **INTERRUPTS**

ADE7759 Interrupts are managed through the Interrupt Status register (STATUS[7:0]) and the Interrupt Enable register (IRQEN[7:0]). When an interrupt event occurs in the ADE7759, the corresponding flag in the Status register is set to a Logic 1—see Interrupt Status register. If the enable bit for this interrupt in the Interrupt Enable register is Logic 1, then the  $\overline{\text{IRQ}}$  logic output goes active low. The flag bits in the Status register are set irrespective of the state of the enable bits.

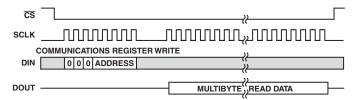

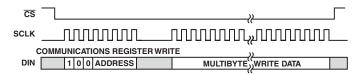

In order to determine the source of the interrupt, the system master (MCU) should perform a read from the Status register with reset (RSTATUS[7:0]). This is achieved by carrying out a read from address 05h. The  $\overline{IRQ}$  output will go logic high on completion of the Interrupt Status register read command—see Interrupt Timing section. When carrying out a read with reset, the ADE7759 is designed to ensure that no interrupt events are missed. If an interrupt event occurs just as the Status register is being read, the event will not be lost and the  $\overline{IRQ}$  logic output is guaranteed to go high for the duration of the Interrupt Status register data transfer before going logic low again to indicate the pending interrupt. See the following section for a more detailed description.

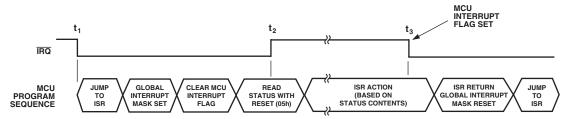

#### Using the ADE7759 Interrupts with an MCU

Figure 17 shows a timing diagram with a suggested implementation of ADE7759 interrupt management using an MCU. At time  $t_1$  the  $\overline{IRQ}$  line will go active low, indicating that one or more interrupt events have occurred in the ADE7759. The  $\overline{IRQ}$  logic output should be tied to a negative edge-triggered external interrupt on the MCU. On detection of the negative edge, the MCU

should be configured to start executing its Interrupt Service Routine (ISR). On entering the ISR, all interrupts should be disabled using the global interrupt enable bit. At this point the MCU external interrupt flag can be cleared to capture interrupt events that occur during the current ISR.

When the MCU interrupt flag is cleared, a read from the Status register with reset is carried out. This will cause the  $\overline{IRQ}$  line to be reset logic high (t<sub>2</sub>)—see Interrupt Timing section. The Status register contents are used to determine the source of the interrupt(s) and hence the appropriate action to be taken. If a subsequent interrupt event occurs during the ISR, that event will be recorded by the MCU external interrupt flag being set again (t<sub>3</sub>). On returning from the ISR, the global interrupt mask will be cleared (same instruction cycle) and the external interrupt flag will cause the MCU to jump to its ISR once again. This will ensure that the MCU does not miss any external interrupts.

#### **Interrupt Timing**

The Serial Interface section should be reviewed first, before the interrupt timing. As previously described, when the  $\overline{IRQ}$  output goes low the MCU ISR must read the Interrupt Status register to determine the source of the interrupt. When reading the Status register contents, the  $\overline{IRQ}$  output is set high on the last falling edge of SCLK of the first byte transfer (read Interrupt Status register command). The  $\overline{IRQ}$  output is held high until the last bit of the next 8-bit transfer is shifted out (Interrupt Status register contents)—see Figure 18. If an interrupt is pending at this time, the  $\overline{IRQ}$  output will go low again. If no interrupt is pending, the  $\overline{IRQ}$  output will stay high.

Figure 17. Interrupt Management

Figure 18. Interrupt Timing

REV. 0 –15–

#### TEMPERATURE MEASUREMENT

ADE7759 also includes an on-chip temperature sensor. A temperature measurement can be made by setting Bit 5 in the Mode register. When Bit 5 is set logic high in the Mode register, the ADE7759 will initiate a temperature measurement on the next zero crossing. When the zero crossing on Channel 2 is detected, the voltage output from the temperature sensing circuit is connected to ADC1 (Channel 1) for digitizing. The resultant code is processed and placed in the Temperature register (TEMP[7:0]) approximately 26 µs later (24 CLKIN cycles). If enabled in the Interrupt Enable register (Bit 5), the IRQ output will go active low when the temperature conversion is finished. Please note that temperature conversion will introduce a small amount of noise in the energy calculation. If temperature conversion is performed frequently (i.e., multiple times per second), a noticeable error will accumulate in the resulting energy calculation over time.

The contents of the Temperature register are signed (two's complement) with a resolution of approximately 1 LSB/°C. The temperature register will produce a code of 00h when the ambient temperature is approximately 70°C. The temperature measurement is uncalibrated in the ADE7759 and has an offset tolerance that could be as high as  $\pm 20$ °C.

#### ANALOG-TO-DIGITAL CONVERSION

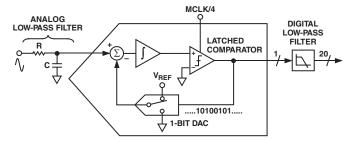

The analog-to-digital conversion in the ADE7759 is carried out using two second order sigma-delta ADCs. The block diagram in Figure 19 shows a first order (for simplicity) sigma-delta ADC. The converter is made up of two parts, first the sigma-delta modulator and second the digital low-pass filter.

A sigma-delta modulator converts the input signal into a continuous serial stream of 1s and 0s at a rate determined by the sampling clock. In the ADE7759, the sampling clock is equal to CLKIN/4. The 1-bit DAC in the feedback loop is driven by the serial data stream. The DAC output is subtracted from the input signal. If the loop gain is high enough, the average value of the DAC output (and therefore the bitstream) will approach that of the input signal level. For any given input value in a single sampling interval, the data from the 1-bit ADC is virtually meaningless. Only when a large number of samples are averaged will a meaningful result be obtained. This averaging is carried out in the second part of the ADC, the digital low-pass filter. By averaging a large number of bits from the modulator, the low-pass filter can produce 20-bit data words that are proportional to the input signal level.

Figure 19. First Order Sigma-Delta (Σ-Δ) ADC

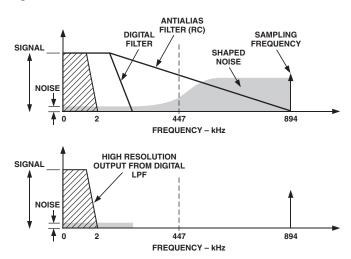

The sigma-delta converter uses two techniques to achieve high resolution from what is essentially a one-bit conversion technique. The first is oversampling. By oversampling we mean that the signal is sampled at a rate (frequency) that is many times higher

than the bandwidth of interest. For example, the sampling rate in the ADE7759 is CLKIN/4 (894 kHz) and the band of interest is 40 Hz to 2 kHz. Oversampling has the effect of spreading the quantization noise (noise due to sampling) over a wider bandwidth. With the noise spread more thinly over a wider bandwidth, the quantization noise in the band of interest is lowered—see Figure 20. However, oversampling alone is not an efficient enough method to improve the signal to noise ratio (SNR) in the band of interest. For example, an oversampling ratio of 4 is required just to increase the SNR by only 6 dB (one bit). To keep the oversampling ratio at a reasonable level, it is possible to shape the quantization noise so that the majority of the noise lies at the higher frequencies. This is what happens in the sigma-delta modulator: the noise is shaped by the integrator, which has a high-pass type response for the quantization noise. The result is that most of the noise is at the higher frequencies, where it can be removed by the digital low-pass filter. This noise shaping is also shown in Figure 20.

Figure 20. Noise Reduction Due to Oversampling and Noise Shaping in the Analog Modulator

#### Antialias Filter

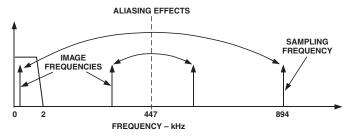

Figure 20 also shows an analog low-pass filter (RC) on the input to the modulator. This filter is present to prevent aliasing. Aliasing is an artifact of all sampled systems. Basically it means that frequency components in the input signal to the ADC that are higher than half the sampling rate of the ADC will appear in the sampled signal at a frequency below half the sampling rate. Figure 21 illustrates the effect. Frequency components (arrows shown in black) above half the sampling frequency (also known as the Nyquist frequency, i.e., 447 kHz) get imaged or folded back down below 447 kHz (arrows shown in grey). This will happen with all ADCs regardless of the architecture. In the example shown, it can be seen that only frequencies near the sampling frequency (894 kHz) will move into the band of interest for metering, i.e., 40 Hz-2 kHz. This allows us to use a very simple LPF (low-pass filter) to attenuate these high frequencies (near 900 kHz) and to prevent distortion in the band of interest. For a conventional current sensor, a simple RC filter (single pole) with a corner frequency of 10 kHz will produce an attenuation of approximately 40 dBs at 894 kHz—see Figure 20. The 20 dB per decade attenuation is usually sufficient to eliminate the effects of aliasing for conventional current sensor.

Figure 21. ADC and Signal Processing in Channel 1

For a di/dt sensor such as a Rogowski coil, however, the sensor has 20 dB per decade gain. This will neutralize the –20 dB per decade attenuation produced by this simple LPF and nullifies the antialias filter. Therefore, when using a di/dt sensor, measure should be taken to offset the 20 dB per decade gain coming from the di/dt sensor and produce sufficient attenuation to eliminate any aliasing effect. One simple approach is to cascade two RC filters to produce –40 dB per decade attenuation. The transfer function for a cascaded filter is the following:

$$H(s) = \frac{1}{1 + sR1C1 + sR2C2 + sR1C2 + s^2R1C1R2C2}$$

where R1C1 represents the RC used in the first stage of the cascade and R2C2 in that of the second stage. The  $s^2$  term in the transfer function produces a -40 dB/decade attenuation. Note that to minimize the measurement error, especially at low power factor, it is important to match the phase angle between the voltage and the current channel. The small phase mismatch in the external antialias filter can be corrected using the Phase Calibration register (PHCAL[7:0])—see Phase Compensation section.

#### **ADC Transfer Function**

Below is an expression which relates the output of the LPF in the sigma-delta ADC to the analog input signal level. Both ADCs in the ADE7759 are designed to produce the same output code for the same input signal level.

$$Code(ADC) = 3.0492 \times \frac{V_{IN}}{V_{REF}} \times 262,144$$

Therefore, with a full-scale signal on the input of 0.5 V and an internal reference of 2.42 V, the ADC output code is nominally 165,151 or 2851Fh. The maximum code from the ADC is  $\pm 262,144$ , which is equivalent to an input signal level of  $\pm 0.794$  V. However, for specified performance it is not recommended that the full-scale input signal level of 0.5 V be exceeded.

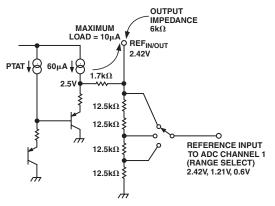

#### Reference Circuit

Shown in Figure 22 is a simplified version of the reference output circuitry. The nominal reference voltage at the  ${\rm REF_{IN/OUT}}$  pin is 2.42 V. This is the reference voltage used for the ADCs in the ADE7759. However, Channel 1 has three input range selections, which are selected by dividing down the reference value used for the ADC in Channel 1. The reference value used for Channel 1 is divided down to 1/2 and 1/4 of the nominal value by using an internal resistor divider as shown in Figure 22.

Figure 22. ADC and Reference Circuit Output

The REF<sub>IN/OUT</sub> pin can be overdriven by an external source, e.g., an external 2.5 V reference. Note that the nominal reference value supplied to the ADCs is now 2.5 V not 2.42 V. This has the effect of increasing the nominal analog input signal range by  $2.5/2.42 \times 100\% = 3\%$ , or from 0.5 V to 0.5165 V.

The internal voltage reference on the ADE7759 has a temperature drift associated with it—see ADE7759 Specifications for the temperature coefficient specification (in ppm°C). The value of the temperature drift varies slightly from part to part. Since the reference is used for the ADCs in both Channel 1 and 2, any x% drift in the reference will result in 2x% deviation of the meter reading. The reference drift resulting from temperature changes is usually very small and it is typically much smaller than the drift of other components on a meter. However, if guaranteed temperature performance is needed, one needs to use an external voltage reference. Alternatively, the meter can be calibrated at multiple temperatures. Real-time compensation can be achieved easily using the on-chip temperature sensor.

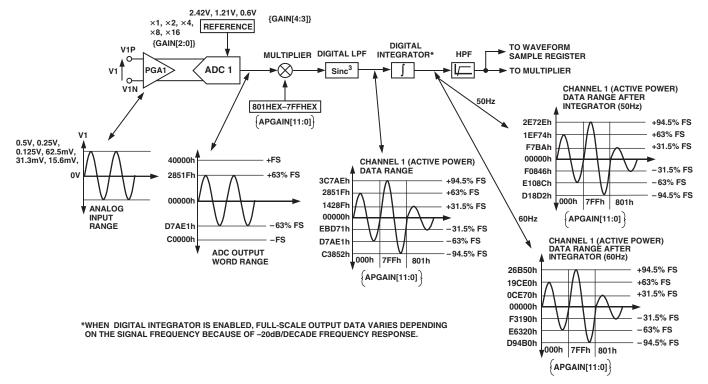

#### **CHANNEL 1 ADC**

Figure 23 shows the ADC and signal processing chain for Channel 1. In waveform sampling mode the ADC outputs a signed two's complement 20-bit data word at a maximum of 27.9 kSPS (CLKIN/128). The output of the ADC can be scaled by  $\pm 50\%$ to perform an overall power calibration or to calibrate the ADC output. While the ADC outputs a 20-bit two's complement value, the maximum full-scale positive value from the ADC is limited to 40,000h (+262,144 decimal). The maximum full-scale negative value is limited to C0000h (-262,144 decimal). If the analog inputs are over-ranged, the ADC output code will clamp at these values. With the specified full-scale analog input signal of 0.5 V (or 0.25 V or 0.125 V—see Analog Inputs section) the ADC will produce an output code that is approximately 63% of its full-scale value. This is illustrated in Figure 23. The diagram in Figure 23. shows a full-scale voltage signal being applied to the differential inputs V1P and V1N. The ADC output swings between D7AE1h (-165,151) and 2851Fh (+165,151). This is approximately 63% of the full-scale value 40,000h (262,144). Over-ranging the analog inputs with more than 0.5 V differential (0.25 or 0.125, depending on Channel 1 full-scale selection) will cause the ADC output to increase towards its full-scale value. However, for specified operation the differential signal on the analog inputs should not exceed the recommended value of 0.5 V.

REV. 0 –17–

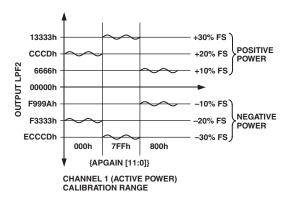

#### Channel 1 ADC Gain Adjust

The ADC gain in Channel 1 can be adjusted by using the multiplier and Active Power Gain register (APGAIN[11:0]). The gain of the ADC is adjusted by writing a two's complement 12-bit word to the Active Power Gain register. Below is the expression that shows how the gain adjustment is related to the contents of the Active Power Gain register.

$$Code = \left(ADC \times \left\{1 + \frac{APGAIN}{2^{12}}\right\}\right)$$

For example, when 7FFh is written to the Active Power Gain register the ADC output is scaled up by 50%. 7FFh = 2047 decimal,  $2047/2^{12} = 0.5$ . Similarly, 801h = 2047 decimal (signed two's complement) and ADC output is scaled by -50%. These two examples are graphically illustrated in Figure 23.

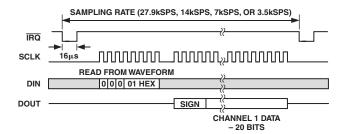

#### **Channel 1 Sampling**

The waveform samples may also be routed to the WAVEFORM register (MODE[14:13] = 1, 0) to be read by the system master (MCU). In waveform sampling mode the WSMP bit (Bit 3) in the Interrupt Enable register must also be set to Logic 1. The Active Power and Energy calculation will remain uninterrupted during waveform sampling.

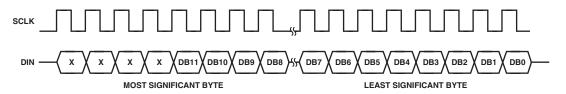

When in waveform sample mode, one of four output sample rates may be chosen by using bits 11 and 12 of the Mode register (WAVSEL1, 0). The output sample rate may be 27.9 kSPS, 14 kSPS, 7 kSPS, or 3.5 kSPS—see Mode Register section. The interrupt request output  $\overline{IRQ}$  signals a new sample availability by going active low. The timing is shown in Figure 24. The 20-bit

waveform samples are transferred from the ADE7759 one byte (eight-bits) at a time, with the most significant byte shifted out first. The 20-bit data word is right justified and sign extended to 24 bits (three bytes)—see Serial Interface section.

Figure 24. Waveform Sampling Channel 1

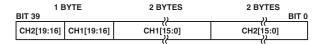

## CHANNEL 1 AND CHANNEL 2 WAVEFORM SAMPLING MODE

In Channel 1 and Channel 2 waveform sampling mode (MODE[14:13] = 01), the output is a 40-bit waveform sample data that contains both the waveform samples from Channel 1 and Channel 2 ADCs. Figure 25 shows the format of the 40-bit waveform output.

Figure 25. 40-Bit Combined Channel 1 and Channel 2 Waveform Sample Data Format

Figure 23. ADC and Signal Processing in Channel 1

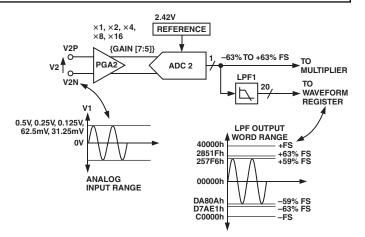

#### **CHANNEL 2 ADC**

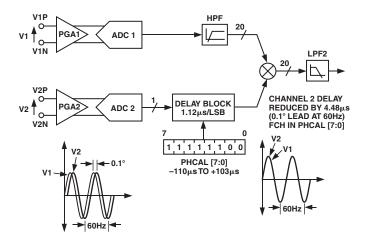

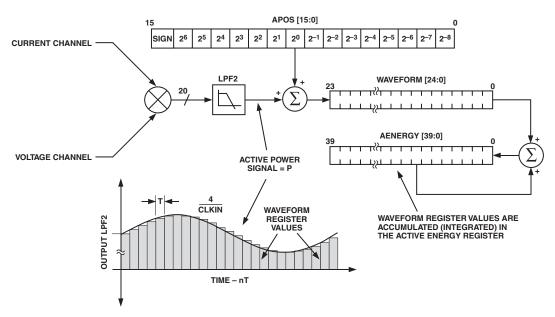

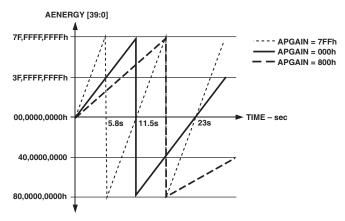

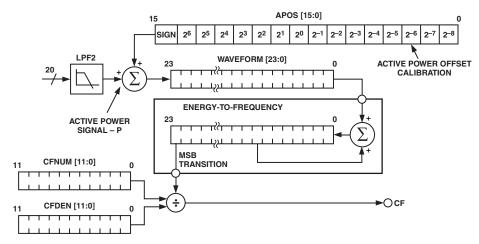

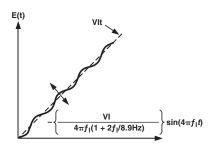

#### **Channel 2 Sampling**