# Secondary Side Post Regulator for AC/DC and DC/DC Multiple Output Converters

## Description

The CS5101 is a bipolar monolithic secondary side post regulator (SSPR) which provides tight regulation of multiple output voltages in AC-DC or DC-DC converters. Leading edge pulse width modulation is used with the CS5101.

The CS5101 is designed to operate over an 8V to 45V supply voltage ( $V_{CC}$ ) range and up to a 75V drive voltage ( $V_C$ ).

The CS5101 features include a totem pole output with 1.5A peak output current capability, externally programmable overcurrent protection, an on chip 2% precision 5V reference, internally compensated error amplifier, externally synchronized switching frequency, and a power switch drain voltage monitor. It is available in a 14 lead plastic DIP or a 16 lead wide body SO package.

1

#### **Application Diagram** (1)(3) R10 (5 $\sum R13$ >R8 ≥R11 6 -- C6 C<sub>R5</sub> $\leq R5$ $\leq_{R6}$ $\leq$ R12 $\leq_{R14}$ 5 R9 C<sub>R1</sub> C5 $S_{R1}$ ≶r2 C<sub>R3</sub> R7 VD VSYNC V<sub>CC</sub> CS5101 V<sub>C</sub> SSPR PGnd V<sub>REF</sub> R3 🗸 C<sub>R2</sub> LGnd C4 IS COMP Vfr COMP ١S R4 RAMP IS+ C2 2 C3: CR

Features

- 1.5A Peak Output (Grounded Totem Pole)

- 8V to 75V Gate Drive Voltage

- 8V to 45V Supply Voltage

- 300ns Propagation Delay

- 1% Error Amplifier Reference Voltage

- Lossless Turn On and Turn Off

- Sleep Mode:  $< 100 \mu A$

- Overcurrent Protection with Dedicated Differential Amp

- Synchronization to External Clock

- External Power Switch Drain Voltage Monitor

## **Package Options**

#### 14L PDIP

16L SO Wide

| SYNC 1          |                                         | 」 v <sub>D</sub> |

|-----------------|-----------------------------------------|------------------|

| Vcc 🗖           |                                         | ⊐v <sub>c</sub>  |

|                 |                                         | JV <sub>G</sub>  |

| DGnd            |                                         | PGnd             |

| AGnd            |                                         | PGnd             |

| V <sub>FB</sub> | /////////////////////////////////////// |                  |

| COMP            |                                         | IS-              |

| RAMP            |                                         | ]IS+             |

Cherry Semiconductor Corporation 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885-3600 Fax: (401)885-5786 Email: info@cherry-semi.com Web Site: www.cherry-semi.com

### A **CHERRY** Company

## Absolute Maximum Ratings

| Power Supply Voltage, V <sub>CC</sub>                                                                              | 0.3V to 45V                      |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------|

| V <sub>SYNC</sub> and Output Supply Voltages, V <sub>C</sub> , V <sub>G</sub> , V <sub>SYNC</sub> , V <sub>D</sub> |                                  |

| $V_{IS}^{+}$ , $V_{IS}^{-}$ ( $V_{CC}^{-}$ 4V, up to 24V)                                                          | 0.3 to 24V                       |

| V <sub>REF</sub> , V <sub>FB</sub> , V <sub>COMP</sub> , V <sub>RAMP</sub> , V <sub>ISCOMP</sub>                   | 0.3 to 10V                       |

| Operating Junction Temperature, T <sub>I</sub>                                                                     | 40 to 150°C                      |

| Operating Temperature Range                                                                                        | 40 to 85°C                       |

| Storage Temperature Range                                                                                          | 65 to 150°C                      |

| Output Energy (capacitive load per cycle)                                                                          | 5µJ                              |

| ESD Human Body                                                                                                     | 2kV                              |

| ESD Machine Model                                                                                                  |                                  |

| Lead Temperature Soldering                                                                                         |                                  |

| Wave Solder (through hole styles only)                                                                             | 10 sec. max, 260°C peak          |

| Reflow (SMD styles only)                                                                                           | sec. max above 183°C, 230°C peak |

| Electrical Characteristics: -40°C ≤                                                  | $T_A \le 85^{\circ}C; -40^{\circ}C \le T_J \le 150^{\circ}C; 10V < V_{CC} < 4$ | 5V; 8V < V <sub>C</sub> | <75V unless | otherwise sp | pecified. |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------|-------------|--------------|-----------|

| PARAMETER                                                                            | TEST CONDITIONS                                                                | MIN                     | ТҮР         | MAX          | UNIT      |

| Error Amplifier                                                                      |                                                                                |                         |             |              |           |

| Input Voltage Initial Accuracy                                                       | $V_{FB} = V_{COMP}; V_{CC} = 15V;$<br>T = 25°C (Note 1)                        | 1.98                    | 2.00        | 2.02         | V         |

| Input Voltage                                                                        | $V_{FB} = V_{COMP'}$ includes line and temp                                    | 1.94                    | 2.00        | 2.06         | V         |

| Input Bias Current                                                                   | $V_{FB} = 0V$ ; $IV_{FB}$ flows out of pin                                     |                         |             | 500          | nA        |

| Open Loop Gain                                                                       | $1.5V < V_{COMP} < 3.0V$                                                       | 60                      | 70          |              | dB        |

| Unity Gain Bandwidth                                                                 | 1.5V < V <sub>COMP</sub> < 3.0V; (Note 1)                                      | 0.7                     | 1.0         |              | MH        |

| Output Sink Current                                                                  | $V_{COMP} = 2.0V; V_{FB} = 2.2V$                                               | 2                       | 8           |              | mA        |

| Output Source Current                                                                | $V_{COMP} = 2.0V; V_{FB} = 1.8V$                                               | 2                       | 6           |              | mA        |

| V <sub>COMP</sub> High                                                               | $V_{FB} = 1.8V$                                                                | 3.3                     | 3.5         | 3.7          | V         |

| V <sub>COMP</sub> Low                                                                | $V_{FB} = 2.2V$                                                                | 0.85                    | 1.0         | 1.15         | V         |

| PSRR                                                                                 | $10V < V_{CC} < 45V;$<br>$V_{FB} = V_{COMP}$ (Note 1)                          | 60                      | 70          |              | dB        |

| Voltage Reference Output Voltage Initial Accuracy                                    | V <sub>CC</sub> = 15V; T = 25°C (Note 1)                                       | 4.9                     | 5.0         | 5.1          | V         |

| Output Voltage                                                                       | $0A < I_{REF} < 8mA$                                                           | 4.8                     | 5.0         | 5.2          | V         |

| Line Regulation                                                                      | $10V < V_{CC} < 45V; I_{REF} = 0A$                                             |                         | 10          | 60           | mV        |

| Load Regulation                                                                      | $0A < I_{REF} < 8mA$                                                           |                         | 20          | 60           | mV        |

| Current Limit                                                                        | $V_{REF} = 4.8V$                                                               | 10                      | 50          |              | mA        |

| $V_{\text{REF}}$ OK FAULT V $V_{\text{SYNC}} = 5V; V_{\text{REF}} = V_{\text{LOAD}}$ |                                                                                | 4.10                    | 4.40        | 4.60         | V         |

| V <sub>REF</sub> OK V                                                                | $V_{SYNC} = 5V; V_{REF} = V_{LOAD}$                                            | 4.30                    | 4.50        | 4.80         | V         |

| V <sub>REF</sub> _OK Hysteresis                                                      |                                                                                | 40                      | 100         | 250          | mV        |

|                                                                                      |                                                                                |                         |             |              |           |

| Current Sense Amplifier                                                              |                                                                                |                         |             |              |           |

| IS COMP High V                                                                       | $IS^+ = 5V; IS^- = IS COMP$                                                    | 4.7                     | 5.0         | 5.3          | V         |

| IS COMP Low V                                                                        | $IS^+ = 0V; IS^- = IS COMP$                                                    | 0.5                     | 1.0         | 1.3          | V         |

| Source Current                                                                       | $IS^+ = 5V; IS^- = 0V$                                                         | 2.0                     | 10          |              | mA        |

| Sink Current                                                                         | $IS^{-} = 5V; IS^{+} = 0V$                                                     | 10                      | 20          |              | mA        |

| Open Loop Gain                                                                       | $1.5V \leq V_{COMP} \leq 4.5V; R_L = 4k\Omega$                                 | 60                      | 80          |              | dB        |

| CMRR                                                                                 | (Note 1)                                                                       | 60                      | 80          |              | dB        |

| PSRR                                                                                 | 10V < V <sub>CC</sub> < 45V, (Note 1)                                          | 60                      | 80          |              | dB        |

| Unity Gain Bandwidth                                                                 | $1.5V \leq V_{COMP} \leq 4.5V; R_L = 4k\Omega \label{eq:complex}$ (Note 1)     | 0.5                     | 0.8         |              | MH        |

|                                                                                      |                                                                                |                         |             |              |           |

| PARAMETER                                                                                  | TEST CONDITIONS                                                             | MIN  | ТҮР  | MAX                  | UNIT |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------|----------------------|------|

| Current Sense Amplifier: contin                                                            | ued                                                                         |      |      |                      |      |

| Input Offset Voltage                                                                       | $V_{IS}$ + = 2.5V; $V_{IS}$ - = $V_{ISCOMP}$                                | -8   | 0    | 8                    | mV   |

| Input Bias Currents                                                                        | $V_{IS}$ + = $V_{IS}$ - = 0V; $I_{IS}$ flows out of pins                    |      | 20   | 250                  | nA   |

| Input Offset Current (IS <sup>+</sup> , IS <sup>-</sup> )                                  |                                                                             | -250 | 0    | 250                  | nA   |

| Input Signal Voltage Range                                                                 | (Note 1)                                                                    | -0.3 |      | V <sub>CC</sub> -4.0 | V    |

| RAMP/SYNC Generator                                                                        |                                                                             |      |      |                      |      |

| Ramp Source Current Initial<br>Accuracy                                                    | $V_{\text{SYNC}} = 5V, V_{\text{RAMP}} = 2.5V; T = 25^{\circ}C$<br>(Note 1) | 0.18 | 0.20 | 0.22                 | mA   |

| Ramp Source Current                                                                        | $V_{SYNC} = 5V$ ; $V_{RAMP} = 2.5V$                                         | 0.16 | 0.20 | 0.24                 | mA   |

| Ramp Sink Current                                                                          | $V_{SYNC} = 0V; V_{RAMP} = 2.5V$                                            | 1.0  | 4.0  |                      | mA   |

| RAMP Peak Voltage                                                                          | $V_{SYNC} = 5V$                                                             | 3.3  | 3.5  | 3.7                  | V    |

| RAMP Valley Voltage                                                                        | $V_{SYNC} = 0V$                                                             | 1.4  | 1.5  | 1.6                  | V    |

| RAMP Dynamic Range                                                                         | $V_{RAMPDR} = V_{RAMPPK} - V_{RAMPVY}$                                      | 1.7  | 2.0  | 2.3                  | V    |

| RAMP Sleep Threshold Voltage                                                               | $V_{RAMP} @ V_{REF} < 2.0V$                                                 | 0.3  | 0.6  | 1.0                  | V    |

| SYNC Threshold                                                                             | $V_{SYNC} @ V_{RAMP} > 2.5V$                                                | 2.3  | 2.5  | 2.7                  | V    |

| SYNC Input Bias Current $V_{SYNC} = 0V$ ; $I_{SYNC}$ flows out of particular               |                                                                             |      | 1    | 20                   | μΑ   |

| Output Stage                                                                               |                                                                             |      |      |                      |      |

| V <sub>G</sub> , High                                                                      | $V_{SYNC} = 5V; IV_G = 200mA, V_C - V_G$                                    |      | 1.6  | 2.5                  | V    |

| V <sub>G</sub> , Low                                                                       | $V_{SYNC} = 0V; IV_G = 200mA$                                               |      | 0.9  | 1.5                  | V    |

| $V_G$ Rise Time Switch $V_{SYNC}$ High; $C_G = 1nF$ ;<br>$V_{CC} = 15V$ ; measure 2V to 8V |                                                                             |      | 30   | 75                   | ns   |

| V <sub>G</sub> Fall Time                                                                   | Switch $V_{SYNC}$ Low; $C_G = 1nF$<br>$V_{CC} = 15V$ ; measure 8V to 2V     |      | 40   | 100                  | ns   |

| $V_{\rm G}$ Resistance to Gnd Remove supplies; $V_{\rm G} = 10V$                           |                                                                             |      | 50   | 100                  | kΩ   |

| V <sub>D</sub> Resistance to Gnd                                                           | Remove supplies; $V_D = 10V$                                                | 500  | 1500 |                      | Ω    |

| General                                                                                    |                                                                             |      |      |                      |      |

| I <sub>CC</sub> , Operating                                                                | $V_{SYNC} = 5V$                                                             |      | 12   | 18                   | mA   |

| I <sub>CC</sub> in UVL                                                                     | $V_{CC} = 6V$                                                               |      | 300  | 500                  | μΑ   |

| I <sub>CC</sub> in Sleep Mode High                                                         | $V_{RAMP} = 0V; V_{CC} = 45V$                                               |      | 80   | 200                  | μA   |

| I <sub>CC</sub> In Sleep Mode Low                                                          | $V_{RAMP} = 0V; V_{CC} = 10V$                                               |      | 20   | 50                   | μA   |

| $I_{C}$ , Operating High $V_{SYNC} = 5V; V_{FB} = V_{IS} = 0V; V_C = 75V$                  |                                                                             |      | 4    | 8                    | mA   |

| I <sub>C</sub> , Operating Low                                                             | $V_{SYNC} = 5V; V_{FB} = V_{IS} = 0V; V_C = 8V$                             |      | 3    | 6                    | mA   |

| UVLO Start Voltage                                                                         |                                                                             | 7.4  | 8.0  | 9.2                  | V    |

| UVLO Stop Voltage                                                                          |                                                                             | 6.4  | 7.0  | 8.3                  | V    |

| UVLO Hysteresis                                                                            |                                                                             | 0.8  | 1.0  | 1.2                  | V    |

| Leading Edge, t <sub>DELAY</sub>                                                           | $V_{SYNC} = 2.5V$ to $V_G = 8V$                                             |      | 280  |                      | ns   |

| Trailing Edge, $t_{DELAY}$ $V_{SYNC} = 2.5V$ to $V_G = 2V$                                 |                                                                             |      | 750  |                      | ns   |

Note 1: Guaranteed by design. Not 100% tested in production.

| CS5101 | Package Pin Description |             |                  |                                                      |  |

|--------|-------------------------|-------------|------------------|------------------------------------------------------|--|

| CS     | PACKAG                  | E PIN #     | PIN SYMBOL       | FUNCTION                                             |  |

|        | 14L PDIP                | 16L SO Wide |                  |                                                      |  |

|        | 1                       | 1           | SYNC             | Synchronization input.                               |  |

|        | 2                       | 2           | V <sub>CC</sub>  | Logic supply (10V to 45V).                           |  |

|        | 3                       | 3           | V <sub>REF</sub> | 5.0V voltage reference.                              |  |

|        | 4                       |             | LGnd             | Logic level ground (Analog and digital ground tied). |  |

|        | 5                       | 6           | $V_{FB}$         | Error amplifier inverting input.                     |  |

|        | 6                       | 7           | COMP             | Error amplifier output and compensation.             |  |

|        | 7                       | 8           | RAMP             | RAMP programmable with the external capacitor.       |  |

|        | 8                       | 9           | IS+              | Current sense amplifier non-inverting input.         |  |

|        | 9                       | 10          | IS-              | Current sense amplifier inverting input.             |  |

|        | 10                      | 11          | IS COMP          | Current sense amplifier compensation and output.     |  |

|        | 11                      | 12, 13      | PGnd             | Power ground.                                        |  |

|        | 12                      | 14          | V <sub>G</sub>   | External power switch gate drive.                    |  |

|        | 13                      | 15          | V <sub>C</sub>   | Output power stage supply voltage (8V to 75V).       |  |

|        | 14                      | 16          | V <sub>D</sub>   | External FET DRAIN Voltage Monitor.                  |  |

|        |                         | 5           | AGnd             | Analog Ground.                                       |  |

|        |                         | 4           | DGnd             | Digital Ground.                                      |  |

## **Circuit Description**

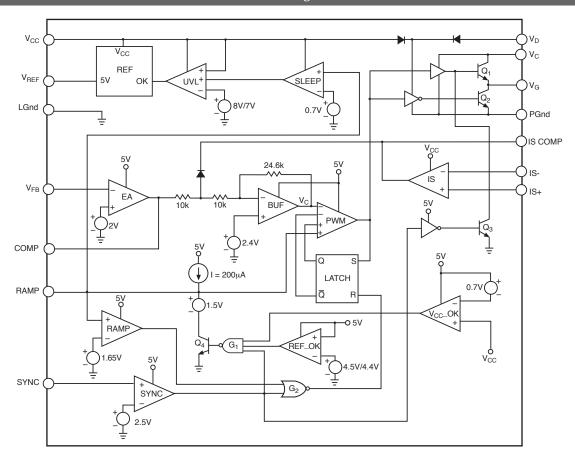

Block Diagram

#### **Theory of Operation**

The CS5101 is designed to regulate voltages in multiple output power supplies. Functionally, it is similar to a magnetic amplifier, operating as a switch with a delayed turn-on. It can be used with both single ended and dual ended topologies.

The V<sub>FB</sub> voltage is monitored by the error amplifier EA. It is compared to an internal reference voltage and the amplified differential signal is fed through an inverting amplifier into the buffer, BUF. The buffered signal is compared at the PWM comparator with the ramp voltage generated by capacitor  $C_R$ . When the ramp voltage  $V_{R'}$ exceeds the control voltage  $V_C$ , the output of the PWM comparator goes high, latching its state through the LATCH, the output stage transistor  $Q_1$  turns on, and the external power switch, usually an N-FET, turns on.

#### **SYNC Function**

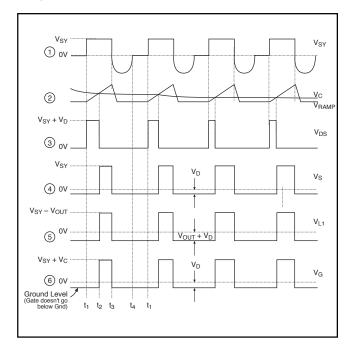

The SYNC circuit is activated at time  $t_1$  (Figure 1) when the voltage at the SYNC pin exceeds the threshold level (2.5V) of the SYNC comparator. The external ramp capacitor  $C_R$  is allowed to charge through the internal current source I (200 $\mu$ A). At time  $t_2$ , the ramp voltage intersects with the control voltage  $V_C$  and the output of the PWM comparator goes high, turning on the output stage and the external power switch. At the same time, the PWM comparator is latched by the RS latch, LATCH.

Figure 1. Waveforms for CS5101. The number to the left of each curve refers to a node on the Application Diagram.

The logic state of the LATCH can be changed only when both the voltage level of the trailing edge of the power pulse at the SYNC pin is less than the threshold voltage of the SYNC comparator (2.5V) and the RAMP voltage is less than the threshold voltage of the RAMP comparator (1.65V). On the negative going transition of the secondary side pulse V<sub>SY</sub>, gate G<sub>2</sub> output goes high, resetting the latch at time t<sub>3</sub>. Capacitor C<sub>R</sub> is discharged through transistor Q<sub>4</sub>. C<sub>R</sub>'s output goes low disabling the output stage, and the external power switch (an N-FET) is turned off.

#### **RAMP** Function

The value of the ramp capacitor  $C_R$  is based on the switching frequency of the regulator and the maximum duty cycle of the secondary pulse  $V_{SY}$ . If the RAMP pin is pulled externally to 0.3V or below, the SSPR is disabled. Current drawn by the IC is reduced to less than  $100\mu A$ , and the IC is in SLEEP mode.

#### **FAULT Function**

The voltage at the V<sub>CC</sub> pin is monitored by the undervoltage lockout comparator with hysteresis. When V<sub>CC</sub> falls below the UVL threshold, the 5V reference and all the circuitry running off of it is disabled. Under this condition the supply current is reduced to less than  $500\mu$ A.

The V<sub>CC</sub> supply voltage is further monitored by the V<sub>CC</sub>–OK comparator. When V<sub>CC</sub> is reduced below V<sub>REF</sub> - 0.7V, a fault signal is sent to gate G<sub>1</sub>. This fault signal, which determines if V<sub>CC</sub> is absent, works in conjunction with the ramp signal to disable the output, but only after the current cycle has finished and the RS latch is reset. Therefore this fault will not cause the output to turn off during the middle of an on pulse, but rather will utilize lossless turn-off. This feature protects the FET from overvoltage stress. This is accomplished through gate G<sub>1</sub> by driving transistor Q<sub>4</sub> on.

An additional fault signal is derived from the REF\_OK comparator.  $V_{REF}$  is monitored so to disable the output through gate  $G_1$  when the  $V_{REF}$  voltage falls below the OK threshold. As in the  $V_{CC}$ -OK fault, the REF\_OK fault disables the output after the current cycle has been completed. The fault logic will operate normally only when  $V_{REF}$  voltage is within the specification limits of REF\_OK.

#### **DRAIN** Function

The drain pin,  $V_D$  monitors the voltage on the drain of the power switch and derives energy from it to keep the output stage in an off state when  $V_C$  or  $V_{CC}$  is below the minimum specified voltage.

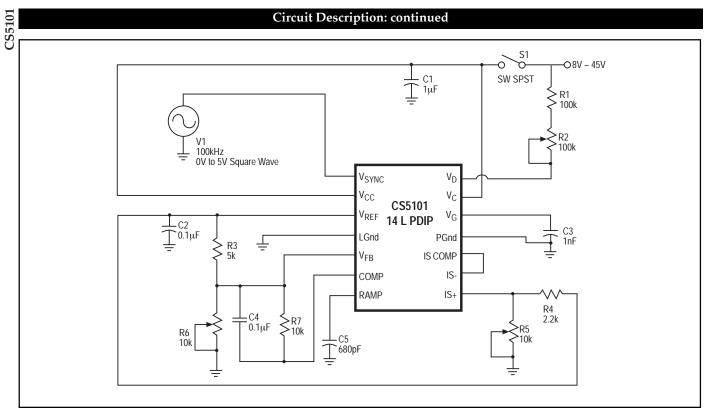

CS5101 bench test

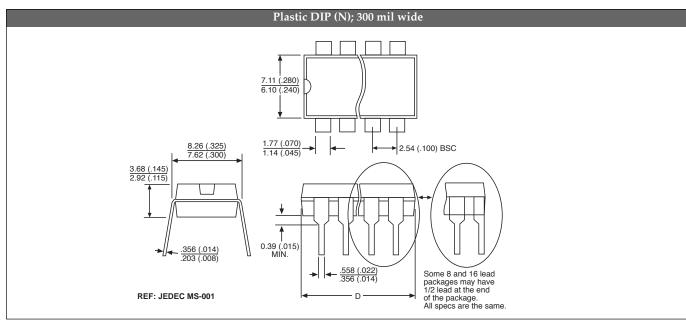

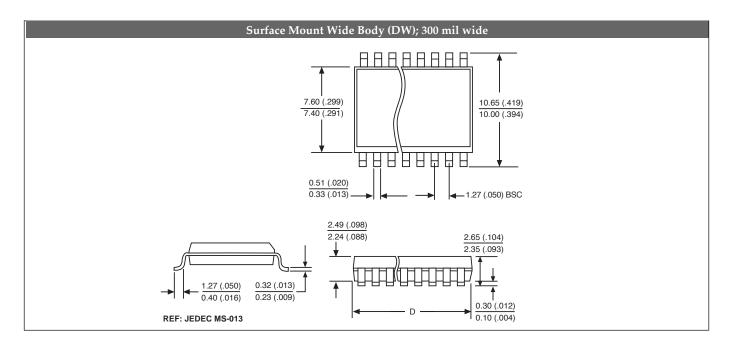

#### **Package Specification**

#### PACKAGE DIMENSIONS IN mm (INCHES)

#### PACKAGE THERMAL DATA

CS5101

|             | D     |       |      |       |

|-------------|-------|-------|------|-------|

| Lead Count  | Me    | tric  | Eng  | glish |

|             | Max   | Min   | Max  | Min   |

| 14L PDIP    | 19.69 | 18.67 | .775 | .735  |

| 16L SO Wide | 10.50 | 10.10 | .413 | .398  |

| Therma            | al Data | 16L SOIC | 14L PDIP |      |

|-------------------|---------|----------|----------|------|

| R <sub>ØJC</sub>  | typ     | 23       | 48       | °C/W |

| R <sub>\OJA</sub> | typ     | 105      | 85       | °C/W |

| 01'      | T (         |

|----------|-------------|

| Ordering | Information |

| 01000000 |             |

| Part Number  | Description               |

|--------------|---------------------------|

| CS5101EN14   | 14L PDIP                  |

| CS5101EDW16  | 16L SO Wide               |

| CS5101EDWR16 | 16L SO Wide (tape & reel) |

Cherry Semiconductor Corporation reserves the right to make changes to the specifications without notice. Please contact Cherry Semiconductor Corporation for the latest available information. PATENTS PENDING

Rev. 3/31/97